查询GC4114供应商

IEXAS RUMENTS

**SLWS134**

# GC4114

# **QUAD TRANSMIT CHIP**

# DATASHEET

May 22, 2000

Rev 1.0

This datasheet contains information which may be changed at any time without notice.

# DATA SHEET REV 1.0

# **REVISION HISTORY**

| Revision | Date          | Description                                                                                                                                                                                                                    |

|----------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0.0      | 20 April 1998 | Original                                                                                                                                                                                                                       |

| 0.1      | 10 July, 1998 | Page 22, added 55531C to the mask revision table,<br>Page 26, t <sub>CDLY</sub> changed from 30 to 40ns.                                                                                                                       |

| 1.0      | 22 May, 2000  | Upgraded to 70 MHz clock rate throughout<br>Page 26, revised timing specifications: Fck, tDLY, tHD,tSSU, tSHD, tCDLY, Notes.<br>Pages 34, 35, Changed Notes for diagnostics 3 and 4<br>Page 37, Corrected input test Table 17. |

# DATA SHEET REV 1.0

| 1.0 |                                                                                                             | KEY FEATURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | .1                                                                   |

|-----|-------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| 2.0 |                                                                                                             | BLOCK DIAGRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | .1                                                                   |

| 3.0 |                                                                                                             | FUNCTIONAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                             | .2                                                                   |

|     | 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9<br>3.10<br>3.11<br>3.12                         | CONTROL INTERFACE<br>INPUT FORMAT<br>GAIN<br>THE UP-CONVERTERS<br>THE OVERALL INTERPOLATION FILTER RESPONSE<br>THE SUM TREE<br>OVERALL GAIN<br>CLOCKING<br>SYNCHRONIZATION<br>POWER DOWN MODES<br>DIAGNOSTICS<br>INITIAL BOARD DEBUG PROCEDURE                                                                                                                                                                                                                                     | . 2<br>. 3<br>. 5<br>. 9<br>. 9<br>10<br>11<br>11                    |

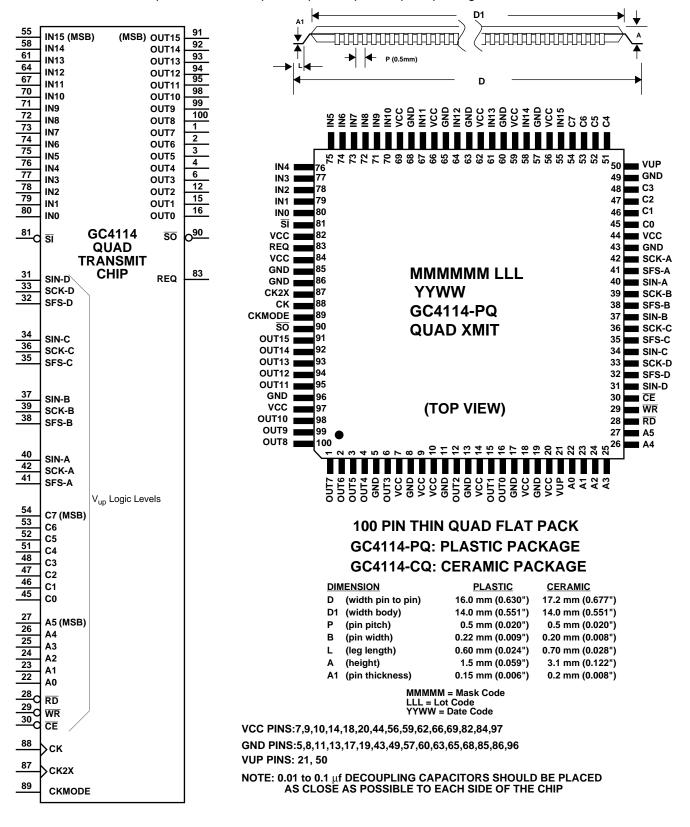

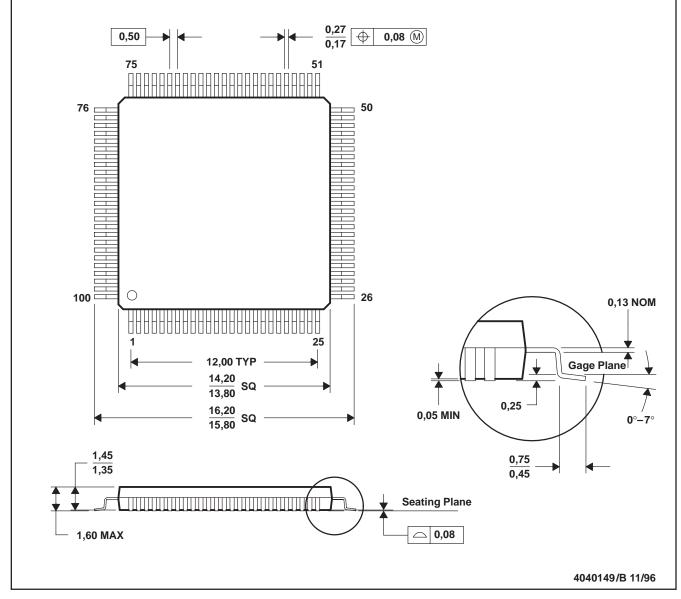

| 4.0 |                                                                                                             | PACKAGING                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 12                                                                   |

| 5.0 |                                                                                                             | CONTROL REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 14                                                                   |

|     | 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11<br>5.12<br>5.13<br>5.14<br>5.15 | SYNC MODE REGISTER<br>INTERPOLATION MODE REGISTER<br>INTERPOLATION GAIN REGISTER<br>INTERPOLATION REGISTERS<br>INPUT MODE REGISTER<br>COUNTER MODE REGISTER<br>CHANNEL SYNC REGISTERS<br>CHANNEL FLUSH CONTROL REGISTER<br>SUMMER MODE REGISTER<br>STATUS CONTROL REGISTER<br>CHECKSUM REGISTER<br>CHECKSUM REGISTER<br>CHANNEL INPUT REGISTERS.<br>PAGE ZERO (CHANNEL CONTROL) REGISTERS.<br>PAGE ONE (STATUS AND TEST) REGISTERS<br>PAGES TWO AND THREE (COEFFICIENT) REGISTERS. | 16<br>16<br>17<br>17<br>18<br>19<br>20<br>20<br>21<br>21<br>22<br>23 |

| 6.0 |                                                                                                             | SPECIFICATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                      |

|     | 6.1<br>6.2<br>6.3<br>6.4<br>6.5                                                                             | ABSOLUTE MAXIMUM RATINGS<br>RECOMMENDED OPERATING CONDITIONS<br>THERMAL CHARACTERISTICS<br>DC CHARACTERISTICS<br>AC CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                                | 24<br>24<br>25<br>26                                                 |

| 7.0 |                                                                                                             | APPLICATION NOTES                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                      |

|     | 7.1<br>7.2<br>7.3<br>7.4<br>7.5<br>7.6<br>7.7<br>7.8<br>7.9                                                 | POWER AND GROUND CONNECTIONS<br>STATIC SENSITIVE DEVICE<br>SYNCHRONIZING MULTIPLE GC4114 CHIPS<br>THERMAL MANAGEMENT<br>PULSE SHAPING AND MODULATING QPSK OR QAM DATA<br>DIAGNOSTICS<br>OUTPUT TEST CONFIGURATION<br>INPUT TEST CONFIGURATION<br>PERIODIC SYNC MODE                                                                                                                                                                                                                | 27<br>27<br>27<br>28<br>32<br>36<br>37                               |

# DATA SHEET REV 1.0

# LIST OF FIGURES

| Figure 1:  | GC4114 Block Diagram                   | 1  |

|------------|----------------------------------------|----|

| Figure 2:  | Control I/O Timing                     | 3  |

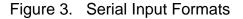

| Figure 3:  | Serial Input Formats                   | 4  |

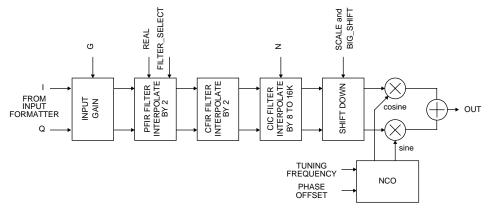

| Figure 4:  | The Up-converter Channel               | 5  |

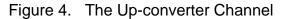

| Figure 5:  | PFIR Spectral Response                 | 6  |

| Figure 6:  | Four Stage CIC Interpolate by N Filter | 7  |

| Figure 7:  | NCO Circuit                            | 8  |

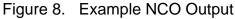

| Figure 8:  | Example NCO Output                     | 9  |

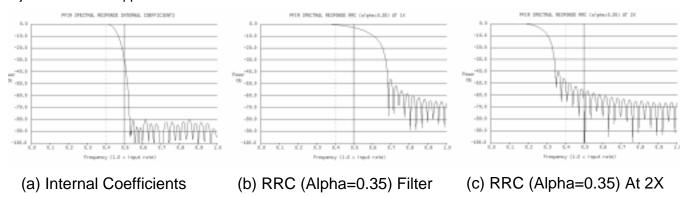

| Figure 9:  | Overall Filter Response                | 9  |

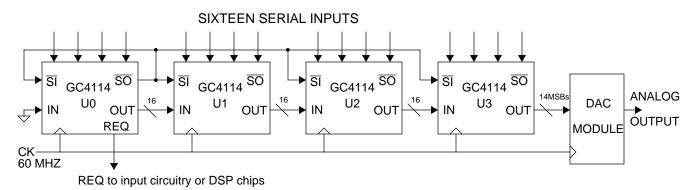

| Figure 10: | Sixteen Channel Modulator              | 28 |

|            |                                        |    |

# LIST OF TABLES

| Sync Modes                             | 15                                                                                                                                                                                                                                                                                                                             |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                        |                                                                                                                                                                                                                                                                                                                                |

|                                        |                                                                                                                                                                                                                                                                                                                                |

|                                        |                                                                                                                                                                                                                                                                                                                                |

|                                        |                                                                                                                                                                                                                                                                                                                                |

| DC Operating Conditions                |                                                                                                                                                                                                                                                                                                                                |

|                                        |                                                                                                                                                                                                                                                                                                                                |

|                                        |                                                                                                                                                                                                                                                                                                                                |

| QPSK Symbol Map                        |                                                                                                                                                                                                                                                                                                                                |

| 1X QPSK Configuration                  |                                                                                                                                                                                                                                                                                                                                |

| 2X QPSK Configuration                  | 31                                                                                                                                                                                                                                                                                                                             |

| Diagnostic Test 1 Configuration        |                                                                                                                                                                                                                                                                                                                                |

| Diagnostic Test 2 Configuration        |                                                                                                                                                                                                                                                                                                                                |

| Diagnostic Test 3 Configuration        |                                                                                                                                                                                                                                                                                                                                |

| Diagnostic Test 4 Configuration        |                                                                                                                                                                                                                                                                                                                                |

| Output Test Configuration              |                                                                                                                                                                                                                                                                                                                                |

| Input Test Configuration               |                                                                                                                                                                                                                                                                                                                                |

| Periodic Sync Initialization Procedure |                                                                                                                                                                                                                                                                                                                                |

|                                        | AC Characteristics<br>Example QPSK Signal Parameters<br>QPSK Symbol Map<br>1X QPSK Configuration<br>2X QPSK Configuration<br>Diagnostic Test 1 Configuration<br>Diagnostic Test 2 Configuration<br>Diagnostic Test 3 Configuration<br>Diagnostic Test 4 Configuration<br>Output Test Configuration<br>Input Test Configuration |

# DATA SHEET REV 1.0

# **GC4114 DATASHEET**

#### 1.0 KEY FEATURES

- Four identical up-convert channels

- Independent modulation frequencies

- Independent phase/gain controls

- The four input signals are summed into a single output signal

- Maximum output rate of 70 MHz

- 16 bit real or complex inputs

- Interpolation factors of 16 to 32,768 in the real input mode 32 to 65,536 in the complex input mode

- Bit serial input format, or

- Memory mapped input registers

- 8 to 16 bit output samples

- 2's Complement or offset-binary output format

- 0.02 Hz tuning resolution

- 90 dB Spur Free Dynamic Range

- > 90 dB far image rejection

- > 70dB near image rejection

- 0.07 dB gain resolution

- 0.05 dB peak to peak passband ripple

- User programmable 63 tap input filter

- Accepts QPSK or QAM symbol data directly, performs transmit (pulse shape) filtering

- Meets Damps and GSM specifications

- Sum I/O path to merge outputs from multiple GC4114 chips

- Microprocessor interface for control, input, and diagnostics

- Built in diagnostics

- Microprocessor and serial inputs will accept either 3.3 or 5 volt input levels.

- 800 mW at 33 MHz, 3.3 volts

- 100 pin thin QFP package

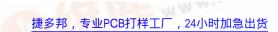

# 2.0 BLOCK DIAGRAM

A block diagram illustrating the major functions of the chip is shown in Figure 1.

Figure 1. GC4114 Block Diagram

#### **DATA SHEET REV 1.0**

#### 3.0 FUNCTIONAL DESCRIPTION

The GC4114 quad transmit chip contains four identical up-conversion circuits. Each up-convert circuit accepts a real or complex signal, interpolates it by a programmable factor ranging from 32 to 65,536 (16 to 32,768 for single-sideband modulation), up-converts the signal to a selected center frequency, sums it with other up-converted samples and outputs the combined signal. The chip contains a user programmable input filter which can be used to shape the transmitted data, or can be used as a Nyquist transmit filter for digital data transmission. See the application notes in Section 7.5 for details on using the chip to transmit QPSK or QAM data.

The up-converters are designed to maintain over 90 dB of spur free dynamic range and image rejection. Each up-convert circuit accepts 16 bit inputs (bit serial) and produces 16 bit outputs. The up-converter outputs are summed with an external 16 bit input to produce a single 16 bit output. The frequencies and phase offsets of the four sine/cosine sequence generators can be independently specified, as can the gain of each circuit. The up-converters share the same bandwidth, filter coefficients and input formats.

On chip diagnostic circuits are provided to simplify system debug and maintenance.

The chip receives configuration and control information over a microprocessor compatible bus consisting of an 8 bit data I/O port, a 6 bit address port, a chip enable strobe, a read strobe and a write strobe. The chip's 64 control registers (8 bits each) are memory mapped into the 6 bit address space of the control port.

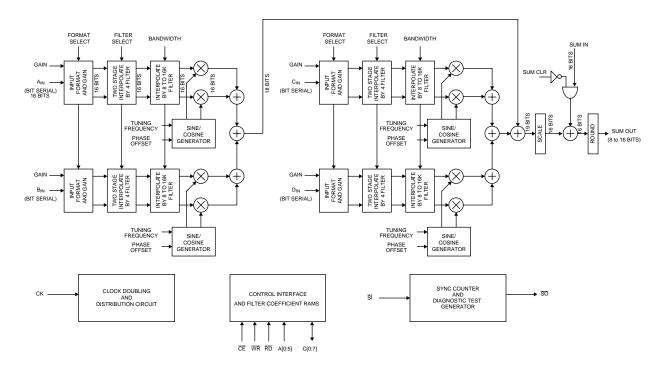

#### 3.1 CONTROL INTERFACE

The chip is configured by writing control information into sixty four control registers within the chip. The contents of these control registers and how to use them are described in Section 5. The registers are written to or read from using the C[0:7], A[0:5],  $\overline{CE}$ ,  $\overline{RD}$  and  $\overline{WR}$  pins. Each control register has been assigned a unique address within the chip. This interface is designed to allow the GC4114 to appear to an external processor as a memory mapped peripheral (the pin  $\overline{RD}$  is equivalent to a memory chip's  $\overline{OE}$  pin).

An external processor (a microprocessor, computer, or DSP chip) can write into a register by setting A[0:5] to the desired register address, selecting the chip using the  $\overline{CE}$  pin, setting C[0:7] to the desired value and then pulsing  $\overline{WR}$  low. The data will be latched on the rising edge of  $\overline{WR}$  or  $\overline{CE}$ .

To read from a control register the processor must set A[0:5] to the desired address, select the chip with the  $\overline{CE}$  pin, and then set  $\overline{RD}$  low. The chip will then drive C[0:7] with the contents of the selected register. After the processor has read the value from C[0:7] it should set  $\overline{RD}$  and  $\overline{CE}$  high. The C[0:7] pins are turned off (high impedance) whenever  $\overline{CE}$  or  $\overline{RD}$  are high or when  $\overline{WR}$  is low. The chip will only drive these pins when both  $\overline{CE}$  and  $\overline{RD}$  are low and  $\overline{WR}$  is high.

One can also ground the  $\overline{RD}$  pin and use the  $\overline{WR}$  pin as a read/write direction control and use the  $\overline{CE}$  pin as a control I/O strobe.

# **DATA SHEET REV 1.0**

Figure 2 shows timing diagrams illustrating both I/O modes.

Figure 2. Control I/O Timing

The setup, hold and pulse width requirements for control read or write operations are given in Section 6.0.

The C, A,  $\overline{WR}$ ,  $\overline{RD}$  and  $\overline{CE}$  pins will accept either 5 volt or 3.3 volt input levels. Separate power supply pins (V<sub>UP</sub>) are provided on the chip to enable this feature.

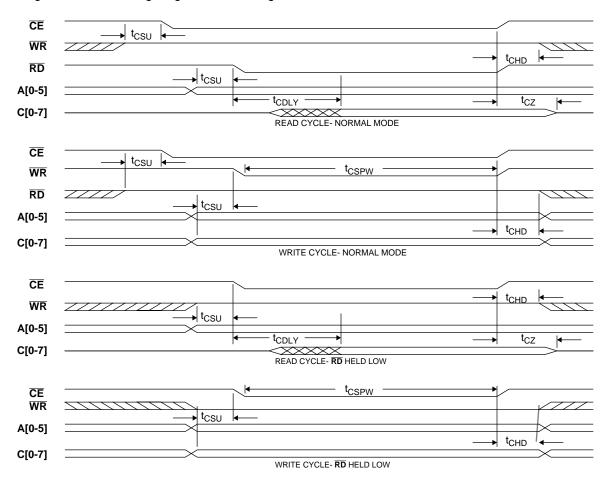

#### 3.2 INPUT FORMAT

The input samples are 16 bits, either real or complex, in 2's complement format. The samples are input to the chip either through the bit-serial input ports, or through memory mapped control registers.

#### 3.2.1 Bit Serial Interface

The bit serial format consists of a data input pin, a bit clock pin, and a frame strobe pin for each of the four channels, and a data request pin which is common to all channels. The input accepts either individual 16 bit words in a format compatible with almost all DSP chips, or as the upper 16 bits of 32 bit words, or as two 16 bit words packed into a 32 bit word. The bit serial data is always entered MSB first. Complex values are entered I-half first followed by the Q-half, either as two separate transfers, or as a single 32 bit words. In the I-half in the MSBs and the Q-half in the LSBs. Real values can be entered as 16 bit words or 32 bit words. In the 32 bit mode each 16 bit

| Texas Instruments Inc. | - 3 - | MAY 22, 2000 |

|------------------------|-------|--------------|

|                        |       |              |

#### **DATA SHEET REV 1.0**

2000

real word is placed in the upper 16 bits of the 32 bits. Real samples can also be entered in the complex input mode by alternately placing samples in the I and Q halves of the complex input words. The data request signal (REQ) is output from the chip to identify when the GC4114 is ready for another serial input sample.

The bit serial inputs use the format shown in Figure 3:

Figure 3a shows the standard input mode (PACKED in the input control register is low). The user provides a bit serial clock (SCK), a frame strobe (SFS) and a data bit line (SIN). The chip clocks SFS and SIN into the chip on the rising edge of SCK (or falling edge if the SCK\_POL bit in the input control register is set). The user sends a 16 bit serial input word to the GC4114 by setting SFS high (or low if SFS\_POL in the input control register is set) for at least one SCK clock cycle, and then transmitting the data, MSB first, on the next 16 SCK clocks. The user must set SFS low at least one SCK clock cycle before the next serial transfer. The data can be transmitted "back to back" as shown in Figure 3b as long as the SFS signal toggles low and then high as shown. If the PACKED control bit is high, then the I and Q samples are sent as a single 32 bit word with only one SFS strobe as shown in Figure 3c.

The GC4114 input interface sends a "new sample request" strobe (REQ) when a new input sample is required for the up-converter channels. The input sample rate is  $F_S=F_{CK}/2N$  for real inputs and  $F_S=F_{CK}/4N$  for complex inputs, where  $F_{CK}$  is the chip's clock rate and N is the interpolation ratio in the CIC filter which varies from 8 to 16,384 (See Section 5.4). This means that the REQ strobe will be output from the chip every 2N clocks (CK, not SCK) in the real mode or every 4N clocks in the complex mode. The pulse width of the REQ strobe can be specified by the user to be either 2 clocks (CK) wide or N/2 clocks wide. The polarity of REQ is user programmable. The REQ strobe is typically used as an interrupt to an external device to tell it to send another input sample. The GC4114 chip must receive the last data bit at least one bit clock (SCK) period before the next REQ strobe.

If the serial interface timing is tight, i.e., the serial bit rate is so slow that the serial frames barely fit between REQ strobes, then the bit serial transfer can start up to 7 bit clocks before the REQ strobe. This means that the frame sync can be sent up to 7 bit clocks before REQ.

| Texas Instruments Inc. |  | - 4 - |  |  | MAY 22, | , |  |

|------------------------|--|-------|--|--|---------|---|--|

|                        |  |       |  |  |         |   |  |

#### **DATA SHEET REV 1.0**

**Very Important Note:** The chip assumes that the serial clock is continuous, and does not stop between transfers. The SCK clock may stop, but must be active when frame sync occurs, and be active for one cycle after the last bit is sent. Serial data can be sent using only 32 bit clocks per REQ period if the frame sync for the 16 bit I word (or the 32 bit I/Q word in the PACKED mode) is synchronized to occur between 7 and 2 bit periods *before* REQ.

The user can choose to operate the serial lines as either 3.3 or 5 volt logic levels to facilitate the interface of the GC4114 chip with external circuitry.

#### 3.2.2 Memory Mapped Interfaced

Input samples can be entered into the chip using the control interface. Addresses 16 through 31 are the input data registers. Note that these registers can be written to in a DMA burst, 8 bits at a time. Note that some DMA formats write samples most significant byte first. If this is the case then the DMA should write from address 31 down to address 16. The REQ strobe from the GC4114 chip defines when the DMA transfer can start. The transfer must be done before the next REQ strobe is received.

#### 3.3 GAIN

Each input sample is multiplied by an 8 bit 2's complement gain word. If the gain word is 'G', which ranges from -128 to +127, then the gain adjustment will be G/128. This gives a 42 dB gain adjustment range. Setting G to zero clears the channel. A different gain can be specified for each channel. Gain is described in more detail in Section 3.7.

#### 3.4 THE UP-CONVERTERS

Each up-converter channel uses a two stage interpolate by four filter and a 4 stage cascaded integrate-comb (CIC) filter to increase the sample rate of the input data up to a sample rate equal to the chip's clock rate. An NCO and mixer circuit to modulate the signal up to the desired center frequency. A block diagram of each up-convert channel is shown below:

After the gain has been applied, as described in the previous section, the input data is interpolated by a factor of 2 in a 63 tap filter with programmable coefficients (PFIR). The user can choose between an internal default filter shape for the PFIR, or can download a custom set of taps. A typical use of the user down loaded coefficients is to implement matched (root-raised-cosine) transmit filters.

Texas Instruments Inc. - 5 -

MAY 22, 2000

#### **DATA SHEET REV 1.0**

The PFIR will also, if desired, convert real input data to single-sideband complex data. In this mode the PFIR does not interpolate by a factor of 2. Instead it down-converts the input data by  $F_S/4$ , where  $F_S$  is the input sample rate, and low pass filters the result.

The second interpolate by 2 filter is a 31 tap compensating filter (CFIR) which pre-compensates for the droop associated with the CIC filter that follows it.

The CIC filter interpolates by another factor of N=8 to 16,384 to give an overall interpolation factor of 32 to 65,536 (16 to 32,768 in the real input mode).

The interpolated signal is up-converted by a sine/cosine sequence generated by the NCO. The real part (I-half) of the complex result is saved as the channel output.

#### 3.4.1 The Programmable Input Filter (PFIR)

The programmable input filter uses either internal ROM based coefficients, or externally downloaded filter coefficients. The 63 filter coefficients are quantized to 16 bit words. The internal 80% bandwidth filter is flat over the range of  $-0.4F_S$  to  $+0.4F_S$  with 0.03 dB of passband ripple, and with 80db of out of band image rejection. The 32 unique coefficients in the 63 tap symmetric filter are:

-14, -20, 19, 73, 43, -70, -82, 84, 171, -49, -269, -34, 374, 192, -449, -430, 460, 751, -357, -1144, 81, 1581, 443, -2026, -1337, 2437, 2886, -2770, -6127, 2987, 20544, 29647

The internal filter is typically used for signals that are digitized analog signals such as voice, AM, FM or SSB signals. The internal filter is also used for digital signals (FSK, PSK, QAM or GMSK signals for example) that have already been modulated and filtered and are ready to be up-converted to their desired carrier frequency.

The external coefficients are typically used to "pulse shape" and then up-convert digital data. The PFIR will accept QPSK, O-QPSK, PSK, PAM, OOK,  $\pi$ /4-QPSK, or QAM symbols and then filter them by the desired pulse shaping filter. A common pulse shaping filter is the root-raised-cosine (RRC) filter. The symbols can be entered directly into the chip at the desired symbol (baud) rate, or entered at twice the baud rate by alternately entering symbol data and entering zeroes.<sup>1</sup> The "twice the baud rate" or "2X" method results in better out of band image rejection. See the application note in Section 7.5 for more details.

Figure 5a shows the spectral response of the internal filter. Figure 5b shows the root-raised-cosine pulse shaping filter with 35% excess bandwidth (alpha=0.35). Figure 5c shows the RRC shape for the 2X mode.

1. Called zero padding.

Texas Instruments Inc.

MAY 22, 2000

\_\_\_\_\_

#### **DATA SHEET REV 1.0**

The set of coefficients used to generate the RRC filter shown in Figure 5b are:

27, -20, -6, 34, -30, -9, 39, -37, -1, 52, -55, -5, 62, -72, 15, 92, -117, 8, 112, -175, 82, 224, -348, 61, 286, -761, 766, 1708, -4042, -2533, 18177, 32767

The set of coefficients used to generate the 2X RRC filter shown in Figure 5c are:

```

-12, -117, -113, 8, 127, 112, -38, -175, -134, 82, 275, 224, -71,

-348,-307, 61, 398, 286, -286, -761, -442, 766, 1954, 1708, -660,

-4042,-5641, -2533, 6187, 18177, 28625, 32767

```

The PFIR will accept either complex or real input data. If the input samples are complex, the filter doubles the input rate by inserting zeroes between each sample, and then low pass filtering the result. If the input samples are real, the filter translates the real samples down by  $F_S/4$ , where  $F_S$  is the input sample rate, by multiplying them by the complex sequence +1, -j, -1, +j, ..., and then lowpass filtering the result. This generates a single-sideband modulation of the real input. If double sideband real upconversion is desired, then the chip should be operated in the complex mode with the Q-half of each complex pair set to zero.

The PFIR has a gain which is equal to (PFIR\_SUM/65536), where PFIR\_SUM is equal to the sum of all of the filter coefficients. The internal filter coefficients have PFIR\_SUM=65543 which gives very close to unity gain. The RRC filter shown in Figure 5b has PFIR\_SUM=59821 and the 2X RRC filter shown in Figure 5c has PFIR\_SUM=119357. See Section 3.7 for more details on the chip's gain settings.

The PFIR output rate relative to the input rate is  $2F_S$  in the complex input mode and is  $F_S$  in the real (single side band) mode. The output rate relative to the clock rate is  $F_{CK}/2N$ .

#### 3.4.2 The Compensating Interpolate by 2 Filter (CFIR)

The second stage filter is a fixed coefficient 31 tap interpolate by 2 filter. The second stage filter always interpolates by a factor of two. The second filter has a passband which is flat (0.01 dB ripple) over 100% of the input bandwidth ( $-0.5F_S$  to  $+0.5F_S$ ). The second filter also compensates for the droop associated with the CIC interpolation filter described in the next section. The 16 unique coefficients of the symmetric filter are:

-23, -3, 103, 137, -21, -230, -387, -235, 802, 1851, 81, -4372, -4774, 5134, 20605, 28216

The CFIR output is scaled to have unity gain. The output rate of the CFIR filter is  $4F_S$  in the complex mode and is  $2F_S$  in the real mode. The CFIR output rate relative to the clock rate is  $F_{CK}/N$ .

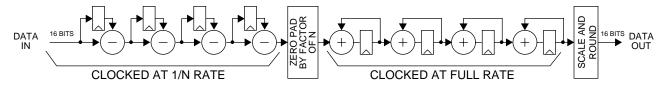

#### 3.4.3 The CIC Interpolate by N Filter

The CFIR output is interpolated by a factor of N in the CIC<sup>1</sup> filter, where N is any integer between 8 and 16,384. The filter is a 4 stage CIC filter. A block diagram of the CIC filter is shown in Figure 6.

## Figure 6. Four Stage CIC Interpolate by N Filter

1. Hogenauer, Eugene B., An Economical Class of Digital Filters for Decimation and Interpolation, IEEE transactions on Acoustics, Speech and Signal Processing, April 1981.

#### **DATA SHEET REV 1.0**

The output of the CIC interpolation filter is equal to the clock rate. The CIC filter has a gain equal to N<sup>3</sup> which must be removed by the "SCALE AND ROUND" circuit shown in Figure 6. This circuit has a gain equal to  $2^{-(3+SCALE+12*BIG_SHIFT)}$ , where SCALE ranges from 0 to 15 and BIG\_SHIFT ranges from 0 to 2. The value chosen for BIG\_SHIFT must also satisfy:  $2^{(12*BIG_SHIFT+18)} \ge N^3$ . Overflows due to improper gain settings will go undetected if this relationship is violated. This restriction means that BIG\_SHIFT = 0 for N between 8 and 64, BIG\_SHIFT = 1 for N between 65 and 1024, and BIG\_SHIFT = 2 for N between 1025 and 16384.

The CIC filter must be initialized when the chip is first configured or whenever the interpolation value N or the shift value BIG\_SHIFT are changed. The CIC filter is initialized using the flush controls described in Section 5.8. If the CIC is disturbed during processing due to noise, radiation particles, or due to changing N or BIG\_SHIFT, then it will become unstable and generate wideband white noise in the output. This instability can be prevented by using the "auto flush" capability of the chip<sup>1</sup> (See control register 2, bit 6 in Section 5.3). The auto flush mode detects the CIC instability and automatically re-initializes the CIC. The auto flush mode requires that the gain up to the output of the CIC filter is less than or equal to unity.

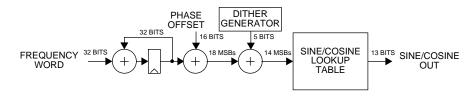

#### 3.4.4 The Sine/Cosine Generator

The tuning frequency of each up-converter is specified as a 32 bit word and the phase offset is specified as a 16 bit word. The tuners can be synchronized with tuners on other chips. This allows multiple up-converter outputs to be coherently combined, each with a unique phase and amplitude. A block diagram of the NCO (Numerically Controlled Oscillator) circuit is shown in Figure 7.

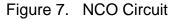

The NCO's spur level is reduced to below 90 dB through the use of phase dithering. Figure 8 shows an example NCO output with and without dithering. Notice that the spur level without dithering is about -82 dB, and the spur level with dithering is well below -90 dB.

The tuning frequency is set according to the formula FREQ =  $2^{32}$ F/F<sub>CK</sub>, where F is the desired tuning frequency and F<sub>CK</sub> is the chip's clock rate. The 16 bit phase offset setting is PHASE =  $2^{16}$ P/2 $\pi$ , where P is the desired phase in radians ranging between 0 and  $2\pi$

<sup>1.</sup> The auto flush mode is a patent pending feature of the chip.

# DATA SHEET REV 1.0

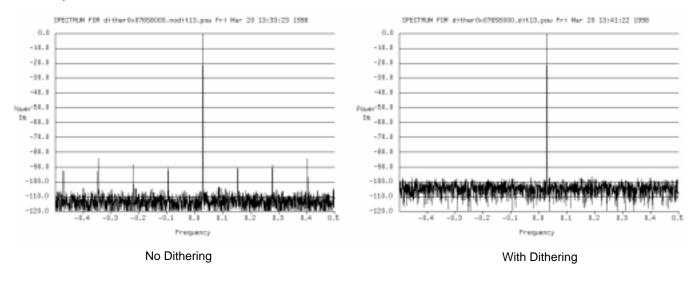

#### 3.5 THE OVERALL INTERPOLATION FILTER RESPONSE

The image rejection of the up-convert channel is equal to the stop band rejection of the overall interpolation filter response. The overall response is obtained by superimposing the interpolated responses of the PFIR and CFIR filters onto the CIC filter response. The overall response is shown in Figure 9. Figure 9a shows the overall response using the default PFIR coefficients. Figure 9b shows the response using a root-raised-cosine PFIR coefficient set. Figure 9c shows the response when using the 2x mode root-raised cosine PFIR coefficient set.

(a) Internal Coefficients

(b) RRC (Alpha=0.35) Filter

(c) RRC (Alpha=0.35) At 2X

Figure 9. Overall Filter Response

# 3.6 THE SUM TREE

The four up-convert channel outputs are summed together, scaled down by powers of two and then added to an external sum input. The sum tree output is rounded to 8, 10, 12, 14 or 16 bits and output from the chip. The sum of the four channels within the chip can be scaled down by powers of two in order to prevent saturation when channels from multiple chips are summed together. The scale factor is equal to 2<sup>-SUM\_SCALE</sup>, where SUM\_SCALE is 0,1,2 or 3 (See Section 5.9). Overflows in the sum tree are saturated to plus or minus full scale.

The latency from IN[0:15] to OUT[[0:15] is seven clock cycles. The chip will optionally invert the MSB output (OUT15) from the chip in order to drive offset binary format digital to analog converters (DACs)

| Texas Instruments Inc. | - ! | 9 - | MAY 22, 2000 |

|------------------------|-----|-----|--------------|

|                        |     |     |              |

#### **DATA SHEET REV 1.0**

#### 3.7 OVERALL GAIN

The overall gain of the chip is a function of the sum of the programmable filter coefficients (PFIR\_SUM) described in Section 3.4.1, the amount of interpolation in the CIC filters (N described in Section 3.4.3), the scale circuit settings in the CIC filter (SCALE and BIG\_SHIFT described in Section 3.4.3), and the sum tree scale factor (SUM\_SCALE described in Section 3.6). The overall gain is:

$$GAIN = \left\{ \frac{G}{128} \right\} \left\{ \frac{PFIR\_SUM}{65536} \right\} \left\{ N^3 2^{-(SCALE + 12 \times BIG\_SHIFT + 3)} \right\} \left\{ 2^{-SUM\_SCALE} \right\}$$

where G can be different for each channel, but N, SCALE, BIG\_SHIFT, SUM\_SCALE and PFIR\_SUM are common to all channels.

The optimal gain setting is one which will keep the amplitude of the data within the channel as high as possible without causing overflow. The recommended gain target is to keep the root-mean-squared amplitude of the data close to one-fifth (0.2) full scale (a 14 dB crest factor). This level should be maintained throughout the channel computations. This means that the products  $\left\{\frac{\text{RMS}}{32768}\right\}\left\{\frac{G}{128}\right\}\left\{\frac{\text{PFIR}_{\text{SUM}}}{65536}\right\}$  and  $\left\{\frac{\text{RMS}}{32768}\right\}\left\{\frac{G}{128}\right\}\left\{\frac{\text{PFIR}_{\text{SUM}}}{65536}\right\}\left\{N^32^{-(\text{SCALE}+12\times\text{BIG}_{\text{SHIFT}}+3)}\right\}$  should both be less than or equal to 0.2, where "RMS" is the root-mean-squared level of the input data. Other crest factors can be used depending upon the application. For example, a crest factor of 12 dB is adequate if the final number of bits going to a DAC is 12 bits. In most cases the input data will already have the correct crest factor for the application, in which case the ratio  $\left\{\frac{\text{RMS}}{32768}\right\}$  will be equal to the crest factor (e.g., 0.2) and the gain settings in the channel should be set to unity.

The sum tree gain (SUM\_SCALE) is used when the outputs from multiple channels are summed together. The recommended gain when "M" uncorrelated channels are being added together is  $\frac{1}{\sqrt{M}}$ . For example, if all four channels are active in a GC4114, then M is four and the gain should be 1/2, which can be achieved by setting SUM\_SCALE equal to 1. If four chips are cascaded to sum sixteen channels, then M is 16 and the gain should be 1/4, which implies SUM\_SCALE should be 2.

The  $\frac{1}{\sqrt{M}}$  gain rule assumes that the channels can be treated as uncorrelated signals which will result in an average amplitude gain of  $\sqrt{M}$ . If the signals are correlated, however, the amplitude gain can be M and the sum tree gain should be set to  $\frac{1}{M}$ . Examples of correlated signals are pure tones or modem signals that have been synchronized so that they might peak at the same time. These signals, however, require a much smaller crest factor, such as 3 dB for pure tones and 6 dB for modem signals. In this case the crest factor of 14 dB will absorb much of the difference in gain between  $\sqrt{M}$  and M.

If overflow does occur, then the samples are saturated to plus or minus full scale. Overflow can be monitored using the overflow status register, see Section 5.14 for details.

The values of N and BIG\_SHIFT must also satisfy  $2^{(12*BIG_SHIFT+18)} \ge N^3$  (see Section 3.4.3 for details). If N and BIG\_SHIFT do not satisfy this relationship, then an overflow may occur which may not be detected.

If the auto flush mode is used, then the gain in the CIC must be less than or equal to unity. This means that the values of N, SCALE and BIG\_SHIFT must satisfy  $2^{(SCALE+12*BIG_SHIFT+3)} \ge N^3$  (see Section 3.4.1 for details).

Note that noise due to rounding errors is minimized by keeping the gain as close to unity as is possible. If attenuation is necessary, for example when multiple channel outputs are to be added together, then the attenuation should be added as close to the output of the chip as is possible. This means that the SUM\_SCALE control should be used to add attenuation before the SCALE and BIG\_SHIFT controls are adjusted.

| Texas Instruments Inc. | - 10 - | MAY 22, 2000 |

|------------------------|--------|--------------|

|                        |        |              |

#### **DATA SHEET REV 1.0**

#### 3.8 CLOCKING

The chip can be clocked in one of two modes. In the standard mode, the clock rate is equal to the output data rate which can be up to 70 MHz. An internal clock doubler doubles the clock rate so that the internal circuitry is clocked at twice the data rate. To use the standard mode the CKMODE pin must be grounded and the internal control register bit EN\_DOUBLER must be set high (See Section 5.10).

The alternate clock mode (pin CKMODE is high) accepts a double rate clock on the CK2X pin and bypasses the clock doubler circuit. The EN\_DOUBLER control bit should be low. In the alternate mode the user must provide both the standard clock and the double rate clock. Note that the rising edges of the two clocks must be such that the rising edge of CK is coincident with or precedes the rising edge of CK2X by no more than 2 nanoseconds.

#### 3.9 SYNCHRONIZATION

Multiple chips can be synchronized through the use of a sync input signal, an internal one shot sync generator, and a sync counter. Each circuit within the chip, such as the sine/cosine generators or the interpolation control counter can be synchronized to one of these sources. These syncs can also be output from the chip so that multiple chips can be synchronized to the sync coming from a "master" chip. See Figure 10 in Section 7.5.

The interpolation control counter generates the request strobe (REQ) output from the chip. This counter can be syncronized using the input  $\overline{SI}$  sync (see bits 2 and 3 of address 0). This allows the user to lock the timing of the request strobe to the  $\overline{SI}$  timing. If this is done, then the REQ strobe will go high 5 clock cycles after the  $\overline{SI}$  signal. For example, if the  $\overline{SI}$  signal is active during clock cycle 0, then REQ will go high during clock cycle 5 and then repeat every 4N clocks (or 2N clocks in the real input mode) thereafter.

#### 3.10 POWER DOWN MODES

The chip has a power down circuit. This circuit contains a slow, nominally 1 KHz, oscillator and a clock-loss detect cell. This circuit is used to detect the loss of clock and provide a slow "keep-alive" clock to the chip. The circuit is also used to power down the chip by switching from the high speed input clock to the low speed keep-alive clock. The low speed clock rate is slow enough to power down the chip while fast enough to refresh the dynamic nodes within the chip. The user can select whether this circuit is in the automatic clock-loss detect mode, is always on (power down mode), or is disabled (the slow clock never kicks in).

#### 3.11 DIAGNOSTICS

The chip has an internal ramp generator which can be used in place of the data inputs for diagnostics. An internal checksum circuit generates a checksum of the output data to verify the chip's operation. See Section 7.6 for diagnostic configurations and checksums.

#### 3.12 INITIAL BOARD DEBUG PROCEDURE

The suggested procedure for bringing up the GC4114 chip is to first check the control interface by writing to the control registers and reading them back. The diagnostics described in Section 7.6 should be run next, followed by the output and input tests described in Sections 7.7 and 7.8. If these pass successfully, then the configuration customized for the desired application should work.

#### 4.0 PACKAGING

The GC4114 chip comes in a 100 pin thin plastic quad flatpack package

Texas Instruments Inc.

MAY 22, 2000

# DATA SHEET REV 1.0

| SIGNAL      | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SIN-A,B,C,D | <b>BIT SERIAL INPUT DATA,</b> <i>Active high</i><br>The bit serial input data for the four channels. The I and Q halves of complex data are entered on the same<br>pin. Each time the chip asserts <b>REQ</b> (See below) the I-half is entered and then the Q-half.                                                                                                                                                              |

| SCK-A,B,C,D | <b>BIT SERIAL DATA CLOCK</b> , <i>Active high or low</i><br>The serial data bits are clocked into the chip by these clocks. The active edge of these clocks are user programmable.                                                                                                                                                                                                                                                |

| SFS-A,B,C,D | <b>BIT SERIAL FRAME STROBE</b> , <i>Active high or low</i><br>The bit serial word strobe. This strobe delineates the 16 bit words within the bit serial input stream. This strobe can be a pulse at the beginning of each bit serial word, or can act as a window enable which is active while the data bits are active.                                                                                                          |

| REQ         | <b>REQUEST FLAG</b> , <i>programmable active high or low</i><br>The chip requests new input data by asserting this signal. The width in input clock cycles and polarity of this signal are user programmable. This signal is typically used as an interrupt to a DSP chip, but can also be used as a start pulse to dedicated circuitry.                                                                                          |

| СК          | <b>INPUT CLOCK.</b> Active high<br>The clock input to the chip. The <b>IN[0:15]</b> and $\overline{SI}$ input signals are clocked into the chip on the rising edge of this clock.                                                                                                                                                                                                                                                 |

| СК2Х        | <b>DOUBLE RATE INPUT CLOCK.</b> Active high<br>The double rate clock input to the chip. Used in the alternate clock mode to clock the chip. This clock must<br>be exactly twice the frequency of the <b>CK</b> clock. Should be grounded in the normal clock mode.                                                                                                                                                                |

| CKMODE      | <b>CLOCK MODE</b> , <i>Active high</i><br>The clock mode control. The chip uses <b>CK2X</b> when this pin is tied high (alternate mode) to clock the internal circuitry. When this signal is grounded (normal mode) the chip doubles the <b>CK</b> clock to use as the internal clock.                                                                                                                                            |

| SI          | <b>SYNC IN</b> . Active low<br>The sync input to the chip. All timers, accumulators, and control counters are, or can be, synchronized to $\overline{SI}$ .<br>This sync is clocked into the chip on the rising edge of the input clock ( <b>CK</b> ).                                                                                                                                                                            |

| <u>50</u>   | <b>SYNC OUT</b> . Active low<br>This signal is either a delayed version of the input sync $\overline{SI}$ , the sync counter's terminal count (TC), or a one-shot strobe. The $\overline{SO}$ signal is clocked out of the chip on the rising edge of the input clock (CK).                                                                                                                                                       |

| IN[0:15]    | <b>SUMMER INPUT DATA.</b> <i>Active high</i><br>The 16 bit two's complement summer input samples. New samples are clocked into the chip on the rising edge of the clock. The input data rate is assumed to be equal to the clock rate.                                                                                                                                                                                            |

| OUT[0:15]   | <b>SUMMER OUTPUT DATA</b> . Active high<br>The summer data are output as a 16 bit words on these pins. The bits are clocked out on the rising edge of<br>the clock ( <b>CK</b> ).                                                                                                                                                                                                                                                 |

| C[0:7]      | <b>CONTROL DATA I/O BUS</b> . Active high<br>This is the 8 bit control data I/O bus. Control register data is loaded into the chip or read from the chip through<br>these pins. The chip will only drive these pins when $\overline{CE}$ is low and $\overline{RD}$ is low.                                                                                                                                                       |

| A[0:5]      | <b>CONTROL ADDRESS BUS</b> . <i>Active high</i><br>These pins are used to address the control registers within the chip. Each of the control registers within the chip are assigned a unique address. A control register can be written to or read from by setting <b>A[0:5]</b> to the register's address.                                                                                                                       |

| RD          | <b>READ ENABLE</b> . Active low<br>This pin enables the chip to output the contents of the selected register on the C[0:7] pins when $\overline{CE}$ is also low.                                                                                                                                                                                                                                                                 |

| WR          | <b>WRITE ENABLE</b> . Active low<br>This pin enables the chip to write the value on the C[0:7] pins into the selected register when $\overline{CE}$ is also low.                                                                                                                                                                                                                                                                  |

| CE          | <b>CHIP ENABLE</b> . Active low<br>This control strobe enables the read or write operation. The contents of the register selected by $A[0:5]$ will<br>be output on $C[0:7]$ when $\overline{RD}$ is low and $\overline{CE}$ is low. If $\overline{WR}$ is low and $\overline{CE}$ is low, then the selected register will<br>be loaded with the contents of $C[0:7]$ .                                                            |

| VUP         | MICROPROCESSOR INTERFACE VOLTAGE.<br>This pin is used to set the voltage interface levels for the following control pins: C[0:7], A[0:5], CE, RD, WR,<br>SIN-A, SIN-B, SIN-C, SIN-D, SCK-A, SCK-B, SCK-C, SCK-D, SFS-A, SFS-B, SFS-C, and SFS-D. This pin<br>can be tied to +5 volts to interface the GC4114 to microprocessors with TTL outputs. Tie this pin to +3.3 volts<br>(VCC) to interface with 3.3 volt microprocessors. |

Texas Instruments Inc.

MAY 22, 2000

\_\_\_\_\_\_

2000

# 5.0 CONTROL REGISTERS

The chip is configured and controlled through the use of eight bit control registers. These registers are accessed for reading or writing using the control bus pins ( $\overline{CE}$ ,  $\overline{RD}$ ,  $\overline{WR}$ , A[0:5], and C[0:7]) described in the previous section. The register names and their addresses are:

The Mode and Control Registers are addresses 0 to 15

| ADDRESS | NAME                 | ADDRESS | NAME               |

|---------|----------------------|---------|--------------------|

| 0       | Sync Mode            | 8       | Channel A Sync     |

| 1       | Interpolation Mode   | 9       | Channel B Sync     |

| 2       | Interpolation Gain   | 10      | Channel C Sync     |

| 3       | Interpolation Byte 0 | 11      | Channel D Sync     |

| 4       | Interpolation Byte 1 | 12      | Channel Flush Mode |

| 5       | Input Mode           | 13      | Summer Mode        |

| 6       | Counter Byte 0       | 14      | Status             |

| 7       | Counter Byte 1       | 15      | Checksum           |

The Input registers are addresses 16 to 31. The 16 bit inputs are stored least significant byte in the first address, the most significant in the second.

| ADDRESSES | NAME               | ADDRESSES | NAME               |

|-----------|--------------------|-----------|--------------------|

| 16,17     | Channel A, I-input | 24,25     | Channel C, I-input |

| 18,19     | Channel A, Q-input | 26,27     | Channel C, Q-input |

| 20,21     | Channel B, I-input | 28,29     | Channel D, I-input |

| 22,23     | Channel B, Q-input | 30,31     | Channel D, Q-input |

Addresses 32 to 63 are used in four modes as determined by the page select control bits in the status register. Page zero is the frequency, phase and gain settings for the four channels. Page one is for monitoring status and test points. Pages two and three are used to store the coefficients for the programmable interpolate by two filter.

The Page zero register assignments are:

| ADDRESSES   | NAME                | ADDRESSES   | NAME                |

|-------------|---------------------|-------------|---------------------|

| 32,33,34,35 | Channel A Frequency | 48,49,50,51 | Channel C Frequency |

| 36,37       | Channel A Phase     | 52,53       | Channel C Phase     |

| 38          | Channel A Gain      | 54          | Channel C Gain      |

| 39          | unused              | 55          | unused              |

| 40,41,42,43 | Channel B Frequency | 56,57,58,59 | Channel D Frequency |

| 44,45       | Channel B Phase     | 60,61       | Channel D Phase     |

| 46          | Channel B Gain      | 62          | Channel D Gain      |

| 47          | unused              | 63          | unused              |

The 32 fir filter coefficients are stored as two bytes per 16 bit word in 2's complement format. The least significant 8 bits in the lower byte and the most significant 8 bits in the upper byte. Page two stores coefficients 0 through 15 in addresses 32 to 63. Page three stores coefficients 16 to 31. Coefficient 31 is the center tap. The lower byte of the coefficient must be loaded and then the upper byte.

The following sections describe each of these registers. The type of each register bit is either R, W, or R/W indicating whether the bit is read only, write only, or read/write. All bits are active high.

| Texas Instruments Inc. | - 14 - | MAY 22, 2 |

|------------------------|--------|-----------|

|                        |        |           |

# DATA SHEET REV 1.0

## 5.1 SYNC MODE REGISTER

The Sync mode control register determines how the circuits within the chip are synchronized. Each circuit which requires synchronization can be configured to be synchronized to the sync input **(SI)**, or to the terminal count of the sync counter **(TC)**. The sync to each circuit can also be set to be always on or always off. Each circuit is given a two bit sync mode control which is defined as:

| MODE | SYNC DESCRIPTION                  |

|------|-----------------------------------|

| 0    | "0" (never asserted)              |

| 1    | SI                                |

| 2    | TC (or OS, if USE_ONESHOT is set) |

| 3    | "1" (always)                      |

| Table | 1: Syn | c Modes |

|-------|--------|---------|

|-------|--------|---------|

NOTE: the internal syncs are active high. The **SI** input has been inverted to be the active high sync **SI**.

| BIT        | TYPE | NAME         | DESCRIPTION                                                                                                                              |

|------------|------|--------------|------------------------------------------------------------------------------------------------------------------------------------------|

| 0,1 (LSBs) | R/W  | INT_SYNC     | Synchronizes the interpolation control counter. The interpolation counter controls the filtering of each channel.                        |

| 2,3        | R/W  | COUNTER_SYNC | Synchronizes the sync counter. This counter is used to generate the periodic "TC" sync pulses. Mode 2 is OS, not TC, for the counter.    |

| 4,5        | R/W  | OUTPUT_SYNC  | The selected sync is inverted and output on the $\overline{\textbf{SO}}$ pin.                                                            |

| 6          | R/W  | USE_ONESHOT  | The terminal count mode in Table 1 is replaced by the one shot pulse (OS) when this bit is set.                                          |

| 7          | R/W  | ONE_SHOT     | The one shot sync pulse (OS) is generated when this bit is set. This bit must be cleared before another one shot pulse can be generated. |

#### **ADDRESS 0:** Sync Mode, suggested default = 0x65

If the user wishes to allow the chip to free run, asynchronous to other chips, then the sync settings can be set to zero. If one wishes to synchronize several chips to a single sync source, then the sync mode selections should be set to one. The suggested default is to output the one-shot (USE\_ONESHOT = 1, OUTPUT\_SYNC=2) and all other syncs to SI. The user should tie the  $\overline{SO}$  output pin of one GC4114 chip to the  $\overline{SI}$  input pin of all other GC4114 chips in a system in order to cleanly synchronize and initialize one or more GC4114 chips. If there is only a single GC4114 chip, then all sync mode selections can be set to "2" to receive the one-shot directly. A one-shot should be sent after initialization and each time the interpolation ratio is changed.

# **DATA SHEET REV 1.0**

# 5.2 INTERPOLATION MODE REGISTER

Registers 1 and 2 control the interpolation modes for the chip. These settings are common to all channels

#### **ADDRESS 1:** Interpolation Mode, suggested default = 0x00

| <u>BIT</u> | <u>TYPE</u> | NAME          | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------|-------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0 LSB      | R/W         | REAL          | The input samples are real when this bit is set and are up-converted as a single sideband signal. The input samples are treated as complex when this bit is low. The input rate is $F_{CK}/4N$ when this bit is low and is $F_{CK}/2N$ when this bit is high, where $F_{CK}$ is the chip's clock rate and N is the interpolation setting in registers 3 and 4 (See Section 5.4). If double sideband real data is to be up-converted, then the complex mode should be used with the Q-half set to zero. |

| 1          | R/W         | FILTER_SELECT | The user downloaded filter coefficients are used instead of the built in filter coefficients for the PFIR filter when this bit is set. This bit must be cleared for at least 4N clock cycles before it is set.                                                                                                                                                                                                                                                                                         |

| 2          | R/W         | REQ_POL       | This control bit inverts the polarity of the <b>REQ</b> output. Normally <b>REQ</b> pulses high when a new sample is requested. <b>REQ</b> will pulse low when REQ_POL is high.                                                                                                                                                                                                                                                                                                                        |

| 3          | R/W         | REQ_WIDTH     | Normally the <b>REQ</b> pin will pulse high for two clock cycles. This control bit forces <b>REQ</b> to be high for "N/2" clocks. NOTE: the period of the <b>REQ</b> signal is either 4N or 2N clocks, depending upon whether the REAL_INPUT control bit is low or high in the input mode control register (See Section 5.5).                                                                                                                                                                          |

| 4          | R/W         | DIAG          | Use the diagnostic ramp as the input source for the four channels. The ramp starts at -32768 and counts up to +32768 and starts over again. The ramp increments once every complex input cycle (every 4N clocks).                                                                                                                                                                                                                                                                                      |

| 5          | R/W         | SO_OVF_MODE   | When set, the SO bit will go low whenever an overflow occurs in the chip. Bits 6 & 7 of control register 32 of page 1 must be low to use this mode (see Section 5.14).                                                                                                                                                                                                                                                                                                                                 |

| 6,7        | R/W         | DIAG_SYNC     | The diagnostic ramp is synchronized by the sync selected by these bits according to Table 1. This sync also loads the checksum register.                                                                                                                                                                                                                                                                                                                                                               |

#### 5.3 INTERPOLATION GAIN REGISTER

Register 2 controls the interpolation gain for the chip. These settings are common to all channels

#### **ADDRESS 2:** Interpolation Gain, suggested default = 0x46

| <u>BIT</u> | <u>TYPE</u> | NAME       | DESCRIPTION                                                                                                             |

|------------|-------------|------------|-------------------------------------------------------------------------------------------------------------------------|

| 0-3        | R/W         | SCALE      | SCALE ranges from 0 to 15.                                                                                              |

| 4,5        | R/W         | BIG_SHIFT  | BIG_SHIFT equals 0, 1 or 2.                                                                                             |

| 6          | R/W         | AUTO_FLUSH | The chip will automatically flush a channel if instability in the channel's CIC filter is detected and this bit is set. |

| 7          | R/W         | MSB_INVERT | Inverts the MSB of the output data (OUT15) for use with offset binary DACs.                                             |

The CIC filter has a gain which is equal to N<sup>3</sup>. To remove this gain the CIC outputs are shifted down by  $(3+SCALE+12*BIG\_SHIFT)$  bits and then rounded to 16 bits before they are sent to the mixer circuit. The value chosen for BIG\\_SHIFT must also satisfy:  $2^{(12*BIG\_SHIFT+18)} \ge N^3$ . Overflows due to improper gain settings will go undetected if this relationship is violated. This restriction means that BIG\_SHIFT = 0 for N between 8 and 64, BIG\_SHIFT = 1 for N between 65 and 1024, and BIG\_SHIFT = 2 for N between 1025 and 16384.

# **DATA SHEET REV 1.0**

#### 5.4 INTERPOLATION REGISTERS

Registers 3, and 4 contain the 14 bit interpolation ratio control.

| ADDRESS 3: | Interpolation | on Byte 0, suggested | default = 0x07                                               |

|------------|---------------|----------------------|--------------------------------------------------------------|

| BIT        | <u>TYPE</u>   | NAME                 | DESCRIPTION                                                  |

| 0-7        | R/W           | <b>INT</b> [0:7]     | The LSBs of the interpolation control                        |

| ADDRESS 4: | Interpolation | on Byte 1, suggested | default = 0x00                                               |

| BIT        | <u>TYPE</u>   | NAME                 | DESCRIPTION                                                  |

| 0-5<br>6,7 | R/W<br>R      | INT[8:13]<br>zero    | The 6 MSBs of the interpolation control<br>Reads back zeros. |

| -          |               |                      |                                                              |

Where **INT** is equal to **N**-1. The chip interpolates the input data by a factor of 2N for real input data and 4N for complex input data, where N ranges from 8 to 16384. This provides an interpolation range from 32 to 65,536 for complex input signals and 16 to 32,768 for real input signals. **NOTE: The chip needs to be flushed each time the interpolation registers are changed.** See Section 5.8.

#### 5.5 INPUT MODE REGISTER

This register controls the input bit serial format.

#### **ADDRESS 5:** Input Mode Register, suggested default = 0x00

| BIT   | <u>TYPE</u> | NAME       | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------|-------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0 LSB | R/W         | PACKED     | Puts the serial inputs into the 32 bit transfer mode where each complex pair is packed into 32 bit words. The complex pair is formatted as I word in the upper 16 bits and the Q word in the lower 16 bits. Each word is formatted as MSB first.                                                                                                                                                                                                                                                                                                                                 |

| 1     | R/W         | REAL_INPUT | The serial input accepts real data samples (not complex) when this bit is set. In this mode a single 16 bit word is expected after every <b>REQ</b> strobe, not a complex pair. The user has the option to enter real input samples as complex pairs and to not use the real input mode. If the complex mode (REAL_INPUT = 0) is used to enter real words, then the real samples should be alternately placed in the I and Q halves of the complex input pairs. NOTE: the REAL control bit in the interpolation mode register still needs set to enable real data up conversion. |

| 2     | R/W         | SCK_POL    | The <b>SIN</b> Input bits and <b>SFS</b> frame strobes are clocked in on the trailing edge of SCK when this bit is set. The rising edge is used when this bit is low.                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3     | R/W         | SFS_POL    | The <b>SFS</b> signal is treated as active low when this bit is set. Otherwise the signal is treated as active high.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 4     | R/W         | PARALLEL_A | The parallel/Serial control for channel A.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5     | R/W         | PARALLEL_B | The parallel/Serial control for channel B.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 6     | R/W         | PARALLEL_C | The parallel/Serial control for channel C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 7     | R/W         | PARALLEL_D | The parallel/Serial control for channel D.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

The parallel/serial control is low for serial input and high for parallel input. See Section 5.12.

Texas Instruments Inc.

- 17 -

MAY 22, 2000

#### **DATA SHEET REV 1.0**

#### 5.6 COUNTER MODE REGISTER

Registers 6, and 7 set the counter's cycle period.

| ADDRESS 6: | <b>Counter Byte 0</b> , suggested default = 0xff |

|------------|--------------------------------------------------|

|------------|--------------------------------------------------|

| <u>BIT</u> | TYPE | NAME             | DESCRIPTION                          |

|------------|------|------------------|--------------------------------------|

| 0-7        | R/W  | <b>CNT</b> [0:7] | The LSBs of the counter cycle period |

**ADDRESS 7: Counter Byte 1**, suggested default = 0xff

| 0-7 R/W | CNT | [8:15] T | The 8 MSBs of the counter cycle period |

|---------|-----|----------|----------------------------------------|

The chip's internal sync counter counts in cycles of 128(CNT+1) clocks. A terminal count signal (TC) is output at the end of each cycle. The counter can be synchronized to an external sync as specified in the Sync mode Register (See Section 5.1). If CNT is set so that 128(CNT+1) is a multiple of twice the interpolation ratio (i.e., a multiple of 16N), then the terminal count of this counter can be output on the  $\overline{SO}$  pin and used to periodically synchronize multiple GC4114 chips.

#### 5.7 CHANNEL SYNC REGISTERS

Registers 8,9,10 and 11 control the synchronization modes of the four channels. The sync modes described here are unique to each of the channels. The modes use the same settings as shown in Table 1 (See Section 5.1).

| ADDRESS    | 8: Chan  | nel-A Sync Modes, sug | gested default = 0x5f                                    |

|------------|----------|-----------------------|----------------------------------------------------------|

| ADDRESS    | 9: Chan  | nel-B Sync Modes      |                                                          |