捷多邦,专业PCB打样工厂,24小时加急出作D-6408

Data Sheet

March 7, 2006

```

FN2952.2

```

#### CMOS Asynchronous Serial Manchester Adapter (ASMA)

The HD-6408 is a CMOS/LSI Manchester Encoder/Decoder for creating a very high speed asynchronous serial data bus. The Encoder converts serial NRZ data (typically from a shift register) to Manchester II encoded data, adding a sync pulse and parity bit. The Decoder recognizes this sync pulse and identifies it as a Command Sync or a Data Sync. The data is then decoded and shifted out in NRZ code (typically into a shift register). Finally, the parity bit is checked. If there were no Manchester or parity errors the Decoder responds with a valid word signal. The Decoder puts the Manchester code to full use to provide clock recovery and excellent noise immunity at these very high speeds.

The HD-6408 can be used in many commercial applications such as security systems, environmental control systems, serial data links and many others. It utilizes a single 12 x clock and achieves data rates of up to one million bits per second with a very minimum overhead of only 4 bits out of 20, leaving 16 bits for data.

### Pinout

#### Features

- Low Bit Error Rate

- Sync Identification and Lock-In

- Clock Recovery

- Manchester II Encoder, Decoder

- Separate Encode and Decode

- Single Power Supply

- 24 Ld Package

- Pb-Free Plus Anneal Available (RoHS Compliant)

## **Ordering Information**

| PART<br>NUMBER        | PART<br>MARKING | TEMP.<br>RANGE<br>(°C) | PACKAGE                  | PKG.<br>NO. |

|-----------------------|-----------------|------------------------|--------------------------|-------------|

| HD3-6408-9            | HD3-6408-9      | -40 to +85             | 24 Ld PDIP               | E24.6       |

| HD3-6408-9Z<br>(Note) | HD3-6408-9Z     | -40 to +85             | 24 Ld PDIP*<br>(Pb-Free) | E24.6       |

| HD1-6408-9            | HD1-6408-9      | -40 to +85             | 24 Ld CERDIP             | F24.6       |

NOTE: Intersil Pb-free plus anneal products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate termination finish, which are RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

\*Pb-free PDIPs can be used for through hole wave solder processing only. They are not intended for use in Reflow solder processing applications.

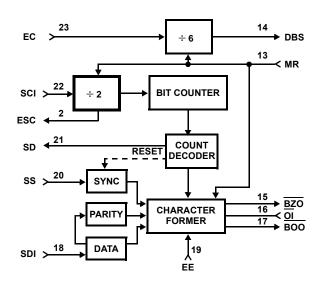

### **Block Diagrams**

ENCODER

# **Pin Description**

| PIN | TYPE | SYMBOL          | SECTION | DESCRIPTION                                                                                                                                                                          |

|-----|------|-----------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | 0    | VW              | Decoder | Output high indicates receipt of a VALID WORD.                                                                                                                                       |

| 2   | 0    | ESC             | Encoder | ENCODER SHIFT CLOCK is an output for shifting data into the Encoder. The Encoder samples SDI on the low-to-high transition of ESC.                                                   |

| 3   | 0    | TD              | Decoder | TAKE DATA output is high during receipt of data after identification of a sync pulse<br>and two valid Manchester data bits.                                                          |

| 4   | 0    | SDO             | Decoder | SERIAL DATA OUT delivers received data in correct NRZ format.                                                                                                                        |

| 5   | Ι    | DC              | Decoder | DECODER CLOCK input drives the transition finder, and the synchronizer which in turn supplies the clock to the balance of the Decoder. Input a frequency equal to 12X the data rate. |

| 6   | I    | BZI             | Decoder | A high input should be applied to BIPOLAR ZERO IN when the bus is in its negative state. This pin must be held high when the Unipolar input is used.                                 |

| 7   | I    | BOI             | Decoder | A high input should be applied to BIPOLAR ONE IN when the bus is in its positive state, this pin must be held low when the Unipolar input is used.                                   |

| 8   | I    | UDI             | Decoder | With pin 6 high and pin 7 low, this pin enters UNIPOLAR DATA IN to the transition finder circuit. If not used this input must be held low.                                           |

| 9   | 0    | DSC             | Decoder | DECODER SHIFT CLOCK output delivers a frequency (DECODER CLOCK <sup>3</sup> ÷ 12), synchronized by the recovered serial data stream.                                                 |

| 10  | 0    | CDS             | Decoder | COMMAND/DATA SYNC output high occurs during output of decoded data which was preceded by a Command synchronizing character. A low output indicates a Data synchronizing character.   |

| 11  | I    | DR              | Decoder | A high input to DECODER RESET during a rising edge of DECODER SHIFT CLOCK resets the decoder bit counting logic to a condition ready for a new word.                                 |

| 12  | I    | GND             | Both    | GROUND supply pin.                                                                                                                                                                   |

| 13  | I    | MR              | Both    | A high on MASTER RESET clears the 2:1 counters in both the encoder and decoder and the $^3$ $\div$ 6 counter.                                                                        |

| 14  | 0    | DBS             | Encoder | DIVIDE BY SIX is an output from 6:1 divider which is driven by the ENCODER CLOCK.                                                                                                    |

| 15  | 0    | BZO             | Encoder | BIPOLAR ZERO OUT is a active low output designed to drive the zero or negative sense of a bipolar line driver.                                                                       |

| 16  | I    | OI              | Encoder | A low on OUTPUT INHIBIT forces pin 15 and 17 high, their inactive states.                                                                                                            |

| 17  | 0    | BOO             | Encoder | BIPOLAR ONE OUT is an active low output designed to drive the one or positive sense of a bipolar line driver.                                                                        |

| 18  | I    | SDI             | Encoder | SERIAL DATA IN accepts a serial data stream at a data rate equal to ENCODER SHIFT CLOCK.                                                                                             |

| 19  | I    | EE              | Encoder | A high on ENCODER ENABLE initiates the encode cycle. (Subject to the preceding cycle being completed).                                                                               |

| 20  | I    | SS              | Encoder | SYNC SELECT actuates a Command sync for an input high and data sync for an input low.                                                                                                |

| 21  | 0    | SD              | Encoder | SEND DATA is an active high output which enables the external source of serial data.                                                                                                 |

| 22  | I    | SCI             | Encoder | SEND CLOCK IN is 2X the Encoder data rate.                                                                                                                                           |

| 23  | I    | EC              | Encoder | ENCODER CLOCK is the input to the 6:1 divider.                                                                                                                                       |

| 24  | I    | V <sub>CC</sub> | Both    | $V_{CC}$ is the +5V power supply pin. A 0.1µF decoupling capacitor from $V_{CC}$ (pin 24) to GND (pin 12) is recommended.                                                            |

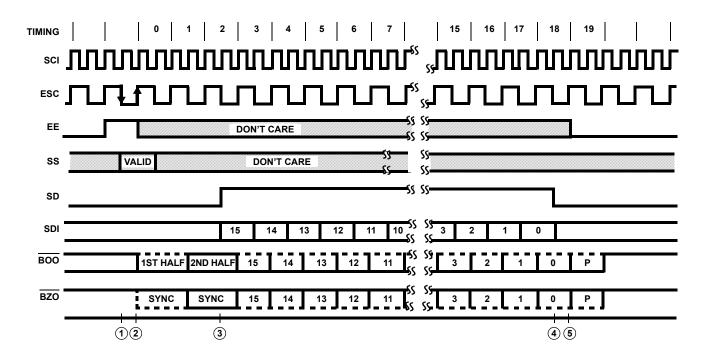

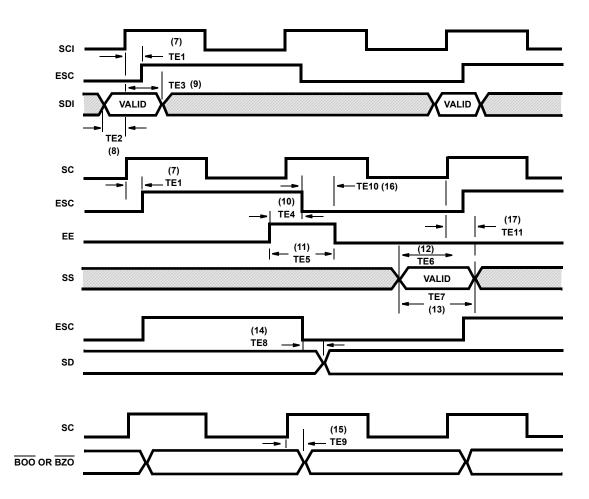

### **Encoder Operation**

The Encoder requires a single clock with a frequency of twice the desired data rate applied at the SClock input. An auxiliary divide by six counter is provided on chip which can be utilized to produce the SClock by dividing the DClock.

The Encoder's cycle begins when EE is high during a falling edge of ESC (1). This cycle lasts for one word length or twenty ESC periods. At the next low-to-high transition of the ESC, a high at SS input actuates a Command sync or a low will produce a Data sync for that word (2). When the Encoder is ready to accept data, the SD output will go high and remain high for sixteen ESC periods (3) - (4).

During these sixteen periods the data should be clocked into the SD Input with every high-to-low transition of the ESC (3) - (4). After the sync and Manchester II encoded data are transmitted through the BOO and BZO outputs, the Encoder adds on an additional bit which is the (odd) parity for that word (5). If ENCODER ENABLE is held high continuously, consecutive words will be encoded without an interframe gap. ENCODER ENABLE must go low by time (5) as shown to prevent a consecutive word from being encoded. At any time a low on OI will force both bipolar outputs to a high state but will not affect the Encoder in any other way.

To Abort the Encoder transmission a positive pulse must be applied at MR. Any time after or during this pulse, a low-tohigh transition on SCI clears the internal counters and initializes the Encoder for a new word.

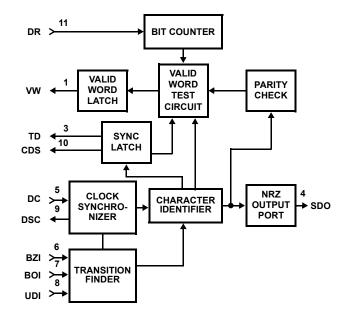

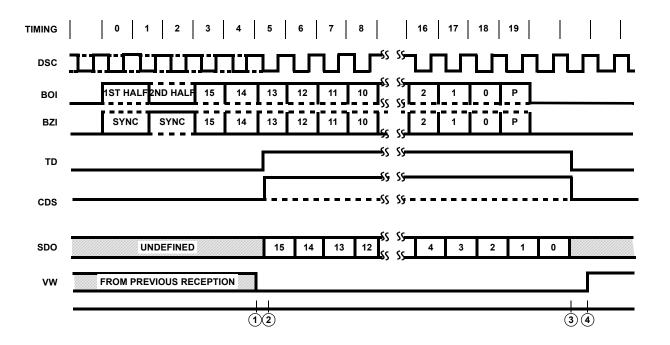

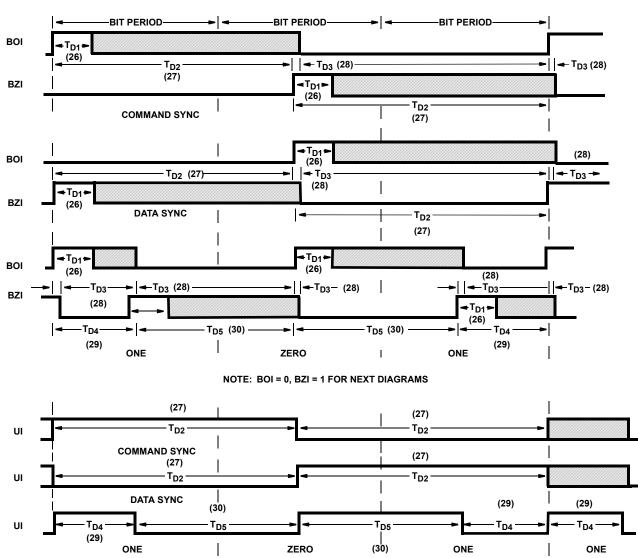

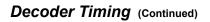

### **Decoder Operation**

The Decoder requires a single clock with a frequency of 12 times the desired data rate applied at the DClock input. The Manchester II coded data can be presented to the Decoder in one of two ways. The BOI and BZI inputs will accept data from a differential output comparator. The UDI input can only accept noninverted Manchester II coded data (e.g. from BOO of an Encoder through an inverter to UDI).

The Decoder is free running and continuously monitors its data input lines for a valid sync character and two valid Manchester data bits to start an output cycle. When a valid sync is recognized (1), the type of sync is indicated by the CDS output. If the sync character was a command, this output will go high (2) and remain high for sixteen DSC periods (3), otherwise it will remain low. The TD output will go high and remain high (2) - (3) while the Decoder is transmitting the decoded data through SDO.

The decoded data available at SDO is in a NRZ format. The DSC is provided so that the decoded bits can be shifted into an external register on every low-to-high transition of this clock (2) - (3). Note that DECODER SHIFT CLOCK may adjust its phase up until the time that TAKE DATA goes high.

After all sixteen decoded bits have been transmitted (3) the data is checked for odd parity. A high on VW output (4) indicates a successful reception of a word without any Manchester or parity errors. At this time the Decoder is looking for a new sync character to start another output sequence. VALID WORD will go low approximately 20 DECODER SHIFT CLOCK periods after it goes high if not reset low sooner by a valid sync and two valid Manchester bits as shown (1).

At any time in the above sequence a high input on DR during a low-to-high transition of DSC will abort transmission and initialize the Decoder to start looking for a new sync character.

#### **Absolute Maximum Ratings**

| Supply Voltage<br>Input, Output or I/O Voltage<br>Gate Count | GND -0.3V to V_CC +0.3V |

|--------------------------------------------------------------|-------------------------|

| ESD Classification                                           |                         |

| Operating Conditions                                         |                         |

| Operating Voltage Range     | +4.5V to +5.5V |

|-----------------------------|----------------|

| Operating Temperature Range |                |

| HD-6408-9                   | 40°C to +85°C  |

#### **Thermal Information**

| Thermal Resistance (Typical)           | $\theta_{JA}$ (°C/W) | θ <sub>JC</sub> (°C/W) |

|----------------------------------------|----------------------|------------------------|

| CERDIP Package                         | 50                   | 11                     |

| PDIP Package*                          | 60                   | N/A                    |

| Storage Temperature Range              | 65'                  | °C to +150°C           |

| Junction Temperature                   |                      | +175°C                 |

| Lead Temperature (Soldering 10s)       |                      | +300°C                 |

| *Pb-free PDIPs can be used for thr     | ough hole            | wave solder            |

| processing only. They are not intended | for use in R         | eflow solder           |

| processing applications.               |                      |                        |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### DC Electrical Specifications $V_{CC} = 5.0V \pm 10\%$ , T<sub>A</sub> = -40°C to +85°C

| SYMBOL           | PARAMETER                         | TEST CONDITIONS                                                                           | MIN                  | TYP                 | MAX  | UNITS |

|------------------|-----------------------------------|-------------------------------------------------------------------------------------------|----------------------|---------------------|------|-------|

| V <sub>IH</sub>  | Logical "1" Input Voltage         |                                                                                           | 70% V <sub>CC</sub>  | -                   | -    | V     |

| VIL              | Logical "0" Input Voltage         |                                                                                           | -                    | 20% V <sub>CC</sub> | -    | V     |

| VIHC             | Logical "1" Input Voltage (Clock) |                                                                                           | V <sub>CC</sub> -0.5 | -                   | -    | V     |

| V <sub>ILC</sub> | Logical "0" Input Voltage (Clock) |                                                                                           | -                    | GND +0.5            | -    | V     |

| II               | Input Leakage                     | V <sub>IN</sub> = V <sub>CC</sub> or GND, DIP Pins<br>5-8, 11, 13, 16, 18, 19, 20, 22, 23 | -1.0                 | -                   | +1.0 | μA    |

| V <sub>OH</sub>  | Logical "1" Output Voltage        | I <sub>OH</sub> = -3mA                                                                    | 2.4                  | -                   | -    | V     |

| V <sub>OL</sub>  | Logical "0" Output Voltage        | I <sub>OL</sub> = 1.8mA                                                                   | -                    | -                   | 0.4  | V     |

| ICCSB            | Supply Current Standby            | V <sub>IN</sub> = V <sub>CC</sub> = 5.5V Outputs Open                                     | -                    | 0.5                 | 2    | mA    |

| ICCOP            | Supply Current Operating (Note 1) | V <sub>CC</sub> = 5.5V, f = 15MHz                                                         | -                    | 8.0                 | 10.0 | mA    |

NOTE:

1. Guaranteed but not 100% tested.

#### AC Electrical Specifications $V_{CC} = 5.0V \pm 10\%$ , T<sub>A</sub> = -40°C to +85°C

| SY   | MBOL             | PARAMETER                | TEST CONDITIONS       | MIN | ТҮР | MAX | UNITS |  |  |

|------|------------------|--------------------------|-----------------------|-----|-----|-----|-------|--|--|

| ENCO | ENCODER TIMING   |                          |                       |     |     |     |       |  |  |

| (1)  | F <sub>EC</sub>  | Encoder Clock Frequency  | C <sub>L</sub> = 50pF | 0   | -   | 12  | MHz   |  |  |

| (2)  | F <sub>ESC</sub> | Send Clock Frequency     | C <sub>L</sub> = 50pF | 0   | -   | 2.0 | MHz   |  |  |

| (3)  | T <sub>ECR</sub> | Encoder Clock Rise Time  | C <sub>L</sub> = 50pF | -   | -   | 8   | ns    |  |  |

| (4)  | T <sub>ECF</sub> | Encoder Clock Fall Time  | C <sub>L</sub> = 50pF | -   | -   | 8   | ns    |  |  |

| (5)  | F <sub>ED</sub>  | Data Rate                | C <sub>L</sub> = 50pF | 0   | -   | 1.0 | MHz   |  |  |

| (6)  | T <sub>MR</sub>  | Master Reset Pulse Width | C <sub>L</sub> = 50pF | 150 | -   | -   | ns    |  |  |

| (7)  | T <sub>E1</sub>  | Shift Clock Delay        | C <sub>L</sub> = 50pF | -   | -   | 125 | ns    |  |  |

| (8)  | T <sub>E2</sub>  | Serial Data Setup        | C <sub>L</sub> = 50pF | 75  | -   | -   | ns    |  |  |

| (9)  | T <sub>E3</sub>  | Serial Data Hold         | C <sub>L</sub> = 50pF | 75  | -   | -   | ns    |  |  |

| (10) | T <sub>E4</sub>  | Enable Setup             | C <sub>L</sub> = 50pF | 90  | -   | -   | ns    |  |  |

| (11) | T <sub>E5</sub>  | Enable Pulse Width       | C <sub>L</sub> = 50pF | 100 | -   | -   | ns    |  |  |

| (12) | T <sub>E6</sub>  | Sync Setup               | C <sub>L</sub> = 50pF | 55  | -   | -   | ns    |  |  |

| (13) | T <sub>E7</sub>  | Sync Pulse Width         | C <sub>L</sub> = 50pF | 150 | -   | -   | ns    |  |  |

| (14) | T <sub>E8</sub>  | Send Data Delay          | C <sub>L</sub> = 50pF | 0   | -   | 50  | ns    |  |  |

| (15) | T <sub>E9</sub>  | Bipolar Output Delay     | C <sub>L</sub> = 50pF | -   | -   | 130 | ns    |  |  |

c

### HD-6408

| SY   | MBOL             | PARAMETER                  | TEST CONDITIONS               | MIN                 | TYP               | MAX                 | UNITS |

|------|------------------|----------------------------|-------------------------------|---------------------|-------------------|---------------------|-------|

| (16) | T <sub>E10</sub> | Enable Hold                | C <sub>L</sub> = 50pF         | 10                  | -                 | -                   | ns    |

| (17) | T <sub>E11</sub> | Sync Hold                  | C <sub>L</sub> = 50pF         | 95                  | -                 | -                   | ns    |

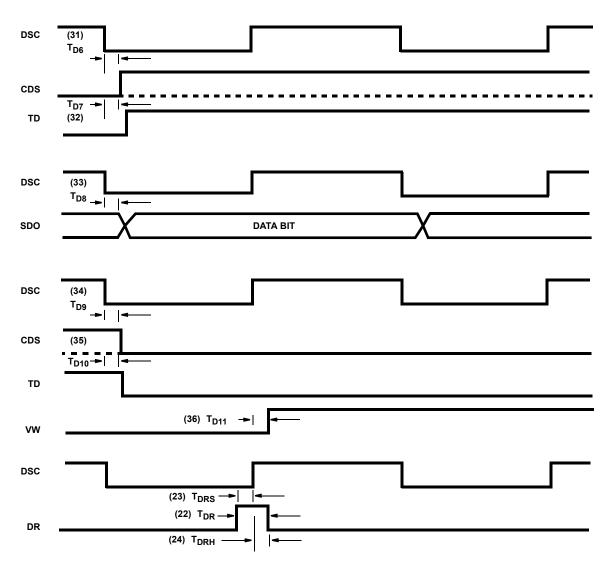

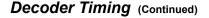

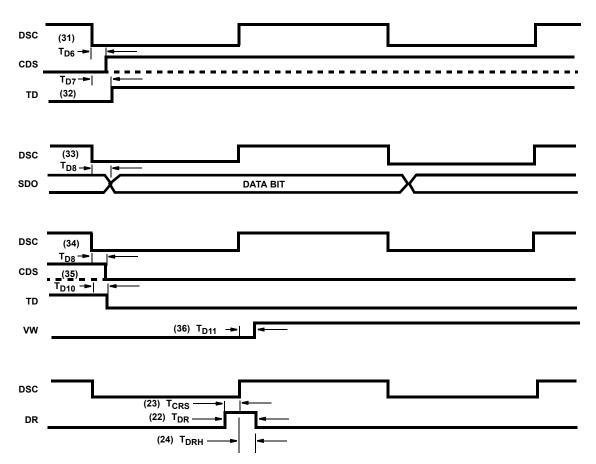

| DECO |                  | /ING                       |                               | I                   |                   |                     |       |

| (18) | F <sub>DC</sub>  | Decoder Clock Frequency    | C <sub>L</sub> = 50pF         | 0                   | -                 | 12                  | MHz   |

| (19) | T <sub>DCR</sub> | Decoder Clock Rise Time    | C <sub>L</sub> = 50pF         | -                   | -                 | 8                   | ns    |

| (20) | T <sub>DCF</sub> | Decoder Clock Fall Time    | C <sub>L</sub> = 50pF         | -                   | -                 | 8                   | ns    |

| (21) | F <sub>DD</sub>  | Data Rate                  | C <sub>L</sub> = 50pF         | 0                   | -                 | 1.0                 | MHz   |

| (22) | T <sub>DR</sub>  | Decoder Reset Pulse Width  | C <sub>L</sub> = 50pF         | 150                 | -                 | -                   | ns    |

| (23) | T <sub>DRS</sub> | Decoder Reset Setup Time   | C <sub>L</sub> = 50pF         | 75                  | -                 | -                   | ns    |

| (24) | T <sub>DRH</sub> | Decoder Reset Hold Time    | C <sub>L</sub> = 50pF         | 10                  | -                 | -                   | ns    |

| (25) | T <sub>MR</sub>  | Master Reset Pulse Width   | C <sub>L</sub> = 50pF         | 150                 | -                 | -                   | ns    |

| (26) | T <sub>D1</sub>  | Bipolar Data Pulse Width   | Note 2, C <sub>L</sub> = 50pF | T <sub>DC</sub> +10 | -                 | -                   | ns    |

| (27) | T <sub>D2</sub>  | Sync Transition Span       | Note 2, C <sub>L</sub> = 50pF | -                   | 18T <sub>DC</sub> | -                   | ns    |

| (28) | T <sub>D3</sub>  | One Zero Overlap           | Note 2, C <sub>L</sub> = 50pF | -                   | -                 | T <sub>DC</sub> -10 | ns    |

| (29) | T <sub>D4</sub>  | Short Data Transition Span | Note 2, C <sub>L</sub> = 50pF | -                   | 6T <sub>DC</sub>  | -                   | ns    |

| (30) | T <sub>D5</sub>  | Long Data Transition Span  | Note 2, C <sub>L</sub> = 50pF | -                   | 12T <sub>DC</sub> | -                   | ns    |

| (31) | T <sub>D6</sub>  | Sync Delay (ON)            | C <sub>L</sub> = 50pF         | -20                 | -                 | 110                 | ns    |

| (32) | T <sub>D7</sub>  | Take Data Delay (ON)       | C <sub>L</sub> = 50pF         | 0                   | -                 | 110                 | ns    |

| (33) | T <sub>D8</sub>  | Serial Data Out Delay      | C <sub>L</sub> = 50pF         | -                   | -                 | 80                  | ns    |

| (34) | T <sub>D9</sub>  | Sync Delay (OFF)           | C <sub>L</sub> = 50pF         | 0                   | -                 | 110                 | ns    |

| (35) | T <sub>D10</sub> | Take Data Delay (OFF)      | C <sub>L</sub> = 50pF         | 0                   | -                 | 110                 | ns    |

| (36) | T <sub>D11</sub> | Valid Word Delay           | C <sub>L</sub> = 50pF         | 0                   | -                 | 110                 | ns    |

#### AC Electrical Specifications $V_{CC} = 5.0V \pm 10\%$ , T<sub>A</sub> = -40°C to +85°C (Continued)

NOTE:

2.  $T_{DC}$  = Decoder Clock Period =  $^{1}/F_{DC}$ . (These parameters are guaranteed but not 100% tested).

## **Capacitance** T<sub>A</sub> = +25°C

| SYMBOL          | PARAMETER          | TEST CONDITIONS                                               | MIN | ТҮР | MAX | UNITS |

|-----------------|--------------------|---------------------------------------------------------------|-----|-----|-----|-------|

| C <sub>IN</sub> | Input Capacitance  | FREQ = 1MHz, all measurements<br>are referenced to device GND | -   | 15  | -   | pF    |

| CO              | Output Capacitance |                                                               | -   | 15  | -   | pF    |

## AC Testing Input, Output Waveform

NOTE: AC Testing: All input signals must switch between V<sub>IL</sub> and V<sub>IH</sub>. Input rise and fall times are driven at 1ns per volt.

# Encoder Timing

### HD-6408

## **Decoder Timing**

NOTE: UI = 0, FOR NEXT DIAGRAMS

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com