# HX6256

## 32K x 8 Static RAM

The 32K x 8 Radiation Hardened Static RAM is a high performance 32,768 word x 8-bit static random access memory with industry-standard functionality. It is fabricated with Honeywell's radiation hardened technology, and is designed for use in systems operating in radiation environments. The RAM operates over the full military temperature range and requires only a single 5 V  $\pm$  10% power supply. The RAM is available with either TTL or CMOS compatible I/O. Power consumption is typically less than 15 mW/MHz in operation, and less than 5 mW when de-selected. The RAM read operation is fully asynchronous, with an associated typical access time of 17 ns at 5 V.

Honeywell's enhanced SOI RICMOS™ IV (Radiation Insensitive CMOS) technology is radiation hardened through the use of advanced and proprietary design, layout, and process hardening techniques. The RICMOS™ IV process is a 5-volt, SOI CMOS technology with a 150 Å gate oxide and a minimum drawn feature size of 0.75  $\mu$ m (0.6  $\mu$ m effective gate length— $L_{eff}$ ). Additional features include tungsten via plugs, Honeywell's proprietary SHARP planarization process, and a lightly doped drain (LDD) structure for improved short channel reliability. A 7 transistor (7T) memory cell is used for superior single event upset hardening, while three layer metal power bussing and the low collection volume SOI substrate provide improved dose rate hardening.

## FEATURES

### RADIATION

- Fabricated with RICMOS™ IV Silicon on Insulator (SOI) 0.7  $\mu$ m Process ( $L_{eff}$  = 0.6  $\mu$ m)

- Total Dose Hardness through  $1 \times 10^6$  rad(SiO<sub>2</sub>)

- Neutron Hardness through  $1 \times 10^{14}$  cm<sup>-2</sup>

- Dynamic and Static Transient Upset Hardness through  $1 \times 10^9$  rad(Si)/s

- Dose Rate Survivability through  $1 \times 10^{11}$  rad(Si)/s

- Soft Error Rate of  $< 1 \times 10^{-10}$  upsets/bit-day in Geosynchronous Orbit

### OTHER

- Listed On SMD#5962-95845

- Fast Cycle Times

- $\leq 17$  ns (Typical)

- $\leq 25$  ns (-55 to 125°C) Read Write Cycle

- Asynchronous Operation

- CMOS or TTL Compatible I/O

- Single 5 V  $\pm$  10% Power Supply

- Packaging Options

- 28-Lead CFP (0.500 in. x 0.720 in.)

- 28-Lead DIP, MIL-STD-1835, CDIP2-T28

- 36-Lead CFP—Bottom Braze (0.630 x 0.650 in.)

- 36-Lead CFP—Top Braze (0.630 x 0.650 in.)

# HX6256

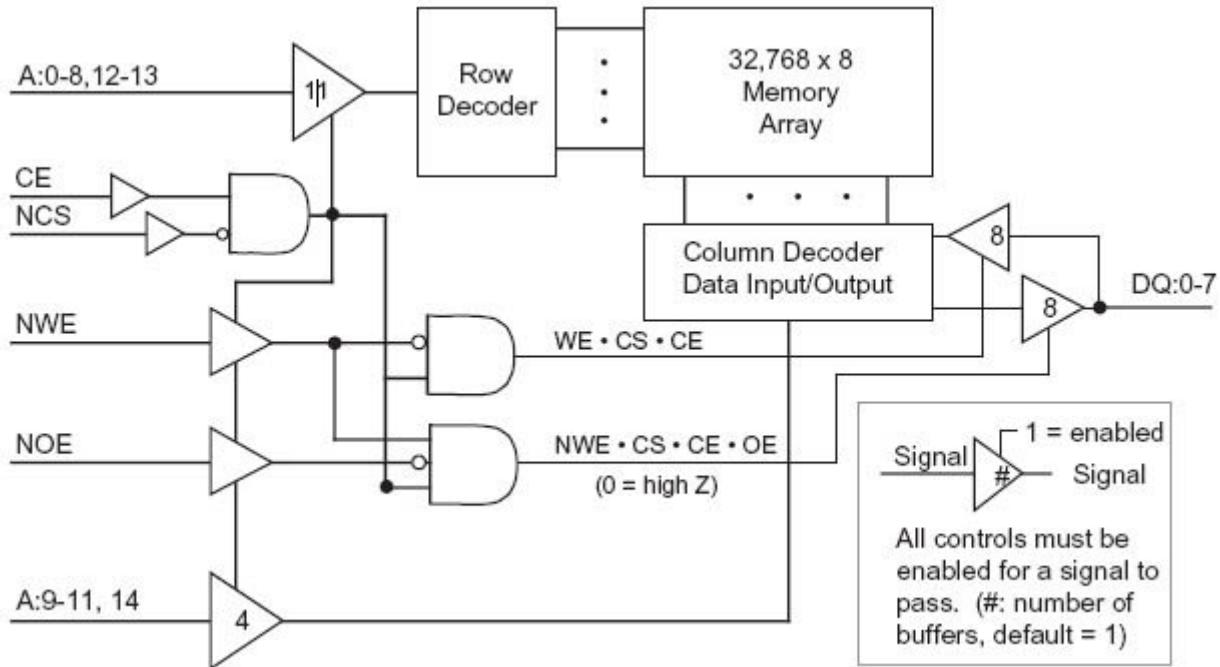

## FUNCTIONAL DIAGRAM

## SIGNAL DEFINITIONS

A: 0-14 Address input pins which select a particular eight-bit word within the memory array.

DQ: 0-7 Bidirectional data pins which serve as data outputs during a read operation and as data inputs during a write operation.

NCS Negative chip select, when at a low level allows normal read or write operation. When at a high level NCS forces the SRAM to a precharge condition, holds the data output drivers in a high impedance state and disables all input buffers except CE. If this signal is not used it must be connected to VSS.

NWE Negative write enable, when at a low level activates a write operation and holds the data output drivers in a high impedance state. When at a high level NWE allows normal read operation.

NOE Negative output enable, when at a high level holds the data output drivers in a high impedance state. When at a low level, the data output driver state is defined by NCS, NWE and CE. If this signal is not used it must be connected to VSS.

CE\* Chip enable, when at a high level allows normal operation. When at a low level CE forces the SRAM to a precharge condition, holds the data output drivers in a high impedance state and disables all the input buffers except the NCS input buffer. If this signal is not used it must be connected to VDD.

## TRUTH TABLE

| NCS | CE* | NWE | NOE | MODE       | DQ       |

|-----|-----|-----|-----|------------|----------|

| L   | H   | H   | L   | Read       | Data Out |

| L   | H   | L   | X   | Write      | Data In  |

| H   | X   | XX  | XX  | Deselected | High Z   |

| X   | L   | XX  | XX  | Disabled   | High Z   |

Notes:

X:  $VI=VIH$  or  $VIL$

XX:  $VSS \leq VI \leq VDD$

NOE=H: High Z output state maintained for  $NCS=X$ ,  $CE=X$ ,  $NWE=X$

\*Not Available in 28-lead DIP or 28-Lead Flat Pack

# HX6256

## RADIATION CHARACTERISTICS

### Total Ionizing Radiation Dose

The SRAM will meet all stated functional and electrical specifications over the entire operating temperature range after the specified total ionizing radiation dose. All electrical and timing performance parameters will remain within specifications after rebound at  $V_{DD} = 5.5$  V and  $T = 125^\circ\text{C}$  extrapolated to ten years of operation. Total dose hardness is assured by wafer level testing of process monitor transistors and RAM product using 10 KeV X-ray and Co60 radiation sources. Transistor gate threshold shift correlations have been made between 10 KeV X-rays applied at a dose rate of  $1 \times 10^5$  rad(SiO<sub>2</sub>)/min at  $T = 25^\circ\text{C}$  and gamma rays (Cobalt 60 source) to ensure that wafer level X-ray testing is consistent with standard military radiation test environments.

### Transient Pulse Ionizing Radiation

The SRAM is capable of writing, reading, and retaining stored data during and after exposure to a transient ionizing radiation pulse up to the transient dose rate upset specification, when applied under recommended operating conditions. To ensure validity of all specified performance parameters before, during, and after radiation (timing degradation during transient pulse radiation is  $\leq 10\%$ ), it is suggested that stiffening capacitance be placed on or near the package VDD and VSS, with a maximum inductance between the package (chip) and stiffening capacitance of 0.7 nH per part. If there are no operate-through or valid stored data requirements, typical circuit board mounted de-coupling capacitors are recommended.

The SRAM will meet any functional or electrical specification after exposure to a radiation pulse up to the transient dose rate survivability specification, when applied under recommended operating conditions. Note that the current conducted during the pulse by the RAM inputs, outputs, and power supply may significantly exceed the normal operating levels. The application design must accommodate these effects.

### Neutron Radiation

The SRAM will meet any functional or timing specification after exposure to the specified neutron fluence under recommended operating or storage conditions. This assumes equivalent neutron energy of 1 MeV.

### Soft Error Rate

The SRAM is immune to Single Event Upsets (SEU's) to the specified Soft Error Rate (SER), under recommended operating conditions. This hardness level is defined by the Adams 90% worst case cosmic ray environment for geosynchronous orbits.

### Latchup

The SRAM will not latch up due to any of the above radiation exposure conditions when applied under recommended operating conditions. Fabrication with the SOI substrate material provides oxide isolation between adjacent PMOS and NMOS transistors and eliminates any potential SCR latchup structures. Sufficient transistor body tie connections to the p- and n-channel substrates are made to ensure no source/drain snapback occurs.

## RADIATION HARDNESS RATINGS (1)

| Parameter                             | Limits (2)              | Units                  | Test Conditions                                                             |

|---------------------------------------|-------------------------|------------------------|-----------------------------------------------------------------------------|

| Total Dose                            | $\geq 1 \times 10^6$    | rad(SiO <sub>2</sub> ) | $T_A = 25^\circ\text{C}$                                                    |

| Transient Dose Rate Upset (3)         | $\geq 1 \times 10^9$    | rad(Si)/s              | Pulse width $\leq \mu\text{s}$                                              |

| Transient Dose Rate Survivability (3) | $\geq 1 \times 10^{11}$ | rad(Si)/s              | Pulse width $\leq 50$ ns, X-ray, $V_{DD} = 6.0$ V, $T_A = 25^\circ\text{C}$ |

| Soft Error Rate (SER)                 | $< 1 \times 10^{-10}$   | upsets/bit-day         | $T_A = 25^\circ\text{C}$ , Adams 90% worst case environment                 |

| Neutron Fluence                       | $\geq 1 \times 10^{14}$ | N/cm <sup>2</sup>      | 1 MeV equivalent energy, Unbiased, $T_A = 25^\circ\text{C}$                 |

(1) Device will not latch up due to any of the specified radiation exposure conditions.

(2) Operating conditions (unless otherwise specified):  $V_{DD} = 4.5$  V to 5.5 V,  $T_A = -55^\circ\text{C}$  to  $125^\circ\text{C}$ .

(3) Not guaranteed with 28-Lead DIP.

# HX6256

## ABSOLUTE MAXIMUM RATINGS (1)

| Symbol  | Parameter                         | Rating      |          | Units |

|---------|-----------------------------------|-------------|----------|-------|

|         |                                   | Min         | Max      |       |

| VDD     | Supply Voltage Range (2)          | -0.5        | 6.5      | V     |

| VPIN    | Voltage on Any Pin (2)            | -0.5        | VDD +0.5 | V     |

| TSTORE  | Storage Temperature (Zero Bias)   | -65         | 150      | °C    |

| TSOLDER | Soldering Temperature (5 Seconds) |             | 270      | °C    |

| PD      | Maximum Power Dissipation (3)     |             | 2        | W     |

| IOUT    | DC or Average Output Current      |             | 25       | mA    |

| VPROT   | ESD Input Protection Voltage (4)  | 2000        |          | V     |

| ΘJC     | Thermal Resistance (Jct-toCase)   | 28 FP/36 FP | 2        | °C/W  |

|         |                                   | 28 DIP      | 10       |       |

| TJ      | Junction Temperature              |             | 175      | °C    |

(1) Stresses in excess of those listed above may result in permanent damage. These are stress ratings only, and operation at these levels is not implied. Frequent or extended exposure to absolute maximum conditions may affect device reliability.

(2) Voltage referenced to VSS.

(3) RAM power dissipation (IDDSB + IDDOP) plus RAM output driver power dissipation due to external loading must not exceed this specification.

(4) Class 2 electrostatic discharge (ESD) input protection. Tested per MIL-STD-883, Method 3015 by DESC certified lab.

## RECOMMENDED OPERATING CONDITIONS

| Symbol  | Parameter                              | Description |     |         | Units |

|---------|----------------------------------------|-------------|-----|---------|-------|

|         |                                        | Min         | Typ | Max     |       |

| VDD     | Supply Voltage (referenced to VSS)     | 4.5         | 5.0 | 5.5     | V     |

| TA      | Ambient Temperature                    | -55         | 25  | 125     | °C    |

| VPIN    | Voltage on Any Pin (referenced to VSS) | -0.3        |     | VDD+0.3 | V     |

| VDDRAMP | VDD Turn on ramp time                  |             |     | 50      | ms    |

## CAPACITANCE (1)

| Symbol | Parameter          | Typical (1) | Worst Case |     | Units | Test Conditions         |

|--------|--------------------|-------------|------------|-----|-------|-------------------------|

|        |                    |             | Min        | Max |       |                         |

| CI     | Input Capacitance  | 5           |            | 7   | pF    | VI=VDD or VSS, f=1 MHz  |

| CO     | Output Capacitance | 7           |            | 9   | pF    | VIO=VDD or VSS, f=1 MHz |

(1) This parameter is tested during initial design characterization only.

## DATA RETENTION CHARACTERISTICS

| Symbol | Parameter              | Typical (1) | Worst Case (2) |            | Units | Test Conditions                                            |

|--------|------------------------|-------------|----------------|------------|-------|------------------------------------------------------------|

|        |                        |             | Min            | Max        |       |                                                            |

| VDR    | Data Retention Voltage |             | 2.5            |            | V     | NCS=VDR<br>VI=VDR or VSS                                   |

| IDR    | Data Retention Current |             |                | 500<br>300 | μA    | NCS=VDD=2.5V, VI=VDD or VSS<br>NCS=VDD=3.0V, VI=VDD or VSS |

(1) Typical operating conditions: TA= 25°C, pre-radiation.

(2) Worst case operating conditions: TA= -55°C to +125°C, post total dose at 25°C.

# HX6256

## DC ELECTRICAL CHARACTERISTICS

| Symbol  | Parameter                                 | Typical<br>(1) | Worst Case (2)                   |                | Units | Test Conditions                                                     |

|---------|-------------------------------------------|----------------|----------------------------------|----------------|-------|---------------------------------------------------------------------|

|         |                                           |                | Min                              | Max            |       |                                                                     |

| IDDSB1  | Static Supply Current                     | 0.2            |                                  | 1.5            | mA    | VIH=VDD, IO=0<br>VIL=VSS, f=0MHz                                    |

| IDDSBMF | Standby Supply Current – Deselected       | 0.2            |                                  | 1.5            | mA    | NCS=VDD, IO=0, f=40 MHz                                             |

| IDDOPW  | Dynamic Supply Current – Selected (Write) | 3.4            |                                  | 4.0            | mA    | F=1 MHz, IO=0, CE=VIH=VDD<br>NCS=VIL=VSS (3)                        |

| IDDOPR  | Dynamic Supply Current – Selected (Read)  | 2.8            |                                  | 4.0            | mA    | F=1 MHz, IO=0, CE=VIH=VDD<br>NCS=VIL=VSS (3)                        |

| II      | Input Leakage Current                     |                | -5                               | +5             | µA    | VSS ≤ VI ≤ VDD                                                      |

| IOZ     | Output Leakage Current                    |                | -10                              | +10            | µA    | VSS ≤ VI ≤ VDD<br>Output = high Z                                   |

| VIL     | Low-Level Input Voltage CMOS<br>TTL       | 1.7            |                                  | 0.3xVDD<br>0.8 | V     | March Pattern<br>VDD = 4.5V                                         |

| VIH     | High-Level Input Voltage CMOS<br>TTL      | 3.2            | 0.7xVDD<br>2.2                   |                | V     | March Pattern<br>VDD = 4.5V                                         |

| VOL     | Low-Level Output Voltage                  | 0.3<br>0.05    |                                  | 0.4<br>0.05    | V     | VDD=4.5V, IOL = 10 mA (CMOS)<br>= 8 mA (TTL) VDD=4.5V, IOL = 200 µA |

| VOH     | High-Level Output Voltage                 | 4.3<br>4.5     | 4.2<br>V <sub>DD</sub> -<br>0.05 |                | V     | VDD=4.5V, IOH=-5mA<br>VDD=4.5V, IOH=-200 µA                         |

(1) Typical operating conditions: VDD= 5.0 V, TA=25°C, pre-radiation.

(2) Worst case operating conditions: VDD=4.5 V to 5.5 V, TA=-55°C to +125°C, post total dose at 25°C.

(3) All inputs switching. DC average current.

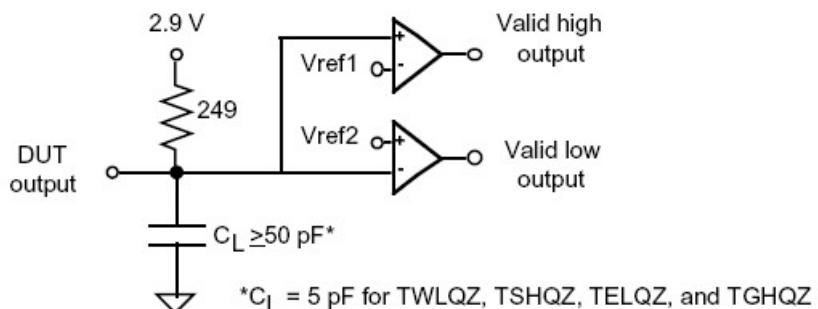

Tester Equivalent Load Circuit

# HX6256

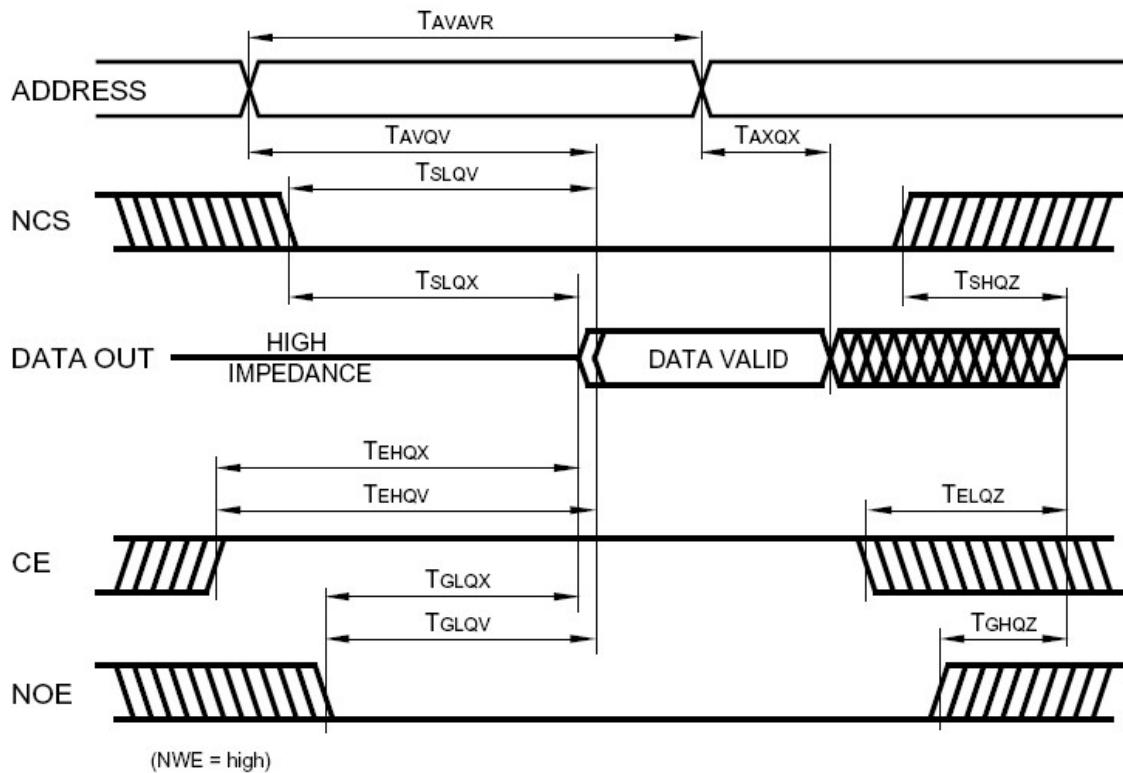

## READ CYCLE AC TIMING CHARACTERISTICS (1)

| Symbol | Parameter                             | Typical<br>(2) | Worst Case (3) |     | Units |

|--------|---------------------------------------|----------------|----------------|-----|-------|

|        |                                       |                | Min            | Max |       |

| TAVAVR | Address Read Cycle Time               | 17             | 25             |     | ns    |

| TAVQV  | Address Access Time                   | 14             |                | 25  | ns    |

| TAXQX  | Address Change to Output Invalid Time | 9              | 3              |     | ns    |

| TSLQV  | Chip Select Access Time               | 17             |                | 25  | ns    |

| TSLQX  | Chip Select Output Enable Time        | 10             | 5              |     | ns    |

| TSHQZ  | Chip Select Output Disable Time       | 4              |                | 10  | ns    |

| TEHQV  | Chip Select Access Time (4)           | 17             |                | 25  | ns    |

| TEHQX  | Chip Select Output Enable Time (4)    | 10             | 5              |     | ns    |

| TELQZ  | Chip Select Output Disable Time (4)   | 4              |                | 10  | ns    |

| TGLQV  | Output Enable Access Time             | 4              |                | 9   | ns    |

| TGLQX  | Output Enable Output Enable Time      | 4              | 0              |     | ns    |

| TGHQZ  | Output Enable Output Disable Time     | 2              |                | 9   | ns    |

(1) Test conditions: input switching levels  $V_{IL}/V_{IH}=0.5V/VDD-0.5V$  (CMOS),  $V_{IL}/V_{IH}=0V/3V$  (TTL), input rise and fall times  $<1\text{ ns}/V$ , input and output timing reference levels shown in the Tester AC Timing Characteristics table, capacitive output loading  $C_L >50\text{ pF}$ , or equivalent capacitive output loading  $C_L=5\text{ pF}$  for TSHQZ, TELQZ TGHQZ. For  $C_L >50\text{ pF}$ , derate access times by  $0.02\text{ ns/pF}$  (typical).

(2) Typical operating conditions:  $VDD=5.0\text{ V}$ ,  $TA=25^\circ\text{C}$ , pre-radiation.

(3) Worst case operating conditions:  $VDD=4.5\text{ V}$  to  $5.5\text{ V}$ ,  $-55$  to  $125^\circ\text{C}$ , post total dose at  $25^\circ\text{C}$ .

(4) Chip Enable (CE) pin not available on 28-lead FP or DIP.

# HX6256

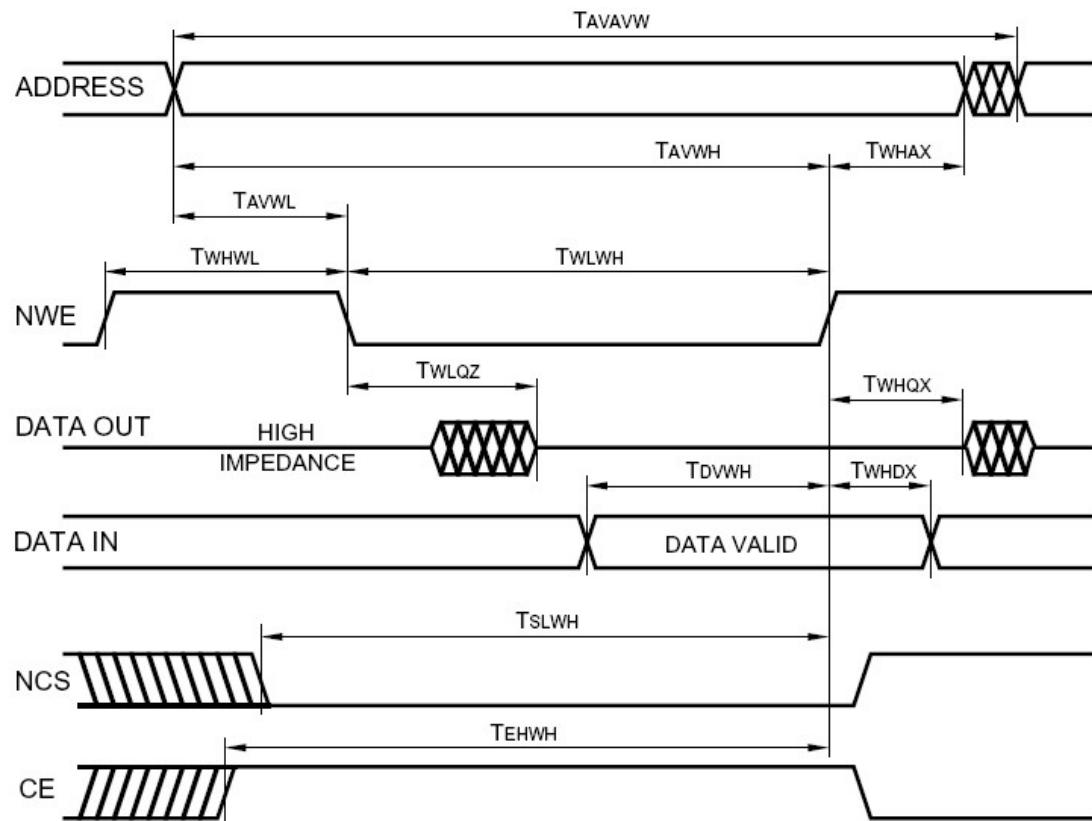

## WRITE CYCLE AC TIMING CHARACTERISTICS (1)

| Symbol | Parameter                                     | Typical (2) | Worst Case (3) |     | Units |

|--------|-----------------------------------------------|-------------|----------------|-----|-------|

|        |                                               |             | Min            | Max |       |

| TAVAVW | Write Cycle Time                              | 13          | 25             |     | ns    |

| TWLWH  | Write Enable Write Pulse Width                | 9           | 20             |     | ns    |

| TSLWH  | Chip Select to End of Write Time              | 10          | 20             |     | ns    |

| TDVWH  | Data Valid to End of Write Time               | 5           | 15             |     | ns    |

| TAVWH  | Address Valid to End of Write Time            | 9           | 20             |     | ns    |

| TWHDX  | Data Hold Time after End of Write Time        | 0           | 0              |     | ns    |

| TAVWL  | Address Valid Setup to Start of Write Time    | 0           | 0              |     | ns    |

| TWHAX  | Address Valid Hold after End of Write Time    | 0           | 0              |     | ns    |

| TWLQZ  | Write Enable to Output Disable Time           | 3           | 0              | 9   | ns    |

| TWHQX  | Write Disable to Output Enable Time           | 9           | 5              |     | ns    |

| TWHWL  | Write Disable to Write Enable Pulse Width (5) | 4           | 5              |     | ns    |

| TEHWH  | Chip Enable to End of Write Time (6)          | 12          | 20             |     | ns    |

(1) Test conditions: input switching levels  $VIL/VIH=0.5V/VDD-0.5V$  (CMOS),  $VIL/VIH=0V/3V$  (TTL), input rise and fall times  $<1\text{ ns/V}$ , input and output timing reference levels shown in the Tester AC Timing Characteristics table, capacitive output loading  $\geq 50\text{ pF}$ , or equivalent capacitive load of  $5\text{ pF}$  for TWLQZ.

(2) Typical operating conditions:  $VDD=5.0\text{ V}$ ,  $TA=25^\circ\text{C}$ , pre-radiation.

(3) Worst case operating conditions:  $VDD=4.5\text{ V}$  to  $5.5\text{ V}$ ,  $-55$  to  $125^\circ\text{C}$ , post total dose at  $25^\circ\text{C}$ .

(4)  $TAVAV = TWLWH + TWHWL$

(5) Guaranteed but not tested.

(6) Chip Enable (CE) pin not available on 28-lead FP or DIP.

## HX6256

# HX6256

## DYNAMIC ELECTRICAL CHARACTERISTICS

### Read Cycle

The RAM is asynchronous in operation, allowing the read cycle to be controlled by address, chip select (NCS), or chip enable (CE) (refer to Read Cycle timing diagram). To perform a valid read operation, both chip select and output enable (NOE) must be low and chip enable and write enable (NWE) must be high. The output drivers can be controlled independently by the NOE signal. Consecutive read cycles can be executed with NCS held continuously low, and with CE held continuously high, and toggling the addresses.

For an address activated read cycle, NCS and CE must be valid prior to or coincident with the activating address edge transition(s). Any amount of toggling or skew between address edge transitions is permissible; however, data outputs will become valid TAVQV time following the latest occurring address edge transition. The minimum address activated read cycle time is TAVAV. When the RAM is operated at the minimum address activated read cycle time, the data outputs will remain valid on the RAM I/O until TAXQX time following the next sequential address transition.

To control a read cycle with NCS, all addresses and CE must be valid prior to or coincident with the enabling NCS edge transition. Address or CE edge transitions can occur later than the specified setup times to NCS, however, the valid data access time will be delayed. Any address edge transition, which occurs during the time when NCS is low, will initiate a new read access, and data outputs will not become valid until TAVQV time following the address edge transition. Data outputs will enter a high impedance state TSHQZ time following a disabling NCS edge transition.

To control a read cycle with CE, all addresses and NCS must be valid prior to or coincident with the enabling CE edge transition. Address or NCS edge transitions can occur later than the specified setup times to CE; however, the valid data access time will be delayed. Any address edge transition which occurs during the time when CE is high will initiate a new read access, and data outputs will not become valid until TAVQV time following the address edge transition. Data outputs will enter a high impedance state TELQZ time following a disabling CE edge transition.

### Write Cycle

The write operation is synchronous with respect to the address bits, and control is governed by write enable (NWE), chip select (NCS), or chip enable (CE) edge transitions (refer to Write Cycle timing diagrams). To perform a write operation, both NWE and NCS must be low, and CE must be high. Consecutive write cycles can be performed with NWE or NCS held continuously low, or CE held continuously high. At least one of the control signals must transition to the opposite state between consecutive write operations.

The write mode can be controlled via three different control signals: NWE, NCS, and CE. All three modes of control are similar except the NCS and CE controlled modes actually disable the RAM during the write recovery pulse. Both CE and NCS fully disable the RAM decode logic and input buffers for power savings. Only the NWE controlled mode is shown in the table and diagram on the previous page for simplicity. However, each mode of control provides the same write cycle timing characteristics. Thus, some of the parameter names referenced below are not shown in the write cycle table or diagram, but indicate which control pin is in control as it switches high or low.

To write data into the RAM, NWE and NCS must be held low and CE must be held high for at least TWLWH/TSLSH/TEHEL time. Any amount of edge skew between the signals can be tolerated, and any one of the control signals can initiate or terminate the write operation. For consecutive write operations, write pulses must be separated by the minimum specified TWHWL/TSHSL/TELEH time. Address inputs must be valid at least TAVWL/TAVSL/TAVEH time before the enabling NWE/NCS/CE edge transition, and must remain valid during the entire write time. A valid data overlap of write pulse width time of TDVWH/TDVSH/TDVEL, and an address valid to end of write time of TAVWH/TAVSH/TAVEL also must be provided for during the write operation. Hold times for address inputs and data inputs with respect to the disabling NWE/NCS/CE edge transition must be a minimum of TWHAX/TSHAX/TELAX time and TWHDX/TSHDX/TELDX time, respectively. The minimum write cycle time is TAVAV.

# HX6256

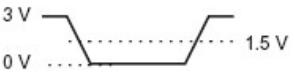

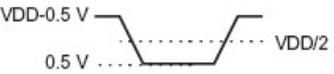

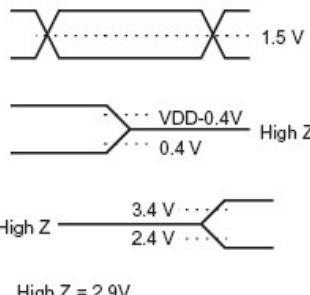

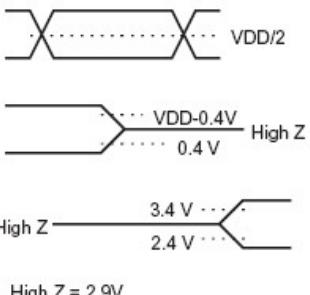

## TESTER AC TIMING CHARACTERISTICS

|                     | TTL I/O Configuration                                                             | CMOS I/O Configuration                                                             |

|---------------------|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| Input Levels*       |  |  |

| Output Sense Levels |  |  |

\* Input rise and fall times <1 ns/V

## QUALITY AND RADIATION HARDNESS ASSURANCE

Honeywell maintains a high level of product integrity through process control, utilizing statistical process control, a complete "Total Quality Assurance System," a computer data base process performance tracking system, and a radiation-hardness assurance strategy.

The radiation hardness assurance strategy starts with a technology that is resistant to the effects of radiation. Radiation hardness is assured on every wafer by irradiating test structures as well as SRAM product, and then monitoring key parameters which are sensitive to ionizing radiation. Conventional MIL-STD-883 TM 5005 Group E testing, which includes total dose exposure with Cobalt 60, may also be performed as required. This Total Quality approach ensures our customers of a reliable product by engineering in reliability, starting with process development and continuing through product qualification and screening.

## SCREENING LEVELS

Honeywell offers several levels of device screening to meet your system needs. "Engineering Devices" are available with limited performance and screening for breadboarding and/or evaluation testing. Hi-Rel Level B and S devices undergo additional screening per the requirements of MIL-STD-883. As a QML supplier, Honeywell also offers QML Class Q and V devices per MIL-PRF-38535 and are available per the applicable Standard Microcircuit Drawing (SMD). QML devices offer ease of procurement by eliminating the need to create detailed specifications and offer benefits of improved quality and cost savings through standardization.

## RELIABILITY

Honeywell understands the stringent reliability requirements for space and defense systems and has extensive experience in reliability testing on programs of this nature. This experience is derived from comprehensive testing of VLSI processes. Reliability attributes of the RICMOS™ process were characterized by testing specially designed irradiated and non-irradiated test structures from which specific failure mechanisms were evaluated. These specific mechanisms included, but were not limited to, hot carriers, electromigration and time dependent dielectric breakdown. This data was then used to make changes to the design models and process to ensure more reliable products.

In addition, the reliability of the RICMOS™ process and product in a military environment was monitored by testing irradiated and non-irradiated circuits in accelerated dynamic life test conditions. Packages are qualified for product use after undergoing Groups B & D testing as outlined in MIL-STD-883, TM 5005, Class S. The product is qualified by following a screening and testing flow to meet the customer's requirements. Quality conformance testing is performed as an option on all production lots to ensure the ongoing reliability of the product.

# HX6256

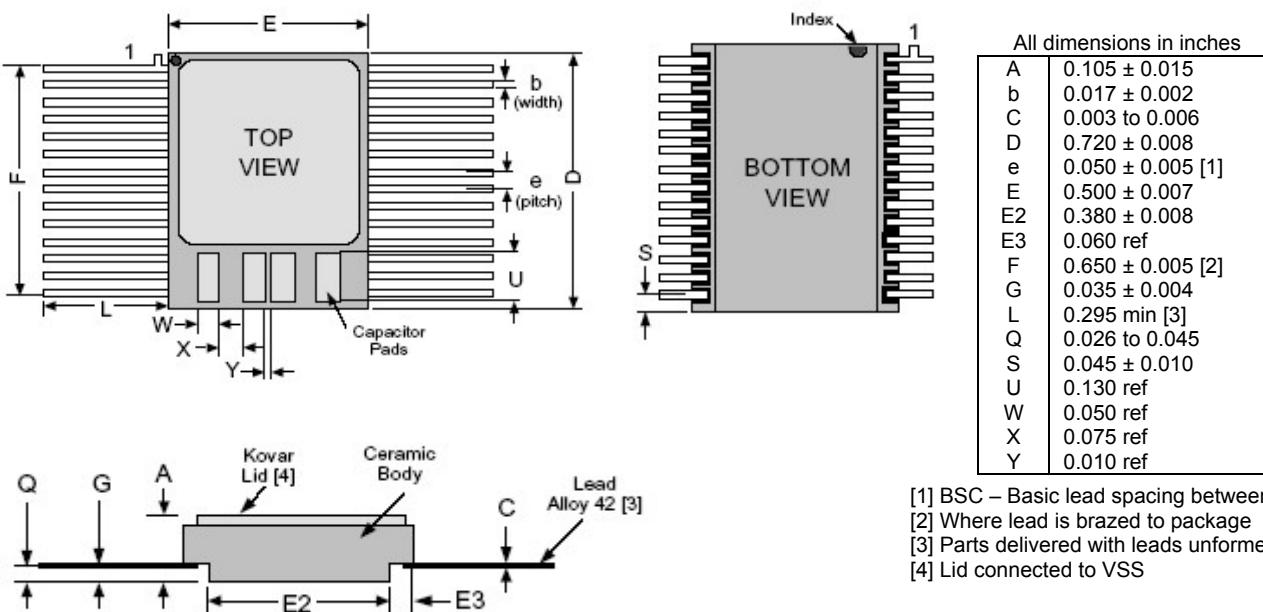

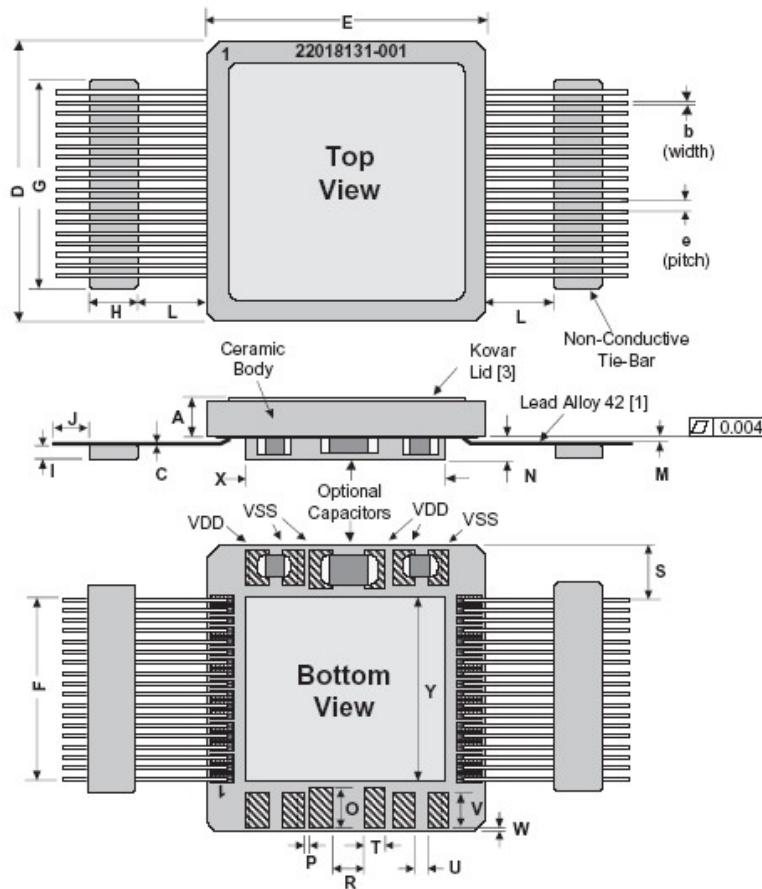

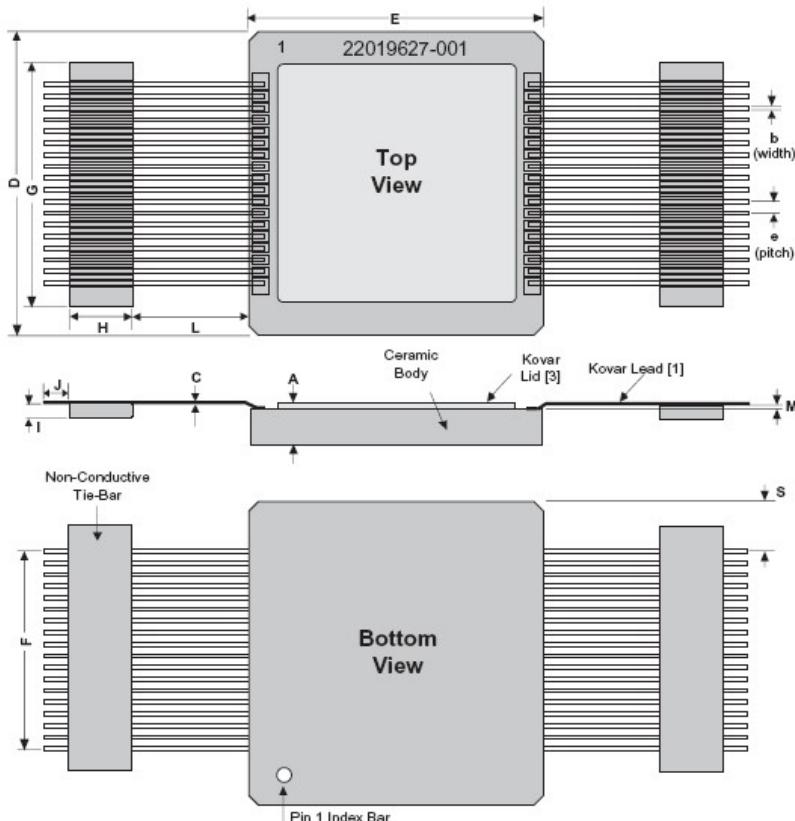

## PACKAGING

The 32K x 8 SRAM is offered in two custom 36-lead flat packs, a 28-Lead FP, or standard 28-lead DIP. Each package is constructed of multilayer ceramic ( $\text{Al}_2\text{O}_3$ ) and features internal power and ground planes. The 36-lead flat packs also feature a non-conductive ceramic tie bar on the lead frame. The tie bar allows electrical testing of the device, while preserving the lead integrity during shipping and handling, up to the point of lead forming and insertion.

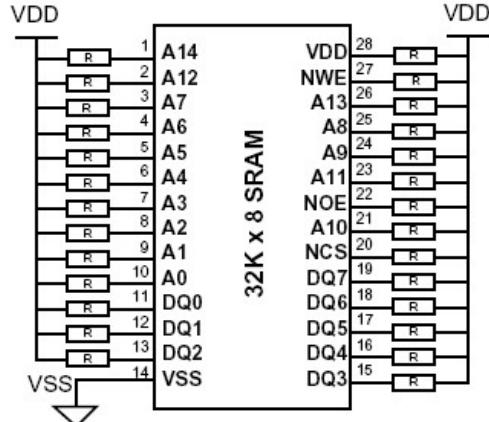

### 28-LEAD DIP & FP PINOUT

|     |    |    |     |

|-----|----|----|-----|

| A14 | 1  | 28 | VDD |

| A12 | 2  | 27 | NWE |

| A7  | 3  | 26 | A13 |

| A6  | 4  | 25 | A8  |

| A5  | 5  | 24 | A9  |

| A4  | 6  | 23 | A11 |

| A3  | 7  | 22 | NOE |

| A2  | 8  | 21 | A10 |

| A1  | 9  | 20 | NCS |

| A0  | 10 | 19 | DQ7 |

| DQ0 | 11 | 18 | DQ6 |

| DQ1 | 12 | 17 | DQ5 |

| DQ2 | 13 | 16 | DQ4 |

| VSS | 14 | 15 | DQ3 |

On the bottom brazed 36-lead FP, ceramic chip capacitors can be mounted to the package by the user to maximize supply noise decoupling and increase board packing density. These capacitors connect to the internal package power and ground planes. This design minimizes resistance and inductance of the bond wire and package. All NC (no connect) pins must be connected to either VDD, VSS or an active driver to prevent charge build up in the radiation environment.

### 36-LEAD FP PINOUT

|     |    |    |     |

|-----|----|----|-----|

| VSS | 1  | 36 | VSS |

| VDD | 2  | 35 | VDD |

| A14 | 3  | 34 | NWE |

| A12 | 4  | 33 | CE  |

| A7  | 5  | 32 | A13 |

| A6  | 6  | 31 | A8  |

| A5  | 7  | 30 | A9  |

| A4  | 8  | 29 | A11 |

| A3  | 9  | 28 | NOE |

| A2  | 10 | 27 | A10 |

| A1  | 11 | 26 | NCS |

| A0  | 12 | 25 | DQ7 |

| DQ0 | 13 | 24 | DQ6 |

| DQ1 | 14 | 23 | DQ5 |

| DQ2 | 15 | 22 | DQ4 |

| NC  | 16 | 21 | DQ3 |

| VDD | 17 | 20 | VDD |

| VSS | 18 | 19 | VSS |

### 28-LEAD FLAT PACK (22017842-001)

### 28-LEAD DIP (22017785-001)

For 28-Lead DIP description, see MIL-STD-1835, Type CDIP2-T28, Config. C, Dimensions D-10

# HX6256

## 36-LEAD FLAT PACK—BOTTOM BRAZE (22018131-001)

| All dimensions in inches |                   |   |               |

|--------------------------|-------------------|---|---------------|

| A                        | 0.095 ± 0.014     | M | 0.008 ± 0.003 |

| b                        | 0.008 ± 0.002     | N | 0.050 ± 0.010 |

| C                        | 0.005 to 0.0075   | O | 0.090 ref     |

| D                        | 0.650 ± 0.010     | P | 0.015 ref     |

| E                        | 0.630 ± 0.007     | R | 0.075 ref     |

| e                        | 0.025 ± 0.002 [2] | S | 0.113 ± 0.010 |

| F                        | 0.425 ± 0.005 [2] | T | 0.050 ref     |

| G                        | 0.525 ± 0.005     | U | 0.030 ref     |

| H                        | 0.135 ± 0.005     | V | 0.080 ref     |

| I                        | 0.030 ± 0.005     | W | 0.005 ref     |

| J                        | 0.080 typ.        | X | 0.450 ref     |

| L                        | 0.285 ± 0.015     | Y | 0.400 ref     |

[1] Parts delivered with leads unformed

[2] At tie bar

[3] Lid tied to VSS

## 36-LEAD FLAT PACK—TOP BRAZE (22019627-001)

| All dimensions in inches |                   |

|--------------------------|-------------------|

| A                        | 0.085 ± 0.010     |

| b                        | 0.008 ± 0.002     |

| C                        | 0.005 to 0.0075   |

| D                        | 0.650 ± 0.010     |

| E                        | 0.630 ± 0.007     |

| e                        | 0.025 ± 0.002 [2] |

| F                        | 0.425 ± 0.005 [2] |

| G                        | 0.525 ± 0.005     |

| H                        | 0.135 ± 0.005     |

| I                        | 0.030 ± 0.005     |

| J                        | 0.080 typ.        |

| L                        | 0.285 ± 0.015     |

| M                        | 0.009 ± 0.003     |

| S                        | 0.113 ± 0.010     |

[1] Parts delivered with leads unformed

[2] At tie bar

[3] Lid tied to VSS

# HX6256

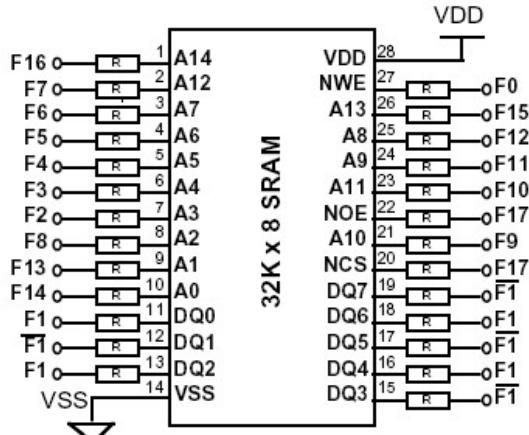

## DYNAMIC BURN-IN DIAGRAM\*

VDD = 5.6V, R ≤ 10 KΩ, VIH = VDD, VIL = VSS

Ambient Temperature ≥ 125°C, F0 ≥ 100 KHz Sq Wave

Frequency of F1 = F0/2, F2 = F0/4, F3 = F0/8, etc.

VDD = 5.5V, R ≤ 10 KΩ

Ambient Temperature ≥ 125°C

\*36-lead Flat Pack burn-in diagram has similar connections and is available on request.

## ORDERING INFORMATION (1)

| H           | X       | 6256                           | N | S                 | H                                          | C            |

|-------------|---------|--------------------------------|---|-------------------|--------------------------------------------|--------------|

|             |         | PART NUMBER                    |   |                   |                                            |              |

|             |         |                                |   | SCREEN LEVEL      |                                            | INPUT        |

|             |         |                                |   | V=QML Class V     |                                            | BUFFER TYPE  |

|             |         |                                |   | Q=QML Class Q     |                                            | C=CMOS Level |

|             |         |                                |   | S=Class S         |                                            | T=TTL Level  |

|             |         |                                |   | B=Class B         |                                            |              |

|             |         |                                |   | E=Engr Device (3) | TOTAL DOSE                                 |              |

|             |         |                                |   |                   | HARDNESS                                   |              |

|             |         |                                |   |                   | R=1x10 <sup>5</sup> rad(SiO <sub>2</sub> ) |              |

|             |         |                                |   |                   | F=3x10 <sup>5</sup> rad(SiO <sub>2</sub> ) |              |

|             |         |                                |   |                   | H=1x10 <sup>6</sup> rad(SiO <sub>2</sub> ) |              |

|             |         |                                |   |                   | N=No Level Guaranteed                      |              |

| SOURCE      | PROCESS | PACKAGE DESIGNATION            |   |                   |                                            |              |

| H=HONEYWELL | X=SOI   | N=28-Lead FP                   |   |                   |                                            |              |

|             |         | R=28-Lead DIP                  |   |                   |                                            |              |

|             |         | X=36-Lead FP (Bottom Braze)(2) |   |                   |                                            |              |

|             |         | P=36-Lead FP (Top Braze)       |   |                   |                                            |              |

|             |         | K=Known Good Die               |   |                   |                                            |              |

|             |         | - = Bare die (No Package)      |   |                   |                                            |              |

(1) Orders may be faxed to 763-954-2257.

(2) For CMOS I/O type only.

(3) Engineering Device description: Parameters are tested from -55 to 125°C, 24 hr burn-in, no radiation guaranteed.

The QML Certified SRAM can also be ordered under the SMD drawing 5962-95845.

## FIND OUT MORE

For more information on Honeywell's SRAM products visit us online at [www.honeywell.com/radhard](http://www.honeywell.com/radhard) or contact us at 800-323-8295 (763-954-2474 internationally).

This product and related technical data is subject to the U.S. Department of State International Traffic in Arms Regulations (ITAR) 22 CFR 120-130 and may not be exported, as defined by the ITAR, without the appropriate prior authorization from the Directorate of Defense Trade Controls, United States Department of State. Diversion contrary to U.S. export laws and regulations is prohibited.

The application circuits herein constitute typical usage and interface of Honeywell product. Honeywell does not warranty or assume liability of customer-designed circuits derived from this description or depiction.

Honeywell reserves the right to make changes to improve reliability, function or design. Honeywell does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others.