## EM MICROELECTRONIC - MARIN SA

H6060

# **Self Recovering Watchdog**

#### Description

The H6060 is a monolithic low-power CMOS device combining a programmable timer and a series of voltage comparators on the same chip. The device is specially suited for watchdog functions such as microprocessor and supply voltage monitoring. If the μP system malfunctions, the watchdog will recover it by issuing repeated active reset signals. The voltage monitoring part provides double security by combining both the unregulated voltage (V<sub>IN</sub>) regulated voltage (V<sub>DD</sub>) simultaneously. The H6060 initializes the power-on reset after V<sub>IN</sub> reaches V<sub>SH</sub> (see table 4) and V<sub>DD</sub> rises above 3.V. If V<sub>IN</sub> drops below V<sub>SL</sub> (see table 4), the H6060 gives an advanced warning signal for register saving and if the voltage drops further below V<sub>RL</sub> (see table 4), RES and RES go active. The H6060 functions at any supply voltage down to 1.6 V and is therefore particularly suited for start-up and shut-down control of microprocessor systems.

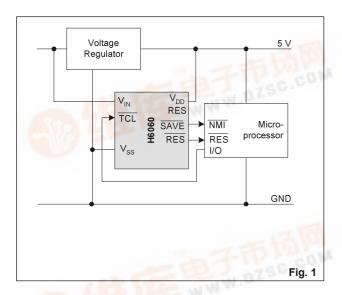

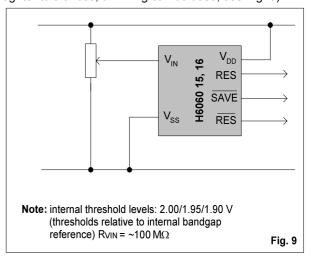

### **Typical Operating Configuration**

#### **Features**

- ☐ Self recovering watchdog function: reset goes active after the 1st timeout period, reset goes inactive again after the 2nd timeout period, repeated active reset signal until the system recovers

- Standard timeout period and power-on reset time (100 ms), externally programmable if required

- □ Unregulated DC monitoring (V<sub>IN</sub>) with 3 standard or programmable trigger voltages for: power-on reset initialization, advanced power-fail warning (SAVE), reset at power-down (RES)

- □ Regulated DC monitoring (V<sub>DD</sub>): power-on reset initialization enabled only if V<sub>DD</sub> ≥ 3.5 V

- □ Internal voltage reference

- ☐ Works down to 1.6 V supply voltage

- □ Push-pull or Open drain outputs

- Low current consumption

- ☐ SO8 package

#### **Applications**

- ☐ Microprocessor and microcontroller systems

- Point of sales equipment

- □ Telecom products

- □ Automotive subsystems

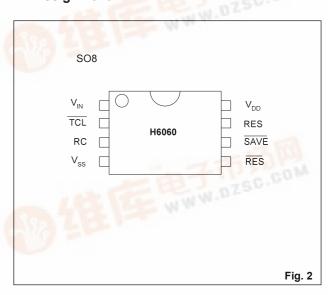

#### **Pin Assignment**

#### **Absolute Maximum Ratings**

| Parameter                                         | Symbol             | Conditions      |

|---------------------------------------------------|--------------------|-----------------|

| Voltage V <sub>DD</sub> to V <sub>SS</sub>        | $V_{DD}$           | – 0.3 to + 8 V  |

| Voltage at any pin to V <sub>SS</sub>             | V <sub>MIN</sub>   | - 0.3           |

| Voltage at any pin to $V_{DD}$ (except $V_{IN}$ ) | V <sub>INMAX</sub> | + 0.3           |

| Voltage at V <sub>IN</sub> to V <sub>SS</sub>     | $V_{MIN}$          | + 15 V          |

| Current at any output                             | I <sub>MAX</sub>   | ± 10 mA         |

| Storage temperature                               | T <sub>STO</sub>   | -65°C to +150°C |

Table 1

Stresses above these listed maximum ratings may cause permanent damages to the device. Exposure beyond specified operating conditions may affect device reliability or cause malfunction.

#### **Handling Procedures**

This device has built-in protection against high static voltages or electric fields; however, anti-static precautions must be taken as for any other CMOS component. Unless otherwise specified, proper operation can only occur when

all terminal voltages are kept within the voltage range. Unused inputs must always be tied to a defined logic voltage level.

#### **Operating Conditions**

| Parameter                        | Symbol          | Min. | Max.     | Units |

|----------------------------------|-----------------|------|----------|-------|

| Operating temperature Industrial | T <sub>AI</sub> | -40  | +85      | °C    |

| Supply voltage                   | $V_{DD}$        | 1.6  | 5.5      | V     |

| Comparator input voltage         |                 |      |          |       |

| Version 13, 14, 15, 16           | $V_{IN}$        | 0    | $V_{DD}$ | V     |

| Version 11,12                    | $V_{IN}$        | 0    | 12       | V     |

| RC-oscillator programm-          |                 |      |          |       |

| ing (see Fig. 15)                |                 |      |          |       |

| External capacitance*            | C1              |      | 1        | μF    |

| External resistance              | R1              | 10   |          | kΩ    |

Table 2

#### **Electrical Characteristics**

$V_{DD}$  = 5.0 V,  $T_A$  = -40 to +85 °C, unless otherwise specified

| Parameter                              | Symbol           | Test Conditions                                   | Min. | Тур.           | Max. | Units |

|----------------------------------------|------------------|---------------------------------------------------|------|----------------|------|-------|

| V <sub>DD</sub> activation threshold   | V <sub>ON</sub>  | T <sub>A</sub> = 25 °C                            | 3    |                | 3.5  | V     |

| V <sub>DD</sub> deactivation threshold | $V_{OFF}$        | T <sub>A</sub> = 25 °C                            |      | $V_{ON} - 0.3$ |      | V     |

| Supply current                         | $I_{DD}$         | RC open, $\overline{TCL}$ at $V_{DD}$ or $V_{SS}$ |      | 80             | 140  | μΑ    |

| Input V <sub>IN</sub> , TCL            |                  |                                                   |      |                |      |       |

| Leakage current                        | I <sub>IP</sub>  | $V_{SS} \le V_{IP} \le V_{DD}$ ;                  |      |                |      |       |

|                                        |                  | T <sub>A</sub> = 85 °C                            |      | 0.005          | 1    | μΑ    |

| Input current on pin V <sub>IN</sub>   | I <sub>IN</sub>  | Version 12; V <sub>IN</sub> = 10 V                |      | 100            | 180  | μA    |

| TCL input low level                    | $V_{IL}$         | ·                                                 |      |                | 8.0  | V     |

| TCL input high level                   | V <sub>IH</sub>  |                                                   | 2.4  |                |      | V     |

| SAVE, RES, RES outputs                 |                  |                                                   |      |                |      |       |

| Leakage currents                       | I <sub>OLK</sub> | Version 15;                                       |      |                |      |       |

|                                        |                  | $V_{OUT} = V_{DD}$                                |      | 0.05           | 1    | μΑ    |

| Drive currents (all versions)          | I <sub>OL</sub>  | V <sub>OL</sub> = 0.4 V                           | 3.2  | 8              |      | mA    |

| , ,                                    | I <sub>OL</sub>  | $V_{DD} = 3.5 \text{ V}; V_{OL} = 0.4 \text{ V}$  | 2    |                |      | mA    |

|                                        | I <sub>OL</sub>  | $V_{DD} = 1.6 \text{ V}; V_{OL} = 0.4 \text{ V}$  | 80   |                |      | μΑ    |

| Drive currents                         | Іон              | V <sub>OH</sub> = 4.0 V                           | 3.2  | 8              |      | mA    |

| (versions 14,16) <sup>1)</sup>         | Іон              | V <sub>DD</sub> = 3.5 V: V <sub>OH</sub> = 2.8 V  | 2    |                |      | mA    |

|                                        | I <sub>OH</sub>  | $V_{DD} = 1.6 \text{ V}; V_{OH} = 1.2 \text{ V}$  | 80   |                |      | μΑ    |

<sup>1)</sup> Versions: 15 = open drain outputs; 14, 16 = push-pull outputs

Table 3

#### **VIN Surveillance**

Voltage thresholds at T<sub>A</sub> = 25 °C

| Version 1) | Comparator         | Input Resistance                       | Threshold |          |                    | Thresholds | Ratio           |

|------------|--------------------|----------------------------------------|-----------|----------|--------------------|------------|-----------------|

|            | Reference          | on V <sub>IN</sub> (R <sub>VIN</sub> ) | $V_{SH}$  | $V_{SL}$ | $V_{RL}$           | Tolerance  | 3)<br>Tolerance |

| 14         | $V_{DD}$           | ~100MΩ                                 | 2.25      | 2.00     | 1.75 <sup>2)</sup> | ±5%        | ±2%             |

| 15, 16     | Band-gap reference | ~100MΩ                                 | 2.00      | 1.95     | 1.90               | ±10%       | ±2%             |

<sup>1)</sup> Version: 15 = open drain outputs; 14, 16 = push-pull outputs

<sup>\*</sup> Leakage < 1µA

$<sup>^{2}</sup>$  at  $V_{DD} = 5 \text{ V}$

$<sup>^{3)}</sup>$  Threshold ratio tolerance is defined as the tolerance of V  $_{SH}$  / V  $_{SL}$  and V  $_{SL}$  / V  $_{RL}$

Timing Characteristics  $V_{DD}$  = 5.0 V,  $T_A$  = –40 °C to +85 °C, unless otherwise specified

| Parameter                                                            | Symbol            | Test Conditions                                                                 | Min.     | Тур.                | Max.       | Units    |

|----------------------------------------------------------------------|-------------------|---------------------------------------------------------------------------------|----------|---------------------|------------|----------|

| Propagation delays TCL to output pins V <sub>IN</sub> to output pins | T <sub>DIDO</sub> | Excluding debounce time T <sub>DB</sub>                                         |          | 250<br>4            | 500<br>10  | ns<br>μs |

| Logic transition times on all output pins                            | T <sub>TR</sub>   | Load 10 kΩ, 100 pF                                                              |          | 30                  | 100        | ns       |

| Timeout period                                                       | T <sub>TO</sub>   | RC open, unshielded, T <sub>A</sub> = 25 °C<br>RC open, unshielded (not tested) | 60<br>45 | 100                 | 160<br>200 | ms<br>ms |

| T <sub>TCL</sub> input pulse width                                   | T <sub>TCL</sub>  | ,                                                                               | 150      |                     |            | ns       |

| Power-on reset debounce                                              | T <sub>DB</sub>   |                                                                                 |          | T <sub>TO</sub> /64 |            | ms       |

| V <sub>IN</sub> low pulse                                            | T <sub>VINL</sub> | Where debounce time T <sub>DB</sub> Is guaranteed                               | 10       |                     |            | μs       |

Table 5

# Timing Waveforms Voltage Reaction: $V_{\text{DD}}$ Monitoring

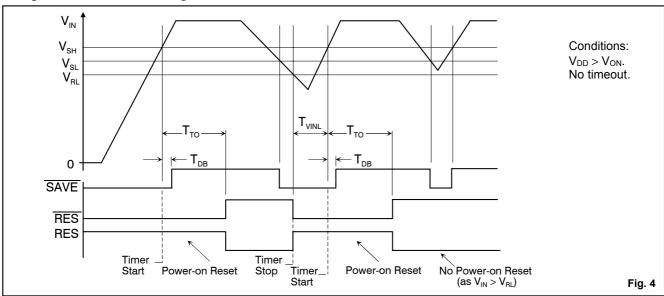

#### Voltage Reaction: V<sub>IN</sub> Monitoring

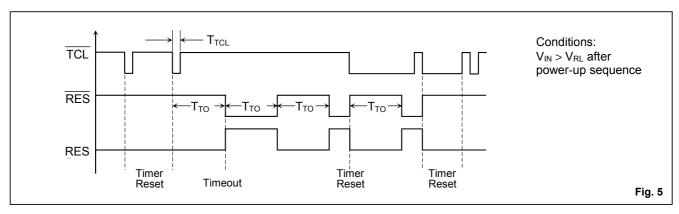

#### **Timer Reaction**

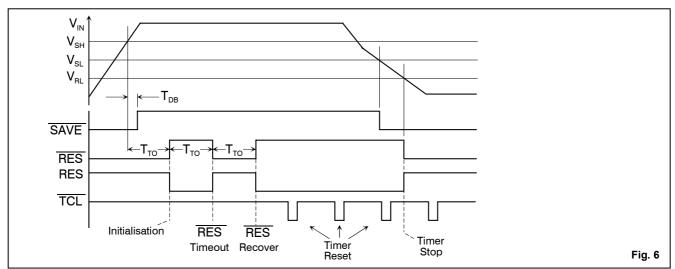

### **Combined Voltage and Timer Reaction**

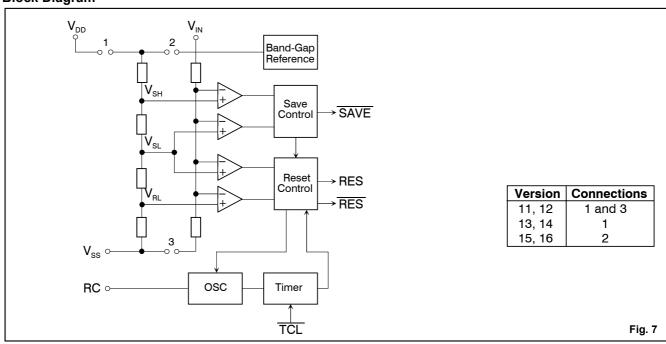

#### **Block Diagram**

**Pin Description**

| Pin | Name            | Function                         |

|-----|-----------------|----------------------------------|

| 1   | V <sub>IN</sub> | Voltage sense input              |

| 2   | TCL             | Timer clear input signal         |

| 3   | RC              | RC oscillator tuning input       |

| 4   | $V_{SS}$        | GND terminal                     |

| 5   | RES             | Active low reset output          |

| 6   | SAVE            | Save output                      |

| 7   | RES             | Active high reset output         |

| 8   | $V_{DD}$        | Positive supply voltage terminal |

Table 6

#### **Functional Description**

#### **Supply Lines**

The circuit is powered through the  $V_{DD}$  and  $V_{SS}$  pins. It monitors both its own  $V_{DD}$  supply and a voltage applied to the  $V_{IN}$  input.

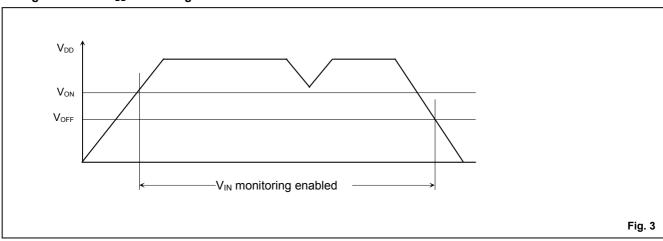

#### **V**<sub>DD</sub> Monitoring

During power-up the V<sub>IN</sub> monitoring is disabled and  $\overline{RES}$ , RES and  $\overline{SAVE}$  stay active low as long as V<sub>DD</sub> is below V<sub>ON</sub> (3.5 V). As soon as V<sub>DD</sub> reaches the V<sub>ON</sub> level, the state of the outputs depend on the watchdog timer and the voltage at V<sub>IN</sub> relative to the thresholds (see Fig. 4). If the supply voltage V<sub>DD</sub> falls back below V<sub>OFF</sub> (V<sub>ON</sub> – 0.3 V) the watchdog timer and the V<sub>IN</sub> monitoring are disabled and the outputs  $\overline{RES}$ , RES and  $\overline{SAVE}$  become active. The V<sub>DD</sub> line should be free of voltage spikes.

#### **VIN Monitoring**

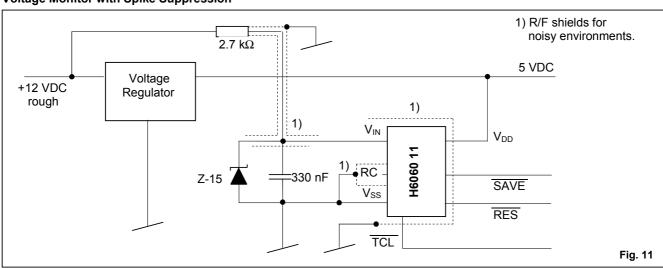

The analog voltage comparators compare the voltage applied to V<sub>IN</sub> (typically connected to the input of the voltage regulator) with the stabilized supply voltage  $V_{\text{DD}}$ (version 14) or with the bandgap voltage (versions 15, 16) (see Fig. 7). At power-up, when  $V_{DD}$  reached  $V_{ON}$  and  $V_{IN}$ reaches the V<sub>SH</sub> level, the SAVE output goes inactive, and the timer starts running, setting  $\overline{\text{RES}}$  and RES in active after the time  $T_{TO}$  (see. Fig. 4). If  $V_{IN}$  falls below  $V_{SL}$ , the SAVE output goes active and stays active until V<sub>IN</sub> rises again above  $V_{SH}$ . If  $V_{IN}$  falls below the voltage  $V_{RL}$ , RES and RES will become active and the on-chip timer will stop. When V<sub>IN</sub> rises again above V<sub>SH</sub>, the timer will initiate a power-up sequence. The RES and RES outputs may however be influenced independently of the voltage V<sub>IN</sub> by the timer action, see section "Combined Voltage and Timer Action". Monitoring the rough DC side of the regulator, as shown in Fig. 11, is the only way to have advanced warning of power-down. Spikes on  $V_{\text{IN}}$  should be filtered if they are likely to exceed the value ( $V_{SL}$  - $V_{RI}$  ).

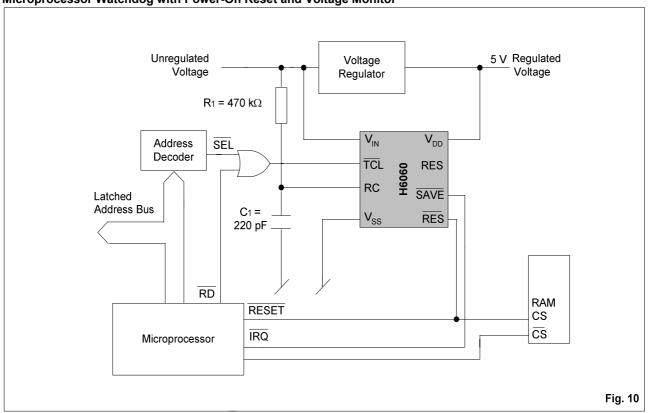

The combination of  $V_{IN}\,$  and  $V_{DD}\,$  monitoring provide high system security: if  $V_{IN}\,$  rises much faster than  $V_{DD}\,$ , then the device starts the power-on sequence only when  $V_{DD}\,$  reached  $V_{ON}\,$  (Fig. 10). Short circuits on the regulated supply voltage can be detected.

#### Voltage Thresholds on VIN

The H6060 is available with 3 different sets of thresholds:

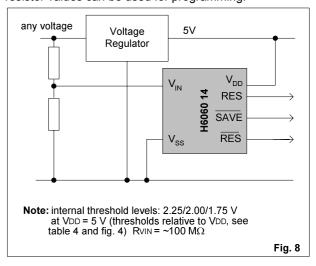

**Version 14:** monitor the unregulated voltage and are ideal for programming of the  $V_{\text{IN}}$  voltage thresholds. Fixed resistor values can be used for programming.

**Version 15, 16:** monitor the regulated voltage. They are suited to applications where the unregulated voltage is not available. (The tolerance is  $\pm$  10%, see table 4. For tighter tolerances, trimming can be used, see Fig. 9).

Monitoring of the unregulated voltage requires version 14. These versions are based on the principle that  $V_{DD}$  rises with  $V_{IN}$  on power-up an  $V_{DD}$  holds up for a certain time after  $V_{IN}$  starts dropping on power-down. The versions 11 and 12 have a 100  $k\Omega$  nominal resistance from  $V_{IN}$  to  $V_{SS}$  (internal voltage divider). The versions 14, 15 and 16 have high impedance  $V_{IN}$  inputs (see Fig. 7 and Table 4) for external threshold voltage programming by a voltage divider on pin  $V_{IN}$ . The levels obtained are proportional to the internal levels  $V_{SH},\,V_{SL}$  and  $V_{RL}$  on the chip itself (see Electrical Specifications).

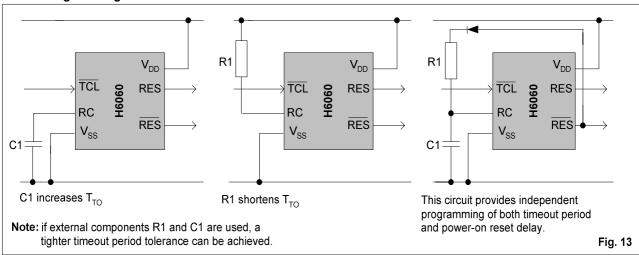

#### **Timer Programming**

With pin RC unconnected, the on-chip RC oscillator together with its divider chain give a timeout  $T_{TO}$  of typically 100 ms. To program different  $T_{TO}$ , an approximation for calculating component values is given by the formula:

$$T_{TO} = \begin{bmatrix} 0.75 + \frac{(32 + C_1) \cdot 2}{5.5 + \frac{V_{DD} - 1}{R_1}} \end{bmatrix} 8.192$$

$R_{1\,\text{min.}}$  = 10 k $\Omega,\,C_{1\,\text{max.}}$  = 1  $\mu F$  If  $R_{1}$  is in  $M\Omega$  and  $C_{1}$  in pF,  $T_{TO}$  will be in ms.

A resistor decreases and a capacitor increases the interval to timeout. Excellent temperature stability of  $T_{TO}$  can be achieved by using external components. A precise square wave of period  $2\times T_{TO}$  is generated at the outputs  $\overline{RES}$  and RES when  $\overline{TCL}$  is tied to either  $V_{DD}$  or  $V_{SS}.$  The oscillator and watchdog timer start running when both  $V_{IN}$  is greater than  $V_{SH}$  (see Fig. 6) and  $V_{DD}$  is greater than  $V_{ON}$  (see Fig. 3).

They will remain running while both  $V_{\text{IN}}$  is greater than  $V_{\text{RL}}$  and  $V_{\text{DD}}$  is greater than  $V_{\text{OFF}}$  (see Fig. 3).

#### Timer Clearing and RES /RES Action

A negative edge or a negative pulse at the  $\overline{TCL}$  input for longer than 150 ns will reset the timer and set RES and RES inactive. If a further  $\overline{TCL}$  signal edge or pulse is applied before  $T_{TO}$  timeout,  $\overline{RES}$  and RES will remain inactive and the timer will again be reset to zero (see Fig. 5). If no  $\overline{TCL}$  signal is applied before the  $T_{TO}$  timeout,  $\overline{RES}$  and RES will start to generate square waves of period 2  $\times$   $T_{TO}$  starting with the inactive state. The watchdog will remain in this state until the next  $\overline{TCL}$  signal appears, or until a fresh power-up sequence.

#### **Combined Voltage and Timer Action**

The combination of voltage and timer actions is illustrated by the sequence of events shown in Fig. 6. One timeout period after  $V_{\text{IN}}$  reaches  $V_{\text{SH}}$ , during power-up,  $\overline{\text{RES}}$  and RES go inactive. A  $\overline{\text{TCL}}$  pulse will have no effect until this power-up sequence the watchdog timer starts acting. If no  $\overline{\text{TCL}}$  pulse occurs,  $\overline{\text{RES}}$  and RES go active after one timeout period  $T_{\text{TO}}$ . After each subsequent timeout period, without a timer clear pulse at  $\overline{\text{TCL}}$ ,  $\overline{\text{RES}}$  and RES change polarity providing square wave signals. A  $\overline{\text{TCL}}$  pulse clears the watchdog timer and causes  $\overline{\text{RES}}$  and RES to go inactive. A voltage drop below the  $V_{\text{RL}}$  level overrides the timer and immediately forces  $\overline{\text{RES}}$ , RES and  $\overline{\text{SAVE}}$  active. Any further  $\overline{\text{TCL}}$  pulse has no effect until the next power-up sequence is completed.

# Typical Applications Microprocessor Watchdog with Power-On Reset and Voltage Monitor

#### **Voltage Monitor with Spike Suppression**

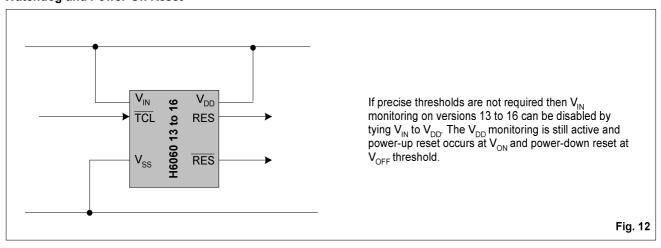

#### Watchdog and Power-On Reset

#### **External Programming of RC Oscillator**

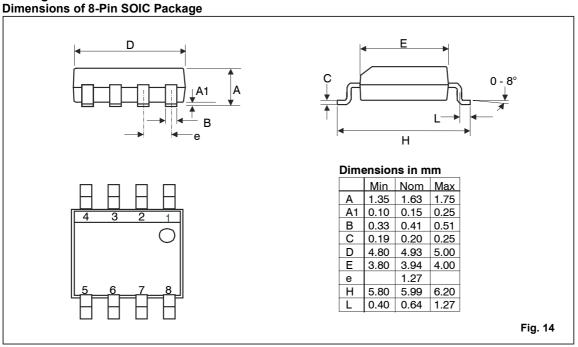

Package Information

#### **Ordering Information**

When ordering please specify complete part number.

| Part Number  | Version | Threshold (see Table 4) | Output    | Package    | Delivery Form | Package Marking<br>(first line) | Temperature    |                |

|--------------|---------|-------------------------|-----------|------------|---------------|---------------------------------|----------------|----------------|

| H6060V15SO8A | V15     | 1.05                    | Open      | 8-pin SOIC | Stick         | 606015                          |                |                |

| H6060V15SO8B | VIS     | 1.95                    | drain     | 8-pin SOIC | Tape&Reel     | 606015                          | 1              |                |

| H6060V14SO8A | V14     | 2.00                    |           | 8-pin SOIC | Stick         | 606014                          | -40°C to °85°C |                |

| H6060V14SO8B | V 14    | 2.00                    | 2.00      | Duch null  | 8-pin SOIC    | Tape&Reel                       | 606014         | 1-40 C tO 65 C |

| H6060V16SO8A | V/4.C   | 1.05                    | Push-pull | 8-pin SOIC | Stick         | 606016                          |                |                |

| H6060V16SO8B | V16     | 1.95                    |           | 8-pin SOIC | Tape&Reel     | 606016                          |                |                |

Note: Other versions are no longer available

EM Microelectronic-Marin SA cannot assume responsibility for use of any circuitry described other than circuitry entirely embodied in an EM Microelectronic-Marin SA product. EM Microelectronic-Marin SA reserves the right to change the circuitry and specifications without notice at any time. You are strongly urged to ensure that the information given has not been superseded by a more up-to-date version.