## 捷多邦,专业PCB打样工厂,24**亿世7135亿**,TLC7135C 4 1/2-DIGIT PRECISION ANALOG-TO-DIGITAL CONVERTERS

DW OR N PACKAGE

SLAS074D - DECEMBER 1986 - REVISED SEPTEMBER 2003

- Zero Reading for 0-V Input

- Precision Null Detection With True Polarity at Zero

- 1-pA Typical Input Current

- True Differential Input

- Multiplexed Binary-Coded-Decimal (BCD)

Output

- Low Rollover Error: ±1 Count Max

- Control Signals Allow Interfacing With UARTs or Microprocessors

- Autoranging Capability With Over-and Under-Range Signals

- TTL-Compatible Outputs

- Second Source to Teledyne TSC7135, Intersil ICL7135, Maxim ICL7135, and Siliconix Si7135

- CMOS Technology

#### (TOP VIEW) 28 UNDER RANGE Vcc-27 OVER RANGE REF [ ANLG COMMON ☐ 3 26 STROBE INT OUT 4 25 RUN/HOLD AUTO ZERO [ 5 24 DGTL GND BUFF OUT [ 23 POLARITY 22 T CLK C<sub>ref</sub>\_ [ 21 T BUSY C<sub>ref+</sub> [] 8 20 D1 IN – [] IN+ **1**10 19 **∏** D2 18**∏** D3 11 $V_{CC+}$ 17 D4 D5 [ 12 16 B8 B1 | 13 15 B4 B2

#### **DESCRIPTION**

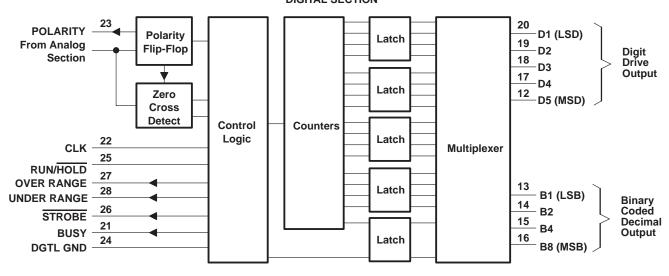

The ICL7135C and TLC7135C converters are manufactured with Texas Instruments highly efficient CMOS technology. These 4 1/2-digit, dual-slope-integrating, analog-to-digital converters (ADCs) are designed to provide interfaces to both a microprocessor and a visual display. The digit-drive outputs D1 through D4 and multiplexed binary-coded-decimal outputs B1, B2, B4, and B8 provide an interface for LED or LCD decoder/drivers as well as microprocessors.

The ICL7135C and TLC7135C offer 50-ppm (one part in 20,000) resolution with a maximum linearity error of one count. The zero error is less than 10  $\mu$ V and zero drift is less than 0.5  $\mu$ V/°C. Source-impedance errors are minimized by low input current (less than 10 pA). Rollover error is limited to  $\pm 1$  count.

The BUSY, STROBE, RUN/HOLD, OVER RANGE, and UNDER RANGE control signals support microprocessor-based measurement systems. The control signals also can support remote data acquisition systems with data transfer through universal asynchronous receiver transmitters (UARTs).

The ICL7135C and TLC7135C are characterized for operation from 0°C to 70°C.

#### **AVAILABLE OPTIONS**

|             | PACKAGE                 |                    |  |  |  |  |  |  |

|-------------|-------------------------|--------------------|--|--|--|--|--|--|

| TA          | PLASTIC DIP<br>(N)      | SMALL OUTLINE (DW) |  |  |  |  |  |  |

| 0°C to 70°C | ICL7135CN               | THE WA             |  |  |  |  |  |  |

| 0 0 10 70 0 | TLC713 <mark>5CN</mark> | TLC7135CDW         |  |  |  |  |  |  |

Caution. These devices have limited built-in protection. The leads should be shorted together or the device placed in conductive foam during storage or handliling to prevent electrostatic damage to the MOS gates.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

#### SLAS074D - DECEMBER 1986 - REVISED SEPTEMBER 2003

## **FUNCTIONAL BLOCK DIAGRAM**

#### **DIGITAL SECTION**

#### **ANALOG SECTION**

#### **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range unless otherwise noted<sup>(1)</sup>

|                                                                         | UNIT                                   |

|-------------------------------------------------------------------------|----------------------------------------|

| Supply voltage (V <sub>CC+</sub> with respect to V <sub>CC-</sub> )     | 15 V                                   |

| Analog input voltage (IN – or IN+)                                      | V <sub>CC</sub> - to V <sub>CC</sub> + |

| Reference voltage range                                                 | V <sub>CC</sub> - to V <sub>CC</sub> + |

| Clock input voltage range                                               | 0 V to V <sub>CC+</sub>                |

| Operating free-air temperature range, T <sub>A</sub>                    | 0°C to 70°C                            |

| Storage temperature range, T <sub>Stg</sub>                             | −65°C to 150°C                         |

| Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds: N package | 260°C                                  |

<sup>(1)</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### RECOMMENDED OPERATING CONDITIONS

|                                                              | MIN                 | NOM | MAX                   | UNIT |

|--------------------------------------------------------------|---------------------|-----|-----------------------|------|

| Supply voltage, V <sub>CC+</sub>                             | 4                   | 5   | 6                     | V    |

| Supply voltage, V <sub>CC</sub> _                            | -3                  | -5  | -8                    | V    |

| Reference voltage, V <sub>ref</sub>                          |                     | 1   |                       | V    |

| High-level input voltage, CLK, RUN/HOLD, VIH                 | 2.8                 |     |                       | V    |

| Low-level input voltage, CLK, RUN/HOLD, V <sub>IL</sub>      |                     |     | 0.8                   | V    |

| Differential input voltage, V <sub>ID</sub>                  | V <sub>CC</sub> _+1 |     | V <sub>CC+</sub> -0.5 | V    |

| Maximum operating frequency, f <sub>Clock</sub> (see Note 1) | 1.2                 | 2   |                       | MHz  |

| Operating free-air temperature range, TA                     | 0                   |     | 70                    | °C   |

NOTE 1: Clock frequency range extends down to 0 Hz.

#### **ELECTRICAL CHARACTERISTICS**

$V_{CC+} = 5 \text{ V}, V_{CC-} = 5 \text{ V}, V_{ref} = 1 \text{ V}, f_{clock} = 120 \text{ kHz}, T_A = 25^{\circ}C \text{ (unless otherwise noted)}$

|                     | PARAMETER                            |                       | TEST                                     | CONDITIONS                               | MIN   | TYP  | MAX   | UNIT |

|---------------------|--------------------------------------|-----------------------|------------------------------------------|------------------------------------------|-------|------|-------|------|

| .,                  |                                      | D1-D5, B1, B2, B4, B8 | $I_{O} = -1 \text{ m}$                   | $I_O = -1 \text{ mA}$                    |       |      | 5     | .,   |

| VOH                 | High-level output voltage            | Other outputs         | $I_{O} = -10 \mu$                        | ιA                                       | 4.9   |      | 5     | V    |

| VOL                 | Low-level output voltage             |                       | I <sub>O</sub> = 1.6 m                   | ıΑ                                       |       |      | 0.4   | V    |

| V <sub>ON(PP)</sub> | Peak-to-peak output noise voltage (s | $V_{ID} = 0$ ,        | Full scale = 2 V                         |                                          | 15    |      | μV    |      |

| ανο                 | Zero-reading temperature coefficient | $V_{ID} = 0$ ,        | $0^{\circ}C \leq T_{A} \leq 70^{\circ}C$ |                                          | 0.5   | 2    | μV/°C |      |

| lін                 | High-level input current             | V <sub>I</sub> = 5 V, | $0^{\circ}C \le T_A \le 70^{\circ}C$     |                                          | 0.1   | 10   | μΑ    |      |

| I∣∟                 | Low-level input current              | V <sub>I</sub> = 0 V, | $0^{\circ}C \le T_A \le 70^{\circ}C$     |                                          | -0.02 | -0.1 | mA    |      |

|                     |                                      |                       | 1/ 0                                     | T <sub>A</sub> = 25°C                    |       | 1    | 10    | A    |

| -                   | Input leakage current, IN – and IN+  | $V_{ID} = 0$          | $0^{\circ}C \leq T_{A} \leq 70^{\circ}C$ |                                          |       | 250  | pА    |      |

|                     | Davidson according to the second     |                       | , ,                                      | T <sub>A</sub> = 25°C                    |       | 1    | 2     | 4    |

| ICC+                | Positive supply current              |                       | $f_{clock} = 0$                          | $0^{\circ}C \leq T_{A} \leq 70^{\circ}C$ |       |      | 3     | mA   |

|                     | Name Construction                    |                       | , ,                                      | T <sub>A</sub> = 25°C                    |       | -0.8 | -2    | 4    |

| ICC-                | Negative supply current              |                       | $f_{clock} = 0$                          | $0^{\circ}C \leq T_{A} \leq 70^{\circ}C$ |       |      | -3    | mA   |

| C <sub>pd</sub>     | Power dissipation capacitance        |                       | See Note 2                               | 2                                        | _     | 40   |       | pF   |

NOTES: 1. This is the peak-to-peak value that is not exceeded 95% of the time.

2. Factor-relating clock frequency to increase in supply current. At  $V_{CC+} = 5 \text{ V}$ ,  $I_{CC+} = I_{CC+}(f_{clock} = 0) + C_{pd} \times 5 \text{ V} \times f_{clock}$

## ICL7135C, TLC7135C 4 1/2-DIGIT PRECISION ANALOG-TO-DIGITAL CONVERTERS

SLAS074D - DECEMBER 1986 - REVISED SEPTEMBER 2003

## **OPERATING CHARACTERISTICS**

$V_{CC+} = 5 \text{ V}, V_{CC-} = 5 \text{ V}, V_{ref} = 1 \text{ V}, f_{clock} = 120 \text{ kHz}, T_A = 25^{\circ}\text{C}$  (unless otherwise noted)

|                                                          | PARAMETER                                                           | TEST CONDITIONS                                                               | MIN     | TYP     | MAX    | UNIT               |

|----------------------------------------------------------|---------------------------------------------------------------------|-------------------------------------------------------------------------------|---------|---------|--------|--------------------|

| αFS                                                      | Full-scale temperature coefficient (see Note 1)                     | $V_{ID} = 2 \text{ V},  0^{\circ}\text{C} \leq T_{A} \leq 70^{\circ}\text{C}$ |         |         | 5      | ppm/°C             |

| EL                                                       | Linearity error                                                     | $-2 \text{ V} \leq \text{V}_{\text{ID}} \leq 2 \text{ V}$                     |         | 0.5     |        | count              |

| E <sub>D</sub> Differential linearity error (see Note 2) |                                                                     | $-2 \text{ V} \leq \text{V}_{\text{ID}} \leq 2 \text{ V}$                     |         | 0.01    |        | LSB                |

| E <sub>FS</sub>                                          | $\pm\mbox{Full-scale}$ symmetry error (rollover error) (see Note 3) | $V_{ID} = \pm 2 V$                                                            |         | 0.5     | 1      | count              |

|                                                          | Display reading with 0-V input                                      | $V_{ID} = 0,$ $0^{\circ}C \le T_A \le 70^{\circ}C$                            | -0.0000 | ±0.0000 | 0.0000 | Digital<br>Reading |

|                                                          | Display reading in ratiometric operation                            | $V_{ID} = V_{ref}$ , $T_A = 25^{\circ}C$                                      | 0.9998  | 0.9999  | 1.0000 | Digital            |

|                                                          | Display reading in ratiometric operation                            | $0^{\circ}C \le T_A \le 70^{\circ}C$                                          | 0.9995  | 0.9999  | 1.0005 | Reading            |

NOTES: 1. This parameter is measured with an external reference having a temperature coefficient of less than 0.01 ppm/°C.

- 2. The magnitude of the difference between the worst case step of adjacent counts and the ideal step.

- 3. Rollover error is the difference between the absolute values of the conversion for 2 V and -2 V.

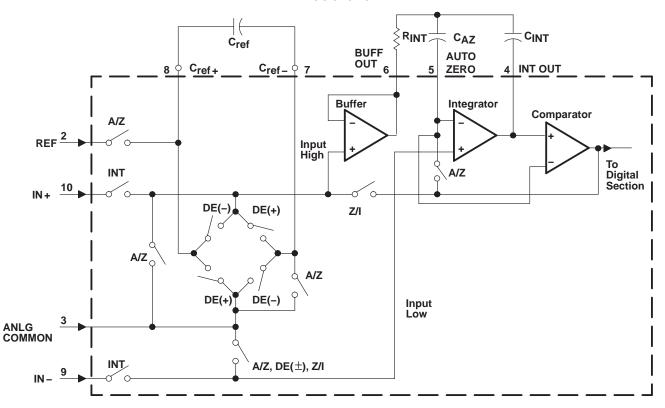

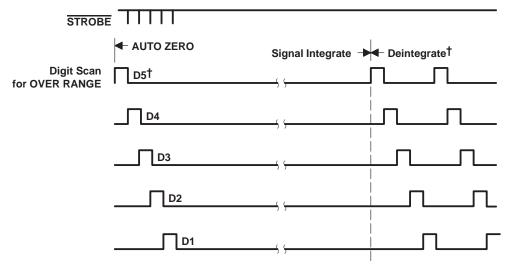

## **TIMING DIAGRAMS**

† Delay between BUSY going low and the first STROBE pulse is dependent upon the analog input.

Figure 1

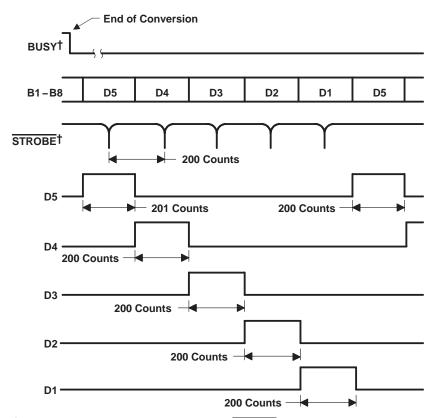

Figure 2

Figure 3

SLAS074D - DECEMBER 1986 - REVISED SEPTEMBER 2003

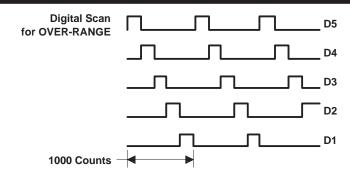

† First D5 of AUTO ZERO and deintegrate is one count longer.

Figure 4

#### PRINCIPLES OF OPERATION

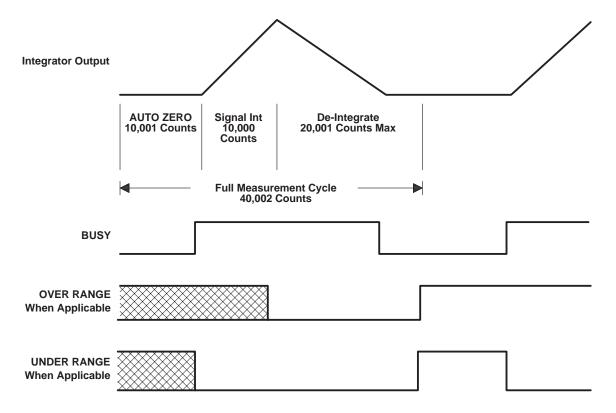

A measurement cycle for the ICL7135C and TLC7135C consists of the following four phases.

- Auto-Zero Phase. The internal IN+ and IN- inputs are disconnected from the terminals and internally connected to ANLG COMMON. The reference capacitor is charged to the reference voltage. The system is configured in a closed loop and the auto-zero capacitor is charged to compensate for offset voltages in the buffer amplifier, integrator, and comparator. The auto-zero accuracy is limited only by the system noise, and the overall offset, as referred to the input, is less than 10 μV.

- 2. Signal Integrate Phase. The auto-zero loop is opened and the internal IN+ and IN- inputs are connected to the external terminals. The differential voltage between these inputs is integrated for a fixed period of time. When the input signal has no return with respect to the converter power supply, IN- can be tied to ANLG COMMON to establish the correct common-mode voltage. Upon completion of this phase, the polarity of the input signal is recorded.

- 3. Deintegrate Phase. The reference is used to perform the deintegrate task. The internal IN– is internally connected to ANLG COMMON and IN+ is connected across the previously charged reference capacitor. The recorded polarity of the input signal ensures that the capacitor is connected with the correct polarity so that the integrator output polarity returns to zero. The time required for the output to return to zero is proportional to the amplitude of the input signal. The return time is displayed as a digital reading and is determined by the equation  $10,000 \times (V_{ID}/V_{ref})$ . The maximum or full-scale conversion occurs when  $V_{ID}$  is two times  $V_{ref}$ .

- 4. Zero Integrator Phase. The internal IN is connected to ANLG COMMON. The system is configured in a closed loop to cause the integrator output to return to zero. Typically, this phase requires 100 to 200 clock pulses. However, after an over-range conversion, 6200 pulses are required.

#### **DESCRIPTION OF ANALOG CIRCUITS**

#### **Input Signal Range**

The common mode range of the input amplifier extends from 1 V above the negative supply to 1 V below the positive supply. Within this range, the common-mode rejection ratio (CMRR) is typically 86 dB. Both differential and common-mode voltages cause the integrator output to swing. Therefore, care must be exercised to ensure that the integrator output does not become saturated.

## **Analog Common**

Analog common (ANLG COMMON) is connected to the internal IN – during the auto-zero, deintegrate, and zero integrator phases. When IN – is connected to a voltage that is different from analog common during the signal integrate phase, the resulting common-mode voltage is rejected by the amplifier. However, in most applications, IN – is set at a known fixed voltage (i.e., power supply common for instance). In this application, analog common should be tied to the same point, thus removing the common-mode voltage from the converter. Removing the common-mode voltage in this manner slightly increases conversion accuracy.

#### Reference

The reference voltage is positive with respect to analog common. The accuracy of the conversion result is dependent upon the quality of the reference. Therefore, to obtain a high accuracy conversion, a high quality reference should be used.

#### **DESCRIPTION OF DIGITAL CIRCUITS**

## **RUN/HOLD** Input

When RUN/HOLD is high or open, the device continuously performs measurement cycles every 40,002 clock pulses. When this input is taken low, the integrated circuit continues to perform the ongoing measurement cycle and then hold the conversion reading for as long as the terminal is held low. When the terminal is held low after completion of a measurement cycle, a short positive pulse (greater than 300 ns) initiates a new measurement cycle. When this positive pulse occurs before the completion of a measurement cycle, it will not be recognized. The first STROBE pulse, which occurs 101 counts after the end of a measurement cycle, is an indication of the completion of a measurement cycle. Thus, the positive pulse could be used to trigger the start of a new measurement after the first STROBE pulse.

## **STROBE** Input

Negative going pulses from this input transfer the BCD conversion data to external latches, UARTs, or microprocessors. At the end of the measurement cycle, STROBE goes high and remains high for 201 counts. The most significant digit (MSD) BCD bits are placed on the BCD terminals. After the first 101 counts, halfway through the duration of output D1–D5 going high, the STROBE terminal goes low for 1/2 clock pulse width. The placement of the STROBE pulse at the midpoint of the D5 high pulse allows the information to be latched into an external device on either a low-level or an edge. Such placement of the STROBE pulse also ensures that the BCD bits for the second MSD are not yet competing for the BCD lines and latching of the correct bits is ensured. The above process is repeated for the second MSD and the D4 output. Similarly, the process is repeated through the least significant digit (LSD). Subsequently, inputs D5 through D1 and the BCD lines continue scanning without the inclusion of STROBE pulses. This subsequent continuous scanning causes the conversion results to be continuously displayed. Such subsequent scanning does not occur when an over-range condition occurs.

## ICL7135C, TLC7135C 4 1/2-DIGIT PRECISION ANALOG-TO-DIGITAL CONVERTERS

SLAS074D - DECEMBER 1986 - REVISED SEPTEMBER 2003

### **BUSY Output**

The BUSY output goes high at the beginning of the signal integrate phase. BUSY remains high until the first clock pulse after zero crossing or at the end of the measurement cycle when an over-range condition occurs. It is possible to use the BUSY terminal to serially transmit the conversion result. Serial transmission can be accomplished by ANDing the BUSY and CLOCK signals and transmitting the ANDed output. The transmitted output consists of 10,001 clock pulses, which occur during the signal integrate phase, and the number of clock pulses that occur during the deintegrate phase. The conversion result can be obtained by subtracting 10,001 from the total number of clock pulses.

#### **OVER-RANGE Output**

When an over-range condition occurs, this terminal goes high after the BUSY signal goes low at the end of the measurement cycle. As previously noted, the BUSY signal remains high until the end of the measurement cycle when an over-range condition occurs. The OVER RANGE output goes high at the end of BUSY and goes low at the beginning of the deintegrate phase in the next measurement cycle.

## **UNDER-RANGE Output**

At the end of the BUSY signal, this terminal goes high when the conversion result is less than or equal to 9% (count of 1800) of the full-scale range. The UNDER-RANGE output is brought low at the beginning of the signal integrate phase of the next measurement cycle.

#### **POLARITY Output**

The POLARITY output is high for a positive input signal and updates at the beginning of each deintegrate phase. The polarity output is valid for all inputs including  $\pm 0$  and OVER RANGE signals.

#### Digit-Drive (D1, D2, D4 and D5) Outputs

Each digit-drive output (D1 through D5) sequentially goes high for 200 clock pulses. This sequential process is continuous unless an over-range occurs. When an over-range occurs, all of the digit-drive outputs are blanked from the end of the strobe sequence until the beginning of the deintegrate phase (when the sequential digit-drive activation begins again). The blanking activity during an over-range condition can cause the display to flash and indicate the over-range condition.

#### **BCD Outputs**

The BCD bits (B1, B2, B4 and B8) for a given digit are sequentially activated on these outputs. Simultaneously, the appropriate digit-drive line for the given digit is activated.

#### System Aspects

## **Integrating Resistor**

The value of the integrating resistor ( $R_{INT}$ ) is determined by the full-scale input voltage and the output current of the integrating amplifier. The integrating amplifier can supply 20  $\mu$ A of current with negligible nonlinearity. The equation for determining the value of this resistor is:

$$R_{INT} = \frac{Full Scale Voltage}{I_{INT}}$$

Integrating amplifier current,  $I_{INT}$ , from 5 to 40  $\mu$ A yields good results. However, the nominal and recommended current is 20  $\mu$ A.

## **Integrating Capacitor**

The product of the integrating resistor and capacitor should be selected to give the maximum voltage swing without causing the integrating amplifier output to saturate and get too close to the power supply voltages. When the amplifier output is within 0.3 V of either supply, saturation occurs. With  $\pm 5$ -V supplies and ANLG COMMON connected to ground, the designer should design for a  $\pm 3.5$ -V to  $\pm 4$ -V integrating amplifier swing. A nominal capacitor value is 0.47  $\mu$ F. The equation for determining the value of the integrating capacitor ( $C_{INT}$ ) is:

$$C_{INT} = \frac{10,000 \times Clock Period \times I_{INT}}{Integrator Output Voltage Swing}$$

where

$I_{INT}$  is nominally 20  $\mu$ A.

Capacitors with large tolerances and high dielectric absorption can induce conversion inaccuracies. A capacitor that is too small could cause the integrating amplifier to saturate. High dielectric absorption causes the effective capacitor value to be different during the signal integrate and deintegrate phases. Polypropylene capacitors have very low dielectric absorption. Polystyrene and polycarbonate capacitors have higher dielectric absorption, but also work well.

## **Auto-Zero and Reference Capacitor**

Large capacitors tend to reduce noise in the system. Dielectric absorption is unimportant except during power up or overload recovery. Typical values are 1 µF.

## Reference Voltage

For high-accuracy absolute measurements, a high quality reference should be used.

#### **Rollover Resistor and Diode**

The ICL7135C and TLC7135C have a small rollover error; however, it can be corrected. The correction is to connect the cathode of any silicon diode to INT OUT and the anode to a resistor. The other end of the resistor is connected to ANLG COMMON or ground. For the recommended operating conditions, the resistor value is  $100~\mathrm{k}\Omega$ . This value may be changed to correct any rollover error that has not been corrected. In many noncritical applications the resistor and diode are not needed.

#### **Maximum Clock Frequency**

For most dual-slope A/D converters, the maximum conversion rate is limited by the frequency response of the comparator. In this circuit, the comparator follows the integrator ramp with a 3- $\mu$ s delay. Therefore, with a 160-kHz clock frequency (6- $\mu$ s period), half of the first reference integrate clock period is lost in delay. Hence, the meter reading changes from 0 to 1 with a 50- $\mu$ V input, 1 to 2 with a 150- $\mu$ V input, 2 to 3 with a 250- $\mu$ V input, etc. This transition at midpoint is desirable; however, when the clock frequency is increased appreciably above 160 kHz, the instrument flashes 1 on noise peaks even when the input is shorted. The above transition points assume a 2-V input range is equivalent to 20,000 clock cycles.

When the input signal is always of one polarity, comparator delay need not be a limitation. Clock rates of 1 MHz are possible since nonlinearity and noise do not increase substantially with frequency. For a fixed clock frequency, the extra count or counts caused by comparator delay are a constant and can be subtracted out digitally.

For signals with both polarities, the clock frequency can be extended above 160 kHz without error by using a low value resistor in series with the integrating capacitor. This resistor causes the integrator to jump slightly towards the zero-crossing level at the beginning of the deintegrate phase, and thus compensates for the comparator delay. This series resistor should be 10  $\Omega$  to 50  $\Omega$ . This approach allows clock frequencies up to 480 kHz.

## ICL7135C, TLC7135C 4 1/2-DIGIT PRECISION ANALOG-TO-DIGITAL CONVERTERS

SLAS074D - DECEMBER 1986 - REVISED SEPTEMBER 2003

## **Minimum Clock Frequency**

The minimum clock frequency limitations result from capacitor leakage from the auto-zero and reference capacitors. Measurement cycles as high as 10 µs are not influenced by leakage error.

## Rejection of 50-Hz or 60-Hz Pickup

To maximize the rejection of 50-Hz or 60-Hz pickup, the clock frequency should be chosen so that an integral multiple of 50-Hz or 60-Hz periods occur during the signal integrate phase. To achieve rejection of these signals, some clock frequencies that can be used are:

50 Hz: 250, 166.66, 125, 100 kHz, etc.

60 Hz: 300, 200, 150, 120, 100, 40, 33.33 kHz, etc.

## Zero-Crossing Flip-Flop

This flip-flop interrogates the comparator's zero-crossing status. The interrogation is performed after the previous clock cycle and the positive half of the ongoing clock cycle has occurred, so any comparator transients that result from the clock pulses do not affect the detection of a zero-crossing. This procedure delays the zero-crossing detection by one clock cycle. To eliminate the inaccuracy, which is caused by this delay, the counter is disabled for one clock cycle at the beginning of the deintegrate phase. Therefore, when the zero-crossing is detected one clock cycle later than the zero-crossing actually occurs, the correct number of counts is displayed.

#### Noise

The peak-to-peak noise around zero is approximately 15  $\mu$ V (peak-to-peak value not exceeded 95% of the time). Near full scale, this value increases to approximately 30  $\mu$ V. Much of the noise originates in the auto-zero loop, and is proportional to the ratio of the input signal to the reference.

#### **Analog and Digital Grounds**

For high-accuracy applications, ground loops must be avoided. Return currents from digital circuits must not be sent to the analog ground line.

#### **Power Supplies**

The ICL7135C and TLC7135C are designed to work with  $\pm 5$ -V power supplies. However, 5-V operation is possible when the input signal does not vary more than  $\pm 1.5$  V from midsupply.

## PACKAGE OPTION ADDENDUM

21-Dec-2007

#### **PACKAGING INFORMATION**

| Orderable Device | Status <sup>(1)</sup> | Package<br>Type | Package<br>Drawing | Pins | Package<br>Qty | e Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> |

|------------------|-----------------------|-----------------|--------------------|------|----------------|---------------------------|------------------|------------------------------|

| ICL7135CN        | ACTIVE                | PDIP            | N                  | 28   | 13             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | N / A for Pkg Type           |

| ICL7135CNG4      | ACTIVE                | PDIP            | N                  | 28   | 13             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | N / A for Pkg Type           |

| TLC7135CDW       | ACTIVE                | SOIC            | DW                 | 28   | 20             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

| TLC7135CDWG4     | ACTIVE                | SOIC            | DW                 | 28   | 20             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

| TLC7135CDWR      | ACTIVE                | SOIC            | DW                 | 28   | 1000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

| TLC7135CDWRG4    | ACTIVE                | SOIC            | DW                 | 28   | 1000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

| TLC7135CN        | ACTIVE                | PDIP            | N                  | 28   | 13             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | N / A for Pkg Type           |

| TLC7135CNG4      | ACTIVE                | PDIP            | N                  | 28   | 13             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | N / A for Pkg Type           |

<sup>&</sup>lt;sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

**NRND:** Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

TBD: The Pb-Free/Green conversion plan has not been defined.

**Pb-Free** (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

(3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

## **PACKAGE MATERIALS INFORMATION**

11-Mar-2008

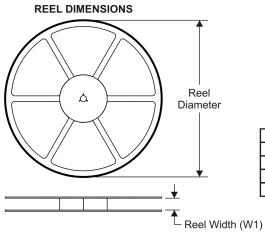

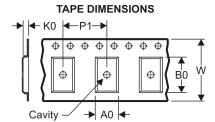

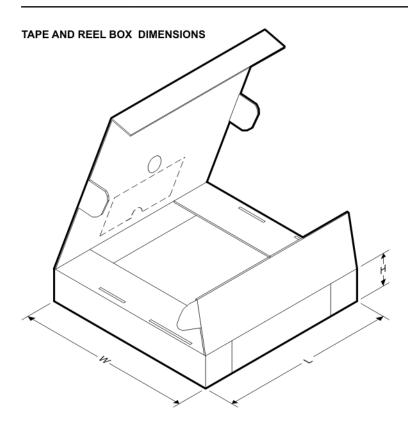

## TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

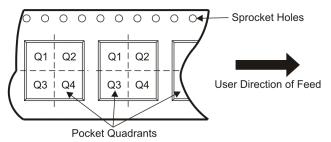

## QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

## \*All dimensions are nominal

| Device      | _    | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-------------|------|--------------------|----|------|--------------------------|--------------------------|---------|---------|---------|------------|-----------|------------------|

| TLC7135CDWR | SOIC | DW                 | 28 | 1000 | 330.0                    | 32.4                     | 11.35   | 18.67   | 3.1     | 16.0       | 32.0      | Q1               |

11-Mar-2008

## \*All dimensions are nominal

| Device      | Device Package Type |    | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |  |

|-------------|---------------------|----|------|------|-------------|------------|-------------|--|

| TLC7135CDWR | SOIC                | DW | 28   | 1000 | 346.0       | 346.0      | 49.0        |  |

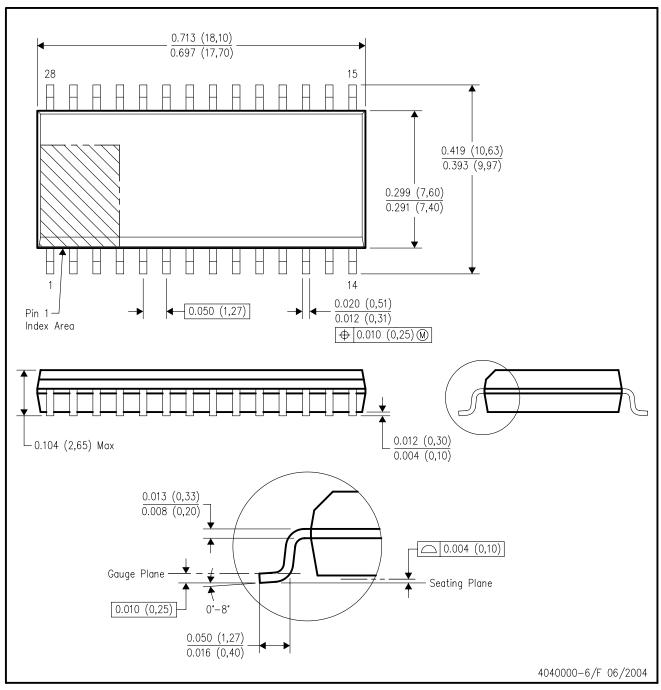

# DW (R-PDSO-G28)

## PLASTIC SMALL-OUTLINE PACKAGE

NOTES:

- A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion not to exceed 0.006 (0,15).

- D. Falls within JEDEC MS-013 variation AE.

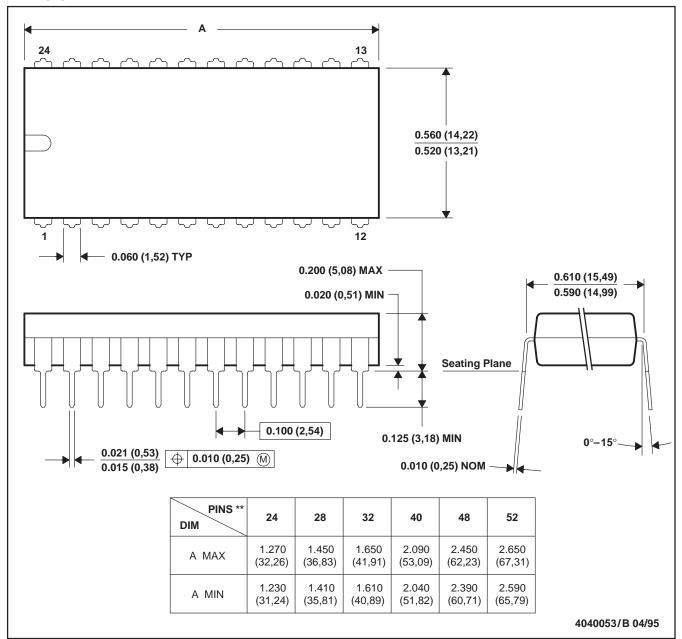

## N (R-PDIP-T\*\*)

## PLASTIC DUAL-IN-LINE PACKAGE

## 24 PIN SHOWN

NOTES: A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. Falls within JEDEC MS-011

- D. Falls within JEDEC MS-015 (32 pin only)

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

**Products** Amplifiers amplifier.ti.com Data Converters dataconverter.ti.com DSP dsp.ti.com Clocks and Timers www.ti.com/clocks Interface interface.ti.com Logic logic.ti.com Power Mgmt power.ti.com Microcontrollers microcontroller.ti.com RFID www.ti-rfid.com RF/IF and ZigBee® Solutions www.ti.com/lprf

Applications Audio www.ti.com/audio Automotive www.ti.com/automotive Broadband www.ti.com/broadband Digital Control www.ti.com/digitalcontrol Medical www.ti.com/medical Military www.ti.com/military Optical Networking www.ti.com/opticalnetwork Security www.ti.com/security Telephony www.ti.com/telephony Video & Imaging www.ti.com/video Wireless www.ti.com/wireless

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2008, Texas Instruments Incorporated