# Impala Linear Corporation

# ILC7080/81

50/100mA SOT-23 CMOS RF LDO™ Regulators

### **General Description**

The ILC7080/81 are 50 or 100mA low dropout (LDO) voltage regulators designed to provide a high performance solution to low power systems.

The devices offer a typical combination of low dropout and low quiescent current expected of CMOS parts, while uniquely providing the low noise and high ripple rejection characteristics usually only associated with bipolar LDO regulators.

The devices have been optimized to meet the needs of modern wireless communications design; Low noise, low dropout, small size, high peak current, high noise immunity. The ILC7080/81 are designed to make use of low cost ceramic capacitors while outperforming other devices that require tantalum capacitors.

#### **Features**

- Ultra low 1mV dropout per 1mA load

- 1% output voltage accuracy

- Uses low ESR ceramic output capacitor to minimize noise and output ripple

- Only 100µA ground current at 100mA load

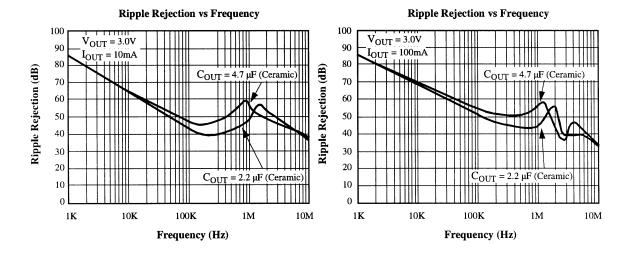

- Ripple rejection up to 85dB at 1kHz, 60dB at 1MHz

- Less than  $80\mu V_{RMS}$  noise at BW = 100Hz to 100kHz

- Excellent line and load transient response

- Over current / over temperature protection

- Guaranteed up to 80/150mA output current

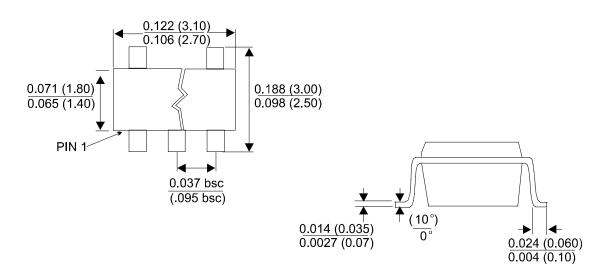

- Industry standard five lead SOT-23 package

- Fixed 2.85V, 3.0V, 3.3V, 3.6V, 4.7V, 5.0V and adjustable output voltage options

- Metal mask option available for custom voltages between 2.5 to 10V

### **Applications**

- Cellular phones

- Wireless communicators

- PDAs / palmtops / organizers

- Battery powered portable electronics

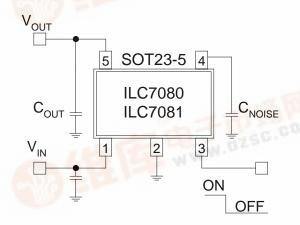

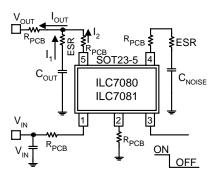

### Typical Circuit

| Ordering Information (T <sub>A</sub> = -40°C to +85°C) |                           |  |  |  |  |  |

|--------------------------------------------------------|---------------------------|--|--|--|--|--|

| ILC7080AIM5-xx                                         | 50mA, fixed voltage       |  |  |  |  |  |

| ILC7080AIM5-ADJ                                        | 50mA adjustable voltage   |  |  |  |  |  |

| ILC7081AIM5-xx                                         | 100mA, fixed voltage      |  |  |  |  |  |

| ILC7081AIM5-ADJ                                        | 100mA, adjustable voltage |  |  |  |  |  |

**Note:** Fixed voltage options are defined by 2-digit code as shown in the package markings information section of the datasheet.

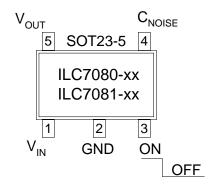

## Pin Description ILC7081/81-xx (fixed voltage version)

| Pin<br>Number | Pin Name           | Pin Description                                                                                                                                               |  |  |  |

|---------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1             | V <sub>IN</sub>    | Connect direct to supply                                                                                                                                      |  |  |  |

| 2             | GND                | Ground pin. Local ground for C <sub>NOISE</sub> and C <sub>OUT</sub> .                                                                                        |  |  |  |

| 3             | ON/OFF             | By applying less than 0.4V to this pin the device will be turned off.                                                                                         |  |  |  |

| 4             | C <sub>NOISE</sub> | Optional noise bypass capacitor may be connected between this pin and GND (pin 2). Do not connect $C_{\text{NOISE}}$ directly to the main power ground plane. |  |  |  |

| 5             | V <sub>OUT</sub>   | Output Voltage. Connect C <sub>OUT</sub> between this pin and GND (pin 2)                                                                                     |  |  |  |

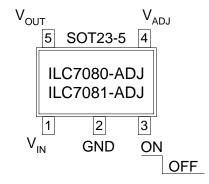

# Pin Description ILC7081/81-ADJ (adjustable voltage version)

| Pin<br>Number | Pin Name         | Pin Description                                                                                    |  |  |  |

|---------------|------------------|----------------------------------------------------------------------------------------------------|--|--|--|

| 1             | V <sub>IN</sub>  | Connect direct to supply                                                                           |  |  |  |

| 2             | GND              | Ground pin. Local ground for C <sub>NOISE</sub> and C <sub>OUT</sub> .                             |  |  |  |

| 3             | ON/OFF           | By applying less than 0.4V to this pin the device will be turned off.                              |  |  |  |

| 4             | $V_{ADJ}$        | Voltage feedback pin to set the adjustable output voltage. Do not connect a capacitor to this pin. |  |  |  |

| 5             | V <sub>OUT</sub> | Output Voltage. Connect C <sub>OUT</sub> between this pin and GND (pin 2)                          |  |  |  |

# Pin Package Configurations

### Absolute Maximum Ratings (Note 1)

| Parameter                     | Symbol              | Ratings                      | Units |

|-------------------------------|---------------------|------------------------------|-------|

| Input voltage                 | V <sub>IN</sub>     | -0.3 to +13.5                | V     |

| On/Off Input voltage          | $V_{ON/OFF}$        | -0.3 to V <sub>IN</sub>      |       |

| Output Current                | I <sub>OUT</sub>    | Short circuit protected      | mA    |

| Output voltage                | $V_{OUT}$           | -0.3 to V <sub>IN</sub> +0.3 | V     |

| Package Power Dissipation     | $P_{D}$             | 250                          | mW    |

| (SOT-23-5)                    |                     | (Internally Limited)         |       |

| Maximum Junction Temp Range   | T <sub>J(max)</sub> | -40~+150                     | °C    |

| Storage Temperature           | T <sub>STG</sub>    | -40~+125                     | °C    |

| Operating Ambient Temperature | T <sub>A</sub>      | -40 to +85                   | °C    |

| Package Thermal Resistance    | $\theta_{JA}$       | 333                          | °C/W  |

### Absolute Maximum Ratings (Note 1)

Unless otherwise specified, all limits are at  $T_A = 25$ °C;  $V_{IN} = V_{OUT(NOM)} + 1V$ ,  $I_{OUT} = 1$ mA,  $C_{OUT} = 1$ μF,  $V_{ON/\overline{OFF}} = 2V$ . **Boldface** limits apply over the operating temperature range. (**Note 2**)

| Parameter           | Symbol                             | Co                                     | nditions                  | Min   | Тур                   | Max   | Units |

|---------------------|------------------------------------|----------------------------------------|---------------------------|-------|-----------------------|-------|-------|

| Input Voltage Range | V <sub>IN</sub>                    |                                        |                           | 2     |                       | 13    | V     |

| Output voltage      | V <sub>OUT</sub>                   | $I_{OUT} = 1mA$                        |                           | -1    | V <sub>OUT(NOM)</sub> | +1    | %     |

|                     |                                    | 1mA ≤ I <sub>OUT</sub>                 | <u>&lt;</u> 100mA         | -1.5  |                       | 1.5   |       |

|                     |                                    | 1mA <u>&lt;</u> I <sub>OUT</sub>       | <u>&lt;</u> 100mA         | -3.5  |                       | +3.5  |       |

| Feedback Voltage    | $V_{ADJ}$                          |                                        |                           | 1.215 | 1.240                 | 1.265 | V     |

| (ADJ version)       |                                    |                                        |                           | 1.202 |                       | 1.278 |       |

| Line Regulation     | $\Delta V_{OUT} /$                 | $V_{OUT(NOM)} + 1V \le V_{IN} \le 12V$ |                           |       | 0.007                 | 0.014 | %/V   |

|                     | $(V_{OUT}^*\Delta V_{IN})$         |                                        |                           |       |                       | 0.032 |       |

| Dropout voltage     |                                    |                                        | $I_{OUT} = 0mA$           |       | 0.1                   | 1     |       |

| (Note 3)            |                                    |                                        |                           |       |                       | 2     |       |

|                     | V <sub>IN</sub> – V <sub>OUT</sub> | 7080/81                                | $I_{OUT} = 10mA$          |       | 10                    | 25    |       |

|                     |                                    |                                        |                           |       |                       | 35    | mV    |

|                     | "                                  |                                        | $I_{OUT} = 50mA$          |       | 50                    | 75    |       |

|                     |                                    |                                        |                           |       |                       | 100   |       |

|                     |                                    |                                        | $I_{OUT} = 100 mA$        |       | 100                   | 150   |       |

|                     |                                    | 7081 only                              |                           |       |                       | 200   |       |

|                     |                                    | 7 CO T OTHY                            | $I_{OUT} = 150 \text{mA}$ |       | 150                   | 225   |       |

|                     |                                    |                                        |                           |       |                       | 300   |       |

### Electrical Characteristics ILC7080/81AIM5 (cont.)

Unless otherwise specified, all limits are  $T_A = 25^{\circ}C$ ;  $V_{IN} = V_{OUT(NOM)} + 1V$ ,  $I_{OUT} = 1mA$ ,  $C_{OUT} = 1\mu F$ ,  $V_{ON/\overline{OFF}} = 2V$ . Boldface limits apply over the operating temperature range. (Note 2)

| Parameter                | Symbol                         |                                           | Condit                | tions        | Min | Тур | Max | Units         |

|--------------------------|--------------------------------|-------------------------------------------|-----------------------|--------------|-----|-----|-----|---------------|

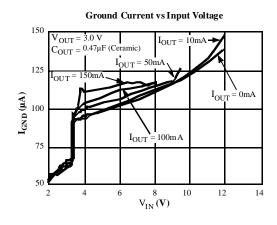

|                          |                                |                                           | I <sub>OUT</sub> =    | 0mA          |     | 95  | 200 |               |

|                          |                                |                                           |                       |              |     |     | 220 |               |

|                          |                                | 7080/81                                   | I <sub>OUT</sub> =    | 10mA         |     | 100 | 220 |               |

| Ground Pin Current       | ,                              |                                           |                       |              |     |     | 240 | μΑ            |

| Ground Fin Current       | I <sub>GND</sub>               |                                           | I <sub>OUT</sub> =    | 50mA         |     | 100 | 220 | μΑ            |

|                          |                                |                                           |                       |              |     |     | 240 |               |

|                          |                                |                                           | I <sub>OUT</sub> =    | 100mA        |     | 100 | 240 |               |

|                          |                                | 7081                                      |                       |              |     |     | 260 |               |

|                          |                                | only                                      | I <sub>OUT</sub> =    | 150mA        |     | 115 | 260 |               |

|                          |                                |                                           |                       |              |     |     | 280 |               |

| Shutdown (OFF) Current   | I <sub>ON/OFF</sub>            | V <sub>ON/OFF</sub> =                     | 0V                    |              |     | 0.1 | 2   | μΑ            |

| ON/OFF Input Voltage     | V <sub>ON/OFF</sub>            | High = Re                                 | egulator              | On           | 2.0 |     | 13  | V             |

|                          |                                | Low = Re                                  | egulator              | Off          |     |     | 0.6 |               |

| ON/OFF Pin Input Current | I <sub>IN(ON/OFF)</sub>        | V <sub>ON/OFF</sub> = 0.6V, regulator OFF |                       |              | 0.3 |     | μΑ  |               |

| (Note 5)                 |                                | V <sub>ON/OFF</sub> =                     | 2V, regi              | ulator ON    |     | 1   |     |               |

| Peak Output Current      | I <sub>OUT(PEAK)</sub>         | $V_{OUT} \ge 0$ .                         | 95V <sub>OUT(1</sub>  | NOM),        | 400 | 500 |     | mΑ            |

| (Note 4)                 |                                | tpw = 2m                                  | S                     |              |     |     |     |               |

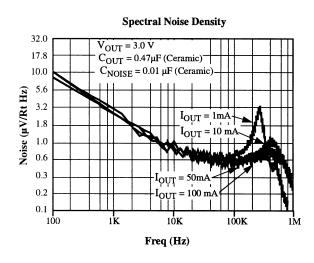

| Output Noise Voltage     | e <sub>N</sub>                 | BW = 30                                   | 0Hz to 5              | 0kHz,        |     | 80  |     | $\mu V_{RMS}$ |

|                          |                                | $C_{NOISE} = 0$                           | 0.01µF                |              |     |     |     |               |

| Dinnle Dejection         | 41/ /41/                       | $C_{OUT} = 4.$                            | 7μF,                  | freq = 1kHz  |     | 85  |     | 40            |

| Ripple Rejection         | $\Delta V_{OUT}/\Delta V_{IN}$ | $I_{OUT} = 100$                           | 0mA                   | freq = 10kHz |     | 70  |     | dB            |

|                          |                                |                                           |                       | freq = 1MHz  |     | 60  |     |               |

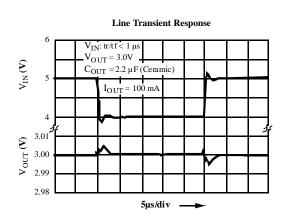

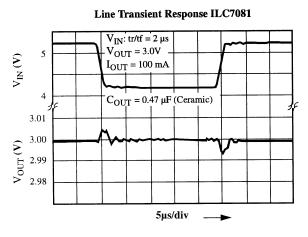

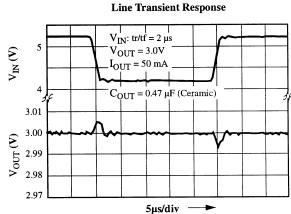

| Demonsis Line Demoletica | $\Delta V_{OUT(line)}$         | V <sub>IN</sub> : V <sub>OUT(</sub>       | (NOM) + 1             | V to         |     | 4   |     | mV            |

| Dynamic Line Regulation  |                                | $V_{OUT(NOM)}$                            | $V_{OUT(NOM)} + 2V$ , |              |     |     |     |               |

|                          |                                | tr/tf = 2µs                               | s; I <sub>OUT</sub> = | 100mA        |     |     |     |               |

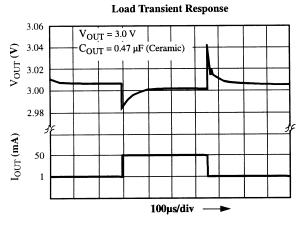

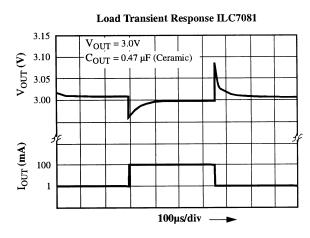

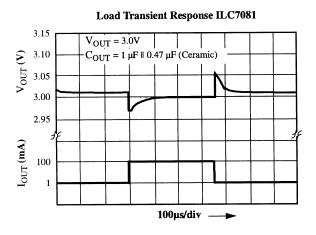

|                          |                                | I <sub>OUT</sub> : 0 to 100mA;            |                       | 50           |     |     |     |               |

| Dynamic Load Regulation  | $\Delta V_{OUT(load)}$         | $d(I_{OUT})/dt = 100mA/\mu s$             |                       | 25           |     | mV  |     |               |

|                          |                                | with $C_{OUT} = 0.47 \mu F$               |                       | 25           |     |     |     |               |

|                          |                                | with $C_{OUT} = 2.2 \mu F$                |                       |              |     |     |     |               |

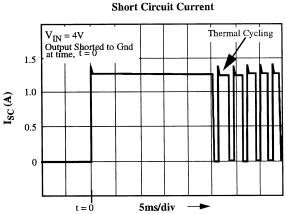

| Short Circuit Current    | I <sub>SC</sub>                | V <sub>OUT</sub> = 0\                     | /                     |              |     | 600 |     | mA            |

Note 1: Absolute maximum ratings indicate limits which when exceeded may result in damage to the component. Electrical specifications do not apply when operating the device outside of its rated operating conditions.

www.impalalinear.com

Note 2: Specified Min/Max limits are production tested or guaranteed through correlation based on statistical control methods. Measurements are taken at constant junction temperature as close to ambient as possible using low duty pulse testing.

Note 3: Dropout voltage is defined as the input to output differential voltage at which the output voltage drops 2% below the nominal value measured with a 1V differential.

Note 4: Guaranteed by design

Note 5: The device's shutdown pin includes a 2MW internal pull down resistor connected to ground.

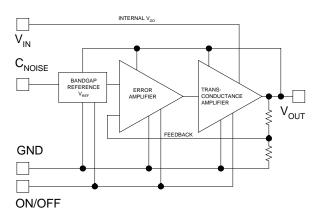

#### Operation

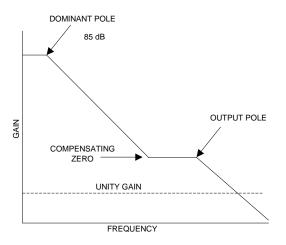

The ILC7080/81 LDO design is based on an advanced circuit configuration for which patent protection has been applied. Typically it is very difficult to drive a capacitive output with an amplifier. The output capacitance produces a pole in the feedback path, which upsets the carefully tailored dominant pole of the internal amplifier. Traditionally the pole of the output capacitor has been "eliminated" by reducing the output impedance of the regulator such that the pole of the output capacitor is moved well beyond the gain bandwidth product of the regulator. In practice, this is difficult to do and still maintain high frequency operation. Typically the output impedance of the regulator is not simply resistive, such that the reactive output impedance interacts with the reactive impedance of the load resistance and capacitance. In addition, it is necessary to place the dominant pole of the circuit at a sufficiently low frequency such that the gain of the regulator has fallen below unity before any of the complex interactions between the output and the load occur. The ILC7080/81 does not try to eliminate the output pole, but incorporates it into the stability scheme. The load and output capacitor forms a pole, which rolls off the gain of the regulator below unity. In order to do this the output impedance of the regulator must be high, looking like a current source. The output stage of the regulator becomes a transconductance amplifier, which converts a voltage to a current with a substantial output impedance. The circuit which drives the transconductance amplifier is the error amplifier, which compares the regulator output to the band gap reference and produces an error voltage as the input to the transconductance amplifier. The error amplifier has a dominant pole at low frequency and a "zero" which cancels out the effects of the pole. The zero allows

the regulator to have gain out to the frequency where the output pole continues to reduce the gain to unity. The configuration of the poles and zero are shown in figure 1.

Instead of powering the critical circuits from the unregulated input voltage, the CMOS RF LDO powers the internal circuits such as the bandgap, the error amplifier and most of the transconductance amplifier from the boot strapped regulated output voltage of the regulator. This technique offers extremely high ripple rejection and excellent line transient response.

A block diagram of the regulator circuit used in the ILC7080/81 is shown in figure 2, which shows the input-tooutput isolation and the cascaded sequence of amplifiers that implement the pole-zero scheme outlined above.

The ILC7080/81 were designed in a CMOS process with some minor additions, which allow the circuit to be used at input voltages up to 13V. The resulting circuit exceeds the frequency response of traditional bipolar circuits. The ILC7080/81 is very tolerant of output load conditions with the inclusion of both short circuit and thermal overload protection. The device has a very low dropout voltage, typically a linear response of 1mV per milliamp of load current, and none of the quasi-saturation characteristics of a bipolar output device. All the good features of the frequency response and regulation are valid right to the point where the regulator goes out of regulation in a 4mV transition region. Because there is no base drive, the regulator is capable of providing high current surges while remaining in regulation. This is shown in the high peak current of 500mA which allows for the ILC7080/81 to be used in systems that require short burst mode operation.

Figure 1: ILC7080/81 RF LDO frequency response

Figure 2: ILC7080/81 RF LDO regulator block digram

#### Shutdown (ON/OFF) Operation

The ILC7080/81 output can be turned off by applying 0.4V or less to the device's ON/OFF pin (pin 3). In shutdown mode, the ILC7080/81 draws less than 1mA quiescent current. The output of the ILC7081 is enabled by applying 2V to 13V at the ON/OFF pin. In applications where the ILC7080/81 output will always remain enabled, the ON/OFF pin may be connected to  $V_{\rm IN}$  (pin 1). The ILC7080/81's shutdown circuitry includes hysteresis, as such the device will operate properly even if a slow moving signal is applied to the ON/OFF pin. The device's shutdown pin includes a  $2M\Omega$  internal pull down resistor connected to ground.

#### **Short Circuit Protection**

The ILC7080/81 output can withstand momentary short circuit to ground. Moreover, the regulator can deliver very high output peak current due to its 1A instantaneous short circuit current capability.

#### **Thermal Protection**

The ILC7080/81 also includes a thermal protection circuit which shuts down the regulator when die temperature exceeds 170°C due to overheating. In thermal shutdown, once the die temperature cools to below 160°C, the regulator is enabled. If the die temperature is excessive due to high package power dissipation, the regulator's thermal circuit will continue to pulse the regulator on and off. This is called thermal cycling.

Excessively high die temperature may occur due to high differential voltage across the regulator or high load current or high ambient temperature or a combination of all three. Thermal protection protects the regulator from such fault conditions and is a necessary requirement in today's designs. In normal operation, the die temperature should be limited to under 150°C.

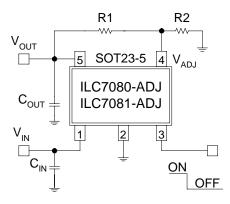

### **Adjustable Output Voltage**

Figure 3 shows how an adjustable output voltage can be easily achieved using ILC7080/81-ADJ. The output voltage, V<sub>OUT</sub> is given by the following equation:

$$V_{OUT} = 1.24V \times (R1/R2 + 1)$$

Figure 3: Application circuit for adjustable output voltage

For best results, a resistor value of  $470k\Omega$  or less may be used for R2. The output voltage can be programmed from 2.5V to 12V.

**Note:** An external capacitor should not be connected to the adjustable feedback pin (pin 4). Connecting an external capacitor to pin 4 may cause regulator instability and lead to oscillations.

#### **Maximum Output Current**

The maximum output current available from the ILC7080/81 is limited by the maximum package power dissipation as well as the device's internal current limit. For a given ambient temperature, TA, the maximum package power dissipation is given by:

$$P_{D(max)} = (T_{J(max)} - T_A) / \theta_{JA}$$

where  $T_{J(max)} = 150$ °C is the maximum junction temperature and  $\theta_{JA}$  = 333°C/W is the package thermal resistance. For example at  $T_A = 85$ °C ambient temperature, the maximum package power dissipation is;

$$P_{D(max)} = 195 mW.$$

The maximum output current can be calculated from the following equation:

$$I_{OUT(max)} < P_{D(max)} / (V_{IN} - V_{OUT})$$

For example at  $V_{IN} = 6V$ ,  $V_{OUT} = 5V$  and  $T_A = 85$ °C, the maximum output current is I<sub>OUT(max)</sub> < 195mA. At higher output current, the die temperature will rise and cause the thermal protection circuit to be enabled.

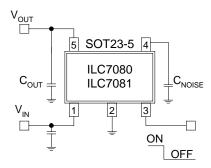

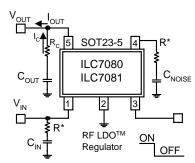

#### **APPLICATION HINTS**

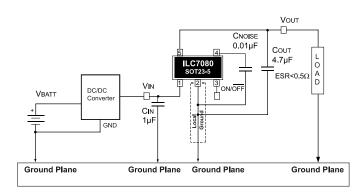

Figure 4 shows the typical application circuit for the ILC7080/81.

Figure 4: Basic application circuit for fixed output voltage versions

### **Input Capacitor**

An input capacitor C<sub>IN</sub> of value 1mF or larger should be connected from V<sub>IN</sub> to the main ground plane. This will help to filter supply noise from entering the LDO. The input capacitor should be connected as close to the LDO regulator input pin as is practical. Using a high-value input capacitor will offer superior line transient response as well as better power supply ripple rejection. A ceramic or tantalum capacitor may be used at the input of the LDO regulator.

Note that there is a parasitic diode from the LDO regulator output to the input. If the input voltage swings below the regulator's output voltage by a couple of hundred milivolts then the regulator may be damaged. This condition must be avoided. In many applications a large value input capacitor,

$C_{IN}$ , will hold  $V_{IN}$  higher than  $V_{OUT}$  and decay slower than  $V_{OLIT}$  when the LDO is powered off.

### **Output Capacitor Selection**

Impala strongly recommends the use of low ESR (equivalent series resistance) ceramic capacitors for COUT and C<sub>NOISE</sub>. The ILC7080/81 is stable with low ESR capacitor (as low as zero  $\Omega$ ). The value of the output capacitor should be 1µF or higher. Either ceramic chip or a tantalum capacitor may be used at the output.

Use of ceramic chip capacitors offer significant advantages over tantalum capacitors. A ceramic capacitor is typically considerably cheaper than a tantalum capacitor, it usually has a smaller footprint, lower height, and lighter weight than a tantalum capacitor. Furthermore, unlike tantalum capacitors which are polarized and can be damaged if connected incorrectly, ceramic capacitors are non-polarized. Low value ceramic chip capacitors with X7R dielectric are available in the 100pF to 4.7µF range, while high value capacitors with Y5V dielectric are available in the 2200pF to 22µF range. Evaluate carefully before using capacitors with Y5V dielectric because their ESR increases significantly at cold temperatures. Figure 10 shows a list of recommended ceramic capacitors for use at the output of ILC7080/81.

Note: If a tantalum output capacitor is used then for stable operation Impala recommends a low ESR tantalum capacitor with maximum rated ESR at or below  $0.4\Omega$ . Low ESR tantalum capacitors, such as the TPS series from AVX Corporation (www.avxcorp.com) or the T495 series from Kemet (www.kemet.com) may be used. In applications where a high output surge current can be expected, use a high value but low ESR output capacitor for superior load transient response. The ILC7080/81 is stable with no load.

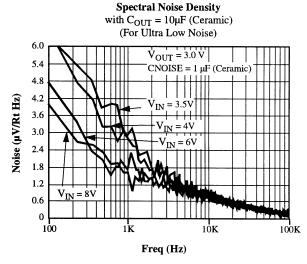

#### **Noise Bypass Capacitor**

www.impalalinear.com

In low noise applications, the self noise of the ILC7080/81 can be decreased further by connecting a capacitor from the noise bypass pin (pin 4) to ground (pin 2). The noise bypass pin is a high impedance node as such, care should be taken in printed circuit board layout to avoid noise pickup from external sources. Moreover, the noise bypass capacitor should have low leakage.

Noise bypass capacitors with a value as low as 470pF may be used. However, for optimum performance, use a 0.01µF or larger, ceramic chip capacitor. Note that the turn on and turn off response of the ILC7080/81 is inversely proportional to the value of the noise bypass capacitor. For fast turn on and turn off, use a small value noise bypass capacitor. In applications were exceptionally low output noise is not required, consider omitting the noise bypass capacitor altogether.

#### The Effects of ESR (Equivalent Series Resistance)

The ESR of a capacitor is a measure of the resistance due to the leads and the internal connections of the component. Typically measured in  $m\Omega$  (milli-ohms) it can increase to ohms in some cases.

Wherever there is a combination of resistance and current, voltages will be present. The control functions of LDOs use two voltages in order to maintain the output precisely;  $V_{OUT}$  and  $V_{REF}$ .

With reference to the block diagram in figure 2,  $V_{OUT}$  is fed back to the error amplifier and is used as the supply voltage for the internal components of the 7080/81. So any change in  $V_{OUT}$  will cause the error amplifier to try to compensate to maintain  $V_{OUT}$  at the set level and noise on  $V_{OUT}$  will be reflected into the supply of each internal circuit. The reference voltage,  $V_{REF}$ , is influenced by the  $C_{NOISE}$  pin. Noise into this pin will add to the reference voltage and be fed through the circuit. These factors will not cause a problem if some simple steps are taken. Figure 5 shows where these added ESR resistances are present in the typical LDO circuit.

Figure 5: ESR in C<sub>OUT</sub> and C<sub>NOISE</sub>

With this in mind low ESR components will offer better performance as LDOs may be exposed to large transients of output voltage, and current flows through the capacitors in order to filter these transient swings. ESR is less of a problem with  $C_{\text{IN}}$  as the voltage fluctuations at the input will be filtered by the LDO.

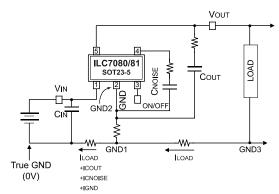

However, being aware of these current flows, there is also another potential source of induced voltage noise from the resistance inherent in the PCB trace. Figure 6 shows where the additive resistance of the PCB can manifest itself. Again these resistances may be very small, but a summation of several currents can develop detectable voltage ripple and will be amplified by the LDO. Particularly the accumulation of current flows in the ground plane can develop significant voltages unless care is taken.

With a degree of care, the ILC7080/81 will yield outstanding performance.

#### **Printed Circuit Board Layout Guidelines**

As was mentioned in the previous section, to take full advantage of any high performance LDO regulator requires paying careful attention to grounding and printed circuit board (PCB) layout.

Figure 6: Inherent PCB resistance

Figure 7 shows the effects of poor grounding and PCB layout caused by the ESR and PCB resistances and the accumulation of current flows.

Note particularly that during high output load current, the LDO regulator's ground pin and the ground return for  $C_{OUT}$  and  $C_{NOISE}$  are not at the same potential as the system ground. This is due to high frequency impedance caused by PCB's trace inductance and DC resistance. The current loop between  $C_{OUT}$ ,  $C_{NOISE}$  and the LDO regulator's ground pin will degrade performance of the LDO.

Figure 7: Effects of poor circuit layout

Figure 8 shows an optimum schematic. In this schematic, high output surge current has little effect on the ground current and noise bypass current return of the LDO regulator. Note that the key difference here is that  $C_{OUT}$  and  $C_{NOISE}$  are directly connected to the LDO regulator's ground pin. The LDO is then separately connected to the main ground plane and returned to a single point system ground.

The layout of the LDO and its external components are also based on some simple rules to minimize EMI and output voltage ripple.

Figure 8: Recommended application circuit schematic

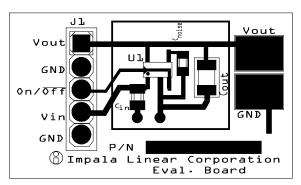

Figure 9: Recommended application circuit layout (not drawn to scale). Note: ground plane is bottom layer of PCB and connects to top layer ground connections through vias

#### **Evaluation Board Parts List For Printed Circuit Board Shown Above**

| Label                                 | Part Number                            | Manufacturer  | Description                                     |

|---------------------------------------|----------------------------------------|---------------|-------------------------------------------------|

| U1                                    | ILC7081AIM5-30                         | Impala Linear | 100mA RF LDO™                                   |

| J1                                    | 69190-405                              | Berg          | Connector, four position header                 |

| $C_{IN}$                              | GRM40 Y5V 105Z16                       | muRata        | Ceramic capacitor, 1µF, 16V, SMT (size 0805)    |

| C <sub>NOISE</sub>                    | C <sub>NOISE</sub> ECU-V1H103KBV Panas |               | Ceramic Capacitor, 0.01µF, 16V, SMT (size 0603) |

| C <sub>OUT</sub> GRM42-<br>6X5R475K10 |                                        | muRata        | Ceramic Capacitor, 4.7µF, 16V, SMT (size 1206)  |

### **Grounding Recommendations**

- 1. Connect  $C_{IN}$  between  $V_{IN}$  of the ILC7080/81 and the "GROUND PLANE".

- 2. Keep the ground side of C<sub>OUT</sub> and C<sub>NOISE</sub> connected to the "LOCAL GROUND" and not directly to the "GROUND PLANE".

- 3. On multilayer boards use component side copper for grounding around the ILC7080/81 and connect back to a "GROUND PLANE" using vias.

- 4. If using a DC-DC converter in your design, use a star grounding system with separate traces for the power ground and the control signals. The star should radiate from where the power supply enters the PCB.

### **Layout Considerations**

- 1. Place all RF LDO related components; ILC7080/81, input capacitor  $C_{\text{IN}}$ , noise bypass capacitor  $C_{\text{NOISE}}$  and output capacitor C<sub>OUT</sub> as close together as possible.

- 2. Keep the output capacitor C<sub>OUT</sub> as close to the ILC7080/81 as possible with very short traces to the V<sub>OUT</sub> and GND pins.

- 3. The traces for the related components; ILC7080/81, input capacitor  $C_{\text{IN}}$ , noise bypass capacitor  $C_{\text{NOISE}}$  and output capacitor COUT can be run with minimum trace widths close to the LDO.

- 4. Maintain a separate "LOCAL GROUND" remote from the "GROUND PLANE" to ensure a quiet ground near the LDO.

Figure 9 shows how this circuit can be translated into a PCB layout.

# Recommended Ceramic Output Capacitors

| C <sub>OUT</sub> | Capacitor Size | I <sub>out</sub> | Dielectric | Part Number       | Capacitor Vendor |

|------------------|----------------|------------------|------------|-------------------|------------------|

| 1µF              | 0805           | 0 to 100mA       | X5R        | C2012X5R1A105KT   | TDK              |

| 1µF              | 0805           | 0 to 100mA       | X7R        | GRM40X7R105K010   | muRata           |

| 1µF              | 0805           | 0 to 100mA       | X7R        | LMK212BJ105KG     | Talyo-Yuden      |

| 1µF              | 1206           | 0 to 100mA       | X7R        | GRM42-6X7R105K016 | muRata           |

| 1µF              | 1206           | 0 to 100mA       | X7R        | EMK316BJ105KL     | Talyo-Yuden      |

| 1µF              | 1206           | 0 to 100mA       | X5R        | TMK316BJ105KL     | Talyo-Yuden      |

|                  |                |                  |            |                   |                  |

| 2.2µF            | 0805           | 0 to 150mA       | X5R        | GRM40X5R225K 6.3  | muRata           |

| 2.2µF            | 0805           | 0 to 150mA       | X5R        | C2012X5R0J225KT   | TDK              |

| 2.2µF            | 1206           | 0 to 150mA       | X5R        | EMK316BJ225ML     | Talyo-Yuden      |

|                  |                |                  |            |                   |                  |

| 4.7µF            | 1206           | 0 to 150mA       | X5R        | GRM42-6X5R475K010 | muRata           |

| 4.7µF            | 1206           | 0 to 150mA       | X7R        | LMK316BJ475ML     | Talyo-Yuden      |

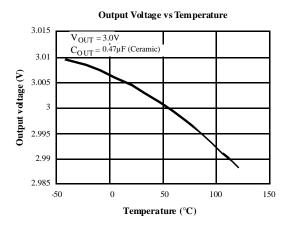

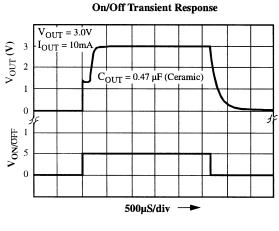

### TYPICAL PERFORMANCE CHARACTERISTICS

Unless otherwise specified T<sub>A</sub> T=25°C, V<sub>IN</sub> =V<sub>OUT(NOM)</sub>, + 1V, ON/ $\overline{\text{OFF}}$  pin tied to V<sub>IN</sub> Characterization at output currents above 50mA applies to ILC7081

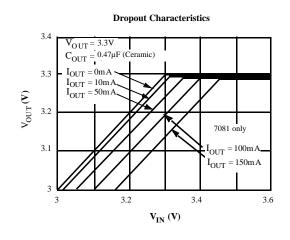

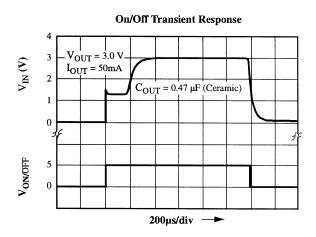

### TYPICAL PERFORMANCE CHARACTERISTICS

Unless otherwise specified  $T_A T=25^{\circ}C$ ,  $V_{IN} = V_{OUT(NOM)}$ , + 1V,  $ON/\overline{OFF}$  pin tied to  $V_{IN}$ Characterization at output currents above 50mA applies to ILC7081

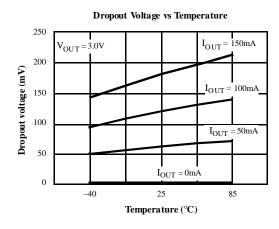

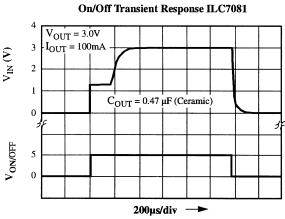

### TYPICAL PERFORMANCE CHARACTERISTICS

Unless otherwise specified  $T_A$  T=25°C,  $V_{IN}$  = $V_{OUT(NOM)}$ , + 1V, ON/ $\overline{OFF}$  pin tied to  $V_{IN}$ Characterization at output currents above 50mA applies to ILC7081

www.impalalinear.com

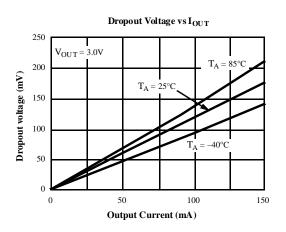

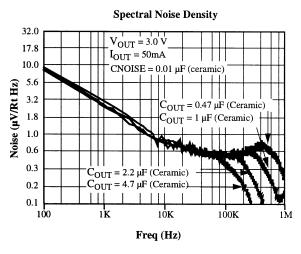

### TYPICAL PERFORMANCE CHARACTERISTICS

Unless otherwise specified  $T_A$  T=25°C,  $V_{IN}$  = $V_{OUT(NOM)}$ , + 1V, ON/OFF pin tied to  $V_{IN}$  Characterization at output currents above 50mA applies to ILC7081

## SOT-23 Package Markings

### ILC7080AIM5-xx

| Output voltage (V) Grade                                                                             |   | Order Information | *Package Marking | Supplied as:              |  |  |  |

|------------------------------------------------------------------------------------------------------|---|-------------------|------------------|---------------------------|--|--|--|

| 2.85 A                                                                                               |   | ILC7080AIM5-285   | CFXX             | 3k Units on Tape and Reel |  |  |  |

| 3.0 A                                                                                                |   | ILC7080AIM5-30    | CAXX             | 3k Units on Tape and Reel |  |  |  |

| 3.3 A                                                                                                |   | ILC7080AIM5-33    | CBXX             | 3k Units on Tape and Reel |  |  |  |

| 3.6 A                                                                                                |   | ILC7080AIM5-36    | CDXX             | 3k Units on Tape and Reel |  |  |  |

| 5.0                                                                                                  | Α | ILC7080AIM5-50    | CCXX             | 3k Units on Tape and Reel |  |  |  |

| ADJ A ILC7080AIM5-ADJ CEXX 3k Units on Tape a                                                        |   |                   |                  |                           |  |  |  |

| *Note: First two characters identify the product and the last two characters identify the date code. |   |                   |                  |                           |  |  |  |

### ILC7081AIM5-xx

| Output voltage (V)                                                                                   | Grade | Order Information | *Package Marking | Supplied as:              |  |  |  |

|------------------------------------------------------------------------------------------------------|-------|-------------------|------------------|---------------------------|--|--|--|

| 2.85                                                                                                 | Α     | ILC7081AIM5-285   | CVXX             | 3k Units on Tape and Reel |  |  |  |

| 3.0                                                                                                  | Α     | ILC7081AIM5-30    | CQXX             | 3k Units on Tape and Reel |  |  |  |

| 3.3                                                                                                  | Α     | ILC7081AIM5-33    | CRXX             | 3k Units on Tape and Reel |  |  |  |

| 3.6                                                                                                  | Α     | ILC7081AIM5-36    | CTXX             | 3k Units on Tape and Reel |  |  |  |

| 4.7                                                                                                  | Α     | ILC7081AIM5-47    | CWXX             | 3k Units on Tape and Reel |  |  |  |

| 5.0                                                                                                  | Α     | ILC7081AIM5-50    | CSXX             | 3k Units on Tape and Reel |  |  |  |

| ADJ                                                                                                  | Α     | ILC7081AIM5-ADJ   | CUXX             | 3k Units on Tape and Reel |  |  |  |

| *Note: First two characters identify the product and the last two characters identify the date code. |       |                   |                  |                           |  |  |  |

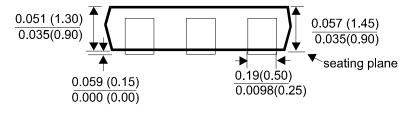

### Package Outline Dimensions

Dimensions shown in inches and (mm). 5-Lead plastic surface mount (SOT-23-5)

Devices sold by Impala Linear Corporation are covered by the warranty and patent indemnification provisions appearing Devices soil by impair Linear Corporation are covered by the warranty and patent indentinication provisions appearing in its Terms of Sale only. Impala Linear Corporation makes no warranty, express, statutory, implied, or by description regarding the information set forth herein or regarding the freedom of the described devices from patent infringement. Impala Linear Corporation makes no warranty of merchantability of fitness for any purpose. Impala Linear Corporation reserves the right to discontinue production and change specifications and prices at any time and without notice.

This product is intended for use in normal commercial applications. Applications requiring an extended temperature range, unusual environmental requirements, or high reliability applications, such as military and aerospace, are specifically not recommended without additional processing by Impala Linear Corporation.

Impala Linear Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in an Impala Linear Corporation product. No other circuits, patents, licenses are implied.

#### Life Support Policy

www.impalalinear.com

Impala Linear Corporation's products are not authorized for use as critical components in life support devices or systems.

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.