# IP113M LF

Preliminary Data Sheet

## Managed 10/100Base-TX / FX Media Converter

#### **Features**

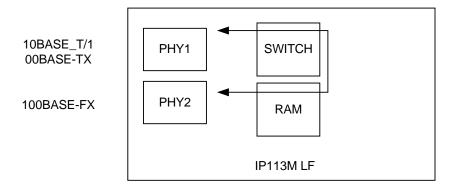

- A 10/100BASE-TX/ 100BASE-FX converter with a SMI port for management

- Built in a 10/100BASE-TX transceiver

- Built in a PHY for 100BASE-FX

- Built in a 2-port switch

- Pass all packets without address and CRC check (optional)

- Supports modified cut-through frame forwarding for low latency

- Supports pure converter mode data forwarding for extreme low latency

- Supports flow control for full and half duplex operation

- Bandwidth control

- Max packet length 1600 bytes

- Optional forward fragments

- Built in 128Kb RAM for data buffer

- Supports 3.3v I/O tolerance SMI (MDC, MDIO) and MII registers for management

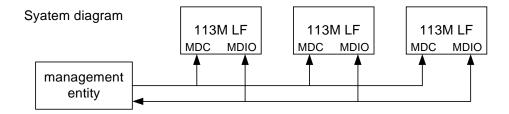

- Configure local and remote IP113M LF through local SMI

- Monitor local and remote IP113M LF through local SMI

- Configure/ monitor TP port support (auto-negotiation or force 10M/100M, full/half)

- Configure/ monitor flow control, bandwidth

- Supports loop back test (In-band or out-band, auto or program)

- The maintenance frame is compliant to TS-1000 standard (the Telecommunication Technology Committee, TTC)

- Supports Statistic Counters

- Supports auto MDI-MDIX function

- Supports link fault pass through function

- Supports far end fault function

- LED display for link/activity, full/half, 10/100

- Built in a watchdog timer to monitor internal switch error

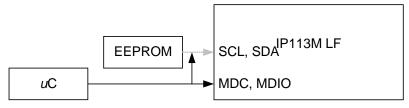

- Supports EEPROM Configuration

- 0.25u CMOS technology

- Single 2.5V power supply

- 48-pin LQFP package

- Support Lead Free package (Please refer to the Order Information)

# General Description

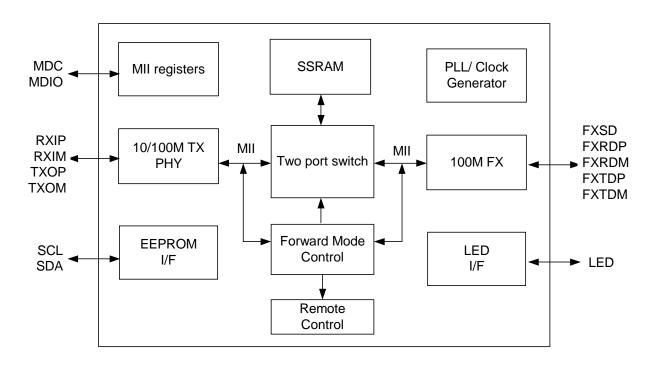

IP113M LF can be a 10/100BASE-TX to 100BASE-FX converter with an SMI port for management. It consists of a 2-port switch controller, a fast Ethernet transceiver and a PHY for 100BASE-FX. The transceivers in IP113M LF are designed in DSP approach with advance 0.25um technology; this results in high noise immunity and robust performance.

IP113M LF not only supports store and forward mode, it also supports modified cut through mode and pure converter mode for low latency data forwarding. IP113M LF can transmit packet(s) up to 1600 bytes to meet requirement of extra long packets.

IP113M LF supports remote management function. IP113M LF supports remote access functions and it also supports remote monitor and loop back test function defined in TS-1000 spec (\*). Local IP113M LF can access the MII registers of remote IP113M LF by programming local IP113M LF's MII registers via SMI connection. IP113M LF implements the management function using the maintenance frame defined in TS-1000 spec.

IP113M LF supports IEEE802.3x, collision base backpressure, and various LED functions, etc. These functions can be configured to fit the different requirements by feeding operation parameters via EEPROM interface or pull up/down resistors on specified pins.

April 9, 2007 IP113M LF-DS-R11

<sup>\*</sup> The Telecommunication Technology Committee owns the copyright of TS-1000.

#### **Contents**

|        |          | ptionption                                                                           |   |   |

|--------|----------|--------------------------------------------------------------------------------------|---|---|

|        |          |                                                                                      |   |   |

|        |          | у                                                                                    |   |   |

| Block  | Diagram  |                                                                                      |   | 5 |

|        |          | gram                                                                                 |   |   |

| Applic | cations  |                                                                                      |   | 6 |

| Mana   | ged conv | erter (up to 31 pieces of IP113M LF in a chassis)                                    |   | 6 |

|        |          | onverter                                                                             |   |   |

|        |          |                                                                                      |   |   |

| 1. I   |          | ription                                                                              |   |   |

|        |          | cription (continued)                                                                 |   |   |

| 2. I   |          | l Description                                                                        |   |   |

|        | 2.1      | Data forwarding                                                                      |   |   |

|        |          | 2.1.1 Modified cut-through mode                                                      |   |   |

|        |          | 2.1.2 Pure converter mode                                                            |   |   |

|        |          | 2.1.3 Fragment forwarding                                                            |   |   |

|        |          | TP port force mode                                                                   |   |   |

|        | 2.3      | Remote management                                                                    |   |   |

|        |          | 2.3.1 Maintenance frame format at MII                                                |   |   |

|        |          | 2.3.2 Bit definition of maintenance frame                                            |   |   |

|        |          | 2.3.3 Bit definition of maintenance frame (continue                                  |   |   |

|        |          | 2.3.4 Remote monitor                                                                 |   |   |

|        |          | 2.3.5 Remote control read                                                            |   |   |

|        |          | 2.3.6 Remote control write                                                           |   |   |

|        | 2.4      | Loop back test                                                                       |   |   |

|        |          | 2.4.1 Out-band loop back test                                                        |   |   |

|        |          | 2.4.2 In-band loop back test                                                         |   |   |

|        |          | 2.4.3 Programming procedure for In-band loop bac                                     |   |   |

|        | 0.5      | 2.4.4 Auto in-band loop back test                                                    |   |   |

|        | 2.5      | Remote monitor without SMI programming                                               |   |   |

|        | 0.0      | 2.5.1 Auto sends (Status change notice)                                              |   |   |

|        | 2.6      | Link fault pass through                                                              |   |   |

|        |          | 2.6.1 Normal case                                                                    |   |   |

|        |          | 2.6.2 Remote TP port disconnected                                                    |   |   |

|        |          | 2.6.3 FX port disconnected                                                           |   |   |

|        | 0.7      | 2.6.4 LED diagnostic functions for fault indication EEPROM – store the initial value |   |   |

|        | 2.7      | Auto MDI MDIX                                                                        |   |   |

|        |          | Serial management interface                                                          |   |   |

| 2 1    | 2.9      |                                                                                      |   |   |

| 3. 1   | -        | Pro hania MII ragistara                                                              |   |   |

|        | 3.1      | The basic MII registers                                                              |   |   |

|        |          | The basic MII registers 0 The basic MII registers 1                                  |   |   |

|        |          | The basic MII registers 1  The basic MII registers 1(continued)                      |   |   |

|        |          | • • • • • • • • • • • • • • • • • • • •                                              |   |   |

|        |          | The basic MII registers 2, 3                                                         |   |   |

|        |          | The basic MII registers 4                                                            |   |   |

|        |          | The basic MII registers 5                                                            | ა | O |

# IP113M LF

# Preliminary Data Sheet

|    |            | The basic MII registers 6                                 | 37 |

|----|------------|-----------------------------------------------------------|----|

|    | 3.2        | Extended MII registers and EEPROM registers               | 38 |

|    |            | Extended MII registers and EEPROM registers 16            | 39 |

|    |            | Extended MII registers and EEPROM registers 17            | 40 |

|    |            | Extended MII registers and EEPROM registers 17(continued) | 41 |

|    |            | Extended MII registers and EEPROM registers 18            |    |

|    |            | Extended MII registers and EEPROM registers 19            | 43 |

|    |            | Extended MII registers and EEPROM registers 20            | 44 |

|    |            | Extended MII registers and EEPROM registers 20(continued) | 45 |

|    |            | Extended MII registers and EEPROM registers 21            | 46 |

|    |            | Extended MII registers and EEPROM registers 22            | 47 |

|    |            | Extended MII registers and EEPROM registers 22(continued) | 48 |

|    |            | Extended MII registers and EEPROM registers 23            | 49 |

|    |            | Extended MII registers and EEPROM registers 23(continued) | 50 |

|    |            | Extended MII registers and EEPROM registers 24            | 51 |

|    |            | Extended MII registers and EEPROM registers 25            | 52 |

|    |            | Extended MII registers and EEPROM registers 26            | 53 |

|    |            | Extended MII registers and EEPROM registers 27,28,29,30   | 54 |

|    |            | Extended MII registers and EEPROM registers 31            | 55 |

| 4. | Electrical | Characteristics                                           | 57 |

|    | 4.1        | Absolute Maximum Rating                                   | 57 |

|    | 4.2.       | DC Characteristic                                         | 57 |

| 5. | Order Inf  | ormation                                                  | 57 |

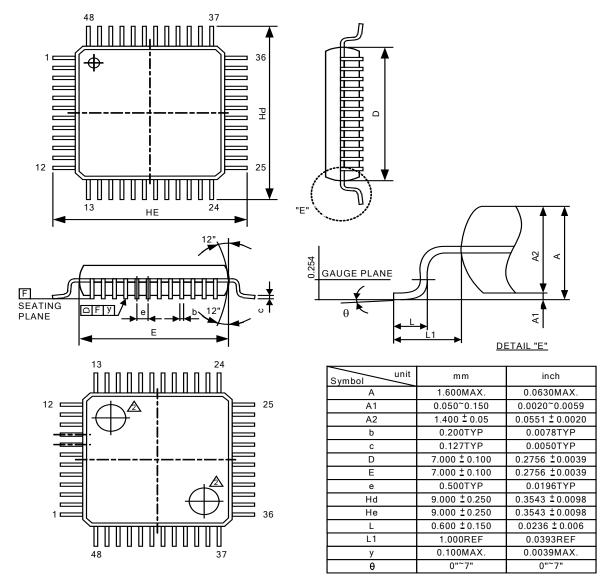

| 6. | Package    | Detail                                                    | 58 |

|    |            |                                                           |    |

## **Revision History**

| Revision #                           | Change Description                                                                                                                                                                                                                     |  |  |  |  |  |

|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| IP113M LF-DS-R01                     | Initial release.                                                                                                                                                                                                                       |  |  |  |  |  |

| IP113M LF-DS-R02                     | 2                                                                                                                                                                                                                                      |  |  |  |  |  |

| IP113M LF-DS-R03                     | 3                                                                                                                                                                                                                                      |  |  |  |  |  |

| IP113M LF-DS-R04                     | Remove Operation Junction Temperature.                                                                                                                                                                                                 |  |  |  |  |  |

| IP113M LF-DS-R05                     | TP port should be linked at 100M full duplex when working at this mode.                                                                                                                                                                |  |  |  |  |  |

| IP113M LF-DS-R06                     | SUpdate page 42,1                                                                                                                                                                                                                      |  |  |  |  |  |

| IP113M LF-DS-R07                     | Add the order information for lead free package. Update page 50 (Item:31.2 & 31.3)                                                                                                                                                     |  |  |  |  |  |

| IP113M LF-DS-R08                     | Update page 27 Update the default value of following resisters MII reg3.[5:4], reg4.10, reg6.2, reg16.6, reg18.3, reg18.13, reg22.4, reg22.6, reg23.13 and Description of reg26.0 Add explanation to MII reg31.[5:4], reg31.3, reg31.2 |  |  |  |  |  |

| IP113M LF-DS-R09 Revise the diagram. |                                                                                                                                                                                                                                        |  |  |  |  |  |

| IP113M LF-DS-R10                     | Modify the IPL: pull-low and IPH: pull-high on page 8.                                                                                                                                                                                 |  |  |  |  |  |

| IP113M LF-DS-R11                     | Add Power Pin description on Page13                                                                                                                                                                                                    |  |  |  |  |  |

## **Block Diagram**

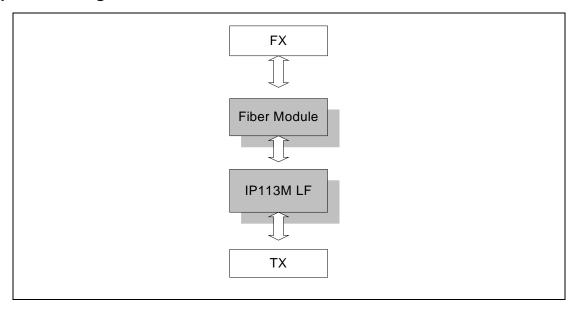

## **Application Diagram**

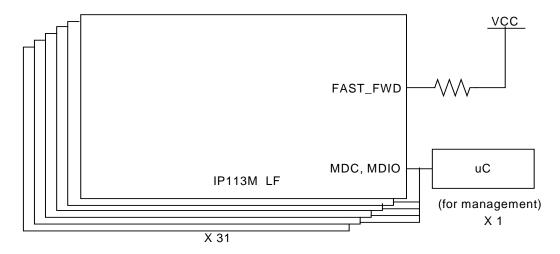

## **Applications**

## Managed converter (up to 31 pieces of IP113M LF in a chassis)

## **Un-managed converter**

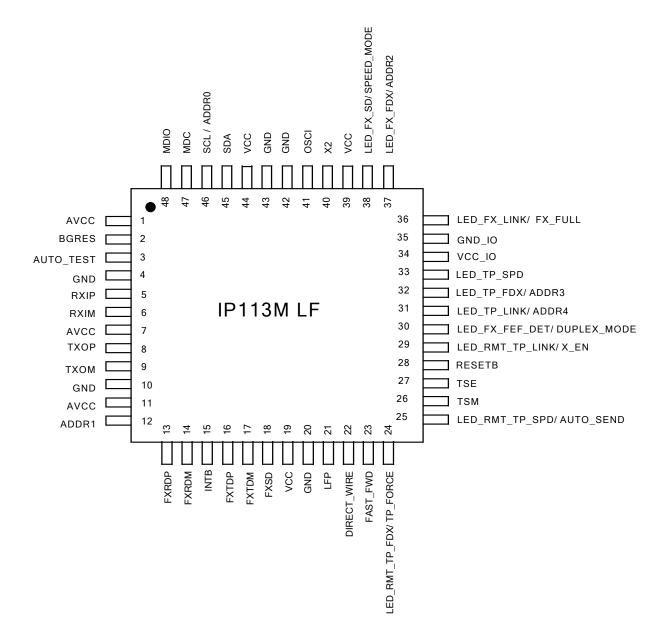

## **PIN Diagram**

## 1. PIN Description

| Туре | Description                                  |  |  |  |  |  |

|------|----------------------------------------------|--|--|--|--|--|

| I    | Input pin                                    |  |  |  |  |  |

| 0    | Output pin                                   |  |  |  |  |  |

| IPH  | Input pin with internal pull-high resistor   |  |  |  |  |  |

| IPL  | PL Input pin with internal pull-low resistor |  |  |  |  |  |

| Pin no.    | Label        | Туре | Description                                                                                                                                                                                                                  |  |

|------------|--------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Transceive | er           | •    |                                                                                                                                                                                                                              |  |

| 5, 6       | RXIP, RXIM   | I    | TP receive                                                                                                                                                                                                                   |  |

| 8, 9       | TXOP, TXOM   | 0    | TP transmit                                                                                                                                                                                                                  |  |

| 2          | BGRES        | 0    | Band gap resistor It is connected to GND through a 6.19k (1%) resistor in application circuit.                                                                                                                               |  |

| 18         | FXSD         | I    | 100Base-FX signal detect Fiber signal detect. It is an input signal from fiber MAU. Fiber signal detect is active if the voltage on FXSD is higher than the threshold voltage, which is 1.35v ±5% when VCC is equal to 2.5v. |  |

| 13, 14     | FXRDP, FXRDM | I    | Fiber receiver data pair Common-mode voltage of FXRDP and FXRDM are suggested to near 0.5x AVCC. When voltage peak-to-peak>0.1V,FXRX could be workable.                                                                      |  |

| 16, 17     | FXTDP, FXTDM | 0    | Fiber transmitter data pair FXTX with the external $100\Omega$ resistor. Common-mode voltage of FXTDP and FXTDM are suggested to near 0.5x AVCC. Swing of Voltage $\geq 0.8$ V.                                              |  |

| Pin no.  | Label           | Туре | D                                                                                                                     | escription                                                        |  |

|----------|-----------------|------|-----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|--|

| LED pins |                 |      |                                                                                                                       |                                                                   |  |

| 31       | LED_TP_LINK     | 0    | TP port link LED On: link ok, Off: link fail, Flash: link ok & activity (Flash: on for 20ms and off for 80ms)         |                                                                   |  |

| 33       | LED_TP_SPD      | 0    | TP port speed LED<br>On: 100M, Off: 10M                                                                               |                                                                   |  |

| 32       | LED_TP_FDX      | 0    | TP port full duplex LED<br>On: full, Off: half,<br>Flash: half & collision ha<br>(Flash: on for 20ms and              | ppens                                                             |  |

| 36       | LED_FX_LINK     | 0    | Fiber port link LED On: link ok, Off: link fail (Flash: on for 20ms and                                               | , Flash: link ok & activity off for 80ms)                         |  |

| 37       | LED_FX_FDX      | 0    | Fiber port full duplex LED On: full, Off: half, Flash: half & collision happens (Flash: on for 20ms and off for 80ms) |                                                                   |  |

| 38       | LED_FX_SD       | 0    | Fiber port signal detect On: FXSD is active, Off: FXSD is inactive                                                    |                                                                   |  |

| 30       | LED_FX_FEF_DET  | 0    | Far end fault pattern received                                                                                        |                                                                   |  |

|          |                 |      | Far End Fault Pattern received: LED On: 80ms, LED Off: 20ms Far End Fault Pattern not Receive: LED is always off      |                                                                   |  |

| 29       | LED_RMT_TP_LINK | 0    | LED for link status of TP                                                                                             | port of remote IP113M LF                                          |  |

|          |                 |      | Pin 3 AUTO_TEST = 0                                                                                                   | Pin 3 AUTO_TEST = 1                                               |  |

|          |                 |      | On: link ok,<br>Off: link fail                                                                                        | Flash<br>(On: 80ms, Off: 20ms)                                    |  |

| 25       | LED_RMP_TP_SPD  | 0    | LED for speed of TP port                                                                                              | t of remote IP113M LF                                             |  |

|          |                 |      | Pin 3 AUTO_TEST = 0                                                                                                   | Pin 3 AUTO_TEST = 1                                               |  |

|          |                 |      | On: 100M,<br>Off: 10M                                                                                                 | On: loop back test complete,<br>Off: under loop back test         |  |

| 24       | LED_RMT_TP_FDX  | 0    | LED for full duplex of TP port of remote IP113M LF                                                                    |                                                                   |  |

|          |                 |      | Pin 3 AUTO_TEST = 0                                                                                                   | Pin 3 AUTO_TEST = 1                                               |  |

|          |                 |      | On: full duplex,<br>Off: half duplex                                                                                  | On: loop back test result is ok, Off: loop back test result fails |  |

Note: The output of LED pin is logic low when the LED is on.

| Pin no.  | Label        | Туре | Description                                                                                                                                                                                                                                                                 |

|----------|--------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LED pins | during reset |      |                                                                                                                                                                                                                                                                             |

| 29       | X_EN         | IPH  | Flow control enable on TP port and fiber port 1: enable (default), 0: disable                                                                                                                                                                                               |

| 24       | TP_FORCE     | IPL  | Local TP port auto negotiation enable  1: TP port supports auto-negotiation with limited capability defined by pin 38 SPEED_MODE and pin 30 DUPLEX_MODE.  0: TP port supports auto-negotiation with 10M/100M, full/half capability (default)                                |

|          |              |      | The setting may be updated by programming EEPROM register 3.5 or MII register 20.13.                                                                                                                                                                                        |

| 38       | SPEED_MODE   | IPH  | Local TP port speed selection  1: TP port has the 100Mb speed ability  0: TP port has the 10Mb speed ability only                                                                                                                                                           |

|          |              |      | It is valid only if pin 24 TP_FORCE is enabled.                                                                                                                                                                                                                             |

| 30       | DUPLEX_MODE  | IPH  | Local TP port duplex selection  1: TP port has the full duplex ability  0: TP port has the half duplex ability only                                                                                                                                                         |

|          |              |      | It is valid only if pin 24 TP_FORCE is enabled.                                                                                                                                                                                                                             |

| 25       | AUTO_SEND    | IPL  | Auto send the status to the remote IP113M LF  1: enable  0: disable (default)                                                                                                                                                                                               |

| 36       | FX_FULL      | IPH  | Set the duplex of fiber port 1: full duplex (default) 0: half duplex                                                                                                                                                                                                        |

| 3        | AUTO_TEST    | IPL  | Auto loop back test  1: enable When IP113M LF detects a low-to-high transition on this pin, it will perform loop back test for once. It supports an easy way to instruct IP113M LF performing fiber loop back test without programming MII registers.  0: disable (default) |

| Pin no.                                            | Label | Туре | Description |

|----------------------------------------------------|-------|------|-------------|

| LED pins used as initial setting mode during reset |       |      |             |

11/58

| Pin no.           | Label                | Туре | Description                                                                                                                                                                                                                                             |                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------------|----------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MC operation mode |                      |      |                                                                                                                                                                                                                                                         |                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 21                | LFP                  | IPL  | Link fault pass through (LFP)  1: enable Link status of one port is forwarded to the other port.  0: disable (default)                                                                                                                                  |                                                                                                                                                                               | ` ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 22<br>23          | DIRECT_WIRE FAST_FWD | IPL  | DIRECT_<br>WIRE                                                                                                                                                                                                                                         | FAST_F<br>WD                                                                                                                                                                  | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                   |                      |      | 0                                                                                                                                                                                                                                                       | 0                                                                                                                                                                             | Store and forward switch mode (default)                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                   |                      |      | 0                                                                                                                                                                                                                                                       | 1                                                                                                                                                                             | Modified cut-through switch mode                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                   |                      |      | 1                                                                                                                                                                                                                                                       | 0                                                                                                                                                                             | Converter mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                   |                      |      | 1                                                                                                                                                                                                                                                       | 1                                                                                                                                                                             | Converter mode with auto-change-forward function                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                   |                      |      | Modified cu<br>IP113M LF<br>bytes data<br>this mode.  Converter r<br>Incoming fr<br>the min late<br>should wor<br>linked at ha<br>fiber should<br>requirement<br>Converter r<br>IP113M LF<br>speed is diff<br>In converter<br>pause fram<br>doesn't for | begins to for received. The mode: fames are not be at 100M for all duplex, the duplex, the duplex of CSMAC mode with a ferent in TF for mode, IP1 are directly. It ward IEEE8 | witch mode: brward a frame after the first 64 port should be forced at 100M at  ot buffered in IP113M LF to achieve port and fiber port of IP113M LF ull duplex in this mode. If TP port is the total length of UTP cable and an 60 meters to meet the D in IEEE802.3.  uto-change-forward function: forward mode itself if it detects the port and FX port.  13M LF forwards IEEE802.3x an the other modes, IP113M LF 02.3x pause frame directly, it sends its internal buffer is full. |

| Pin no.               | Label     | Туре  | Description                                                                                                                                                          |

|-----------------------|-----------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SMI interfa           |           |       |                                                                                                                                                                      |

| 47, 48                | MDC, MDIO | I, IO | SMI interface The external MAC device uses the interface to program IP113M LF. MDIO is an open drain.                                                                |

| 31, 32,<br>37, 12, 46 | ADDR[4:0] | IPL   | PHY address The external MAC device uses the address to identify each IP113M LF in a chassis. IP113M LF also uses ADDR[2:0] as EEPROM address A[2:0] to read EEPROM. |

| Pin no. Label Typ |          | Туре   | Description      |  |

|-------------------|----------|--------|------------------|--|

| EEPROM i          | nterface | -      |                  |  |

| 45, 46            | SDA, SCL | IPH, O | EEPROM interface |  |

| Pin no. | Label    | Туре | Description                                                                                                                                                         |

|---------|----------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Misc.   |          |      |                                                                                                                                                                     |

| 28      | RESETB   | I    | Reset It is low active.                                                                                                                                             |

| 41, 40  | OSCI, X2 | I, O | Crystal pins OSCI and X2 are connected to a 25Mhz crystal.  If a 25MHz oscillator is used, OSCI is connected to the oscillator's output and X2 should be left open. |

| 26, 27  | TSM, TSE | IPL  | Scan pins These two pins should be left open or connected to ground for normal operation.                                                                           |

| 15      | INTB     | 0    | Interrupt 0: an interrupt happens. Its output is low. 1: no interrupt. Its output is high impedance and it needs an external pull up resistor.                      |

| Pin no.           | Label  | Туре | Description                |

|-------------------|--------|------|----------------------------|

| Power             |        |      |                            |

| 1,7,11            | AVCC   |      | 2.5V Analog Power          |

| 19,39,44          | VCC    |      | 2.5V Digital Power         |

| 34                | VCC_IO |      | 3.3V or 2.5V Digital Power |

| 35                | GND_IO |      | I/O Ground                 |

| 4,10,20,<br>42,43 | GND    |      | Ground                     |

## 2. Functional Description

#### 2.1 Data forwarding

IP113M LF supports three types of data forwarding mode, store & forward mode, modified cut-through mode and pure converter mode. It can forward a frame despite of its address and CRC error. IP113M LF begins to forward the received data when it receives the frame completely. The latency depends on the packet length.

#### 2.1.1 Modified cut-through mode

IP113M LF begins to forward the received data when it receives the first 64 bytes of the frame. The latency is about 512 bits time width. The maximum packet length is up to1600 bytes in this mode. Please refer to pin description of FAST\_FWD for configuration information.

#### 2.1.2 Pure converter mode

IP113M LF operates with the minimum latency in this mode. The transmission flow does not wait until entire frame is ready, but instead it forwards the received data immediately after the data being received. Both transceivers are interconnected via internal MIIs and the internal switch engine and data buffer are not used. Both TP port and fiber port of IP113M LF should work at 100M full duplex in this mode. If TP port is linked at half duplex, the total length of UTP cable and fiber should be less than 60 meters to meet the requirement of CSMACD in IEEE802.3. The packet length is not limited at this mode. Please refer to pin description of DIRECT\_WIRE for configuration information.

In converter mode, it is strongly recommended that both TP port and fiber port of IP113M LF should work at 100M full duplex. If TP port is linked at half duplex, the UTP cable length should be less than 30 meters to meet the requirement of CSMACD in IEEE802.3.

#### 2.1.3 Fragment forwarding

IP113M LF forwards CRC error packets but it will filter fragments when it works in modified cut-through mode. IP113M LF forwards fragments if user turns on bit 3 of MII register 20.

## 2.2 TP port force mode

The TP port of IP113M LF can work at auto mode or force mode. The following table shows all of the combination of its TP port.

|                           |                           |              |       | Link | partner | 's capa | bility |     |      |  |

|---------------------------|---------------------------|--------------|-------|------|---------|---------|--------|-----|------|--|

|                           |                           | AN on AN off |       |      |         |         |        |     |      |  |

| {TP_FORCE,<br>SPEED_MODE, | IP113M LF's link result   | 100F         | 100H  | 10F  | 10H     | 100F    | 100H   | 10F | 10H  |  |

| DUPLEX_MODE}              | IP113M LF's capability    | 1001         | 10011 | 101  | 1011    | 1001    | 10011  | 101 | 1011 |  |

| 011                       | 100/10M, Full/Half, AN on | 100F         | 100H  | 10F  | 10H     | 100H    | 100H   | 10H | 10H  |  |

| 010                       | 100/10M, Half, AN on      | Х            | 100H  | Χ    | 10H     | 100H    | 100H   | 10H | 10H  |  |

| 001                       | 10M, Full/Half, AN on     | Х            | Χ     | 10F  | 10H     | 100H    | 100H   | 10H | 10H  |  |

| 000                       | 10M, Half, AN on          | Х            | Χ     | Χ    | 10H     | 100H    | 100H   | 10H | 10H  |  |

| 111                       | 100M, Full, AN on         | 100F         | Χ     | Χ    | Х       | 100F    | 100F   | Χ   | Χ    |  |

| 110                       | 100M, Half, AN on         | Х            | 100H  | Χ    | Х       | 100H    | 100H   | Χ   | Χ    |  |

| 101                       | 10M, Full, AN on          | Х            | Χ     | 10F  | Х       | Χ       | Χ      | 10F | 10F  |  |

| 100                       | 10M, Half, AN on          | Х            | Х     | Х    | 10H     | Х       | Х      | 10H | 10H  |  |

Note:

AN on: with auto-negotiation capability AN off: without auto-negotiation capability

100F: 100M full duplex 100H: 100M half duplex 10F: 10M full duplex 10H: 10M half duplex

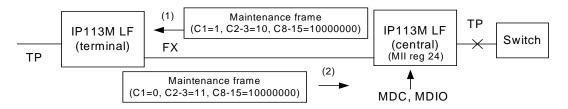

## 2.3 Remote management

IP113M LF supports remote monitor and configuration function. IP113M LF implement the function by exchanging maintenance frames on fiber ports between two IP113M LF's. The maintenance frames are not forwarded to TP ports. The frame format follows the TS-1000 standard.

#### 2.3.1 Maintenance frame format at MII

| TXD0 | F0 | F4 | C0 | C4 | C8  | C12 | S0 | S4 | S8  | S12 | M0 | M4 | M8  | M12 | M16 | M20 | M24 | M28 | M32 | M36 | M40 | M44 | E0 | E4 |

|------|----|----|----|----|-----|-----|----|----|-----|-----|----|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|----|----|

| TXD1 | F1 | F5 | C1 | C5 | C9  | C13 | S1 | S5 | S9  | S13 | M1 | M5 | M9  | M13 | M17 | M21 | M25 | M29 | M33 | M37 | M41 | M45 | E1 | E5 |

| TXD2 | F2 | F6 | C2 | C6 | C10 | C14 | S2 | S6 | S10 | S14 | M2 | M6 | M10 | M14 | M18 | M22 | M26 | M30 | M34 | M38 | M42 | M46 | E2 | E6 |

| TXD3 | F3 | F7 | C3 | C7 | C11 | C15 | S3 | S7 | S11 | S15 | МЗ | M7 | M11 | M15 | M19 | M23 | M27 | M31 | M35 | M39 | M43 | M47 | E3 | E7 |

TXEN

#### 2.3.2 Bit definition of maintenance frame

| Bit      | Item                                          |                                                   |                                                                  |      |      |               | Desc                        | riptio | on                 | Note  |

|----------|-----------------------------------------------|---------------------------------------------------|------------------------------------------------------------------|------|------|---------------|-----------------------------|--------|--------------------|-------|

| F7 – F0  | Preamble                                      | 01                                                | 010                                                              | 101  |      |               |                             |        |                    | Fixed |

| C0       | Discriminator for the maintenance signal      | 0                                                 |                                                                  |      |      |               |                             |        |                    | Fixed |

| C1       | Direction                                     | 1:                                                | cen                                                              | tral | МС   | $\rightarrow$ | centra<br>termina<br>erter) |        |                    |       |

| C3 – C2  | Command                                       | 10<br>01                                          | 00: Reserved<br>10: Indication<br>01: Request<br>11: Acknowledge |      |      |               |                             |        |                    |       |

| C7 – C4  | Version                                       | 00                                                | 0000                                                             |      |      |               |                             |        | Fixed              |       |

| C15 – C8 | Control signal                                | C15 C8 Function                                   |                                                                  |      |      |               |                             |        |                    |       |

|          |                                               | 0                                                 | 0                                                                | 0    | 0    | 0             | 0                           | 01     | Loop test start    |       |

|          |                                               | 0                                                 | 0                                                                | 0    | 0    | 0             | 0                           | 00     | Loop test finished |       |

|          |                                               | 0                                                 | 0                                                                | 0    | 0    | 0             | 0                           | 10     | Status indication  |       |

|          |                                               | Address [4:0] R/W 11 R/W link partner's registers |                                                                  |      |      |               |                             |        |                    |       |

| S0       | Condition of power                            | 0:                                                | nori                                                             | mal, | 1: p | oow           | er off                      |        |                    |       |

| S1       | Situation of receiving optical power          | 0:                                                | nor                                                              | mal, | 1: a | abn           | ormal                       |        |                    |       |

| S2       | Terminal/ network side link                   |                                                   | 0: link up, 1: link down<br>If S11="1", S2="X"                   |      |      |               |                             |        |                    |       |

| S3       | MC (media converter) fails                    | 0:                                                | 0: normal, 1: abnormal                                           |      |      |               |                             |        |                    |       |

| S4       | Informing way for optical receiving power off |                                                   | 0: maintenance frame<br>1: Far end fault indication              |      |      |               |                             |        |                    |       |

| S5       | Status indication for loop test               | 0:                                                | nori                                                             | mal  | mod  | de,           | 1: unde                     | er loo | p test             |       |

16/58

April 9, 2007

| Bit       | Item                                                                           | Description                                                                                                                                                                                  | Note |

|-----------|--------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| S6        | Information for notice of terminal link status (Available for option B or not) | O: terminal IP113M LF does not support option B.  1: terminal IP113M LF supports option B, which can inform speed, duplex, and auto-negotiation in terminal IP113M LF.  If S11 = "1", S6="X' |      |

| S8 – S7   | Terminal link speed                                                            | 00: 10 Mbps<br>01: 100 Mbps<br>10: 1000 Mbps<br>11: others<br>It is valid, if S6 = "1".<br>If S2 or S11 = "1", S7, S8 = {X, X}                                                               |      |

| S9        | Duplex for the terminal side                                                   | 1: full duplex, 0: half duplex<br>It is valid, if S6 = "1".<br>If S6 ="0", S9="0".<br>If {S7, S8} = {1,1}, S9="X"<br>If S2 or S11 = "1", S9="X"                                              |      |

| S10       | Auto-negotiation capability for the terminal side                              | 1: available, 0: un-available It is valid, if S6 = "1". If S6 ="0", S10="0". If {S7, S8} = {1,1}, S10="X" If S11 = "1", S10="X"                                                              |      |

| S11       | Number of interface in Terminal/ network side                                  | 0: one UTP<br>1: more than one UTP                                                                                                                                                           |      |

| S15 – S12 | Reserved                                                                       |                                                                                                                                                                                              |      |

| M23 – M0  | Vender code                                                                    | Vender code for TTC standard It is C30900h.                                                                                                                                                  |      |

| M47 – M24 | Model number                                                                   | Specified by vender It is 000000h.                                                                                                                                                           |      |

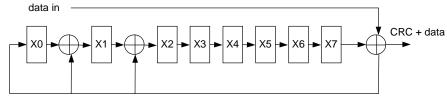

| E7 – E0   | FCS                                                                            | CRC – 8<br>FCS calculation area: C0 - M47                                                                                                                                                    |      |

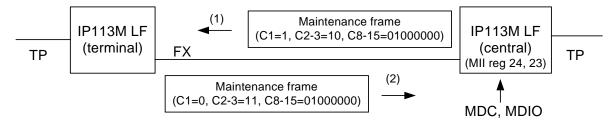

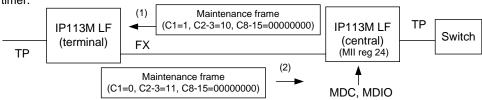

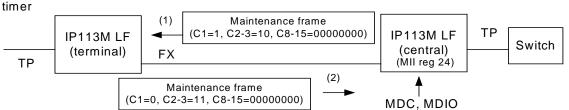

#### 2.3.4 Remote monitor

Refer to the diagram below, users can instruct central IP113M LF, on the right, to issue a status request frame to get status defined in TS-1000 by programming MII register 24. The terminal IP113M LF, on the left, receives the status request frame and sends out its current status as a response frame onto the fiber port when it is available. The central IP113M LF receives the status frame and stores the status of terminal IP113M LF to its MII register 23. An acknowledge maintenance frame is store to MII register 26~30. The status of terminal IP113M LF is shown on the LEDs of central IP113M LF.

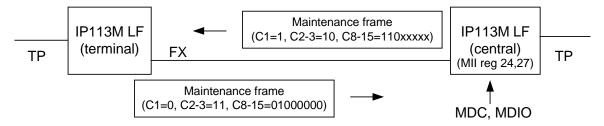

#### 2.3.5 Remote control read

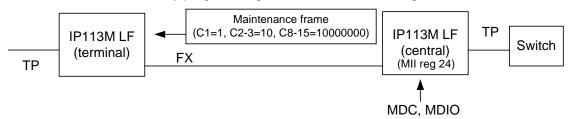

Users can instruct central IP113M LF to issue a remote control read frame to read the MII register of terminal IP113M LF by programming MII register 24. The bits [11:7] of the register 24 are filled with the address of register and bits [6:4] of the register 24 are filled with "011". The terminal IP113M LF receives the frame and sends out the content of the MII register to central IP113M LF when it is available. The central IP113M LF receives the frame and stores the data to MII register 27. An acknowledge maintenance frame is stored to MII register 26~30. The status of terminal IP113M LF is shown on LED of central IP113M LF.

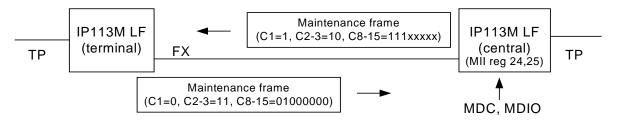

#### 2.3.6 Remote control write

Users can instruct central IP113M LF to issue a configure frame to write the MII register of terminal IP113M LF by programming MII register 24 and 25. The bits [11:7] of the register 24 are filled with the address of register and bits [6:4] of the register 24 are filled with "111". MII register 25 defines the data. The terminal IP113M LF receives the configure frame, configures itself according to the content of the frame and sends out its current status as a response frame onto the fiber port when it is available. The status of terminal IP113M LF is shown on LED of central IP113M LF.

18/58

#### 2.4 Loop back test

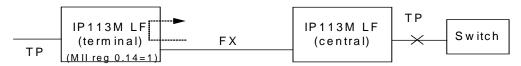

IP113M LF supports two kind of loop back test function, in-band loop back test and out-band loop back test.

#### 2.4.1 Out-band loop back test

Users can instruct central IP113M LF to issue a maintenance frame onto the fiber port by programming MII register 24 to request a loop back test. Central IP113M LF does not generate test frames and users need an external packet source from PC.

1. Disconnect switch port and instruct the terminal IP113M LF to perform loop back and disable terminal T2 timer by programming central IP113M LF through SMI

2. Terminal IP113M LF runs at loop back mode

3. PC forces test frames to central IP113M LF and terminal IP113M LF loops back the frames.

4. PC reports the loop back test result after sending all test frames.

19/58

5. Reconnect switch and instruct the central IP113M LF to end loop back test and enable T2 timer.

#### Loop back test (continued)

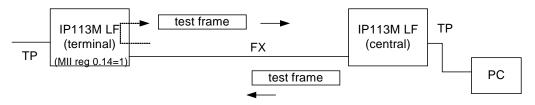

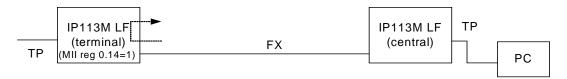

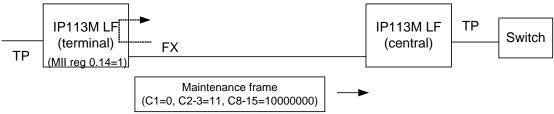

#### 2.4.2 In-band loop back test

Besides performing the loop back test with an external packet source, IP113M LF supports an easy alternative. IP113M LF sends out private maintenance frame to do loop back test. All users have to do is to program MII registers through SMI.

1. Disabe receive function of central TP port and instruct the terminal IP113M LF to perform loop back and disable T2 timer by programming central IP113M LF through SMI

2. Terminal IP113M LF runs at loop back mode and acknowledges with maintenance frame

3. Central IP113M LF forces test frames to terminal IP113M LF and terminal IP113M LF loops back the test frames. Central IP113M LF checks the received test frame.

4. Central IP113M LF ends loop back test enables receive function of TP port and enable LP T2

21/58

## Loop back test (continued)

2.4.3 Programming procedure for In-band loop back test

| Step | Description                                                                                        | C1 | C3~C2 | C15~C8      | Note                      |

|------|----------------------------------------------------------------------------------------------------|----|-------|-------------|---------------------------|

| 1    | Set local IP113M LF TP receive disabled                                                            |    |       |             | Set Reg. 20.14 off        |

| 2a   | Set remote T2 timer disabled by maintenance frame                                                  | 1  | 01    | 11 11 11 11 | Reg24 and Reg 25          |

| 2    | Set remote IP113M LF to be loop back mode enabled by maintenance frame                             | 1  | 01    | 00 00 00 01 | TS-1000: loop<br>back set |

| 3    | Remote IP113M LF sends back loop back acknowledge                                                  |    |       |             |                           |

| 4    | Send loop back test maintenance frame                                                              | 1  | 01    | 11 01 10 11 | Reg24 and Reg 25          |

| 5    | Remote IP113M LF send back acknowledge                                                             |    |       |             |                           |

| 6    | Local IP113M LF stores the loop back maintenance to Reg. 26~30 and checks CRC bit is in Reg. 26.12 |    |       |             |                           |

| 7    | Repeat step 4~6 continuously                                                                       |    |       |             |                           |

| 8    | Set remote IP113M LF to be loop back mode disable by maintenance frame                             | 1  | 01    | 00 00 00 00 | TC-1000: loop<br>back end |

| 9    | Remote IP113M LF sends back loop back acknowledge                                                  |    |       |             |                           |

| 10   | Set local IP113M LF TP receive enable                                                              |    |       |             | Set Reg. 20.14 on         |

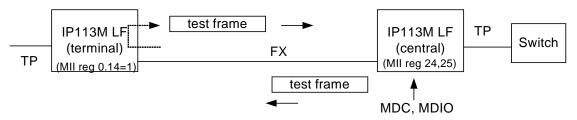

2.4.4 Auto in-band loop back test

| Step | Description                                                                                                                                                                            |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | Set pin AUTO_TEST to "1" (The following step is executed automatically by IP113M LF)                                                                                                   |

| 1.1  | Central IP113M LF sends loop back start request to remote IP113M LF and goes to CST2 state.                                                                                            |

| 1.2  | Remote IP113M LF sends loop back start acknowledge to Central IP113M LF and enters loop back test mode.                                                                                |

| 1.3  | Central IP113M LF goes to CST1 state and begins sending 15 frames in 64 bytes.                                                                                                         |

| 1.4  | Remote IP113M LF loops back the received frames at the TP port's PMD sub-layer.                                                                                                        |

| 1.5  | Central IP113M LF checks the loop back frames and reports the result.                                                                                                                  |

| 2    | The LED pin LED_RMT_TP_LINK is Flash (on 80ms / off 20ms) during the auto loop back test period (AUTO_TEST is "1").                                                                    |

| 3    | The LED pin LED_RMT_TP_SPD indicates the loop back test complete (on) (when AUTO_TEST is "1"). The LED pin LED_RMT_TP_FDX indicates the loop back test ok (on) (when AUTO_TEST is "1") |

| 4    | If another auto loop back test is needed, set AUTO_TEST to "0" and then "1". That is, AUTO_TEST is triggered whenever there is a low-to-high transition on this pin.                   |

#### Remote monitor without SMI programming

#### 2.5.1 Auto sends (Status change notice)

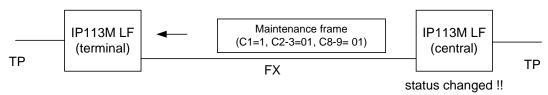

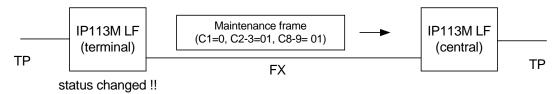

IP113M LF sends out status frame without receiving status request frame if pin AUTO SEND is pulled high. It sends out the first status frame onto the fiber port when the link status of fiber port has established. It sends out status frames when the status on TP port has changed. IP113M LF supports two types of frame. For a TS-1000 maintenance frame, C[9:8] is 2'b10 and S[15:0] is defined as that in TS-1000 standard. For an ICplus maintenance frame, C[9:8] is 2'b11 and S[15:0] is the content of MII register 22. It carries ICplus private defined information. User can select the frame type by programming MII register 20.10. Central IP113M LF uses the mechanism to get the status of the remote IP113M LF even if there is no SMI programming.

#### Option A

Central IP113M LF sends indication frames to terminal IP113M LF if its status is changed.

#### Option B

Terminal IP113M LF sends indication frames to central IP113M LF if its status is changed.

23/58

CRC polynomial for maintenance frame: X8 + X2 + X + 1

**CRC** calculation

April 9, 2007

#### 2.6 Link fault pass through

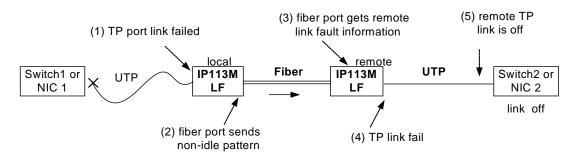

When link fault pass through function is enabled, link status on TX port will inform the FX port of the same device and vice versa. From the link fault pass through procedure illustrates in the figure below, if link fail happens on IP113M LF's TX port (1), the local FX port sends non-idle pattern to notice the remote FX port (2). The remote FX port then forces its TX port to link failed after receiving the non-idle pattern (4). In other words, this mechanism will alert the link fault status of local TX port to the remote converter's TX port, and the link status of the remote TX port will become off. Link status LED will also be off for both IP113M LF and its link partner.

The procedure of link fault pass through

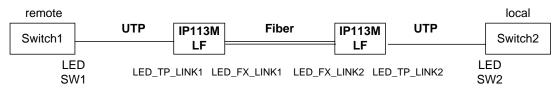

#### 2.6.1 Normal case

| L | ink LED on SW1 | LED_TP_LINK1 | LED_FX_LINK1 | LED_FX_LINK2 | LED_TP_LINK2 | Link LED on SW2 |

|---|----------------|--------------|--------------|--------------|--------------|-----------------|

|   | ON             | ON           | ON           | ON           | ON           | ON              |

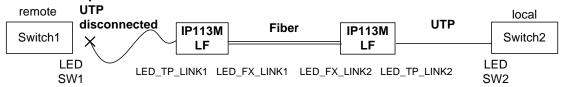

#### 2.6.2 Remote TP port disconnected

| Link LED on SW1 | LED_TP_LINK1 | LED_FX_LINK1 | LED_FX_LINK2 | LED_TP_LINK2 | Link LED on SW2 |

|-----------------|--------------|--------------|--------------|--------------|-----------------|

| Off             | Off          | Off          | Off          | Off          | Off             |

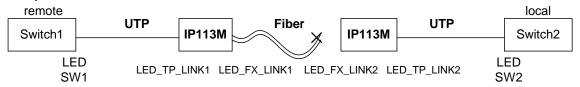

#### 2.6.3 FX port disconnected

| Link LED on SW1 | LED_TP_LINK1 | LED_FX_LINK1 | LED_FX_LINK2 | LED_TP_LINK2 | Link LED on SW2 |

|-----------------|--------------|--------------|--------------|--------------|-----------------|

| Off             | Off          | Off          | Off          | Off          | Off             |

2.6.4 LED diagnostic functions for fault indication

|             |             | 1         |                |                                |

|-------------|-------------|-----------|----------------|--------------------------------|

| LED_TP_LINK | LED_FX_LINK | LED_FX_SD | LED_FX_FEF_DET | Status                         |

| On          | On          | On Off    |                | Link ok                        |

| Flash       | Flash       | On        | Off            | Link ok & activity             |

| Off         | Off         | On        | Off            | Remote TP link off             |

| Off         | Off         | Off       | Off            | Fiber RX off, Fiber TX/ RX off |

| Off         | Off         | On        | Flash          | Fiber TX off                   |

Note

Flash: flash, period 100 ms

Link fault pass through is enabled.

#### 2.7 EEPROM – store the initial value

IP113M LF supports two ways to load initial value of MII registers. The procedure is illustrated as below.

1. IP113M LF reads the default setting of MII register from pins

2. IP113M LF updates the default setting of MII by reading EEPROM. If there exists an EEPROM.

3. After reading EEPROM, IP113M LF is virtually isolated from the EEPROM. Micro-controller can program both MII register and EEPROM.

4. IP113M LF reloads the content of EEPROM to recover the value in MII registers programmed by Micro-controller after power on reset.

26/58

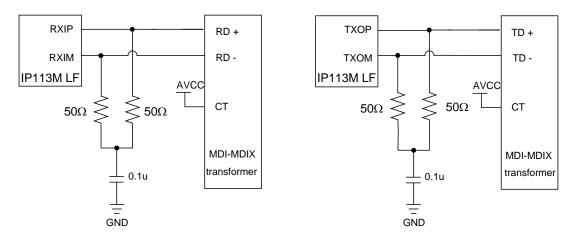

## 2.8 Auto MDI\_MDIX

IP113M LF supports auto MDI-MDIX. It is always enabled. The following is its application circuit for auto MDI-MDIX.

IP113M LF's application circuit (auto MDI-MDIX on)

#### 2.9 Serial management interface

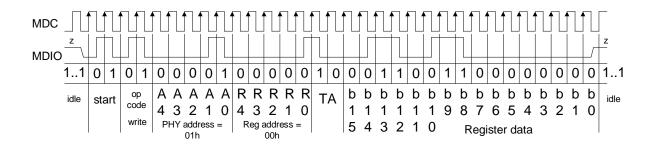

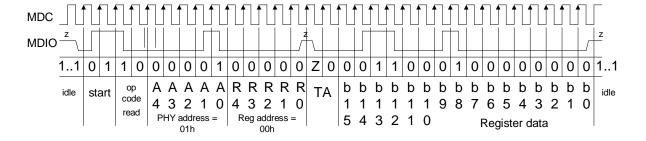

User can access IP113M LF's MII registers through serial management interface MDC and MDIO. A specific pattern on MDIO is used to access a MII register. Its format is shown in the following table. When the SMI is idle, MDIO is in high impedance. To initialize the MDIO interface, the management entity sends a sequence of 32 contiguous "1" and "start" on MDIO.

| Frame<br>format    | <ld><ldle><start><op code=""><ip113m address="" lf's=""><registers<br>address&gt;<turnaround><br/><data><idle></idle></data></turnaround></registers<br></ip113m></op></start></ldle></ld>                                                                                                                                                                                                                                                                             |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Read<br>Operation  | <Idle> $<$ 01> $<$ 10> $<$ A <sub>4</sub> A <sub>3</sub> A <sub>2</sub> A <sub>1</sub> A <sub>0</sub> > $<$ R <sub>4</sub> R <sub>3</sub> R <sub>2</sub> R <sub>1</sub> R <sub>0</sub> > $<$ Z0> $<$ b <sub>15</sub> b <sub>14</sub> b <sub>13</sub> b <sub>12</sub> b <sub>11</sub> b <sub>10</sub> b <sub>9</sub> b <sub>8</sub> b <sub>7</sub> b <sub>6</sub> b <sub>5</sub> b <sub>4</sub> b <sub>3</sub> b <sub>2</sub> b <sub>1</sub> b <sub>0</sub> > $<$ Idle> |

| Write<br>Operation | $< dle><01><01><10> < dle>$                                                                                                                                                                                                                                                                                                                                                                                                                                            |

28/58

## 3. MII registers

| Address | Register Name                                | Control |

|---------|----------------------------------------------|---------|

| 0       | Control Register                             | NWAY    |

| 1       | Status Register                              | NWAY    |

| 2       | PHY identifier Register 1                    | NWAY    |

| 3       | PHY identifier Register 2                    | NWAY    |

| 4       | AN Advertisement Register                    | NWAY    |

| 5       | AN Link Partner Base Page Ability Register   | NWAY    |

| 6       | AN Expansion Register                        | NWAY    |

| 7       | (Reserved)                                   |         |

| 8       | (Reserved)                                   |         |

| 9       | (Reserved)                                   |         |

| 10      | (Reserved)                                   |         |

| 11      | (Reserved)                                   |         |

| 12      | (Reserved)                                   |         |

| 13      | (Reserved)                                   |         |

| 14      | (Reserved)                                   |         |

| 15      | (Reserved)                                   |         |

| 16      | Special Control Register                     | NWAY    |

| 17      | Interrupt Register                           | NWAY    |

| 18      | Extended Status Register                     | NWAY    |

| 19      | Statistic Counter Register                   | SWITCH  |

| 20      | Switch Configuration Register 1              | SWITCH  |

| 21      | Switch Configuration Register 2              | SWITCH  |

| 22      | Local Switch Extended Register               | SWITCH  |

| 23      | Link Partner Switch Extended Status Register | SWITCH  |

| 24      | Remote Control Transmit Register 1           | RMC     |

| 25      | Remote Control Transmit Register 2           | RMC     |

| 26      | Remote Control Receive Register 1            | RMC     |

| 27      | Remote Control Receive Register 2            | RMC     |

| 28      | Remote Control Receive Register 3            | RMC     |

| 29      | Remote Control Receive Register 4            | RMC     |

| 30      | Remote Control Receive Register 5            | RMC     |

| 31      | Switch Configuration Register 3              | SWITCH  |

## 3.1 The basic MII registers

| Туре   | Description                                                                      |

|--------|----------------------------------------------------------------------------------|

| R/W    | Read/Write                                                                       |

| SC     | Self-Clearing                                                                    |

| RO     | Read Only                                                                        |

| Pin(1) | The default value is "1" and it depends on the setting of its corresponding pin. |

| Туре   | Description                                                                      |

|--------|----------------------------------------------------------------------------------|

| RC     | Read and Clear                                                                   |

| LL     | Latching Low                                                                     |

| LH     | Latching High                                                                    |

| Pin(0) | The default value is "0" and it depends on the setting of its corresponding pin. |

## The basic MII registers 0

| MII                                | NAME                       | R/W       | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                           | DEFAULT |  |

|------------------------------------|----------------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--|

| MII control register (address 00h) |                            |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |  |

| 0.15                               | Reset                      | R/W<br>SC | 1 = PHY reset 0 = normal operation This bit is self-clearing, IP113M LF will return a value of 1 before reset process is completed, and will not accept any write transaction of MII Management within reset process. Make any change to Auto-Negotiation or speed mode will cause IP113M LF reset again.                                                                                                                                             | 0       |  |

| 0.14                               | Loop back                  | R/W       | 1 = Loop back mode 0 = normal operation When this bit is set, IP113M LF will be isolated from the network media, and the assertion of TXEN at the MII will not transmit data on the network. All MII transmit data path will return to MII receive data path in response to the assertion of TXEN. MII COL signal will remain de-asserted at all times, unless bit 0.7 (Collision Test) is set. Use has to wait about 100ms for loop back path ready. | 0       |  |

| 0.13                               | Speed Selection            | RW        | 1 = 100Mbps<br>0 = 10Mbps<br>It is valid only if bit 0.12 is set to be 0.                                                                                                                                                                                                                                                                                                                                                                             | Pin(1)  |  |

| 0.12                               | Auto-Negotiation<br>Enable | RW        | 1 = Auto-Negotiation Enable 0 = Auto-Negotiation Disable MII register 16.11 auto-MDI/MDIX should be disabled if auto-negotiation is disabled.                                                                                                                                                                                                                                                                                                         | 1       |  |

| 0.11                               | Reserved                   | R/W       | This bit should be "0" for normal operation.                                                                                                                                                                                                                                                                                                                                                                                                          | 0       |  |

| 0.10                               | Isolate                    | R/W       | 1 = electrically isolate PHY from MII 0 = normal operation When this bit is setting to 1, IP113M LF will be isolated from MII, and not respond to the TXD[3:0] and TXEN and keep CRS, RXDV and RXD[3:0] in high impedance, but will respond to management transactions.                                                                                                                                                                               | 0       |  |

| MII                                | NAME                         | R/W | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | DEFAULT |  |

|------------------------------------|------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--|