#### 查询IRS2153供应商

#### 专业PCB打样工厂,24小时加急出货

Data Sheet No. PD60238 revE

# International ISR Rectifier

## IRS2153(1)D(S)PbF

### SELF-OSCILLATING HALF-BRIDGE DRIVER IC

#### **Features**

- Integrated 600 V half-bridge gate driver

- C<sub>T</sub>, R<sub>T</sub> programmable oscillator

- 15.4 V Zener clamp on V<sub>CC</sub>

- Micropower startup

- Non-latched shutdown on  $C_T$  pin (1/6th  $V_{CC}$ )

- Internal bootstrap FET

- Excellent latch immunity on all inputs and outputs

- +/- 50 V/ns dV/dt immunity

- ESD protection on all pins

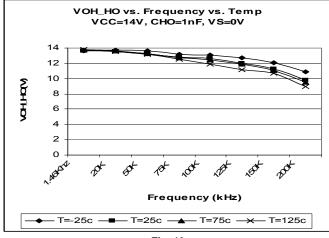

- 8-lead SOIC or PDIP package

- Internal deadtime

#### Description

The IRS2153(1)D is based on the popular IR2153 selfoscillating half-bridge gate driver IC using a more advanced silicon platform, and incorporates a high voltage half-bridge gate driver with a front end oscillator similar to the industry standard CMOS 555 timer. HVIC and latch immune CMOS technologies enable rugged monolithic construction. The output driver features a high pulse current buffer stage designed for minimum driver cross-conduction. Noise immunity is achieved with low di/dt peak of the gate drivers.

#### **Product Summary**

15.4 V typ.

Deadtime

V<sub>clamp</sub>

1.1 μs typ. (IRS2153D)

50%

0.6 μs typ. (IRS21531D)

#### Package

# International **IOR** Rectifier

### Absolute Maximum Ratings

Absolute maximum ratings indicate sustained limits beyond which damage to the device may occur. All voltage parameters are absolute voltages referenced to COM, all currents are defined positive into any lead. The thermal resistance and power dissipation ratings are measured under board mounted and still air conditions.

|                          | Parameter                                                                              |                     |                       |       |  |

|--------------------------|----------------------------------------------------------------------------------------|---------------------|-----------------------|-------|--|

| Symbol                   | Definition                                                                             | Min.                | Max.                  | Units |  |

| VB                       | High side floating supply voltage                                                      | -0.3                | 625                   |       |  |

| Vs                       | High side floating supply offset voltage                                               | V <sub>B</sub> - 25 | V <sub>B</sub> + 0.3  | V     |  |

| $V_{\text{HO}}$          | High side floating output voltage $V_{\rm S} - 0.3$ $V_{\rm B} + 0$                    |                     |                       |       |  |

| $V_{\text{lo}}$          | Low side output voltage                                                                | -0.3                | V <sub>CC</sub> + 0.3 |       |  |

| I <sub>RT</sub>          | R <sub>T</sub> pin current                                                             | -5                  | 5                     | mA    |  |

| V <sub>RT</sub>          | R⊤ pin voltage                                                                         | -0.3                | V <sub>CC</sub> + 0.3 |       |  |

| V <sub>CT</sub>          | C⊤ pin voltage                                                                         | -0.3                | V <sub>CC</sub> + 0.3 | V     |  |

| Icc                      | Supply current (Note 1)                                                                |                     | 20                    |       |  |

| I <sub>OMAX</sub>        | Maximum allowable current at LO and HO due to external power transistor Miller effect. | -500                | 500                   | mA    |  |

| dV <sub>S</sub> /dt      | Allowable offset voltage slew rate                                                     | -50                 | 50                    | V/ns  |  |

| PD                       | Maximum power dissipation @ $T_A \le +25 \text{ °C}$ , 8-Pin DIP                       |                     | 1.0                   |       |  |

| PD                       | Maximum power dissipation @ $T_A \le +25 \text{ °C}$ , 8-Pin SOIC                      |                     | 0.625                 | W     |  |

| R <sub>thJA</sub>        | Thermal resistance, junction to ambient, 8-Pin DIP                                     |                     | 85                    |       |  |

| <b>R</b> <sub>thJA</sub> | R <sub>thJA</sub> Thermal resistance, junction to ambient, 8-Pin SOIC                  |                     | 128                   | °C/W  |  |

| TJ                       | Junction temperature                                                                   | -55                 | 150                   |       |  |

| Ts                       | Storage temperature                                                                    | -55                 | 150                   | °C    |  |

| TL                       | Lead temperature (soldering, 10 seconds)                                               |                     | 300                   | 1     |  |

**Note 1:** This IC contains a zener clamp structure between the chip V<sub>CC</sub> and COM which has a nominal breakdown voltage of 15.4 V. Please note that this supply pin should not be driven by a DC, low impedance power source greater than the V<sub>CLAMP</sub> specified in the Electrical Characteristics section.

## International **IOR** Rectifier

### **Recommended Operating Conditions**

For proper operation the device should be used within the recommended conditions.

|                 | Parameter                                        |                           |                       |       |

|-----------------|--------------------------------------------------|---------------------------|-----------------------|-------|

| Symbol          | Definition                                       | Min.                      | Max.                  | Units |

| V <sub>BS</sub> | High side floating supply voltage                | V <sub>CC</sub> - 0.7     | V <sub>CLAMP</sub>    |       |

| Vs              | Steady state side floating supply offset voltage | -3.0 (Note 2)             | 600                   | V     |

| V <sub>CC</sub> | Supply voltage                                   | V <sub>CCUV+</sub> +0.1 V | V <sub>CC CLAMP</sub> |       |

| Icc             | Supply current                                   | (Note 3)                  | 5                     | mA    |

| TJ              | Junction temperature                             | -40                       | 125                   | °C    |

- Note 2: It is recommended to avoid output switching conditions where the negative-going spikes at the  $V_S$  node would decrease  $V_S$  below ground by more than -5 V.

- **Note 3:** Enough current should be supplied to the V<sub>CC</sub> pin of the IC to keep the internal 15.6 V zener diode clamping the voltage at this pin.

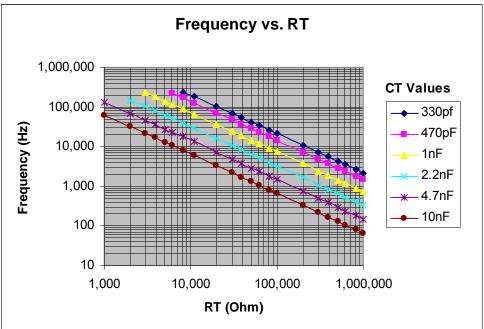

#### **Recommended Component Values**

| Parameter        |                                    |      |      |       |

|------------------|------------------------------------|------|------|-------|

| Symbol Component |                                    | Min. | Max. | Units |

| R⊤               | Timing resistor value              | 1    |      | kΩ    |

| Ст               | C <sub>T</sub> pin capacitor value | 330  |      | pF    |

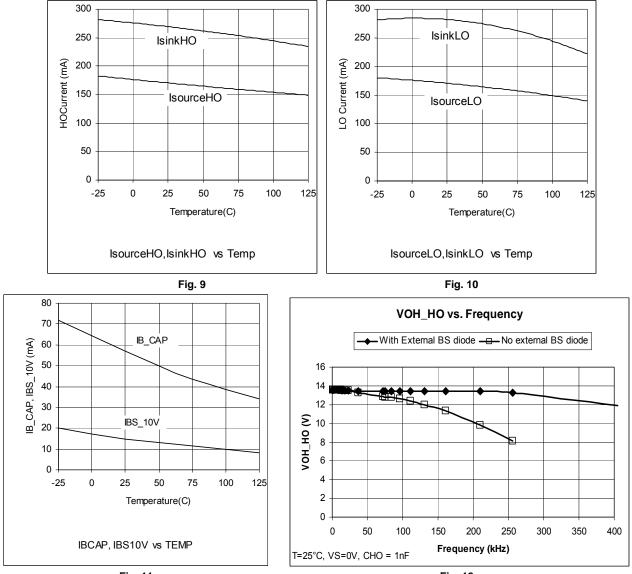

$V_{BIAS}~(V_{CC},~V_{BS})$  = 14 V,  $V_{S}$  =0 V and  $T_{A}$  = 25 °C, CLO = CHO = 1 nF.

For further information, see Fig. 12.

# International **ICR** Rectifier

### **Electrical Characteristics**

$V_{BIAS}$  ( $V_{CC}$ ,  $V_{BS}$ ) = 14 V,  $C_T$  = 1 nF,  $V_S$ =0 V and  $T_A$  = 25 °C unless otherwise specified. The output voltage and current ( $V_o$  and  $I_o$ ) parameters are referenced to COM and are applicable to the respective output leads: HO or LO. CLO = CHO = 1 nF.

| Symbol                | Definition                                                   | Min  | Тур  | Max  | Units | Test Conditions                                     |

|-----------------------|--------------------------------------------------------------|------|------|------|-------|-----------------------------------------------------|

| Low Volt              | age Supply Characteristics                                   |      |      |      |       |                                                     |

| V <sub>CCUV+</sub>    | Rising V <sub>CC</sub> undervoltage lockout threshold        | 10.0 | 11.0 | 12.0 |       |                                                     |

| V <sub>CCUV</sub> -   | Falling V <sub>CC</sub> undervoltage lockout threshold       | 8.0  | 9.0  | 10.0 | V     |                                                     |

| V <sub>CCUVHYS</sub>  | V <sub>CC</sub> undervoltage lockout hysteresis              | 1.6  | 2.0  | 2.4  |       |                                                     |

| I <sub>QCCUV</sub>    | Micropower startup $V_{CC}$ supply current                   |      | 130  | 170  | μA    | $V_{CC} \leq V_{CCUV}$                              |

| locc                  | Quiescent V <sub>CC</sub> supply current                     |      | 800  | 1000 | μΑ    |                                                     |

| lcc                   | V <sub>CC</sub> supply current                               |      | 1.8  |      | mA    | R <sub>T</sub> = 36.9 kΩ                            |

| $V_{\text{CC CLAMP}}$ | V <sub>CC</sub> zener clamp voltage                          | 14.4 | 15.4 | 16.8 | V     | I <sub>CC</sub> = 5 mA                              |

| Floating              | Supply Characteristics                                       |      |      |      |       |                                                     |

| I <sub>QBS</sub>      | Quiescent V <sub>BS</sub> supply current                     |      | 60   | 80   | μA    |                                                     |

| $V_{BSUV+}$           | V <sub>BS</sub> supply undervoltage positive going threshold | 8.0  | 9.0  | 9.5  | V     |                                                     |

| VBSUV-                | V <sub>BS</sub> supply undervoltage negative going threshold | 7.0  | 8.0  | 9.0  | v     |                                                     |

| I <sub>LK</sub>       | Offset supply leakage current                                |      |      | 50   | μA    | V <sub>B</sub> = V <sub>S</sub> = 600 V             |

| Oscillato             | r I/O Characteristics                                        | 1    |      |      |       |                                                     |

| £                     |                                                              | 18.4 | 19.0 | 19.6 | kHz   | R <sub>T</sub> = 36.5 kΩ                            |

| fosc                  | Oscillator frequency                                         | 88   | 93   | 100  | КПД   | R <sub>T</sub> = 7.15 kΩ                            |

| d                     | R⊤ pin duty cycle                                            |      | 50   |      | %     | f <sub>o</sub> < 100 kHz                            |

| I <sub>CT</sub>       | $C_T$ pin current                                            |      | 0.02 | 1.0  | μA    |                                                     |

| I <sub>CTUV</sub>     | UV-mode $C_T$ pin pulldown current                           | 0.20 | 0.30 | 0.6  | mA    | $V_{CC}$ = 7 V                                      |

| V <sub>CT+</sub>      | Upper $C_T$ ramp voltage threshold                           |      | 9.32 |      |       |                                                     |

| V <sub>CT</sub> -     | Lower $C_T$ ramp voltage threshold                           |      | 4.66 |      | V     |                                                     |

| V <sub>CTSD</sub>     | $C_T$ voltage shutdown threshold                             | 2.2  | 2.3  | 2.4  |       |                                                     |

| V <sub>RT+</sub>      | High-level $R_T$ output voltage, $V_{CC}$ - $V_{RT}$         |      | 10   | 50   |       | I <sub>RT</sub> = -100 μA                           |

| VRI+                  |                                                              |      | 100  | 300  |       | I <sub>RT</sub> = -1 mA                             |

| V <sub>RT-</sub>      | Low-level R⊤ output voltage                                  |      | 10   | 50   |       | I <sub>RT</sub> = 100 μA                            |

| v KI-                 |                                                              |      | 100  | 300  |       | I <sub>RT</sub> = 1 mA                              |

| VRTUV                 | UV-mode $R_T$ output voltage                                 |      | 0    | 100  |       | $V_{CC} \leq V_{CCUV}$                              |

| V <sub>RTSD</sub>     | SD-mode $R_T$ output voltage, $V_{CC}$ - $V_{RT}$            |      | 10   | 50   | mV    | I <sub>RT</sub> = -100 μA,<br>V <sub>CT</sub> = 0 V |

|                       |                                                              |      | 100  | 300  |       | I <sub>RT</sub> = -1 mA,<br>V <sub>CT</sub> = 0 V   |

# International **tor** Rectifier

### **Electrical Characteristics**

$V_{BIAS}$  ( $V_{CC}$ ,  $V_{BS}$ ) = 14 V,  $C_T$  = 1 nF,  $V_S$ =0 V and  $T_A$  = 25 °C unless otherwise specified. The output voltage and current ( $V_o$  and  $I_o$ ) parameters are referenced to COM and are applicable to the respective output leads: HO or LO. CLO = CHO = 1 nF.

| Symbol             | Definition                                   | Min  | Тур             | Max  | Units      | Test Conditions                                                                      |

|--------------------|----------------------------------------------|------|-----------------|------|------------|--------------------------------------------------------------------------------------|

| Gate Driv          | ver Output Characteristics                   |      |                 |      |            |                                                                                      |

| V <sub>OH</sub>    | High-level output voltage                    |      | V <sub>CC</sub> |      |            |                                                                                      |

| V <sub>OL</sub>    | Low-level output voltage                     |      | COM             |      | V          | l <sub>O</sub> = 0 A                                                                 |

| V <sub>OL_UV</sub> | UV-mode output voltage                       |      | СОМ             |      |            | $\label{eq:loss} \begin{array}{l} I_O = 0 \ A, \\ V_{CC} \leq V_{CCUV}. \end{array}$ |

| tr                 | Output rise time                             |      | 120             | 220  |            |                                                                                      |

| t <sub>f</sub>     | Output fall time                             |      | 50              | 80   | ns         |                                                                                      |

| t <sub>sd</sub>    | Shutdown propagation delay                   |      | 350             |      |            |                                                                                      |

| t <sub>d</sub>     | Output deadtime (HO or LO) (IRS2153D)        | 0.65 | 1.1             | 1.75 | μS         |                                                                                      |

| t <sub>d</sub>     | Output deadtime (HO or LO) (IRS21531D)       | 0.35 | 0.6             | 0.85 | μS         |                                                                                      |

| I <sub>O+</sub>    | Output source current                        |      | 180             |      | <b>m A</b> |                                                                                      |

| I <sub>O-</sub>    | Output sink current                          |      | 260             |      | mA         |                                                                                      |

| Bootstra           | p FET Characteristics                        |      |                 |      |            |                                                                                      |

| $V_{B_ON}$         | $V_{\text{B}}$ when the bootstrap FET is on  |      | 13.7            |      | V          |                                                                                      |

| $I_{B_{CAP}}$      | $V_{\text{B}}$ source current when FET is on | 40   | 55              |      | mA         | C <sub>BS</sub> =0.1 uF                                                              |

| I <sub>B_10V</sub> | $V_{\text{B}}$ source current when FET is on | 10   | 12              |      | IIIA       | V <sub>B</sub> =10 V                                                                 |

# International **tor** Rectifier

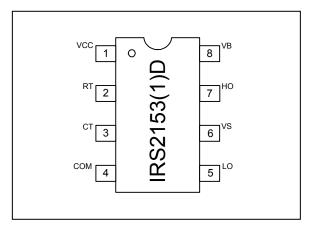

### Lead Definitions

|        | Lead                                         |  |  |  |  |

|--------|----------------------------------------------|--|--|--|--|

| Symbol | Description                                  |  |  |  |  |

| Vcc    | Logic and internal gate drive supply voltage |  |  |  |  |

| RT     | Oscillator timing resistor input             |  |  |  |  |

| CT     | Oscillator timing capacitor input            |  |  |  |  |

| COM    | IC power and signal ground                   |  |  |  |  |

| LO     | Low-side gate driver output                  |  |  |  |  |

| Vs     | High voltage floating supply return          |  |  |  |  |

| НО     | High-side gate driver output                 |  |  |  |  |

| VB     | High side gate driver floating supply        |  |  |  |  |

## International **IOR** Rectifier

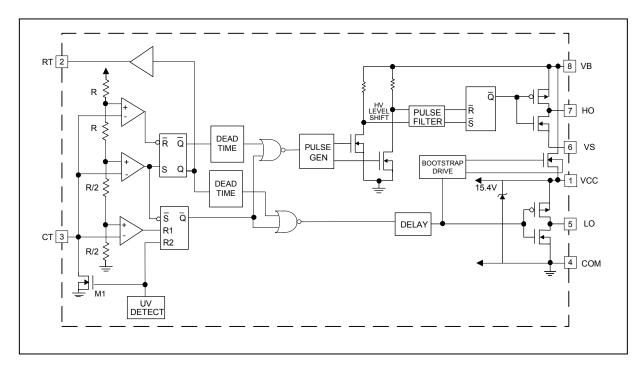

### **Functional Block Diagram**

## International **ICR** Rectifier

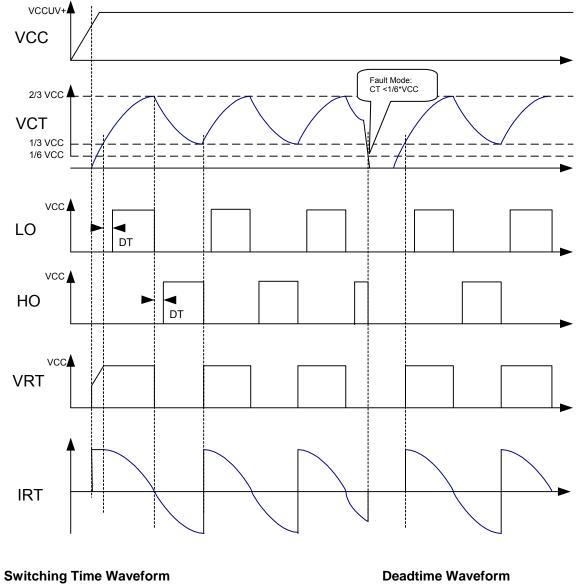

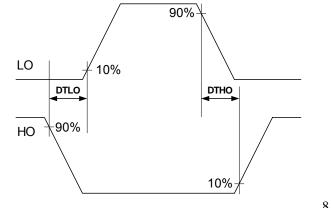

### **Timing Diagram**

#### **Operating Mode**

tf tr 90% HO LO 10%

# International **tor** Rectifier

#### **Functional Description**

#### Under-voltage Lock-Out Mode (UVLO)

The under-voltage lockout mode (UVLO) is defined as the state the IC is in when V<sub>CC</sub> is below the turn-on threshold of the IC. The IRS2153(1)D under voltage lock-out is designed to maintain an ultra low supply current of less than 170  $\mu$ A, and to guarantee the IC is fully functional before the high and low side output drivers are activated. During under voltage lock-out mode, the high and low-side driver outputs HO and LO are both low.

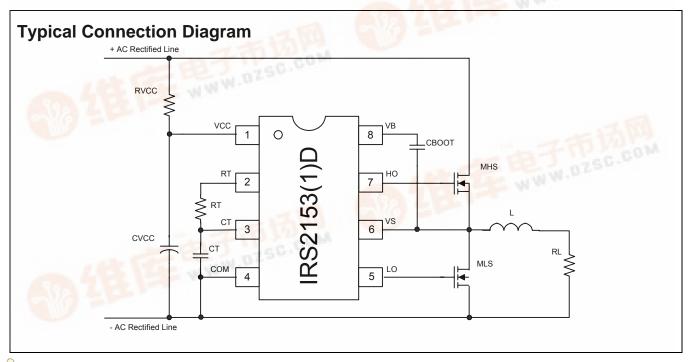

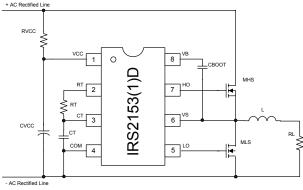

#### Supply voltage

Fig. 1 Typical Connection Diagram

Fig. 1 shows an example of supply voltage. The start-up capacitor ( $C_{VCC}$ ) is charged by current through supply resistor ( $R_{VCC}$ ) minus the start-up current drawn by the IC. This resistor is chosen to provide sufficient current to supply the IRS2153(1)D from the DC bus.  $C_{VCC}$  should be large enough to hold the voltage at VCc above the UVLO threshold for one half cycle of the line voltage as it will only be charged at the peak, typically 0.1 uF. It will be necessary for  $R_{VCC}$  to dissipate around 1 W.

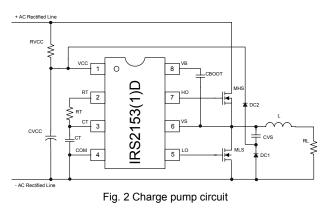

The use of a two diode charge pump made of DC1, DC2 and CVS (Fig. 2) from the half bridge (V<sub>s</sub>) is also possible however the above approach is simplest and the dissipation in  $R_{VCC}$  should not be unacceptably high.

The supply resistor ( $R_{VCC}$ ) must be selected such that enough supply current is available over all operating conditions.

Once the capacitor voltage on  $V_{\rm CC}$  reaches the start-up threshold  $V_{\rm CCUV+}, \ the IC turns on and HO and LO begin to oscillate.$

## IRS2153(1)D

#### **Bootstrap MOSFET**

The internal bootstrap FET and supply capacitor ( $C_{BOOT}$ ) comprise the supply voltage for the high side driver circuitry. The internal boostrap FET only turns on when LO is high. To guarantee that the high-side supply is charged up before the first pulse on pin HO, the first pulse from the output drivers comes from the LO pin.

#### Normal operating mode

Once the V<sub>CCUV+</sub> threshold is passed, the MOSFET M1 opens, RT increases to approximately V<sub>CC</sub> (V<sub>CC</sub>-V<sub>RT+</sub>) and the external CT capacitor starts charging. Once the CT voltage reaches V<sub>CT</sub>- (about 1/3 of V<sub>CC</sub>), established by an internal resistor ladder, LO turns on with a delay equivalent to the deadtime (t<sub>d</sub>). Once the CT voltage reaches V<sub>CT+</sub> (approximately 2/3 of V<sub>CC</sub>), LO goes low, RT goes down to approximately ground (V<sub>RT</sub>), the CT capacitor discharges and the deadtime circuit is activated. At the end of the deadtime, HO goes high again, the deadtime is activated. At the end of the deadtime, LO goes high and the cycle starts over again.

The following equation provides the oscillator frequency:

$$f \sim \frac{1}{1.453 \times RT \times CT}$$

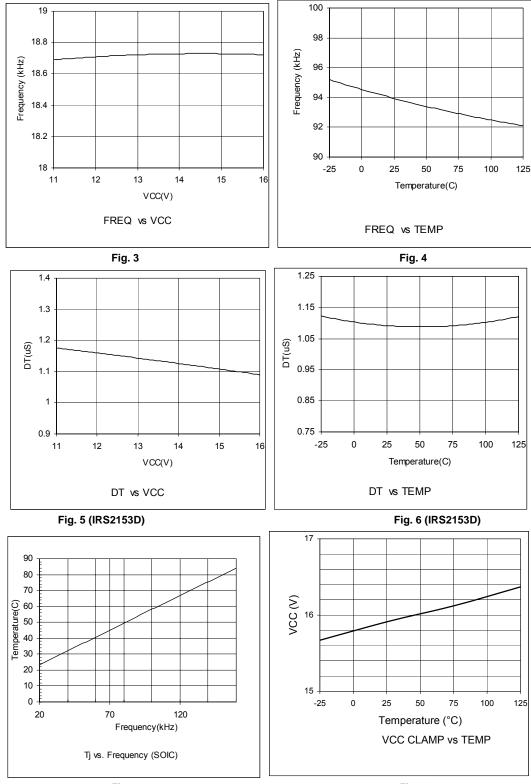

This equation can vary slightly from actual measurements due to internal comparator over- and under-shoot delays. For a more accurate determination of the output frequency, the frequency characteristic curves should be used (RT vs. Frequency, page 3).

#### Shut-down

If CT is pulled down below  $V_{CTSD}$  (approximately 1/6 of  $V_{cc})$  by an external circuit, CT doesn't charge up and oscillation stops. LO is held low and the bootstrap FET is off. Oscillation will resume once CT is able to charge up again to  $V_{CT}.$

# International **tor** Rectifier

# International **ICR** Rectifier

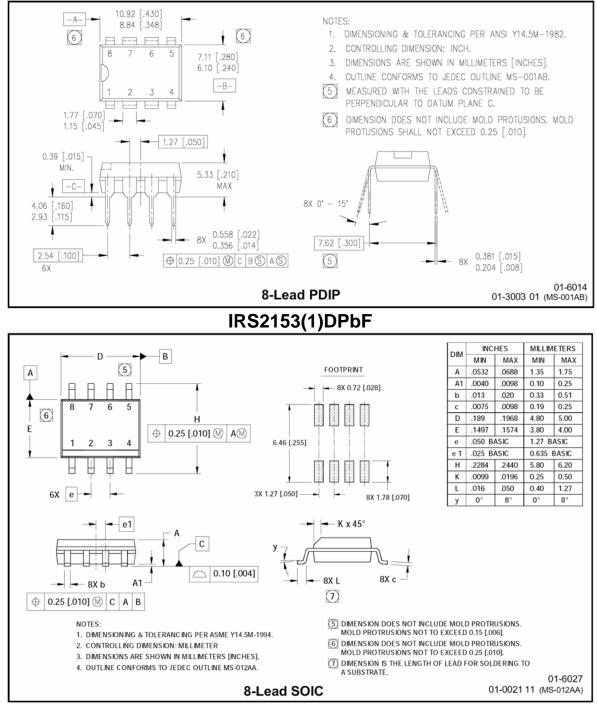

Fig. 12

Fig. 13

# International **IOR** Rectifier

## International **IGR** Rectifier

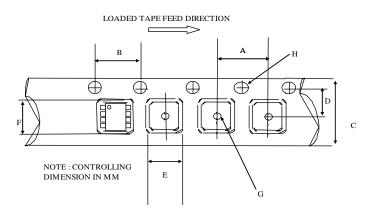

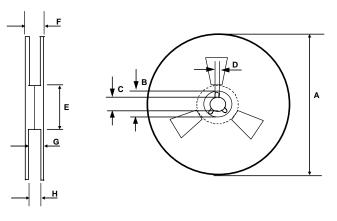

CARRIER TAPE DIMENSION FOR 8SOICN

|      | Metric |       | Imp   | erial |

|------|--------|-------|-------|-------|

| Code | Min    | Max   | Min   | Max   |

| A    | 7.90   | 8.10  | 0.311 | 0.318 |

| В    | 3.90   | 4.10  | 0.153 | 0.161 |

| С    | 11.70  | 12.30 | 0.46  | 0.484 |

| D    | 5.45   | 5.55  | 0.214 | 0.218 |

| E    | 6.30   | 6.50  | 0.248 | 0.255 |

| F    | 5.10   | 5.30  | 0.200 | 0.208 |

| G    | 1.50   | n/a   | 0.059 | n/a   |

| Н    | 1.50   | 1.60  | 0.059 | 0.062 |

REEL DIMENSIONS FOR 8SOICN

|      | Me     | etric  | Imperial |        |  |

|------|--------|--------|----------|--------|--|

| Code | Min    | Max    | Min      | Max    |  |

| А    | 329.60 | 330.25 | 12.976   | 13.001 |  |

| В    | 20.95  | 21.45  | 0.824    | 0.844  |  |

| С    | 12.80  | 13.20  | 0.503    | 0.519  |  |

| D    | 1.95   | 2.45   | 0.767    | 0.096  |  |

| E    | 98.00  | 102.00 | 3.858    | 4.015  |  |

| F    | n/a    | 18.40  | n/a      | 0.724  |  |

| G    | 14.50  | 17.10  | 0.570    | 0.673  |  |

| Н    | 12.40  | 14.40  | 0.488    | 0.566  |  |

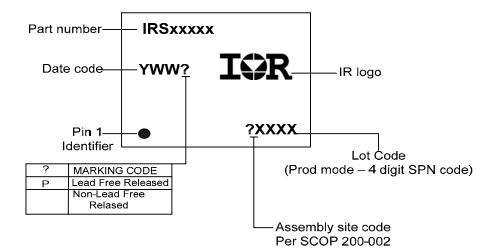

#### PART MARKING INFORMATION

#### **ORDER INFORMATION**

8-Lead PDIP IRS2153DPbF 8-Lead PDIP IRS21531DPbF 8-Lead SOIC IRS2153DSPbF 8-Lead SOIC IRS21531DSPbF 8-Lead SOIC Tape & Reel IRS2153DSTRPbF 8-Lead SOIC Tape & Reel IRS21531DSTRPbF

International

The SOIC-8 is MSL2 qualified. This product has been designed and qualified for the industrial level. Qualification standards can be found at <u>www.irf.com</u> <a href="http://www.irf.com">www.irf.com</a> IR WORLD HEADQUARTERS: 233 Kansas St., El Segundo, California 90245, Tel: (310) 252-7105 Data and specifications subject to change without notice. 6/27/2006