PD-96992 Rev.A

Half-Bridge FredFET and Integrated Driver

# IR3103 \*\*MOTION Series 0.75A, 500V

## **Description**

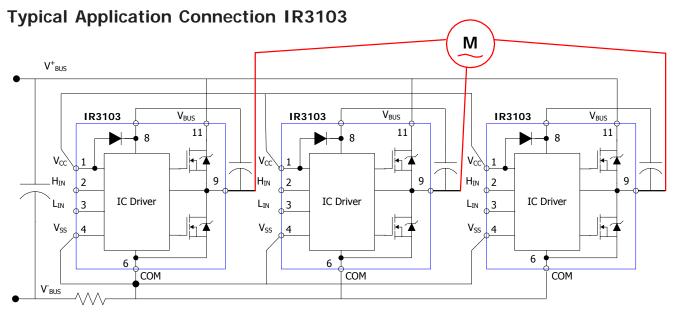

The IR3103 is a gate driver IC integrated with a half bridge FredFET designed for motor drive applications up to 180W (heatsink-less). The sleek and compact single-in-line package is optimized for electronic motor control in appliance applications such as fans and compressors for refrigerators. The IR3103 offers an extremely compact, high performance half-bridge inverter in a single isolated package for two-phase and three-phase motor drivers.

Proprietary HVIC and latch immune CMOS technologies, along with the HEXFET® power FredFET technology (HEXFET® MOSFET with ultra-fast recovery body diode characteristics), enable efficient and rugged single package construction. Propagation delays for the high and low side power FredFETs are matched thanks to advanced IC technology.

#### **Features**

- Output Power FredFET in Half-Bridge Configuration

- High Side Gate Drive Designed for Bootstrap Operation

- Bootstrap Diode Integrated into Package

- Lower Power Level-Shifting Circuit

- Lower di/dt Gate Drive for Better Noise Immunity

- Excellent Latch Immunity on All Inputs and Outputs

- ESD Protection on All Leads

- Isolation 1500 V<sub>RMS</sub> min.

## **Absolute Maximum Ratings**

Absolute maximum ratings indicate sustained limits beyond which damage to the device may occur. All voltage parameters are absolute voltages referenced to COM. Power dissipation is measured under board mounted and still air conditions.

| Parameter                             | Description                                          | Max. Value  | Units     |

|---------------------------------------|------------------------------------------------------|-------------|-----------|

| V <sub>DS</sub>                       | Drain to Source Blocking Voltage                     | 500         | V         |

| $V_{DD}$                              | DC Bus Supply Voltage (No Switching Operation)       | 500         | V         |

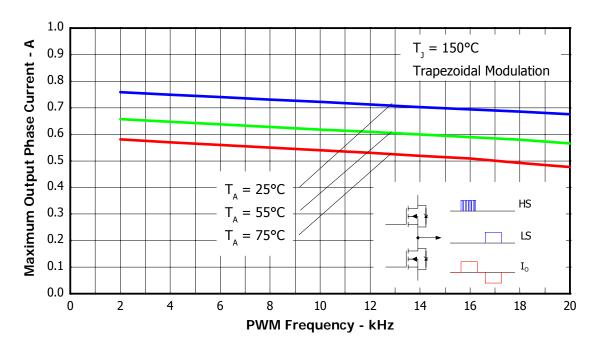

| I <sub>O</sub> (T <sub>A</sub> =25°C) | Continuous Output Current (1)                        | 0.7         | Α         |

| I <sub>O</sub> (T <sub>A</sub> =55°C) | Continuous Output Current (1)                        | 0.6         | Α         |

| I <sub>O</sub> (T <sub>A</sub> =25°C) | Pulsed Output Current (2)                            | 2.7         | А         |

| $P_d$                                 | Package Power Dissipation @T <sub>A</sub> ≤ 55°C (3) | 1.4         | W         |

| $V_{ISO}$                             | Isolation Voltage (1min)                             | 1500        | $V_{RMS}$ |

| T <sub>3</sub>                        | Junction Temperature (Power MOSFET)                  | -40 to +150 | °C        |

| T <sub>S</sub>                        | Storage Temperature                                  | -40 to +150 | °C        |

| TL                                    | Lead Temperature (soldering, 10 seconds)             | 300         | °C        |

| T <sub>S</sub>                        | Storage Temperature                                  | -40 to +150 | °C        |

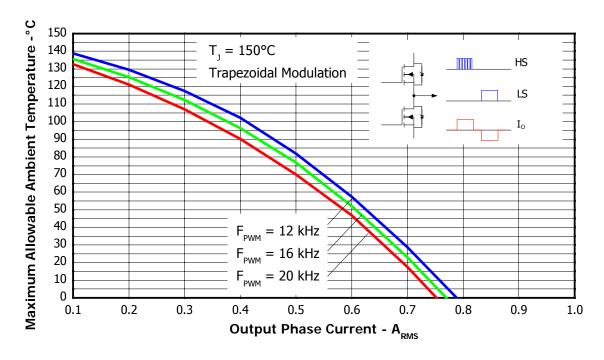

Note 1: See figure 3, fpwm=16kHz

Note 2: Te=100ms, other conditions as per Figure 3, fpwm=16kHz

Note 3: Single Device Operating

## **Absolute Maximum Ratings (Continued)**

Absolute maximum ratings indicate sustained limits beyond which damage to the device may occur. All voltage parameters are absolute voltages referenced to COM.

| Symbol             | Parameter                                       | Min                  | Max                   | Units | Conditions                                   |

|--------------------|-------------------------------------------------|----------------------|-----------------------|-------|----------------------------------------------|

| $\mathbf{I}_{BDF}$ | Bootstrap Continuous Diode<br>Forward Current   |                      | 0.3                   | А     | T <sub>J</sub> = 150°C, T <sub>A</sub> =55°C |

| V <sub>B</sub>     | High Side Floating Supply<br>Absolute Voltage   | -0.3                 | 525                   | V     |                                              |

| Vo                 | High Side Floating Supply Offset<br>Voltage     | V <sub>B</sub> - 25  | V <sub>B</sub> +0.3   | V     |                                              |

| V <sub>CC</sub>    | Low Side and Logic Fixed Supply<br>Voltage      | -0.3                 | 25                    | V     |                                              |

| V <sub>IN</sub>    | Input Voltage L <sub>IN</sub> , H <sub>IN</sub> | V <sub>SS</sub> -0.3 | V <sub>CC</sub> +0.3V | V     |                                              |

| V <sub>SS</sub>    | Logic Ground                                    | V <sub>cc</sub> -25  | V <sub>CC</sub> +0.3V | V     |                                              |

## **Recommended Operating Conditions Driver Function**

For proper operation the device should be used within the recommended conditions. All voltages are absolute referenced to COM. The  $V_S$  and  $V_O$  offset are tested with all supplies biased at 15V differential.

| Symbol          | Definition                                 | Min                | Max                | Units    |

|-----------------|--------------------------------------------|--------------------|--------------------|----------|

| $V_B$           | High Side Floating Supply Absolute Voltage | V <sub>O</sub> +10 | V <sub>0</sub> +20 | <b>V</b> |

| $V_{DD}$        | High Voltage Supply                        | Note 4             | 400                | V        |

| V <sub>CC</sub> | Low Side and Logic Fixed Supply Voltage    | 10                 | 20                 | V        |

| V <sub>IN</sub> | Logic Input Voltage                        | V <sub>SS</sub>    | V <sub>CC</sub>    | V        |

| V <sub>SS</sub> | Logic Ground                               | -5                 | 5                  | V        |

Note 4: Logic operation for  $V_O$  of -5 to +500V. Logic state held for  $V_O$  of -5V to - $V_{BO}$ . (Please refer to the Design Tip DT97-3 for more details).

# Half Bridge Electrical Characteristics @ $T_J$ = 25°C

$V_{\text{CC}} = V_{\text{BO}} = 15 \text{V} \text{ and } T_{\text{J}} = 25 ^{\circ} \text{C unless otherwise specified. } V_{\text{DD}} \text{ and } V_{\text{IN}} \text{ parameters referenced to COM}$

| Symbol                | Parameter                             | Min | Тур  | Max  | Units | Conditions                                                                           |  |

|-----------------------|---------------------------------------|-----|------|------|-------|--------------------------------------------------------------------------------------|--|

| $V_{(BR)DSS}$         | Drain-to-Source Breakdown<br>Voltage  | 500 |      |      | V     | $V_{IN} = 0V$ , $I_{DD}/I_{O} = 250 \mu A$                                           |  |

| т                     | Low Side Leakage Current              |     | 5    | 50   | μA    | V <sub>DS</sub> =500V, V <sub>IN</sub> =0V                                           |  |

| I <sub>HS-LK</sub>    | Low Side Leakage Current              |     | 80   |      | μΑ    | V <sub>DS</sub> =500V, V <sub>IN</sub> =0V, T <sub>J</sub> =150°C                    |  |

| I <sub>LS-LK</sub>    | Low Side Leakage Current              |     | 5    | 105  | μA    | V <sub>DS</sub> =500V, V <sub>IN</sub> =0V                                           |  |

| LS-LK                 | Low Side Leakage Current              |     | 100  |      | μΑ    | $V_{DS}$ =500V, $V_{IN}$ =0V, $T_{J}$ =150°C                                         |  |

| R <sub>DS(ON)</sub>   | Drain-to-Source ON Resistance         |     | 1.9  | 2.5  | Ω     | $I_{O} = 0.75A, V_{IN} = 5V$                                                         |  |

| $V_{SD}$              | Diode Forward Voltage                 |     | 0.8  | 0.9  | V     | $I_{O} = 0.75A, V_{IN} = 0V$                                                         |  |

| R <sub>DS(ON)</sub>   | Drain-to-Source ON Resistance         |     | 4.3  | 6.5  | Ω     | $I_{O} = 0.75A$ , $V_{IN}=5V$ , $T_{J}=150$ °C                                       |  |

| $V_{SD}$              | Diode Forward Voltage                 |     | 0.6  | 0.75 | V     | $I_{O} = 0.75A$ , $V_{IN}=0V$ , $T_{J}=150$ °C                                       |  |

| V                     | Bootstrap Diode Forward               |     |      | 1.25 | V     | I <sub>F</sub> =1A                                                                   |  |

| $V_{BDFM}$            | Voltage Drop                          |     |      | 1.10 | V     | I <sub>F</sub> =1A, T <sub>J</sub> =125°C                                            |  |

| E <sub>ON</sub>       | Turn-On Energy Losses                 |     | 55   | 75   | μJ    | I /I 0.754 \/ 200\/                                                                  |  |

| E <sub>OFF</sub>      | Turn-Off Energy Losses                |     | 4    | 10   | μJ    | $I_{DD}/I_{O} = 0.75A$ , $V_{DD}=300V$ , $V_{BO}/V_{CC}=15V$ , L= 6.3mH              |  |

| E <sub>TOT</sub>      | Total Energy Losses                   |     | 59   | 85   | μJ    | - 100/ 1CC = 21/ = 0.0                                                               |  |

| E <sub>REC</sub>      | Body-Diode Reverse Recovery<br>Losses |     | 2    | 5    | μJ    | Energy Losses include Body-Diode<br>Reverse Recovery                                 |  |

| t <sub>RR</sub>       | Reverse Recovery Time                 |     | 70   |      | ns    | The verse recovery                                                                   |  |

| E <sub>ON</sub>       | Turn-On Energy Losses                 |     | 85   | 115  | μJ    | I /I - 0.754 \/ -200\/                                                               |  |

| E <sub>OFF</sub>      | Turn-Off Energy Losses                |     | 5    | 11   | μJ    | $I_{DD}/I_{O} = 0.75A$ , $V_{DD}=300V$ , $V_{BO}/V_{CC}=15V$ , L=6.3mH               |  |

| E <sub>TOT</sub>      | Total Energy Losses                   |     | 90   | 126  | μJ    | T <sub>J</sub> =150°C                                                                |  |

| E <sub>REC</sub>      | Body-Diode Reverse Recovery<br>Losses |     | 6    | 11   | μЈ    | Energy Losses include Body-Diode<br>Reverse Recovery                                 |  |

| t <sub>RR</sub>       | Reverse Recovery Time                 |     | 90   |      | ns    | Reverse Recovery                                                                     |  |

| $Q_{G}$               | Turn-ON MOSFET Gate Charge            |     | 15   | 21   | nC    | V <sub>DD</sub> =250V, I <sub>O</sub> =3.2A. Note 5                                  |  |

| C <sub>OSS</sub>      | Output Capacitance                    |     | 12   |      | pF    | V <sub>DD</sub> =400V, f=1MHz. Note 5                                                |  |

| C <sub>OSS</sub> eff. | Effective Output Capacitance          |     | 30   |      | pF    | V <sub>DD</sub> =0V to 400V. Note 5,6                                                |  |

| SCSOA                 | Short Circuit Safe Operating<br>Area  | 10  |      |      | μs    | $T_J=150$ °C, $V_P=450$ V, $V^+=320$ V, $V_{CC}=+15$ V                               |  |

| $I_{SC}$              | Short Circuit Drain Current           |     | 18.5 |      | А     | $T_J=150$ °C, $V_P=450$ V, $t_{SC}<10$ µs $V^+=320$ V, $V_{GE}=15$ V, $V_{CC}=+15$ V |  |

Note 5: Characterized on FREDFET die level, not measured at EOL

Note 6:  $C_{OSS}$  eff. is a fixed capacitance that gives same charging time as  $C_{OSS}$  while  $V_{DS}$  is rising from 0 to 80%  $V_{DSS}$ .

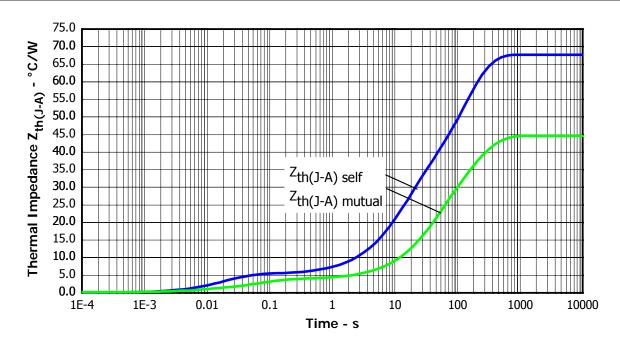

#### **Thermal Resistance**

Thermal Resistance is measured under board mounted and still air conditions.

| Symbol                   | Parameter                                                 | Min | Тур | Max | Units | Conditions |

|--------------------------|-----------------------------------------------------------|-----|-----|-----|-------|------------|

| Rth <sub>JA self</sub>   | Self Thermal resistance, junction to ambient (note 7,8)   |     |     | 70  | °C/W  | No airflow |

| Rth <sub>JA mutual</sub> | Mutual Thermal resistance, junction to ambient (note 7,8) |     |     | 45  | °C/W  | NO all now |

Note 7: under normal operational conditions: both power devices working, no heatsink

Note 8: TJ=RthJA\_self\*PA+RthJA\_mutual\*PB

### **Static Electrical Characteristics Driver Function**

$V_{BIAS}$  ( $V_{CC}$ ,  $V_{O}$ )=15V,  $V_{SS}$ =COM and  $T_{A}$ =25°C, unless otherwise specified.  $V_{DD \ and} \ V_{IN}$  parameters are referenced to COM.

| Symbol                                | Definition                                                         | Min | Тур | Max | Units | Conditions                           |  |

|---------------------------------------|--------------------------------------------------------------------|-----|-----|-----|-------|--------------------------------------|--|

| V <sub>IN,th</sub>                    | Logic "1" Input Voltage                                            | 2.9 |     |     | V     |                                      |  |

| V <sub>IN,th</sub>                    | Logic "0" Input Voltage                                            |     |     | 0.8 | V     |                                      |  |

| V <sub>CCUV+</sub><br>V <sub>BO</sub> | $V_{CC}$ and $V_{BO}$ Supply Undervoltage Positive Going Threshold | 8.0 | 8.9 | 9.8 | V     |                                      |  |

| V <sub>CCUV</sub> -                   | $V_{CC}$ and $V_{BO}$ Supply Undervoltage Negative Going Threshold | 7.4 | 8.2 | 9.0 | V     |                                      |  |

| V <sub>CCUVH</sub><br>V <sub>BO</sub> | $V_{CC}$ and $V_{BO}$ Supply Undervoltage Lock-Out Hysteresis      | 0.3 | 0.7 |     | V     |                                      |  |

| I <sub>LK</sub>                       | Offset Supply Leakage Current                                      |     |     | 50  | μA    | V <sub>B</sub> =V <sub>O</sub> =600V |  |

| $I_{QBS}$                             | Quiescent V <sub>BO</sub> Supply Current                           |     | 75  | 130 | μΑ    | V <sub>IN</sub> =0V to 5V            |  |

| $I_{QCC}$                             | Quiescent V <sub>CC</sub> Supply current 120                       |     | 120 | 180 | mA    | V <sub>IN</sub> =0V to 5V            |  |

| I <sub>IN+</sub>                      | Input Bias Current                                                 |     | 5   | 20  | μΑ    | V <sub>IN</sub> =0V to 5V            |  |

| $I_{IN	ext{-}}$                       | Input Bias Current                                                 |     |     | 2   | μΑ    | V <sub>IN</sub> =0V                  |  |

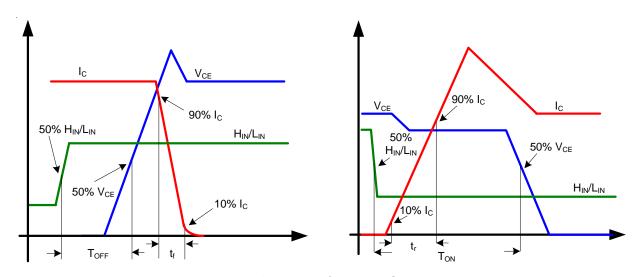

# **Dynamic Electrical Characteristics Driver Function**

Driver only timing unless otherwise specified.

| Symbol           | Definition                                                      | Min | Тур | Max | Units | Conditions                                                     |

|------------------|-----------------------------------------------------------------|-----|-----|-----|-------|----------------------------------------------------------------|

| T <sub>ON</sub>  | Input to Output Propagation Turn-<br>on Delay Time (see fig. 2) |     | 300 |     | ns    | V <sub>CC</sub> =V <sub>BO</sub> = 15V, I <sub>O</sub> =0.75A, |

| T <sub>OFF</sub> | Input to Output Propagation Turnoff Delay Time (see fig. 2)     |     | 400 |     | ns    | V <sub>DD</sub> =300V                                          |

| M <sub>T</sub>   | Matching Propagation Delay Time (On & Off)                      |     | 0   | 30  | ns    | $V_{CC} = V_{BO} = 15V$                                        |

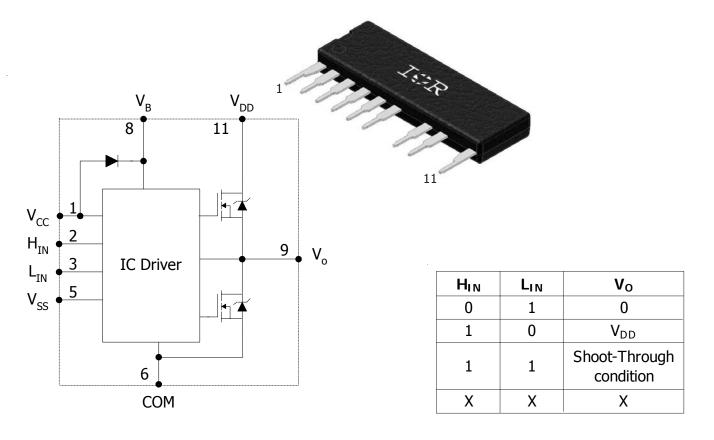

**Pin-Out Description**

| Pin | Name            | Description                           |  |

|-----|-----------------|---------------------------------------|--|

| 1   | V <sub>CC</sub> | Logic and Internal Gate Drive Supply  |  |

| 2   | H <sub>IN</sub> | Logic Input for High Side Gate Output |  |

| 3   | L <sub>IN</sub> | Logic Input For Low Side Gate Output  |  |

| 4   | NC              | Not Connected                         |  |

| 5   | V <sub>SS</sub> | Logic Ground                          |  |

| 6   | СОМ             | Low Side MOSFET Gate Return           |  |

| 7   | NC              | Not Connected                         |  |

| 8   | V <sub>B</sub>  | High Side Gate Drive Floating Supply  |  |

| 9   | Vo              | Half Bridge Output                    |  |

| 10  | NC              | Not Connected                         |  |

| 11  | V <sub>DD</sub> | High Voltage Supply                   |  |

Figure 1: Driver Input/Output relation

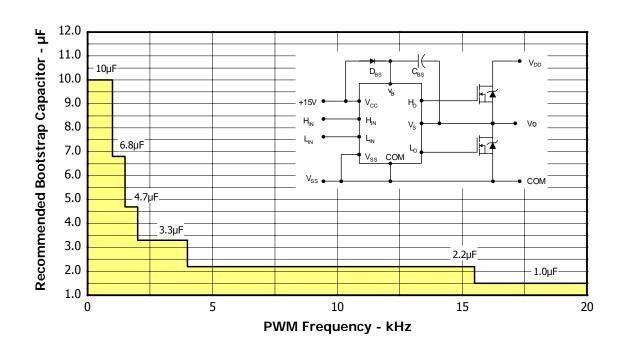

- 1. Electrolytic bus capacitors should be mounted as close as possible to the module bus terminals to reduce ringing and EMI problems. High frequency ceramic capacitors mounted close to the module pins will further improve performance.

- 2. In order to provide good decoupling between  $V_{cc}$ - $V_{SS}$  and  $V_B$ - $V_O$  terminals, a capacitor connected between these terminals is recommended and should be located very close to the module pins. Additional high frequency capacitors, typically 0.1mF, are strongly recommended.

- 3. Low inductance shunt resistor should be used for phase leg current sensing. Similarly, the length of the traces from the pin to the corresponding shunt resistor should be kept as small as possible.

- 4. Value of the bootstrap capacitors depends upon the switching frequency. Their selection should be made based on IR design tip DN 98-2a or Figure 8.

- 5. Application conditions should guarantee minimum dead-time of 400ns

Figure 2.  $T_{ON}$  and  $T_{OFF}$  Definitions.

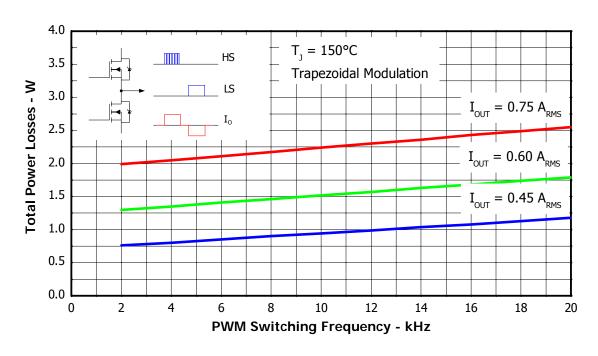

Figure 3. Maximum RMS Phase Current vs. PWM Switching Frequency  $V_{DD}\!=\!300V$  ,  $T_{J}\!=\!150^{\circ}\text{C}$ , Modulation Depth=0.5, PF=0.99

Figure 4. Total Power Losses as Function of Switching Frequency  $V_{DD}$ =300V,  $T_1$ =150°C, Modulation Depth=0.5, PF=0.99

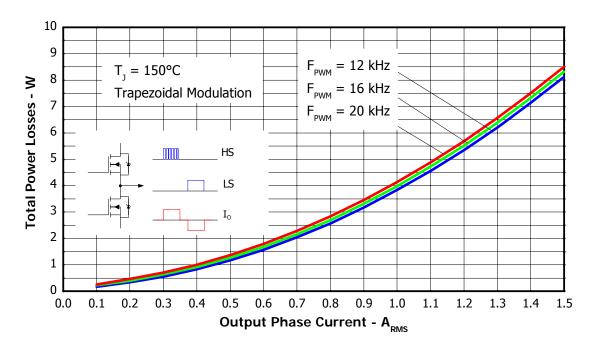

Figure 5. Total Power Losses as Function of Output Phase Current  $V_{DD}$ =300V,  $T_{J}$ =150°C, Modulation Depth=0.5, PF=0.99

Figure 6. Maximum Allowable Ambient Temperature vs. Output Phase Current  $V_{DD}$ =300V,  $T_J$ =150°C, Modulation Depth=0.5, PF=0.99

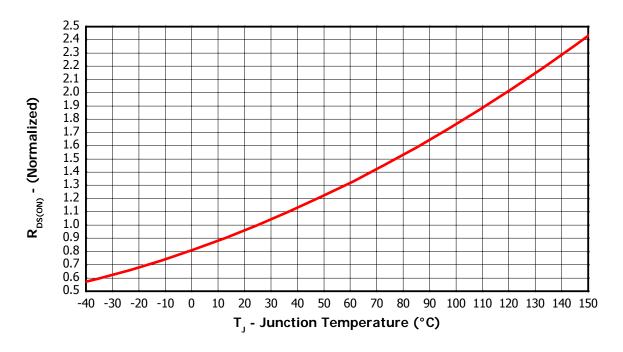

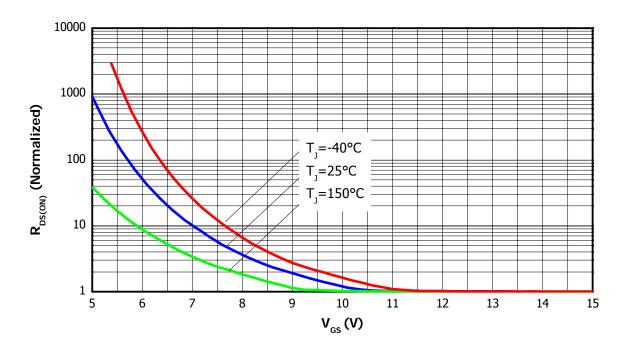

Figure 7. Normalized Drain to Source Resistance vs Junction Temperature

Figure 8. Normalized Drain to Source Resistance vs Gate Source Voltage

Figure 9. Thermal Impedance vs. Time

Figure 10. Recommended Bootstrap Capacitor Value vs. Switching Frequency

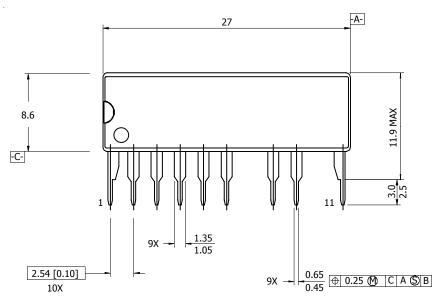

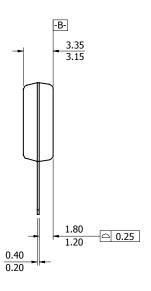

## Package Outline

Note 1: Marking for pin 1 identification

Note 2: Product Part Number

Note 3: Lot and Date code marking

Dimensioning and Tolerancing per ANSY Y14.5M-1992

Controlling Dimensions: INCH

Dimensions are shown in millimeters [inches]

Data and Specifications are subject to change without notice

IR WORLD HEADQUARTERS: 233 Kansas St., El Segundo, California 90245, USA Tel: (310) 252-7105

TAC Fax: (310) 252-7903

Visit us at www.irf.com for sales contact information

04/05