Data Sheet No.PD94722 revA

### IR3622MPbF

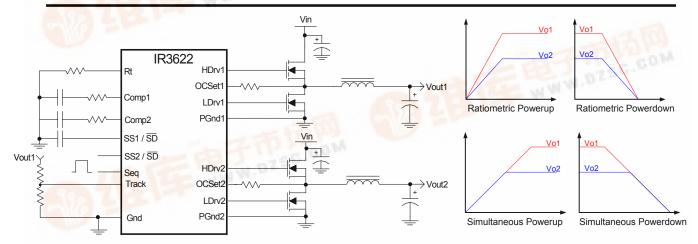

# HIGH FREQUENCY 2-PHASE, SINGLE OR DUAL OUTPUT SYNCHRONOUS STEP DOWN CONTROLLER WITH OUTPUT TRACKING AND SEQUENCING

#### **Features**

- Dual Synchronous Controller with 180°

Out of Phase Operation

- Configurable to 2-Independent Outputs or Current Shared Single Output

- Output Voltage Tracking

- Power up / down Sequencing

- Current Sharing Using Inductor's DCR

- +/-1% Accurate Reference Voltage

- Programmable Switching Frequency up 600kHz

- Programmable Over Current Protection

- Hiccup Current Limit Using MOSFET R<sub>ds(on)</sub> sensing

- · Latched Overvoltage Protection

- Dual Programmable Soft-Starts

- Programmable Enable Input

- Pre-Bias Start-up

- Dual Power Good Outputs

- On Board Regulator

- External Frequency Synchronization

- Thermal Protection

- 32-Lead MLPQ Package

#### **Applications**

- · Embedded Telecom Systems

- Distributed Point of Load Power Architectures

- Computing Peripheral Voltage Regulators

- Graphics Cards

- General DC/DC Converters

#### **Description**

The IR3622 IC integrates a dual synchronous Buck controller, providing a high performance and flexible solution. The IR3622 can be configured as 2-independent outputs or as current shared single output. The current share configuration is ideal for high current applications.

The IR3622 enables output tracking and sequencing of multiple rails in either ratiometric or simultaneous fashion. The IR3622 features 180° out of phase operation which reduces the required input/output capacitance and results in lower number of capacitors. The switching frequency is programmable from 200kHz to 600kHz per phase using one external resistor. In addition, IR3622 also allows the switching frequency to be synchronized to an external clock signal.

Other key features offered by this device include two independent programmable soft starts, two independent power good outputs, precision enable input, and under voltage lockout function. The current limit is provided by sensing the lower MOSFET's on-resistance for optimum cost and performance. The output voltages are monitored through dedicated pins to protect against open circuit, and enhance faster response to an overvoltage event.

|       | URDERING INFORMATION |       |          |          |            |  |  |  |

|-------|----------------------|-------|----------|----------|------------|--|--|--|

| PKG   | PACKAGE              | PIN   | PARTS    | PARTS    | T&R        |  |  |  |

| DESIG | DESCRIPTION          | COUNT | PER TUBE | PER REEL | ORIANTAION |  |  |  |

| M     | IR3622MPbF           | 32    | 73       |          | F: A       |  |  |  |

| M     | IR3622MTRPbF         | 32    |          | 3000     | Fig A      |  |  |  |

w.irf.com 03/15/07

#### **ABSOLUTE MAXIMUM RATINGS**

(Voltages referenced to GND)

| ,                                    |                              |

|--------------------------------------|------------------------------|

| Vcc, VcL Supply Voltage              | -0.5V to 16V                 |

| VcH1,VcH2                            | -0.5V to 30V                 |

| PGood1, PGood2                       | -0.5V to 16V                 |

| HDrv1, HDrv2                         | 0.5V to 30V (-2V for 100ns)  |

| LDrv1, LDrv2                         | -0.5V to 16V (-2V for 100ns) |

| Gnd to PGnd                          | +/- 0.3V                     |

| Storage Temperature Range            | -65°C To 150°C               |

| Operating Junction Temperature Range | -40°C To 125°C               |

| ESD Classification                   | JEDEC, JESD22-A114 (1KV)     |

| Moisture Sensitivity Level           | JEDEC, Level 3 @ 260°C       |

**Caution:** Stresses above those listed in "Absolute Maximum Rating" may cause permanent damage to the device. These are stress ratings only and function of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to "Absolute Maximum Rating" conditions for extended periods may affect device reliability.

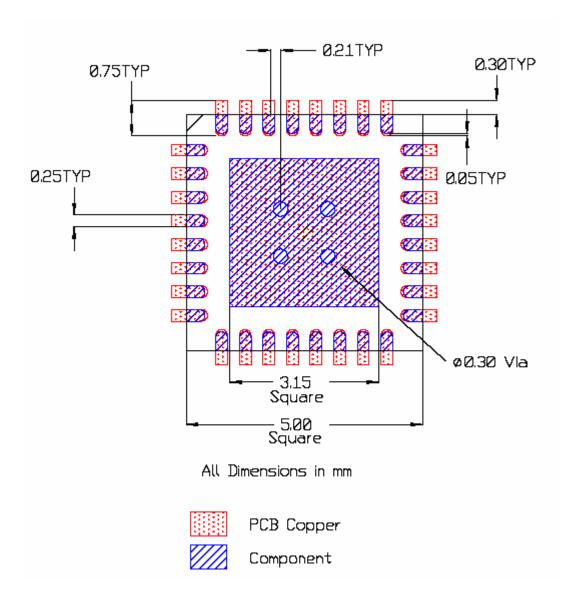

### **Package Information**

$$\Theta_{JA} = 36^{\circ} C/W^*$$

$\Theta_{JC} = 1^{\circ} C/W$

<sup>\*</sup>Exposed pad on underside is connected to a copper pad through vias for 4-layer PCB board design

### Recommended Operating Conditions

| Symbol     | Definition           | Min                    | Max  | Units |

|------------|----------------------|------------------------|------|-------|

| Vcc, VcL   | Supply Voltage       | 7.5                    | 14.5 | V     |

| VcH1, VcH2 | Supply Voltage       | Converter Voltage + 5V | 28   | V     |

| Fs         | Operating frequency  | 200                    | 600  | kHz   |

| Tj         | Junction temperature | -40                    | 125  | °C    |

**Electrical Specifications**Unless otherwise specified, these specification apply over Vcc=VcL=VcH1=VcH2=12V, 0°C<Tj<105°C

| Parameter                                   | SYM                                              | Test Condition                                                           | Min  | TYP  | MAX  | Units |

|---------------------------------------------|--------------------------------------------------|--------------------------------------------------------------------------|------|------|------|-------|

| Output Voltage Accurac                      | у                                                |                                                                          |      |      |      |       |

| FB1,2 Voltage                               | V <sub>FB</sub>                                  | Vp1=Vp2=Vref=0.8V                                                        |      | 0.8  |      | V     |

| Accuracy                                    |                                                  | 0°C <tj< 125°c<="" td=""><td>-1</td><td></td><td>+1</td><td>%</td></tj<> | -1   |      | +1   | %     |

|                                             |                                                  | -40°C <tj< 125°c;="" <i="">Note2</tj<>                                   | -1.5 |      | +1.5 | %     |

| Supply Current                              |                                                  |                                                                          |      |      |      |       |

| V <sub>CC</sub> Supply Current (Static)     | I <sub>CC</sub> (Static)                         | SS=0V, No Switching                                                      |      | 13   | 18   | mA    |

| V <sub>CC</sub> Supply Current<br>(Dynamic) | I <sub>CC</sub> (Dynamic)                        | Fs=300kHz, C <sub>LOAD</sub> = 3.3nF                                     |      | 20   | 30   | mA    |

| V <sub>CL</sub> Supply Current (Static)     | I <sub>CL</sub> (Static)                         | SS=0V, No Switching                                                      |      | 8    | 10   | mA    |

| V <sub>CL</sub> Supply Current (Dynamic)    | I <sub>CL</sub> (Dynamic)                        | Fs=300kHz, C <sub>LOAD</sub> = 3.3nF                                     |      | 30   | 42   | mA    |

| V <sub>CH1,2</sub> Supply Current (Static)  | I <sub>CH</sub> (Static)                         | SS=0V, No Switching                                                      |      | 9    | 11   | mA    |

| V <sub>CH1,2</sub> Supply Current (Dynamic) | I <sub>CH</sub> (Dynamic                         | Fs=300kHz, C <sub>LOAD</sub> = 3.3nF                                     |      | 30   | 42   | mA    |

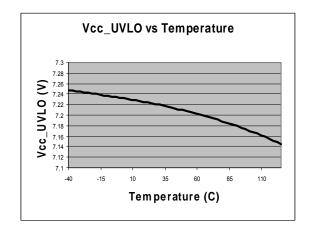

| Under Voltage Lockou                        | t, Enable                                        |                                                                          |      |      |      |       |

| V <sub>CC</sub> -Start Threshold            | V <sub>CC</sub> _UVLO(R)                         | Supply ramping up                                                        | 6.85 | 7.1  | 7.5  | V     |

| V <sub>CC</sub> -Stop Threshold             | V <sub>CC</sub> _UVLO(F)                         | Supply ramping down                                                      | 6.1  | 6.4  | 6.7  | V     |

| V <sub>CC</sub> -Hysteresis                 |                                                  | Supply ramping up and down                                               | 0.5  | 0.8  | 1.0  | V     |

| V <sub>CH1,2</sub> -Start Threshold         | V <sub>CH</sub> _UVLO(R)                         | Supply ramping up                                                        | 4.6  | 4.95 | 5.3  | V     |

| V <sub>CH1,2</sub> -Stop Threshold          | V <sub>CH</sub> _UVLO(F)                         | Supply ramping down                                                      | 4.1  | 4.4  | 4.7  | V     |

| V <sub>CH1,2</sub> -Hysteresis              |                                                  | Supply ramping up and down                                               | 0.32 | 0.6  | 0.8  | V     |

| Enable-Threshold                            | En_UVLO                                          | Supply ramping up                                                        | 1.14 | 1.24 | 1.34 | V     |

| Enable-Hysteresis                           | <del>                                     </del> | Supply ramping up and down                                               | 0.15 | 0.2  | 0.33 | V     |

| Oscillator                                  |                                                  |                                                                          |      |      |      |       |

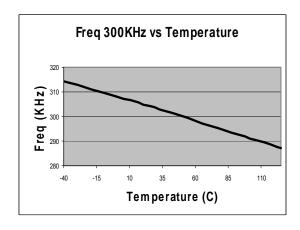

| Frequency Range                             | Fs                                               |                                                                          | 200  |      | 600  | kHz   |

| Accuracy                                    |                                                  | Fs=300kHz                                                                | -12  |      | +12  | %     |

| Ramp Amplitude                              | Vramp                                            | Note1                                                                    |      | 1.25 |      | V     |

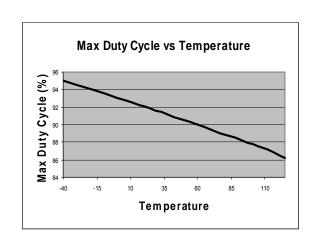

| Min Duty Cycle                              | Dmin                                             | Fb=1V                                                                    |      |      | 0    | %     |

| Min Pulse Width                             | Ton(min)                                         | F <sub>s</sub> =300kHz, <i>Note1</i>                                     |      |      | 150  | ns    |

| Max duty Cycle                              | Dmax                                             | F <sub>S</sub> =300kHz, Fb=0.6V                                          | 84   |      |      | %     |

| Sync Frequency Range                        | Sync(F)                                          | 20% above free running Freq                                              |      |      | 1200 | kHz   |

| Sync Pulse Duration                         | Sync(Pulse)                                      |                                                                          | 200  | 300  |      | ns    |

| Sync High Level Threshold                   | Sync(H)                                          |                                                                          | 2    |      |      | V     |

| Sync Low Level Threshold                    | Sync(L)                                          |                                                                          |      |      | 0.6  | V     |

## **Electrical Specifications**

| Parameter                            | SYM                                | Test Condition                                       | Min      | TYP       | MAX      | Units   |

|--------------------------------------|------------------------------------|------------------------------------------------------|----------|-----------|----------|---------|

| Error Amplifier 1                    | , 2                                |                                                      | •        | •         | <u>'</u> |         |

| Fb Voltage Input                     | IFB                                | SS=3V                                                |          | -0.1      | -0.5     | μА      |

| Bias Current E/A Source/Sink Current | I(source/Sink)                     |                                                      | 120      | 200       | 280      | μΑ      |

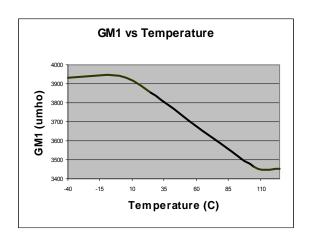

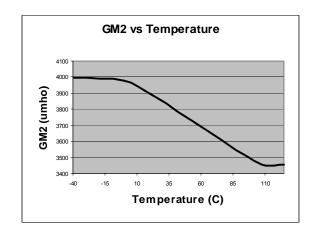

| Transconductance                     | gm1,2                              |                                                      | 3000     |           | 4500     | μmho    |

| Input offset                         | Voffset                            | Fb to Vref                                           | -4       | 0         | +4       | mV      |

| Voltage<br>VP Voltage Range          | VP                                 | Note1                                                | 0.4      |           | Vcc-2    | V       |

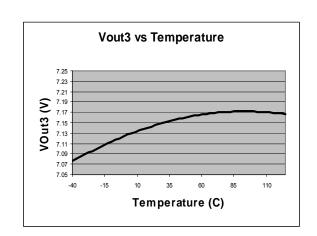

| Internal Regulato                    | Ar.                                |                                                      |          |           |          |         |

| Output Accuracy                      | Vout3                              |                                                      | 6.7      | 7.2       | 7.7      | V       |

| Dropout                              | Vdrop                              | Vcc(min)=9V, Isource=100mA                           |          |           | 2        | V       |

| Current Limit                        | Ishort                             |                                                      | 110      |           | _        | mA      |

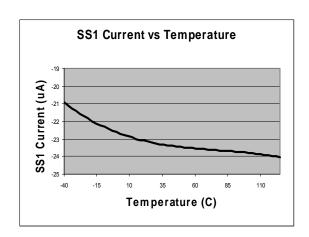

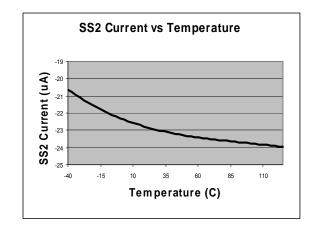

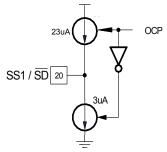

| Soft Start/SD                        |                                    | <u>I</u>                                             |          |           |          |         |

| Soft Start Current                   | ISS                                | Source/Sink                                          | 18       | 23        | 28       | μА      |

| Shutdown                             | SD                                 |                                                      |          |           | 0.25     | V       |

| Threshold                            |                                    |                                                      |          |           |          | -       |

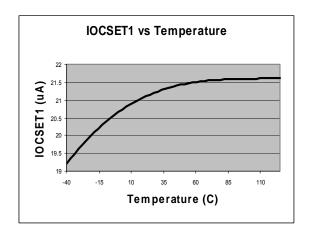

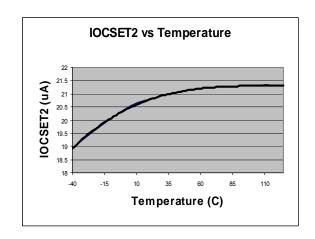

| Over Current Pro                     | tection                            |                                                      |          |           |          |         |

| OCSET Current                        | I <sub>OCSET</sub><br>Hiccup(duty) | Ihiccup / locset, Note1                              | 16       | 20<br>5   | 24       | μA<br>% |

| Hiccup Duty Cycle                    |                                    | Iniccup / locset, Note I                             |          | 3         |          | 70      |

| Over Voltage Pro                     |                                    |                                                      | 1 1\/rof | 1 15\/rof | 1.2Vref  | V       |

| ·                                    | OVP(trip)                          |                                                      | 1.1Vref  | 1.15Vref  |          |         |

| OVP Fault Prop<br>Delay              | OVP(delay)                         | Output Forced to 1.25Vref                            |          |           | 5        | μS      |

| Thermal Shutdov                      | vn                                 |                                                      |          |           |          |         |

| Thermal shutdown                     |                                    | Note1                                                |          | 140       |          | °C      |

| Thermal shutdown<br>Hysteresis       |                                    | Note1                                                |          | 20        |          | °C      |

| Power Good                           |                                    |                                                      |          |           |          |         |

| Vsen Lower Trip point                | Vsen(trip)                         | Vsen Ramping Down                                    | 0.8Vref  | 0.9Vref   | 0.95Vref | V       |

| PGood Output Low<br>Voltage          | PG(voltage)                        | I <sub>PGood</sub> =2mA                              |          | 0.1       | 0.5      | V       |

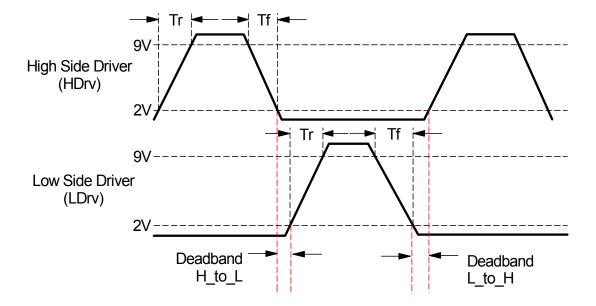

| Output Drivers                       |                                    |                                                      |          |           |          |         |

| LO, Drive Rise Time                  | Tr(Lo)                             | C <sub>LOAD</sub> =3.3nF, Fs=300KHz, <b>2V to 9V</b> |          | 25        | 50       | ns      |

| LO Drive Fall Time                   | Tf(Lo)                             | C <sub>LOAD</sub> =3.3nF, Fs=300KHz, <b>9V to 2V</b> |          | 25        | 50       | ns      |

| HI Drive Rise Time                   | Tr(Hi)                             | C <sub>LOAD</sub> =3.3nF, Fs=300KHz, <b>2V to 9V</b> |          | 25        | 50       | ns      |

| HI Drive Fall Time                   | Tf(Hi)                             | C <sub>LOAD</sub> =3.3nF, Fs=300KHz, <b>9V to 2V</b> |          | 25        | 50       | ns      |

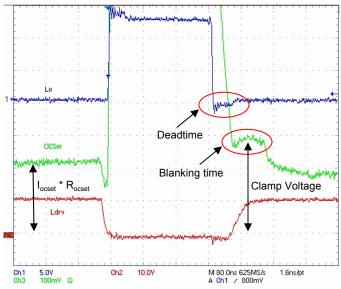

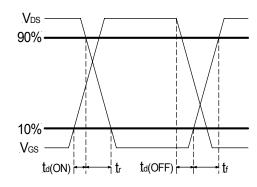

| Dead Band Time                       | Tdead                              | See Figure1                                          | 20       | 60        | 100      | ns      |

| Seq Input                            |                                    |                                                      | •        | •         | •        |         |

| Seq Threshold                        | Seq                                | On                                                   | 2.0      |           |          | V       |

|                                      |                                    | Off                                                  |          |           | 0.3      |         |

| Tracking                             | T                                  |                                                      | T        | 1         |          |         |

| Track voltage range                  | TK                                 | Note1                                                | 0        | 1         | Vcc      | V       |

Note1: Guaranteed by design but not tested in production.

Note2: Cold temperature performance is guaranteed via correlation using statistical quality control. Not tested in production.

Fig. 1: Rise / Fall and deadband time for driver section

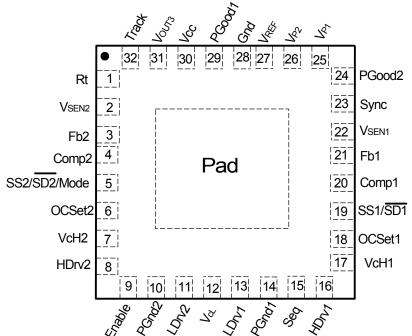

| Pin#   | Pin Name        | Description                                                                                                                                                                                                                                                   |  |

|--------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

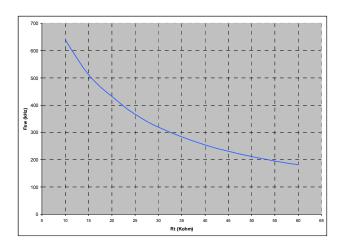

| 1      | Rt              | Connecting a resistor from this pin to ground sets the switching frequency                                                                                                                                                                                    |  |

| 2      | VSEN2           | (see figure 16 on page 17 for selecting resistor value) Sense pin for OVP2 and Power Good2, Channel 2                                                                                                                                                         |  |

| 3      | Fb2             | Inverting input to the error amplifier2                                                                                                                                                                                                                       |  |

| 4      | Comp2           | Compensation pin for the error amplifier2                                                                                                                                                                                                                     |  |

| 5      | SS2/SD2/Mode    | Soft start for channel 2, can be used as SD pin. Float this pin for current                                                                                                                                                                                   |  |

|        |                 | share single output application                                                                                                                                                                                                                               |  |

| 6      | OCSet2          | Current limit set point for channel2                                                                                                                                                                                                                          |  |

| 7, 17  | VcH2, VcH1      | Supply voltage for the high side output drivers. These are connected to voltage that must be typically 6V higher than their bus voltages. A 0.1uF high frequency capacitor must be connected from these pins to PGND to provide peak drive current capability |  |

| 8,16   | HDrv2, HDrv1    | Output drivers for the high side power MOSFETs                                                                                                                                                                                                                |  |

| 9      | Enable          | Enable pin, recycling this pin will reset OV, SS and Prebias latch                                                                                                                                                                                            |  |

| 10, 14 | PGnd2, PGnd1    | These pins serve as the separate grounds for MOSFET drivers and should be connected to the system's ground plane                                                                                                                                              |  |

| 11, 13 | LDrv2 , LDrv1   | Output drivers for the synchronous power MOSFETs                                                                                                                                                                                                              |  |

| 12     | VcL             | Supply voltage for the low side output drivers                                                                                                                                                                                                                |  |

| 15     | Seq             | Enable pin for tracking and sequencing. If this pin is not used connect it to V <sub>out3</sub>                                                                                                                                                               |  |

| 18     | OCSet1          | Current limit set point for Channel 1                                                                                                                                                                                                                         |  |

| 19     | SS1/SD1         | Soft start for Channel 1, can be used as SD pin                                                                                                                                                                                                               |  |

| 20     | Comp1           | Compensation pin for the error amplifier1                                                                                                                                                                                                                     |  |

| 21     | Fb1             | Inverting input to the error amplifier1                                                                                                                                                                                                                       |  |

| 22     | VSEN1           | Sense pin for OVP1 and Power Good1, Channel 1                                                                                                                                                                                                                 |  |

| 23     | Sync            | External synchronization pin                                                                                                                                                                                                                                  |  |

| 24     | PGood2          | Power Good pin output for channel 2, open collector. This pin needs to be externally pulled high                                                                                                                                                              |  |

| 25     | V <sub>P1</sub> | Non inverting input of error amplifier1                                                                                                                                                                                                                       |  |

| 26     | VP2             | Non inverting input of error amplifier2                                                                                                                                                                                                                       |  |

| 27     | VREF            | Reference Voltage                                                                                                                                                                                                                                             |  |

| 28     | Gnd             | IC's Ground                                                                                                                                                                                                                                                   |  |

| 29     | PGood1          | Power Good pin output for Channel 1, open collector. This pin needs to be externally pulled high                                                                                                                                                              |  |

| 30     | Vcc             | Supply voltage for the internal blocks of the IC. A 0.1uF high frequency capacitor must be connected from this pin to Gnd.                                                                                                                                    |  |

| 31     | Vout3           | Output of the internal regulator. A 0.1uF high frequency capacitor must be connected from this pin to PGnd.                                                                                                                                                   |  |

| 32     | Track           | Sets the type of power up / down sequencing (ratiometric or simultaneous). If this pin is not used connect it to V <sub>out3</sub>                                                                                                                            |  |

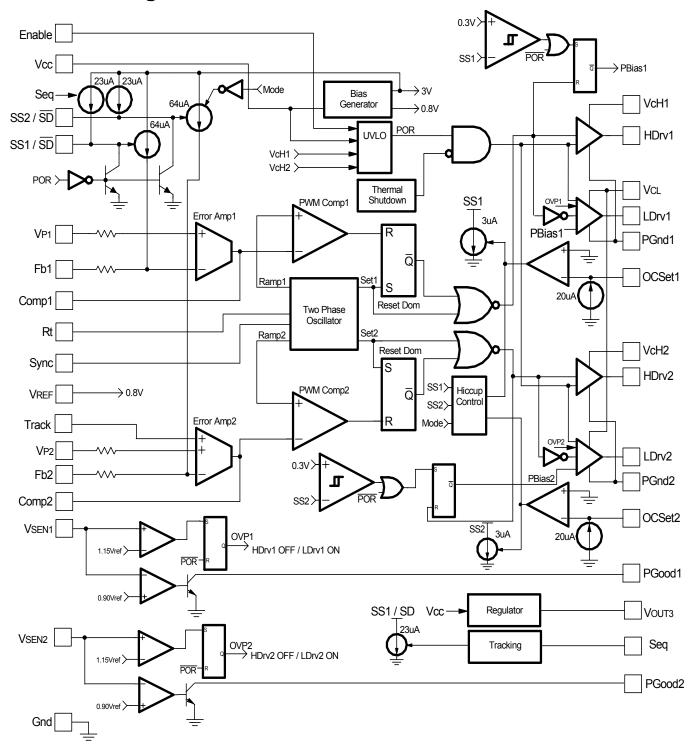

### **Block Diagram**

Fig. 2: Simplified block diagram of the IR3622

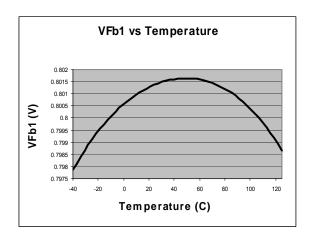

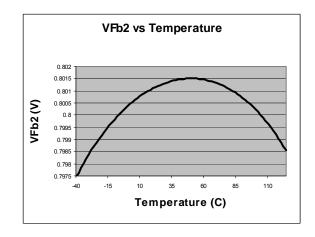

#### TYPICAL OPERATING CHARACTERISTICS (-40°C-125°C)

#### TYPICAL OPERATING CHARACTERISTICS (-40°C-125°C)

### Circuit Description

#### THEORY OF OPERATION

#### Introduction

The IR3622 is a versatile device for high performance buck converters. It consists of two synchronous buck controllers which can be operated either in two independent outputs mode or in current share single output mode for high current applications.

The timing of the IC is provided by an internal oscillator circuit which generates two 180°-out-of-phase clock signals that can be externally programmed up to 600kHz per phase.

#### **Under-Voltage Lockout**

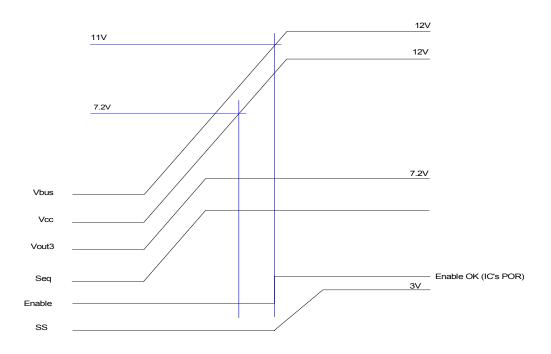

The under-voltage lockout circuit monitors four signals (Vcc, VcH1, VcH2 and Enable). This ensures the correct operation of the converter during power up and power down sequence. The driver outputs remain in the off state whenever one of these signals drop below set thresholds. Normal operation resumes once these signals rise above the set values. Figure 3 shows a typical start up sequence.

#### **Programmable Enable Input**

The enable features another level of flexibility for start up. The Enable has precise threshold which is internally monitored by under-voltage lockout circuit.

It's threshold can be externally programmed to desired level by using two external resistors, so the converter doesn't start up until the input voltage is sufficiently high (see figure 3).

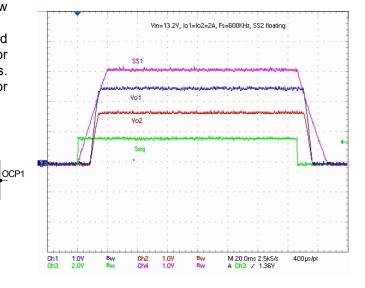

Fig. 3: Normal Start up, Enable threshold is externally set to 11V Seq pin is pulled to Vout3 prior to start up

#### **Internal Regulator**

The IR3622 features an on-board 7.2V regulator with short circuit protection. The regulator is capable of sourcing current up to 100mA. This integrated regulator can be used to generate the necessary bias voltage for drivers, an example of how this can be used is shown in figure 23, page26.

#### **Out-of-Phase Operation**

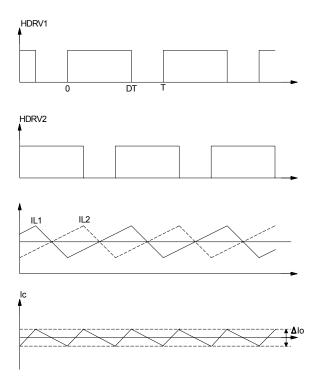

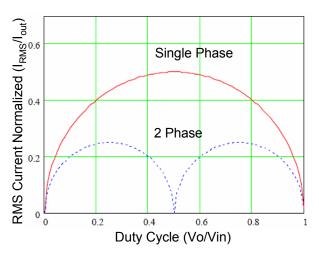

The IR3622 drives its two output stages 180° outof-phase. In current share mode single output, the two inductor ripple currents cancel each other and result in a reduction of the output current ripple and yield a smaller output capacitor for the same voltage ripple requirement. Figure 4 shows two channels inductor current and the resulting voltage ripple at the output.

Fig. 4: Current ripple cancellation for output

In addition, the 180° out of phase contributes to input current cancellation. This results in much smaller input capacitor's RMS current and reduces the number of required input capacitors. Figure 5 shows the equivalent RMS current.

Fig. 5: Input RMS value vs. Duty Cycle

#### **Mode Selection**

The IR3622 can operate as a dual output independently regulated buck converter, or as a 2 phase single output buck converter (current share mode). The SS2 pin is used for mode selection. In current share mode this pin should be floating. In the dual output mode, a soft start capacitor must be connected from this pin to the ground to program the start time for the second output.

#### **Independent Mode**

In this mode the IR3622 provides control to two independent output power supplies with either common or different input voltages. The output voltage of each individual channel is set and controlled by the output of the error amplifier, which is the amplified error signal from the sensed output voltage and the reference voltage. The error amplifier output voltage is compared to the ramp signal thus generating fixed frequency pulses of variable duty-cycle, (PWM) which are applied to the internal MOSEFT drivers. Figure 24 shows a typical schematic for such application.

#### **Current Share Mode**

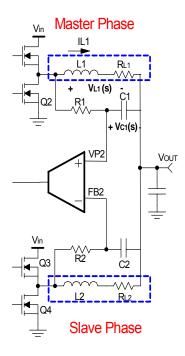

This feature allows to connect both outputs together to increase current handling capability of the converter to support a common load. In the current sharing mode, error amplifier 1 becomes the master which regulates the common output voltage and the error amplifier 2 performs the current sharing function, figure 6 shows the configuration of error amplifier 2.

In this mode, IR3622 makes sure the master channel starts first followed by slave channel to prevent any glitch during start up. This is done by clamping the output of slave's error amplifier until the master channel generates the first PWM signal.

At no load condition the slave channel may be kept off depending on the offset of the error amplifier.

#### **Lossless Inductor Current Sensing**

The IR3622 uses a lossless current sensing for current share purposes. The inductor current is sensed by connecting a series resistor and a capacitor network in parallel with the inductor and by measuring the voltage across the capacitor. The measured voltage is proportional to the inductor current. This is shown figure 6. The voltage across the inductor's DCR can be expressed by:

$$V_{RL1}(s) = (V_{in} - V_{out}) * \frac{R_{L1}}{R_{L1} + sL_1}$$

----(1)

$$V_{RL1}(s) = I_{L1} * R_{L1} - - - (2)$$

The voltage across the C<sub>1</sub> can expressed by:

$$V_{c1}(s) = (V_{in} - V_{out}) * \frac{1/sC_1}{R_1 + 1/sC_1}$$

---(3)

Combining equations (1),(2) and (3) result in the following expression for  $V_{C1}$ :

$$V_{c_1}(s) = I_{L_1} * \frac{R_{L_1} + sL_1}{1 + sR_1 * C_1} - - - - (4)$$

Usually the resistor  $R_1$  and  $C_1$  are chosen so that the time constant of  $R_1$  and  $C_1$  equals the time constant of the inductor which is the inductance  $L_1$  over the inductor's DCR ( $R_{L1}$ ). If the two time constants match, the voltage across  $C_1$  is proportional to the current through  $L_1$ , and

Fig. 6: Loss Less inductor current sensing and current sharing

the sense circuit can be treated as if only a sense resistor with the value  $R_{\rm L1}$  was used.

$$If: R_{1} * C_{1} = \frac{L_{1}}{R_{L1}}$$

$$V_{C}(s) \approx I_{L1} * R_{L1}$$

The mismatch of the time constant does not affect the measurements of inductor DC current, but affects the AC component of the inductor current.

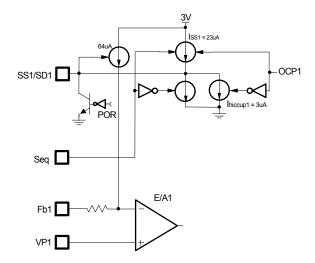

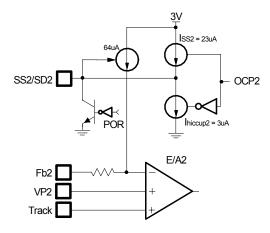

#### **Soft-Start**

The IR3622 has programmable soft-start to control the output voltage rise and limit the inrush current during start-up. It provides a separate soft-start function for each output. This will enable to sequence the outputs by controlling the rise time of each output through selection of different value soft-start capacitors.

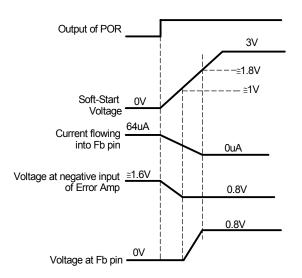

To ensure correct start-up, the soft-start sequence initiates when the Vcc, VcH1, VcH2 and Enable rise above their threshold and generate the Power On Reset (POR) signal. Soft-start function operates by sourcing an internal current to charge an external capacitor to about 3V. Initially, the soft-start function clamps the error amplifier's output of the PWM converter.

#### Soft-Start (cont.)

During power up, the converter output starts at zero and thus the voltage at Fb is about 0V. An internal voltage-controlled current source (64uA) injects current into the Fb pin and generates a voltage about 1.6V (64ux25K) across the negative input of error amplifier, see figure 7. This keeps the output of the error amplifier low.

The magnitude of this current is inversely proportional to the voltage at the soft-start pin. The 23uA current source starts to charge up the external capacitor. In the mean time, the soft-start voltage ramps up, the current flowing into Fb pin starts to decrease linearly and so does the voltage at the negative input of error amplifier.

When the soft-start voltage reaches about 1V, the voltage at the negative input of the error amplifier is approximately 0.8V.

As the soft-start capacitor voltage charges up, the current flowing into the Fb pin keeps decreasing.

The feedback voltage increases linearly as the injecting current goes down. The injecting current drops to zero when soft-start voltage is around 1.8V and the output voltage goes into steady state. Figure 8 shows the theoretical operational waveforms during soft-start.

The output start-up time is the time period when soft-start capacitor voltage increases from 1V to 1.8V. The start-up time will be dependent on the size of the external soft-start capacitor. The start-up time can be estimated by:

$$23\mu A*\frac{T_{start}}{C_{ss}}=1.8V-1V$$

For a given start up time, the soft-start capacitor (nF) can be estimated as:

$$C_{ss} \cong \frac{23(\mu A) * T_{start} (ms)}{0.8(V)}$$

----(5)

For normal start up the **Seq** pin should be pulled high (usually can be connected to Vout3).

Fig. 7: Soft-Start circuit for IR3622

Fig. 8: Theoretical operation waveforms during soft-start

SS1/SD1

VREF

SS2/SD2

Floating

#### **Output Voltage Tracking and** Sequencing

The IR3622 can accommodate a full spectrum of user programmable tracking and sequencing options using Track, Seq, Enable and Power Good pins.

Through these pins both simple voltage tracking such as that required by the DDR memory application or more sophisticated sequencing such as ratiometric or simultaneous can be implemented.

The Seq pin controls the internal current sources to set the power up or down sequencing. Toggle this pin high for power up, and toggle this pin low for power down.

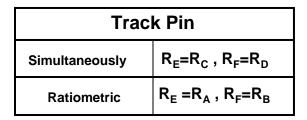

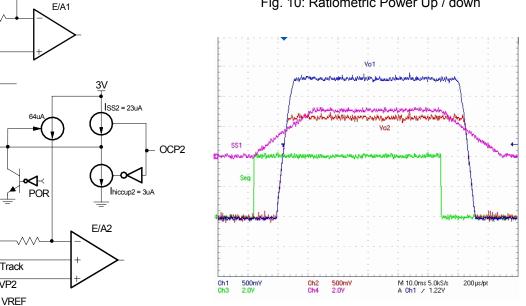

The Track pin is used to determine the second channel output for either ratiometric simultaneous by using two external resistors. Figure 9 shows how these pins are configured for different sequencing mode.

ISS1 = 23uA

In general the  $R_A$  and  $R_B$  set the output voltage for the first output and  $R_{\rm C}$  and  $R_{\rm D}$  set the output voltage for the second output.

For simultaneous vs. ratiometric, RE and RF can be selected according to the table below:

Fig. 10: Ratiometric Power Up / down

Fig. 9: Using Seq and Track pin for different sequencing

Fig. 11: Simultaneously Power up /down

#### **Fault Protection**

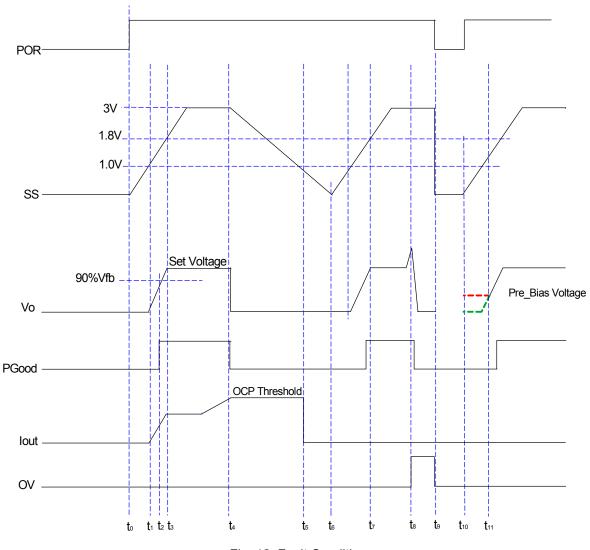

The IR3622 monitors the output voltage for over voltage protection and power good indication. It senses the  $R_{ds(on)}$  of low side MOSFET for over current protection. It also protects the output for prebias conditions. Figure 12 shows the IC's operating waveforms under different fault conditions.

Fig. 12: Fault Conditions

$t_0$  –  $t_1$ : Vcc, VcH1,VcH2 and Enable signals passed their respective UVLO threshold. Soft start sequence starts.

t<sub>1</sub> - t<sub>2</sub>: Power Good signal flags high.

$t_1 - t_3$ : Output voltage ramps up and reaches the set voltage.

$\mathbf{t_4} - \mathbf{t_5}$ : OC event, SS ramps down. IC in Hiccup mode.

$t_5$ -  $t_6$ : OC is removed, recovery sequence, fresh SS.

**t**<sub>6</sub> -**t**<sub>7</sub>: Output voltage reaches the set voltage.

$t_8$ : OVP event. HDrv turns off and LDrv turns on. The IC latches off.

${\bf t_9}$  –  ${\bf t_{10}}$ : Manually recycled the Vcc after latched OVP. PreBias start up.

t<sub>10</sub> -t<sub>11</sub>: New Soft Start sequence

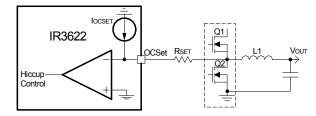

#### **Over-Current Protection**

The over current protection is performed by sensing current through the  $R_{ds(on)}$  of the low side MOSFET (Q2). This method enhances the converter's efficiency and reduce cost by eliminating a current sense resistor. As shown in figure 13, an external resistor ( $R_{SET}$ ) is connected between the OCSet pin and the drain of Q2 which sets the current limit set point.

The internal current source develops a voltage across  $R_{\text{SET}}$ . When the Q2 is turned on, the inductor current flows through the Q2 and results in a voltage drop which is given by:

$$V_{\text{OCSet}} = (I_{\text{OCSet}} * R_{\text{OCSet}}) - (R_{ds(on)} * I_{L}) \qquad \text{----}(6)$$

Fig. 13: Connection of over current sensing resistor

The critical inductor current can be calculated by setting:

$$V_{\text{OCSet}} = (I_{\text{OCSet}} * R_{\text{OCSet}}) - (R_{ds(on)} * I_L) = 0$$

$$I_{SET} = I_{L(critical)} = \frac{R_{OCSet} * I_{OCSet}}{R_{ds(on)}} - - - - (7)$$

An over current is detected if the OCSet pin goes below ground. This trips the OCP comparator and cycles the soft start function in hiccup mode.

The hiccup is performed by charging and discharging the soft-start capacitor at a certain slope rate. As shown in figure 14 the 3uA current source is used to discharge the soft-start capacitor.

The OCP comparator resets after every soft start cycles, and the converter stays in this mode until the overload or short circuit is removed. The converter will automatically recover.

Fig. 14: 3uA current source for discharging soft-start capacitor during hiccup

The OCP circuit starts sampling current when the low gate drive is about 3V. The OCSet pin is internally clamped to approximately 1.4V during deadtime to prevent false trigging. Figure 15 shows the OCSet pin during one switching cycle. There is about 150ns delay to mask out the deadtime, since this node contains switching noise, this delay also functions as a filter.

Fig. 15: OCset pin during normal condition Ch1: Inductor point, Ch2:LDrv, Ch3:OCSet

The value of  $R_{\text{SET}}$  should be checked in an actual circuit to ensure that the over current protection circuit activates as expected. The IR3622 current limit is designed primarily as short circuit protection, "no blow up" circuit, and doesn't operate as a precision current regulator.

When the SS2 is floating, an over current condition on either phase would result in hiccup current protection.

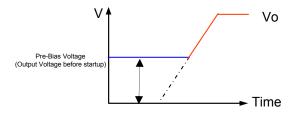

#### **Pre-Bias**

The IR3622 is able to start up into pre-charged output, which prevents oscillation and disturbances of the output voltage.

The output starts in asynchronous fashion and keeps the synchronous MOSFET off until the first gate signal for control MOSFET is generated. Figure below shows a typical Pre-Bias condition at start up.

Depending on system configuration, specific amount of output capacitance may be required to prevent discharging the output voltage.

#### **Over Voltage Protection**

Over-voltage is sensed through two dedicated sense pins  $V_{\rm SEN1}, \, V_{\rm SEN2}.$  A separate OVP circuit is provided for each channel.

The OVP threshold is user programmable and can be set by two external resistors. Upon overvoltage condition of either one of the outputs, the OVP forces a latched shutdown on the fault output. In this mode, the upper FET driver turns off and the lower FET drivers turn on, thus crowbaring the output. Reset is performed by recycling the Vcc or Enable.

#### **Power Good**

The IR3622 provides two separate open collector power good signals which report the status of the outputs. The outputs are sensed through the two dedicated  $V_{\rm SEN1}$  and  $V_{\rm SEN2}$  pins.

Once the IR3622 is enabled and the outputs reach the set value (90% of the Vout set point) the power good signals go open and stay open as long as the outputs stay within the set values. These pins need to be externally pulled high.

#### Shutdown using Soft Start pins

The outputs can be shutdown by pulling the softstart pins below 0.3V. This can be easily done by using an external small signal transistor. During shutdown both MOSFET drivers will be turned off. Normal operation will resume by cycling soft start pin.

#### **Operating Frequency Selection**

The switching frequency is determined by connecting an external resistor (Rt) to ground. Figure 16 provides a graph of oscillator frequency versus Rt. The maximum recommended channel frequency is 600kHz.

Fig. 16: Switching Frequency vs. External Resistor (Rt)

#### Frequency Synchronization

The IR3622 is capable of accepting an external digital synchronization signal. Synchronization will be enabled by the rising edge at an external clock. Per –channel switching frequency is set by external resistor (Rt). The free running frequency oscillator frequency is twice the perchannel frequency. During synchronization, Rt is selected such that the free running frequency is 20% below the synchronization frequency. Synchronization capability is provided for both single output current share mode and dual output configuration. The sync pin is noise immune, when unused it should be left floating.

#### **Thermal Shutdown**

Temperature sensing is provided inside IR3622. The trip threshold is typically set to 140°C. When trip threshold is exceeded, thermal shutdown turns off both MOSFETs. Thermal shutdown is not latched and automatic restart is initiated when the sensed temperature drops to the normal range. There is a 20°C (typical) hysteresis in the shutdown threshold.

#### **Application Information**

#### **Design Example:**

The following is a design of typical single output current share application for IR3622. The application circuit is shown on page 26.

$$V_{in} = 12V, (\pm 10\%)$$

$V_{o} = 1.8V$

$I_{o} = 40A$

$\Delta V_{o} \leq 30mV$

$F_{s} = 375kHz$

#### **Output Voltage Programming**

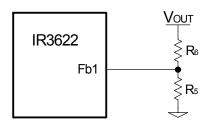

Output voltage is programmed by reference voltage and external voltage divider. As shown in figure 17 the Fb1 pin is the inverting input of the error amplifier, which is internally referenced to 0.8V. The divider is set to provide 0.8V at the Fb pin when the output is at its desired value. The output voltage is defined by the following equation:

Fig. 17: Typical application of the IR3622 for programming the output voltage

$$V_o = V_{REF} * \left(1 + \frac{R_6}{R_5}\right)$$

----(8)

Equation (8) can be rewritten as:

$$R_{s} = R_{s} * \left(\frac{V_{ref}}{V_{o} - V_{ref}}\right) \quad ---(9)$$

For the calculated values of  $R_5$  and  $R_6$  see feedback compensation section.

#### **Soft-Start Programming**

The soft-start timing can be programmed by selecting the soft-start capacitance value. The start-up time of the converter can be calculated using the following expression:

$$C_{ss}(nF) \cong 28.75(\mu A) * T_{start}(ms)$$

----(10)

Where  $T_{\text{start}}$  is the desired start-up time (ms) For a start-up time of 5ms, the soft-start capacitor will be 0.15uF. Choose a ceramic capacitor at 0.15uF.

#### **Input Capacitor Selection**

The 180° out of phase will reduce the RMS value of the ripple current seen by input capacitors. This reduces numbers of input capacitors. The input capacitors must be able to handle both the maximum ripple RMS current at the highest ambient temperature, as well as the maximum input voltage. The RMS value of current ripple for a duty cycle under 50% is expressed by:

$$I_{RMS} = \sqrt{(I_1^2 D_1 (1 - D_1) + I_2^2 D_2 (1 - D_2) - 2I_1 I_2 D_1 D_2)} - - - - (11)$$

Where:

-I<sub>RMS</sub> is the RMS value of the input capacitor current

$-D_1$  and  $D_2$  are duty cycle for each channel  $-I_1$  and  $I_2$  are the output current for each channel

For Io=40A and D=0.16 (1.8V/10.8V), the  $I_{RMS}$ = 9.43A.

Ceramic capacitors are recommended due to their peak current capabilities. They also feature low ESR and ESL at higher frequency, which enhance circuit efficiency.

Use 10x22uF, 16V ceramic capacitor from TDK (C3225X5R1C226M).

For the single output application when the duty cycle is larger than 50% the following equation can be used to calculate the total RMS current for the input capacitor current:

$$I_{RMS} = I_{O}\sqrt{(2D(1-D)+(2-2D))}$$

$D > 0.5$

#### **Inductor Selection**

The inductor is selected based on output power, operating frequency and efficiency requirements. Low inductor value results in large ripple current, smaller size, faster response to a load transient but poor efficiency and high output noise. Generally, the selection of inductor value can be reduced to desired maximum ripple current in the inductor  $(\Delta i)$ . The optimum point is usually found between 20% and 50% ripple of the output current.

For the buck converter, the inductor value for desired operating ripple current can be determined using the following relation:

$$V_{in} - V_o = L * \frac{\Delta i}{\Delta t}; \quad \Delta t = D * \frac{1}{F_s}$$

$$L = (V_{in} - V_{o}) * \frac{V_{o}}{V_{in} * \Delta j * F_{s}} - - - - (12)$$

Where:

$V_{in} = Maximum input voltage$

V<sub>o</sub> = Output Voltage

$\Delta i = Inductor ripple current$

F = Switching frequency

$\Delta t = Turn on time$

D = Duty cycle

For 2-phase single output application the inductor ripple current is chosen between 20-50% of maximum phase current

If  $\Delta i \approx 50\% (I_{\circ})$ , then the output inductor will be:

L = 0.41uH

The Coilcraft MLC1260-401ML ( $L_1$ =0.4uH, 20A,  $R_{L_1}$ =0.93mOhm) is a low profile inductor suitable for this application.

Use the following equation to calculate  $C_1$  and  $R_1$  for current sensing:

(refer to figure 6 on page 12)

$$R_1 * C_1 = \frac{L_1}{R_{11}}$$

This results to C₁=1uF and R₁=0.432K

#### **Output Capacitor Selection**

The voltage ripple and transient requirements determine the output capacitors types and values. The criteria is normally based on the value of the Equivalent Series Resistance (ESR). However the actual capacitance value and the Equivalent Series Inductance (ESL) are other contributing factors. The overall output voltage ripple can be expressed as:

$$\Delta V_{o} = \Delta V_{o(ESR)} + \Delta V_{o(ESI)} + \Delta V_{o(C)}$$

where:

$$\Delta V_{o(ESR)} = \Delta I_L * ESR ----(13)$$

$$\Delta V_{o(ESL)} = \left(\frac{V_{in}}{I}\right) * ESL$$

$$\Delta V_{o(C)} = \frac{\Delta I_L}{8 * C_o * F_s}$$

$\Delta V_{o} = Output \ voltage \ ripple$

$\Delta I_{i} = Inductor ripple current$

Therefore it is recommended to select output capacitor with low enough ESR to meet output ripple and step load transient requirements.

The output ripple is highest at maximum input voltage since  $\Delta i$  increases with input voltage.

Special Polymer capacitors offers low ESR with large storage capacity per unit volume. These capacitors offer a cost effective output capacitor solution and are ideal choice when combined with a controller having high loop bandwidth.

The IR3622 can perform well with all types of capacitors.

Panasonic EEFSXOD221R (SP, 220F, 2V, 9mOhm) is selected for this design.

Equation (13) can be used to calculate the required ESR for the specific voltage ripple.

Four SP capacitors would meet the voltage ripple requirement.

#### **Power MOSFET Selection**

The IR3622 uses two N-Channel MOSFETs per channel. The selection criteria to meet power transfer requirements are based on maximum drain-source voltage ( $V_{DSS}$ ), gate-source drive voltage ( $V_{gs}$ ), maximum output current, Onresistance  $R_{DS(on)}$ , and thermal management.

The MOSFET must have a maximum operating voltage  $(V_{DSS})$  exceeding the maximum input voltage  $(V_{in})$ .

The gate drive requirement is almost the same for both MOSFETs. Logic-level transistor can be used and caution should be taken with devices at very low gate threshold voltage ( $V_{\rm gs}$ ) to prevent undesired turn-on of the complementary MOSFET, which results a shoot-through current.

The total power dissipation for MOSFETs includes conduction and switching losses. For the Buck converter the average inductor current is equal to the DC load current. The conduction loss is defined as:

$$P_{cond} = (upperswitch) = I_{load}^2 * R_{ds(on)} * D * \mathcal{G}$$

$P_{cond} = (lowerswitch) = I_{load}^2 * R_{ds(on)} * (1-D) * \mathcal{G}$

$\mathcal{G} = R_{ds(on)}$  temperatue dependency

The  $R_{DS(on)}$  temperature dependency should be considered for the worst case operation. This is typically given in the MOSFET data sheet. Ensure that the conduction losses and switching losses do not exceed the package ratings or violate the overall thermal budget.

For this design, IRF6622 is selected for control FET and IRF6629 is selected for synchronous FET. These devices provide low on resistance in a compact Direct FET package.

The MOSFETs have the following data:

$$\begin{split} & Control FET (IRF6622); & Sync FET (IRF6629); \\ & V_{ds} = 25 V, Q_g = 18.7 n \text{C} & @10 V_{gs} \\ & V_{ds} = 25 V, Q_g = 51 n \text{C} & @10 V_{gs} \\ & R_{ds(on)} = 6.3 m \Omega @V_{gs} = 10 V \end{split}$$

The conduction losses will be:  $P_{con}$ =1.1W/Phase The switching loss is more difficult to calculate, even though the switching transition is well understood. The reason is the effect of the parasitic components and switching times during the switching procedures such as turn-on / turn-off delays and rise and fall times. The control MOSFET contributes to the majority of the

switching losses in synchronous Buck converter. The synchronous MOSFET turns on under zero voltage conditions, therefore, the turn on losses for synchronous MOSFET can be neglected. With a linear approximation, the total switching loss can be expressed as:

$$P_{sw} = \frac{V_{ds(off)}}{2} * \frac{t_r + t_f}{T} * I_{load} - - - (13A)$$

Where:

V <sub>ds(off)</sub> = Drain to source voltage at the off time

$t_r$  = Rise time

$t_f$  = Fall time

T = Switching period

I<sub>load</sub> = Load current

The switching time waveforms is shown in figure 18.

Fig. 18: switching time waveforms

From IRF6622 data sheet:

tr = 13ns

tf = 14ns

These values are taken under a certain condition test. For more details please refer to the IRF6622 data sheet.

By using equation (13A), we can calculate the switching losses.  $P_{sw}$ =2.8W

The reverse recovery loss is also another contributing factor in control FET switching losses. This is equivalent to extra current requires to remove the minority charges from synchronous FET. The reverse recovery loss can be expressed as:

$$P_{Qrr} = Q_{rr} * t_{rr} * F_{s}$$

Q.: ReverseRecoveryCharge

$t_{rr}$ : ReverseRecoveryTime

F.: SwitchingFrequency

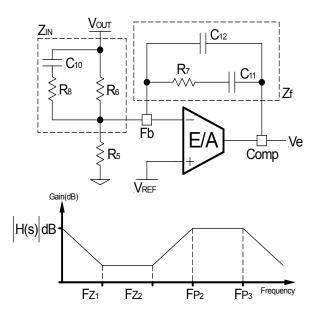

#### Feedback Compensation

The IR3622 is a voltage mode controller; the control loop is a single voltage feedback path including error amplifier and error comparator. To achieve fast transient response and accurate output regulation, a compensation circuit is necessary. The goal of the compensation network is to provide a closed loop transfer function with the highest 0dB crossing frequency and adequate phase margin (greater than 45°).

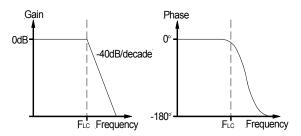

The output LC filter introduces a double pole, – 40dB/decade gain slope above its corner resonant frequency, and a total phase lag of 180° (see figure 19). The resonant frequency of the LC filter expressed as follows:

$$F_{LC} = \frac{1}{2 * \pi \sqrt{L_0 * C_0}} - - - - (14)$$

Figure 19 shows gain and phase of the LC filter. Since we already have 180° phase shift just from the output filter, the system risks being unstable.

Fig. 19: Gain and Phase of LC filter

The IR3622's error amplifier is a differential-input transconductance amplifier. The output is available for DC gain control and AC phase compensation.

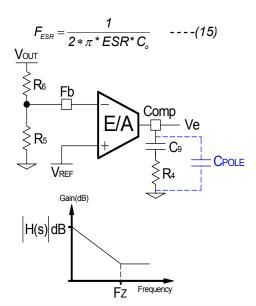

The E/A can be compensated either in type II or type III compensation. When it is used in type II compensation the transconductance properties of the E/A become evident and can be used to cancel one of the output filter poles. This will be accomplished with a series RC circuit from Comp pin to ground as shown in figure 20.

This method requires that the output capacitor has enough ESR to satisfy stability requirements. In general the output capacitor's ESR generates a zero typically at 5kHz to 50kHz which is essential for an acceptable phase margin. The ESR zero of the output capacitor expressed as follows:

Fig. 20: TypeII compensation network and its asymptotic gain plot

The transfer function (Ve/Vo) is given by:

$$H(s) = \left(g_{m} * \frac{R_{5}}{R_{5} + R_{6}}\right) * \frac{1 + sR_{4}C_{9}}{sC_{9}} \quad ---(16)$$

The (s) indicates that the transfer function varies as a function of frequency. This configuration introduces a gain and zero, expressed by:

$$[H(s)] = \left(g_m * \frac{R_s}{R_s + R_s}\right) * R_s \qquad ----(17)$$

$$F_z = \frac{1}{2\pi * R_s * C_g} \qquad ----(18)$$

The gain is determined by the voltage divider and E/A's transconductance gain.

First select the desired zero-crossover frequency (Fo):

$$F_o > F_{ESR}$$

and  $F_o \le (1/5 \sim 1/10) * F_s$

Use the following equation to calculate R<sub>4</sub>:

$$R_4 = \frac{V_{osc} * F_o * F_{ESR} * (R_5 + R_6)}{V_{in} * F_{ic}^2 * R_5 * g_m} ----(19)$$

Where:

V<sub>in</sub> = Maximum Input Voltage

$V_{osc}$  = Oscillator Ramp Voltage

F<sub>o</sub> = Crossover Frequency

F<sub>ESR</sub> = Zero Frequency of the Output Capacitor

$F_{LC}$  = Resonant Frequency of the Output Filter

g<sub>m</sub> = Error Amplifier Transconductance

To cancel one of the LC filter poles, place the zero before the LC filter resonant frequency pole:

$$F_z = 75\% F_{LC}$$

$$F_z = 0.75 * \frac{1}{2\pi \sqrt{L_o * C_o}} - - - - (20)$$

Using equations (18) and (20) to calculate C9.

$$C_{9} = \frac{1}{2\pi * R_{4} * F_{2}}$$

One more capacitor is sometimes added in parallel with  $C_9$  and  $R_4$ . This introduces one more pole which is mainly used to suppress the switching noise.

The additional pole is given by:

$$F_{p} = \frac{1}{2\pi * R_{4} * \frac{C_{9} * C_{POLE}}{C_{9} + C_{POLE}}}$$

The pole sets to one half of switching frequency which results in the capacitor  $C_{POLF}$ :

$$C_{POLE} = \frac{1}{\pi * R_4 * F_s - \frac{1}{C_9}} \cong \frac{1}{\pi * R_4 * F_s}$$

For  $F_P << \frac{F_s}{2}$

For a general solution for unconditional stability for any type of output capacitors in a wide range of ESR values, we should implement local feedback with a compensation network (typeIII). The typically used compensation network for voltage-mode controller is shown in figure 21.

In such configuration, the transfer function is given by:

$$\frac{V_e}{V_o} = \frac{1 - g_m Z_f}{1 + g_m Z_{IN}}$$

The error amplifier gain is independent of the transconductance under the following condition:

$$g_m * Z_f >> 1$$

and  $g_m * Z_{in} >> 1$  ----(21)

By replacing  $Z_{in}$  and  $Z_{f}$  according to figure 15, the transformer function can be expressed as:

$$H(s) = \frac{1}{sR_{6}(C_{11} + C_{12})} * \frac{(1 + sR_{7}C_{11}) * [1 + sC_{10}(R_{6} + R_{8})]}{[1 + sR_{7}(\frac{C_{11} * C_{12}}{C_{11} + C_{12}})] * (1 + sR_{8}C_{10})}$$

Fig. 21: Compensation network with local feedback and its asymptotic gain plot

As known, transconductance amplifier has high impedance (current source) output, which needs to be considered when loading the E/A output. If the source/sink output current capability is exceeded the amplifier will not be able to swing its output voltage over the necessary range.

The compensation network has three poles and two zeros and they are expressed as follows:

$$F_{P1} = 0$$

$$F_{P2} = \frac{1}{2\pi * R_8 * C_{10}}$$

$$F_{P3} = \frac{1}{2\pi * R_7 \left(\frac{C_{11} * C_{12}}{C_{11} + C_{12}}\right)} \cong \frac{1}{2\pi * R_7 * C_{12}}$$

$$F_{z1} = \frac{1}{2\pi * R_7 * C_{11}}$$

$$F_{z2} = \frac{1}{2\pi * C_{10} * (R_6 + R_8)} \cong \frac{1}{2\pi * C_{10} * R_6}$$

Cross over frequency is expressed as:

$$F_o = R_7 * C_{10} * \frac{V_{in}}{V_{osc}} * \frac{1}{2\pi * L_o * C_o}$$

Based on the frequency of the zero generated by output capacitor and its ESR versus crossover frequency, the compensation type can be different. The table below shows the compensation types and location of crossover frequency.

| Compensator type       | F <sub>ESR</sub> vs. F <sub>o</sub>                                  | Output capacitor           |

|------------------------|----------------------------------------------------------------------|----------------------------|

| Typll(PI)              | F <sub>LC</sub> <f<sub>ESR<f<sub>o<f<sub>s/2</f<sub></f<sub></f<sub> | Electrolytic<br>, Tantalum |

| TypellI(PID)  Method A | F <sub>LC</sub> <f<sub>o<f<sub>ESR<f<sub>s/2</f<sub></f<sub></f<sub> | Tantalum,<br>ceramic       |

| TypellI(PID)  Method B | F <sub>LC</sub> <f<sub>o<f<sub>s/2<f<sub>ESR</f<sub></f<sub></f<sub> | Ceramic                    |

Table1- The compensation type and location of  $F_{\text{ESR}}$  versus  $F_{\text{o}}$

The details of these compensation types are discussed in application note AN-1043 which can be downloaded from IR Web-Site.

For this design we have:

$$V_{in}$$

=13.2V

$V_{o}$ =1.8V

$V_{osc}$ =1.25V

$V_{ref}$ =0.8V

$g_{m}$ =3000umoh

$L_{o}$ =0.4uH, DCR=0.930mOhm

$C_{o}$ =4x220uF, ESR= 2.25mOhm

$F_{e}$ =375kHz

These result in:

$$F_{LC}=12kHz$$

(Replace L to L/2 in formula#14 for current share configuration)

$$F_{ESR}$$

=80.38kHz

$$F_{s/2} = 185 \text{kHz}$$

Select crossover frequency:

$$F_{0} < F_{ESR}$$

and  $F_{0} \le (1/5 \sim 1/10) * F_{0}$

#### F<sub>a</sub>=60kHz

Since:  $F_{LC} < F_o < F_{ESR} < Fs/2$ , typeIII method A is selected to place the pole and zeros.

The following design rules will give a crossover frequency approximately one-sixth of the switching frequency. The higher the band width, the potentially faster the load transient response. The DC gain will be large enough to provide high DC-regulation accuracy (typically -5dB to -12dB). The phase margin should be greater than 45° for overall stability.

$$R_{\gamma} \ge \frac{2}{g_{m}}$$

;  $R_{\gamma} \ge 0.67 K\Omega$ ; Select:  $R_{\gamma} = 6.04 K\Omega$

Calculate  $C_{11}$ ,  $C_{12}$  and  $C_{10}$ :

$$F_{z_1} = 0.75 * F_{LC}$$

$C_{t_1} = \frac{1}{2\pi * F_{z_1} * F_{z_2}}; C_{t_1} = 2.90nF, Select: C_{t_1} = 2.8nF$

$$F_{P3} = F_s$$

$$C_{12} = \frac{1}{2\pi * F_{P3} * R_7}; C_{12} = 70pF, Select: C_{12} = 56pF$$

$$C_{10} = \frac{2\pi * F_o * L_o * C_o * V_{osc}}{R_z * V_{io}}; C_{10} = 1.03nF,$$

Select:  $C_{10} = 1.5nF$

Calculate  $R_s$ ,  $R_s$  and  $R_s$ :

$$R_{8} = \frac{1}{2\pi * C_{10} * F_{P2}}; R_{8} = 1.32K\Omega, Select: R_{8} = 1K\Omega$$

$$R_6 = \frac{1}{2\pi * C_{10} * F_{22}} - R_8; R_6 = 7.84 K\Omega, Select: R_6 = 7.87 K\Omega$$

$$R_{\scriptscriptstyle 5} = \frac{V_{\scriptscriptstyle ref}}{V_{\scriptscriptstyle 0} - V_{\scriptscriptstyle ref}} * R_{\scriptscriptstyle 6}; R_{\scriptscriptstyle 5} = 6.30 \text{K}\Omega, \; \; \text{Select:} \; R_{\scriptscriptstyle 5} = 6.34 \text{K}\Omega$$

Check:

$$R_{s} \| R_{s} \| R_{s} \| > \frac{1}{gm}$$

$$\frac{1}{gm} = 0.33 K\Omega$$

$$0.78 k\Omega > \frac{1}{gm} \quad OK!$$

If this condition is not met, then iteration may be required by selecting larger  $R_7$ .

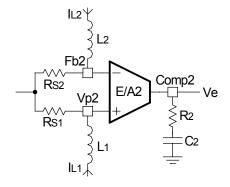

# Compensation for Current Loop (slave channel)

The slave error differential amplifier is transconductance amplifier, in 2-phase configuration the main goal for the slave channel feedback loop is to control the inductor current to match the master channel inductor current as well provides highest bandwidth and adequate phase margin for overall stability. The following analysis is valid for both using external current sense resistors and using DCR of the inductor. The transfer function of power stage is

expressed by:  $G(s) = \frac{I_{L2}(s)}{V_{s}} = \frac{V_{in}}{sL_{s} * V_{cos}} - - - - (22)$

Where:

V<sub>in</sub>=Input voltage L<sub>2</sub>=Output inductor

V<sub>osc</sub>=Oscillator Peak Voltage

As shown the G(s) is a function of inductor current. The transfer function for compensation network is given by equation (23), when using a series RC circuit as shown in figure 22.

Fig. 22: The Compensation network for current loop

$$T(s) = \frac{V_e(s)}{R_{s2}} = \left(g_m * \frac{R_{s1}}{R_{s2}}\right) * \left(\frac{1 + sC_2R_2}{sC_2}\right) \quad ----(23)$$

The loop gain function is:

$$H(s) = [G(s) * T(s) * R_{s2}]$$

$$H(s) = R_{s2} * \left(g_m * \frac{R_{s1}}{R_{s2}}\right) * \left(\frac{1 + sR_2C_2}{sC_2}\right) * \left(\frac{V_{in}}{sL_2 * V_{occ}}\right)$$

Select a zero frequency for current loop ( $F_{o2}$ ) 1.2 times larger than zero cross frequency for voltage loop ( $F_{o1}$ ).

$$F_{02} \cong 1.25\% * F_{01}$$

$$H(F_{02}) = g_m * R_{s1} * R_2 * \frac{V_{in}}{2\pi * F_{02} * L_2 * V_{osc}} = 1$$

----(24)

From (24), R2 can be expressed as:

$$R_2 = \frac{1}{g_m * R_{s1}} * \frac{2\pi * F_{o2} * L_2 * V_{osc}}{V_{in}} - - - - (25)$$

$V_{in} = 13.2V$  $V_{osc} = 1.25V$

g<sub>m</sub>=3000umoh

L<sub>2</sub>=0.4uH

$R_{s1}$ =DCR=0.930mOhm

$F_{o2}$ =72kHz

This results to :  $R_2$ =6.14K Select  $R_2$ =6.09K

The power stage of current loop has a dominant pole (Fp) at frequency expressed by:

$$F_{P} = \frac{R_{eq}}{2\pi L}$$

$$R_{eq} = R_{ds(on1)} * D + R_{ds(on2)} * (1-D) + R_{L}$$

Where  $R_{ds(on1)}$  is the on-resistance of control FET,  $R_{ds(on2)}$  is the on-resistance of synchronous FET,  $R_L$  is the DCR of output inductance and D is the duty cycle

$$R_{eq}$$

=3.7mOhm

Set the zero of compensator at 10 times the dominant pole frequency  $F_p$ , the compensator capacitor, C2 can be expressed as:

$$F_z = 10 * F_P$$

$$C_2 = \frac{1}{2\pi * R_0 * F}$$

C<sub>2</sub>=1.8nF

All design should be tested for stability to verify the calculated values.

#### **Programming the Current-Limit**

The Current-Limit threshold can be set by connecting a resistor ( $R_{SET}$ ) from drain of low side MOSFET to the OCSet pin. The resistor can be calculated by using equation (7).

The  $R_{ds(on)}$  has a positive temperature coefficient and it should be considered for the worse case operation. This resistor must be placed close to the IC, place a small ceramic capacitor from this pin to ground for noise rejection purposes.

$$I_{SET} = I_{L(critical)} = \frac{R_{OCSet} * I_{OCSet}}{R_{ds(on)}} - - - - (7)$$

$$R_{ds(on)} = 2.1 m\Omega * 1.5 = 3.15 m\Omega$$

$I_{SET} \cong I_{o(LIM)} = 20A * 1.5 = 30A$

(50% over nominal output current)

$R_{OCSet} = R_3 = R_4 = 4K\Omega$

#### **Layout Consideration**

The layout is very important when designing high frequency switching converters. Layout will affect noise pickup and can cause a good design to perform with less than expected results.

Start to place the power components, make all the connection in the top layer with wide, copper filled areas. The inductor, output capacitor should be close to each other as possible. This helps to reduce the EMI radiated by the power traces due to the high switching currents through them. Place input capacitor close to control FETs. to reduce the ESR replace the single input capacitor with two parallel units. The feedback part of the system should be kept away from the inductor and other noise sources, and be placed close to the IC. In multilayer PCB use one layer as power ground plane and have a control circuit ground (analog ground), to which all signals are referenced. The goal is to localize the high current path to a separate loop that does not interfere with the more sensitive analog control function. These two grounds must be connected together on the PC board layout at a single point. The exposed pad of IC should be connected to analog ground.

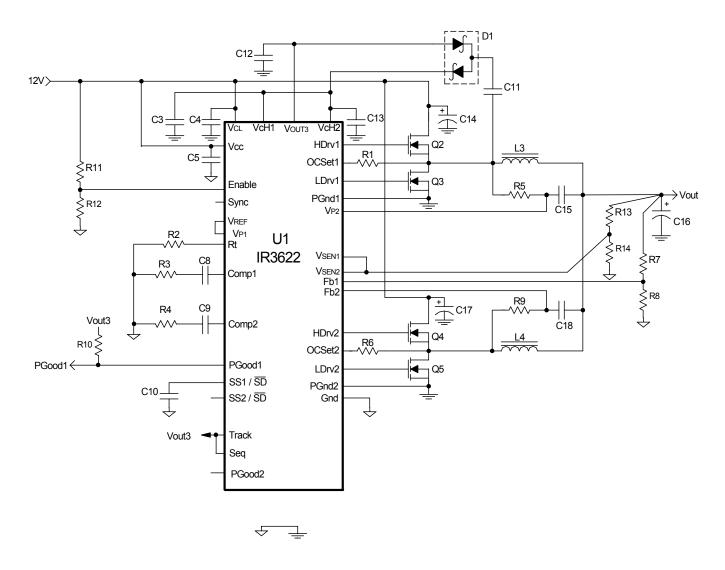

# **Typical Application**

Fig. 23: Application circuit for 12V to 1.8V @ 40A

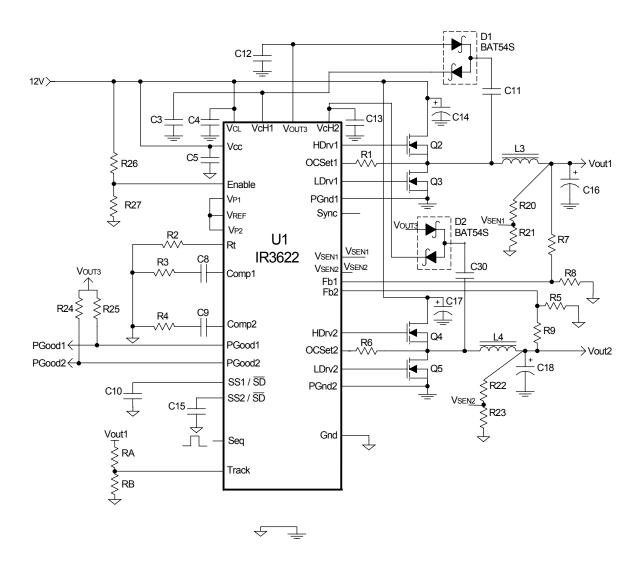

# **Typical Application**

Fig. 24: Application circuit for Dual output application Tracking and sequencing using Track pin

| Track Pin                                |                           |  |  |

|------------------------------------------|---------------------------|--|--|

| Simultaneously $R_A = R_9$ , $R_B = R_5$ |                           |  |  |

| Ratiometric                              | $R_A = R_7$ , $R_B = R_8$ |  |  |

#### **PCB Metal and Components Placement**

- Lead land width should be equal to nominal part lead width. The minimum lead to lead spacing should be  $\geq 0.2$ mm to minimize shorting.

- Lead land length should be equal to maximum part lead length + 0.3 mm outboard extension + 0.05mm inboard extension. The outboard extension ensures a large and inspectable toe fillet, and the inboard extension will accommodate any part misalignment and ensure a fillet.

- Center pad land length and width should be equal to maximum part pad length and width. However, the minimum metal to metal spacing should be  $\geq$  0.17mm for 2 oz. Copper ( $\geq$  0.1mm for 1 oz. Copper and  $\geq$  0.23mm for 3 oz. Copper).

- A single 0.30mm diameter via shall be placed in the center of the pad land and connected to ground to minimize the noise effect on the IC.

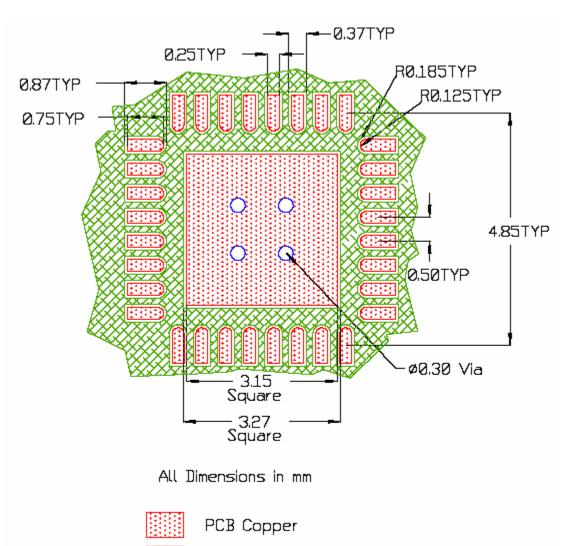

#### **Solder Resist**

- The solder resist should be pulled away from the metal lead lands by a minimum of 0.06mm. The solder resist mis-alignment is a maximum of 0.05mm and it is recommended that the lead lands are all Non Solder Mask Defined (NSMD). Therefore pulling the S/R 0.06mm will always ensure NSMD pads.

- The minimum solder resist width is 0.13mm. At the inside corner of the solder resist where the lead land groups meet, it is recommended to provide a fillet so a solder resist width of ≥ 0.17mm remains.

- The land pad should be Solder Mask Defined (SMD), with a minimum overlap of the solder resist onto the copper of 0.06mm to accommodate solder resist mis-alignment. In 0.5mm pitch cases it is allowable to have the solder resist opening for the land pad to be smaller than the part pad.

- ■Ensure that the solder resist in-between the lead lands and the pad land is  $\ge 0.15$ mm due to the high aspect ratio of the solder resist strip separating the lead lands from the pad land.

- The single via in the land pad should be tented or plugged from bottom boardside with solder resist.

www.irf.com

PCB Solder Resist

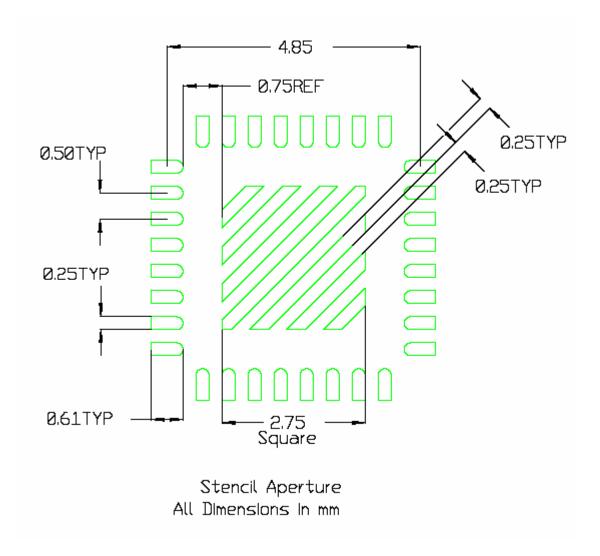

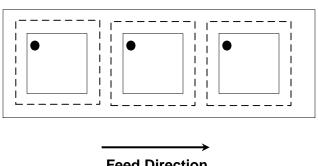

#### **Stencil Design**

- The stencil apertures for the lead lands should be approximately 80% of the area of the lead lands. Reducing the amount of solder deposited will minimize the occurrence of lead shorts. Since for 0.5mm pitch devices the leads are only 0.25mm wide, the stencil apertures should not be made narrower; openings in stencils < 0.25mm wide are difficult to maintain repeatable solder release.

- The stencil lead land apertures should therefore be shortened in length by 80% and centered on the lead land.

- The land pad aperture should be striped with 0.25mm wide openings and spaces to deposit approximately 50% area of solder on the center pad. If too much solder is deposited on the center pad the part will float and the lead lands will be open.

- The maximum length and width of the land pad stencil aperture should be equal to the solder resist opening minus an annular 0.2mm pull back to decrease the incidence of shorting the center land to the lead lands when the part is pushed into the solder paste.

\_ 0.23 SQUARE

0 18

0.18

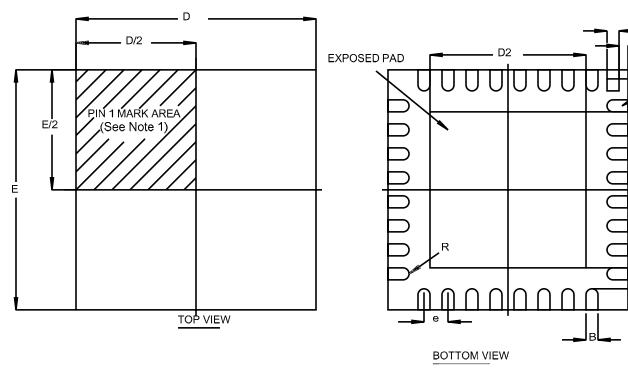

# (IR3622M) MLPQ Package; 5x5-32 Lead

Note 1: Details of pin #1 are optional, but must be located within the zone indicated. The identifier may be molded, or marked features. Carsem MLPQ32-5x5mm VHHD-2 spec.

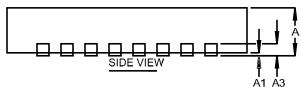

| Feed Direction |  |

|----------------|--|

| Figure A       |  |

| SYMBOL | 32 PIN 5X5 MM |      |      |  |

|--------|---------------|------|------|--|

| DESIGN | MIN           | NOM  | MAX  |  |

| А      | 0.80          | 0.90 | 1.00 |  |

| A1     | 0.00          | 0.02 | 0.05 |  |

| A3     | 0.20 REF      |      |      |  |

| В      | 0.18          | 0.23 | 0.30 |  |

| D      | 5.00 BSC      |      |      |  |

| D2     | 3.00          | 3.15 | 3.25 |  |

| E      | 5.00 BSC      |      |      |  |

| E2     | 3.00          | 3.15 | 3.25 |  |

| е      | 0.50 BSC      |      |      |  |

| L      | 0.30          | 0.40 | 0.50 |  |

| R      | 0.09          |      |      |  |

International

Rectifier

IR WORLD HEADQUARTERS: 233 Kansas St., El Segundo, California 90245, USA Tel: (310) 252-7105

TAC Fax: (310) 252-7903

This product has been designed and qualified for the Industrial market.

Visit us at www.irf.com for sales contact information Data and specifications subject to change without notice. 6/15/2007