查询TB1308FG供应商 **TOSHIBA**

### 捷多邦,专业PCB打样工厂,24小时加急出货 TB1305FG,TB1308FG

TOSHIBA BiCMOS Integrated Circuit Silicon Monolithic

# TB1305FG,TB1308FG

Component SW, Sync Separation and H/V Frequency Counter IC for TVs

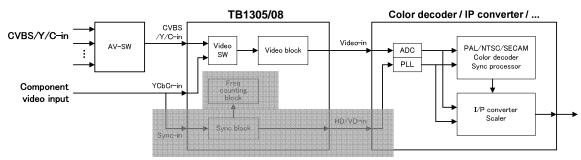

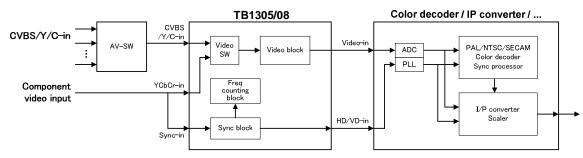

The TB1305FG and TB1308FG include a component SW block, a prefilter for AD conversion, sync separation and H/V format detectors for TV component video signals.

The TB1305FG and TB1308FG contribute to reduction in the proportion of PCB occupied by LCR filters and to the simplification of designs on analog interfaces.

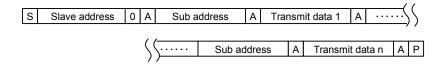

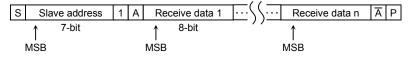

The TB1305FG and TB1308FG are equipped with an I<sup>2</sup>CBUS interface through which various functions can be controlled.

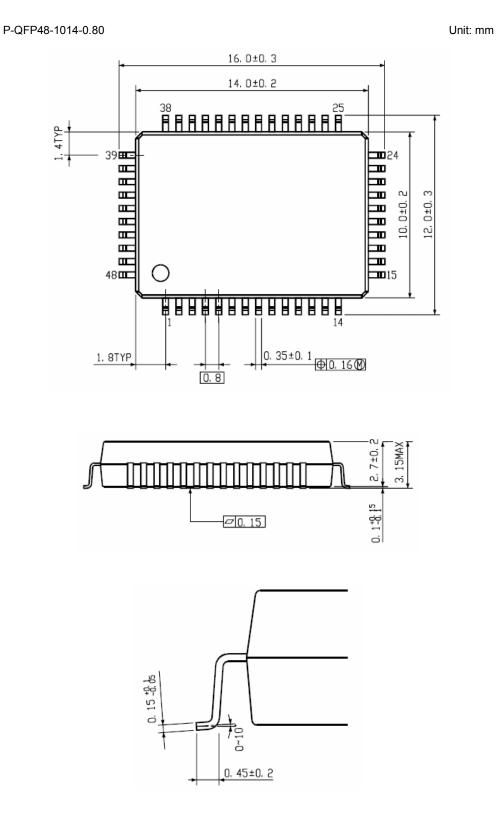

Weight: 0.83 g (typ.)

#### Features

#### COMPONENT BLOCK

- · Component video input: TB1305FG 2 channels, TB1308FG 3 channels; RGB available

- Component video output

- Gain switching: 0dB / +6dB

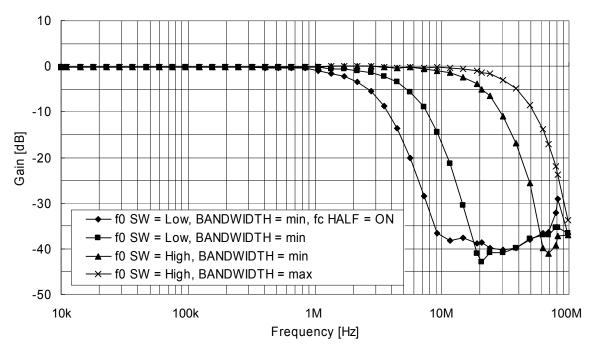

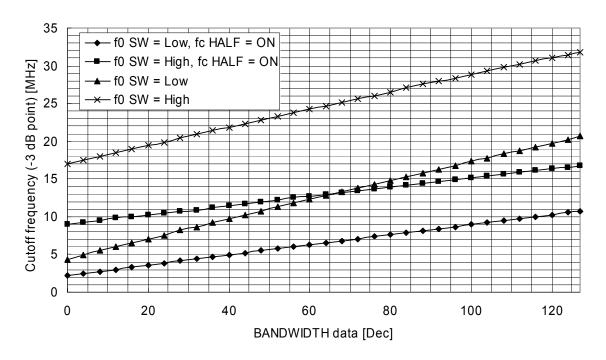

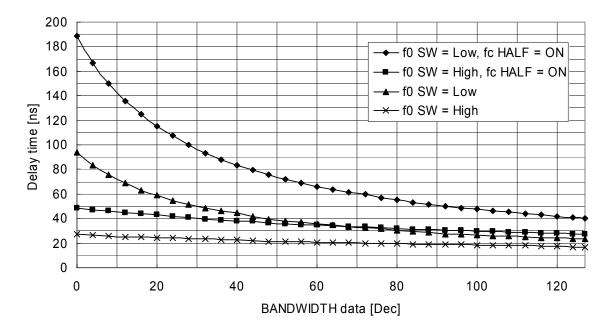

- Bandwidth filter: prefilter for ADC; 4.2 to 31MHz variable)

#### SYNC SEPARATION BLOCK

- Supports 525/60i/60p, 625/50i/50p, 750/50p/60p, 1125/50i/60i/50p/60p, 1250/50i, VGA@60, SVGA@60, XGA@60, SXGA@60, UXGA@60

- HD/VD input: 2 channels; positive and negative input acceptable

- HD/VD output: positive and negative output selectable

- Masking pseudo-sync for copyguard signal

#### OTHERS

- Line detector for D-pin (2 channels)

- Horizontal and vertical frequency counter

- Format detection circuit for input signal

- Automatic sync process switching mode

#### Lineup

| Part No. | Number of component video inputs |

|----------|----------------------------------|

| TB1305FG | 2                                |

| TB1308FG | 3                                |

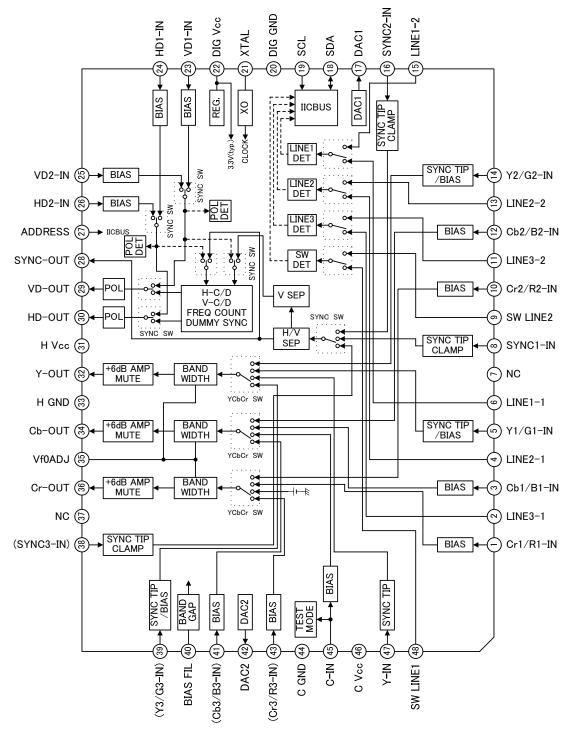

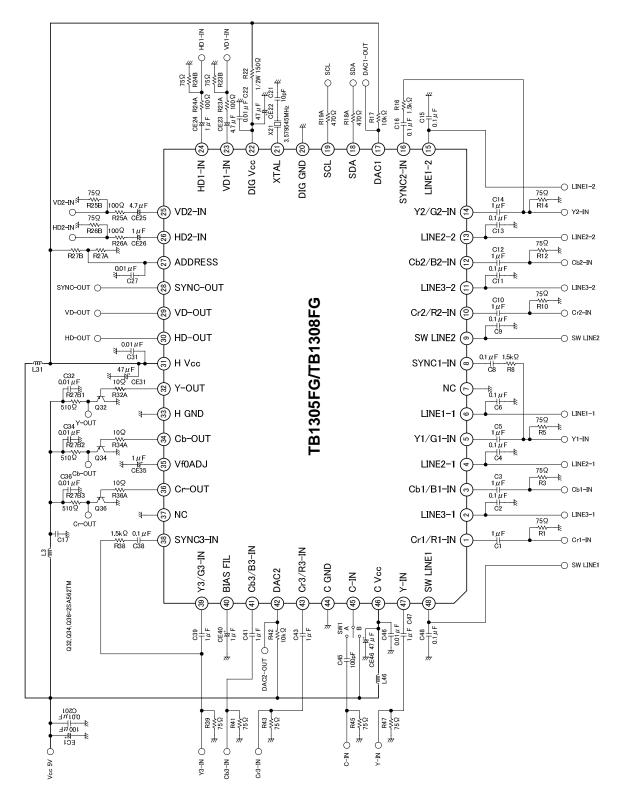

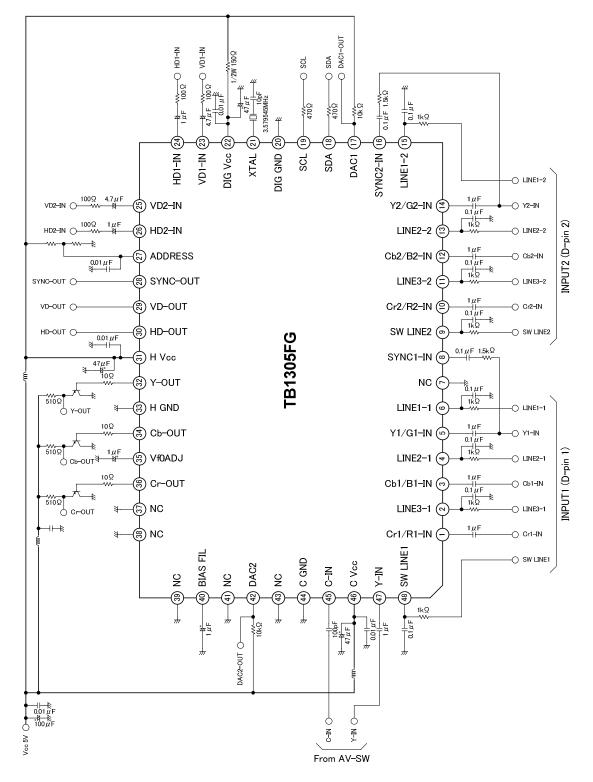

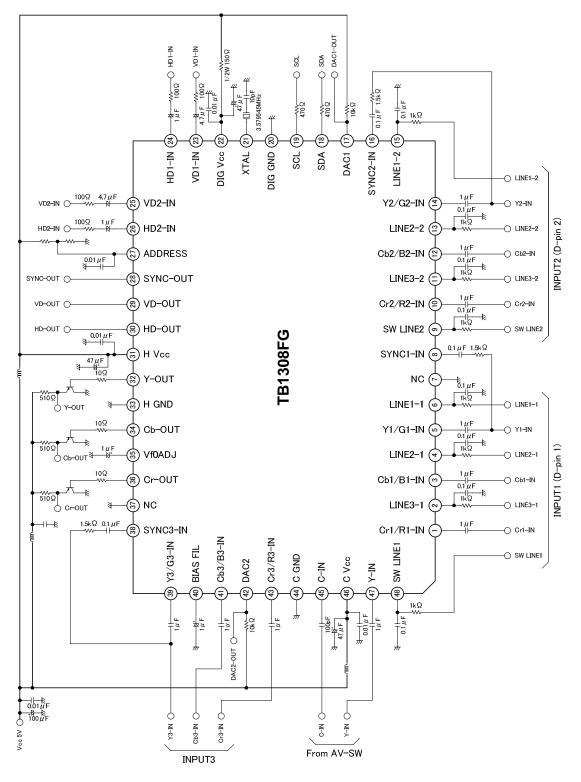

### **Block Diagram**

NOTE: Pins 38, 39, 41 and 43 are available for the TB1308FG only. The pins are NC for the TB1305FG.

The TB1305FG and TB1308FG do not support weak signals, ghost signals or other non-standard signals.

Some functional blocks, circuits or constants may be omitted or simplified in the block diagram for explanatory purposes.

#### **Pin Functions**

| Pin<br>No. | Pin Name            | Function                                                                                                                                                                                            | Interface Circuit                                                                                                                           | Input Signal/Output Signal           |

|------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| 22         | DIG V <sub>cc</sub> | $V_{cc}$ pin for the logical circuits.<br>Supply power through a resistor from pin 31<br>like the Application Circuit. This pin voltage<br>is clipped to 3.3 V (typ.) by the internal<br>regulator. |                                                                                                                                             | 3.3 V (typ.)                         |

| 20         | DIG GND             | GND pin for the logical circuits.                                                                                                                                                                   |                                                                                                                                             | _                                    |

| -          |                     | $V_{cc}$ pin for the sync circuits.                                                                                                                                                                 |                                                                                                                                             |                                      |

| 31         | H V <sub>cc</sub>   | Connect 5.0 V (typ.)                                                                                                                                                                                | —                                                                                                                                           | 5.0 V (typ.)                         |

| 33         | H GND               | GND pin for the sync circuits.                                                                                                                                                                      | _                                                                                                                                           | _                                    |

|            |                     | $V_{cc}$ pin for the video circuits.                                                                                                                                                                |                                                                                                                                             |                                      |

| 46         | C V <sub>cc</sub>   | Connect 5.0 V (typ.)                                                                                                                                                                                | —                                                                                                                                           | 5.0 V (typ.)                         |

| 44         | C GND               | GND pin for the video circuits.                                                                                                                                                                     | _                                                                                                                                           | _                                    |

|            |                     | Y or G input pin.                                                                                                                                                                                   |                                                                                                                                             |                                      |

| 5          | Y1/G1-IN            | Input the signal via a clamp capacitor.                                                                                                                                                             |                                                                                                                                             | Sync tip level: 2.1 V (typ.)         |

| 14         | Y2/G2-IN            | The clamp system is selectable by CLAMP                                                                                                                                                             |                                                                                                                                             | Bias level: 2.7 V (typ.)             |

| 39         | Y3/G3-IN            | register.                                                                                                                                                                                           |                                                                                                                                             | RGB/YCbCr/YPbPr signal<br>amplitude: |

|            | 10,00               | NOTE: Pin 39 is not available for the TB1305FG. It is an NC pin.                                                                                                                                    |                                                                                                                                             | 0.7 Vp-p (without sync)              |

|            |                     | Y or CVBS input pin.                                                                                                                                                                                | (39)<br>47 ► ≥ ≈ 101 0                                                                                                                      |                                      |

|            |                     | Input the Y or CVBS signal in NTSC, PAL or                                                                                                                                                          | Sync tip level: 2.1 V (typ.)                                                                                                                |                                      |

| 47         | Y-IN                |                                                                                                                                                                                                     |                                                                                                                                             | Bias level: 2.7 V (typ.)             |

|            |                     |                                                                                                                                                                                                     | 44                                                                                                                                          | Y/CVBS signal's amplitude:           |

|            |                     | The clamp system is selectable by CLAMP register.                                                                                                                                                   |                                                                                                                                             | 1.0 Vp-p (with sync)                 |

| 1          | Cr1/R1-IN           |                                                                                                                                                                                                     | 1 (46)                                                                                                                                      |                                      |

| 3          | Cb1/B1-IN           | Cb/Cr, Pb/Pr or B/R input pin.                                                                                                                                                                      | 3                                                                                                                                           |                                      |

| 10         | Cr2/R2-IN           | Input the signal via a capacitor.                                                                                                                                                                   |                                                                                                                                             | 2.7 V bias (typ.)                    |

| 12         | Cb2/B2-IN           | NOTE: Pins 41 and 43 are not available for                                                                                                                                                          | $(43) \qquad \qquad$ | RGB/YCbCr/YPbPr signal<br>amplitude: |

| 43         | Cr3/R3-IN           | the TB1305FG. They are NC pins.                                                                                                                                                                     |                                                                                                                                             | 0.7 Vp-p (without sync)              |

| 41         | Cb3/B3-IN           |                                                                                                                                                                                                     |                                                                                                                                             |                                      |

|            |                     |                                                                                                                                                                                                     |                                                                                                                                             | 1.7 V bias (typ.)                    |

|            |                     |                                                                                                                                                                                                     | (46)                                                                                                                                        |                                      |

|            |                     | Chroma signal input pin.                                                                                                                                                                            | •                                                                                                                                           | 5V<br>Prohibited                     |

| 45         | C-IN                | Input C signal from AV-SW via a capacitor.                                                                                                                                                          |                                                                                                                                             | 3.6V                                 |

|            |                     | When this pin's voltage is High, TEST mode for shipping is active. The pin voltage must                                                                                                             |                                                                                                                                             | n dhfh                               |

|            |                     | be less than 3.6 V during operating.                                                                                                                                                                |                                                                                                                                             |                                      |

|            |                     |                                                                                                                                                                                                     |                                                                                                                                             | 0V                                   |

|            |                     |                                                                                                                                                                                                     |                                                                                                                                             | Sync tip level: 1.75 V (typ.)        |

|            |                     |                                                                                                                                                                                                     |                                                                                                                                             | - j                                  |

|            |                     |                                                                                                                                                                                                     |                                                                                                                                             |                                      |

| c          |                     | Composite SYNC input pin to separate into H- and V-SYNC.                                                                                                                                            |                                                                                                                                             |                                      |

| 8          | SYNC1-IN            | Input the signal via a resister and a clamp                                                                                                                                                         |                                                                                                                                             | ⊔ ⊔.⊮.                               |

| 16         | SYNC2-IN            | capacitor.                                                                                                                                                                                          | 8 4                                                                                                                                         | or                                   |

| 38         | SYNC3-IN            | NOTE: Pin 38 is not available for the                                                                                                                                                               |                                                                                                                                             |                                      |

|            |                     | TB1305FG. It is an NC pin.                                                                                                                                                                          |                                                                                                                                             |                                      |

|            |                     |                                                                                                                                                                                                     |                                                                                                                                             | ┤╶╢╝╶╺┶╖╟╴╢ <sup>╹⋁┍−┍</sup>         |

|            |                     |                                                                                                                                                                                                     |                                                                                                                                             | U U¥                                 |

The equivalent circuit diagrams may be simplified or some parts of them may be omitted for explanatory purposes.

#### TB1305FG, TB1308FG

| Pin<br>No. | Pin Name             | Function                                                                                                                                                                                                                                         | Interface Circuit                                                | Input Signal/Output Signal                   |

|------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|----------------------------------------------|

| 24<br>26   | HD1-IN<br>HD2-IN     | HD input pin.<br>Input a separated horizontal sync signal<br>(1.0 to 2.0 Vp-p) via a resister and a<br>coupling capacitor.<br>The polarity of the input signal is detected<br>and its leading edge becomes a timing<br>trigger.<br>VD input pin. |                                                                  | 1.45 V bias (typ.)<br>1.0 to 2.0 Vp−p<br>or  |

| 23<br>25   | VD1-IN<br>VD2-IN     | Input a separated vertical sync signal (1.0 to 2.0 Vp-p) via a resister and a coupling capacitor.<br>The polarity of the input signal is detected and its leading edge becomes a timing trigger.                                                 | 33 <b>* 7+</b> (3)                                               | 1.0 to 2.0 Vp-p                              |

| 6<br>15    | LINE1-1<br>LINE1-2   | LINE1 (number of lines) detection pin.<br>Connect LINE1 of D-pin.                                                                                                                                                                                |                                                                  | DC                                           |

| 2<br>11    | LINE3-1<br>LINE3-2   | LINE3 (aspect ratio) detection pin.<br>Connect LINE3 of D-pin.                                                                                                                                                                                   | $\begin{array}{c} 11 \\ 15 \\ 15 \\ 15 \\ 15 \\ 15 \\ 15 \\ 15 $ | DC                                           |

| 4<br>13    | LINE2-1<br>LINE2-2   | LINE2 (i/p) detection pin.<br>Connect LINE2 of D-pin.                                                                                                                                                                                            |                                                                  | DC                                           |

| 48<br>9    | SW LINE1<br>SW LINE2 | SW LINE detection pin.<br>Connect SW LINE of D-pin.                                                                                                                                                                                              |                                                                  | DC                                           |

| 32         | Y-OUT                | Y, G or CVBS signal output pin.                                                                                                                                                                                                                  | 46                                                               |                                              |

| 34         | Cb-OUT               | Cb, Pb, B or C signal output pin.                                                                                                                                                                                                                |                                                                  | AC: 0 dB or +6 dB (typ.)                     |

| 36         | Cr-OUT               | Cr, Pr or R signal output pin.                                                                                                                                                                                                                   | 4                                                                |                                              |

| 28         | SYNC-OUT             | Separated composite sync output pin.                                                                                                                                                                                                             |                                                                  | - 3.4V(typ.)<br>0.1V(typ.)                   |

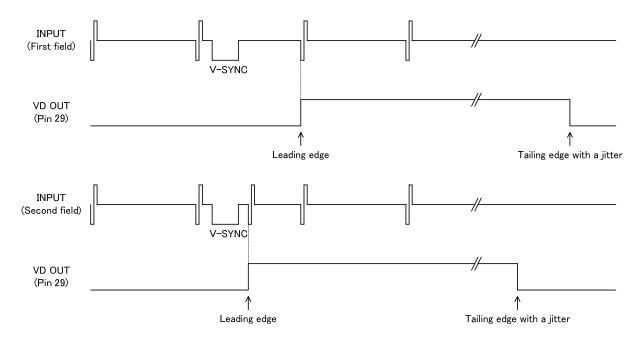

| 29<br>30   | VD-OUT<br>HD-OUT     | HD or VD output pin.<br>The polarity of the output is selectable by<br>HV-POL register.<br>The tailing edge of the VD-OUT has a jitter.<br>Use the leading edge only.                                                                            |                                                                  | or<br>0.1V(typ.)<br>0.1V(typ.)<br>0.1V(typ.) |

| 17<br>42   | DAC1<br>DAC2         | 1-bit DAC output pin.<br>Open-collector pin.                                                                                                                                                                                                     |                                                                  | DC                                           |

#### TB1305FG, TB1308FG

| Pin<br>No. | Pin Name | Function                                                                                                                              | Interface Circuit | Input Signal/Output Signal                                                                                                   |

|------------|----------|---------------------------------------------------------------------------------------------------------------------------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------|

| 21         | XTAL     | Crystal connection pin.<br>Connect a 3.579545 MHz crystal for NTSC<br>demodulation to generate internal clocks.                       |                   |                                                                                                                              |

| 35         | Vf0ADJ   | A filter pin to adjust bandwidth filter characteristics.                                                                              |                   | _                                                                                                                            |

| 40         | BIAS FIL | A filter pin for internal bias circuits.                                                                                              |                   | _                                                                                                                            |

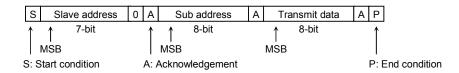

| 18         | SDA      | SDA pin for I <sup>2</sup> CBUS.                                                                                                      |                   | H to L: 1.50 V (typ.)<br>L to H: 2.25 V (typ.)                                                                               |

| 19         | SCL      | SCL pin for I <sup>2</sup> CBUS.                                                                                                      |                   | H to L: 1.50 V (typ.)<br>L to H: 2.25 V(typ.)                                                                                |

| 27         | ADDRESS  | Slave address switching pin.<br>Connect to 5 V Vcc or GND. Or leave this<br>pin open.                                                 |                   | 5 V Vcc: DC <sub>H</sub> /DD <sub>H</sub><br>Open: DA <sub>H</sub> /DB <sub>H</sub><br>GND: D8 <sub>H</sub> /D9 <sub>H</sub> |

| 7<br>37    | NC       | These pins are not used.<br>Connect to GND.<br>NOTE: Pins 38, 39, 41 and 43 of the<br>TB1305FG are not used . Connect them to<br>GND. | _                 | _                                                                                                                            |

#### **BUS Control Map**

### Write Mode Slave address: D8<sub>H</sub> / DA<sub>H</sub> / DC<sub>H</sub>

| SA | D7      | D6              | D5         | D4     | D3     | D2    | D1       | D0     | PRESET   |

|----|---------|-----------------|------------|--------|--------|-------|----------|--------|----------|

| 00 | MUTE    | FILPASS         | HD WIDTH   | DAC2   | DAC1   | YCbC  | Cr SW    | GAIN   | 00000000 |

| 01 | f0 SW   |                 | BANDWIDTH  |        |        |       |          |        | 00000000 |

| 02 | fc HALF | SYNC SW HV FREQ |            |        |        |       | 00000000 |        |          |

| 03 | HV-SEP  | VGA-SEP         | 1(PS MASK) | A SYNC | S MODE | CLAMP | HV-POL   | VD PHS | 00000000 |

NOTE: Set PS MASK = 1 (ON) for except "Sync on G" input. Remark: SA = Sub-Address.

### Read Mode Slave address: D9<sub>H</sub> / DB<sub>H</sub> / DD<sub>H</sub>

|   | D7         | D6     | D5                   | D4       | D3          | D2  | D1       | D0   |

|---|------------|--------|----------------------|----------|-------------|-----|----------|------|

| 0 | LIN        | IE1    | LINE2 LINE3 SW LI    |          | LINE2 LINE3 |     | SW LINE2 | *    |

| 1 | HD-POL     | VD-POL |                      | H FORMAT |             |     |          | RMAT |

| 2 | H FM2      | V FM2  | H IN V IN V-SYNC-W * |          |             | VER | SION     |      |

| 3 | *          |        | V FREQ DET           |          |             |     |          |      |

| 4 | H FREQ DET |        |                      |          |             |     |          |      |

\*: Undefined

### TB1305FG, TB1308FG

### **Bus Control Functions**

#### Write Mode

| Register Name | Function                                                                                                                                                                   | Preset Value   |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| MUTE          | Swtches mute mode.                                                                                                                                                         | NORMAL         |

| MUTE          | 0: NORMAL 1: Video mute                                                                                                                                                    | (0)            |

|               | Switches the bandwidth limit filter.                                                                                                                                       | ON             |

| FILPASS       | 0: ON (by-pass) 1: OFF                                                                                                                                                     | (0)            |

|               | Switches the width of HD-OUT.                                                                                                                                              |                |

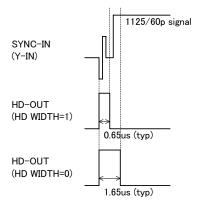

|               | 0: WIDE 1: NARROW                                                                                                                                                          | WIDE           |

| HD WIDTH      | Remark: HD WIDTH = 1 (NARROW) is recommended for the 1125/50p/60p format owing to crosstalk from HD-OUT to video signals so that spike noises on video signals will occur. | (0)            |

|               | 1-bit DAC switching                                                                                                                                                        |                |

| DAC1,2        | Output voltages of DAC1 (pin 17) and DAC2 (pin 42) are controlled. DAC1/2 are open-collector pins.                                                                         | LOW<br>(0)     |

|               | 0: LOW (ON) 1: HIGH (OPEN)                                                                                                                                                 |                |

|               | Switches the component video input and line input                                                                                                                          |                |

|               | 00: Y1 / Cb1 / Cr1 / LINE1, 2, 3-1 (pins 1, 2, 3, 4, 5, 6)                                                                                                                 |                |

| YCbCr SW      | 01: Y2 / Cb2 / Cr2 / LINE1, 2, 3-2 (pins 10, 11, 12, 13, 14, 15)                                                                                                           | Y1 / Cb1 / Cr1 |

|               | 10: Y / C (pins 45, 47. Cr-out is muted.)                                                                                                                                  | (00)           |

|               | 11: Y3 / Cb3 / Cr3 (pins 39, 41, 43)                                                                                                                                       |                |

|               | NOTE: The data (11) is not available for the TB1305FG.                                                                                                                     |                |

|               | Switches the output gain.                                                                                                                                                  |                |

|               | Gain of YCbCr output (pins 32, 34, 36) is controlled.                                                                                                                      | 0 dB           |

| GAIN          | 0: 0 dB 1: +6 dB                                                                                                                                                           | (0)            |

|               | Remark: GAIN = 0 (0 dB) is recommended for the $1125/50p/60p$ format since this offers superior frequency characteristics to those of +6 dB mode.                          |                |

| f0 SW         | Switches the f0 of bandwidth limit filter                                                                                                                                  | HIGH           |

| 10 3 10       | 0: HIGH 1: LOW                                                                                                                                                             | (0)            |

|               | Switches the f0 of bandwidth limit filter                                                                                                                                  | MIN            |

| BANDWIDTH     | 0000000: MIN (low)                                                                                                                                                         |                |

|               | 1111111: MAX (high)                                                                                                                                                        | (000000)       |

|               | Switches the frequency of bandwidth limit filters for Cb/Cr                                                                                                                |                |

| fc HALF       | The cutoff frequency of bandwidth limit filters for Cb/Cr is 1/2 to Y.                                                                                                     | OFF            |

|               | 0: OFF (same for 3 outputs) 1: ON (1/2 fc for Cb/Cr)                                                                                                                       | (0)            |

| Register Name |                                                                                                                                                                                                                                                                                                         | Function                       |                                   | Preset Value |  |  |  |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|-----------------------------------|--------------|--|--|--|

|               | Switches sync input.<br>Sync input to HD/VD-OUT                                                                                                                                                                                                                                                         |                                |                                   |              |  |  |  |

|               | HD OUT (pin 30                                                                                                                                                                                                                                                                                          | ) VD OUT (pin 29)              | SYNC OUT (pin 28)                 |              |  |  |  |

|               | 000                                                                                                                                                                                                                                                                                                     |                                |                                   |              |  |  |  |

|               | 001 SYNC2 (pin 16)                                                                                                                                                                                                                                                                                      |                                |                                   |              |  |  |  |

|               | 010                                                                                                                                                                                                                                                                                                     | SYNC3 (pin 38: TB13            | 08FG only)                        |              |  |  |  |

| SYNC SW       | 011                                                                                                                                                                                                                                                                                                     | Not available                  | e                                 | SYNC1        |  |  |  |

|               | 100 HD1 (pin 24)                                                                                                                                                                                                                                                                                        | VD1 (pin 23)                   | SYNC1 (pin 8)                     | (000)        |  |  |  |

|               | 101 HD2 (pin 26)                                                                                                                                                                                                                                                                                        | VD2 (pin 25)                   | SYNC2 (pin 16)                    |              |  |  |  |

|               | 110 HD1 (pin 24)                                                                                                                                                                                                                                                                                        | VD1 (pin 23)                   | SYNC3<br>(pin 38 : TB1308FG only) |              |  |  |  |

|               | 111 HD2 (pin 26)                                                                                                                                                                                                                                                                                        | VD2 (pin 25)                   | SYNC3<br>(pin 38: TB1308FG only)  |              |  |  |  |

|               | NOTE: SYNC3 of the data 01                                                                                                                                                                                                                                                                              | ), 110, 111 is not availa      | ble for the TB1305FG.             |              |  |  |  |

| HV FREQ       | Set the horizontal and verti<br>0000: 15.625 kHz, 50 Hz<br>0010: 31.25 kHz, 50 Hz<br>0100: 28.125 kHz, 50 Hz<br>0110: 37.5 kHz, 50 Hz<br>1000: 31.25 kHz, 50 Hz<br>1001: 37.9 kHz, 60 Hz (S<br>1010: 64 kHz, 60 Hz (U)<br>1101: 75 kHz, 60 Hz (U)<br>1100: 56.25 kHz, 50 Hz<br>1101 ~ 1111: Not availat | 15.625 kHz, 50 Hz<br>(0000)    |                                   |              |  |  |  |

| HV-SEP        | Switches the separation level<br>The H/V sync separation le<br>0: LOW<br>Remark: The separation leve<br>width per H period a                                                                                                                                                                            | LOW<br>(0)                     |                                   |              |  |  |  |

| VGA-SEP       | Switches the separation level<br>The H/V sync separation<br>signals.<br>0: Normal (component vi<br>Remark: The separation leve<br>width per H period a                                                                                                                                                  | Normal<br>(0)                  |                                   |              |  |  |  |

| PS MASK       | Switches the mask mode for p<br>Pseudo-syncs in lines are r<br>0: OFF (V-BLK period or<br>NOTE: Set PS MASK = 1 (ON                                                                                                                                                                                     | emoved.<br>ly) 1: ON (all line | ,                                 | OFF<br>(0)   |  |  |  |

### TB1305FG, TB1308FG

| Register Name | Function                                                                                                                                                                                                                                                                                                                   | Preset Value |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

|               | Automatic sync processing mode.                                                                                                                                                                                                                                                                                            |              |

| A-SYNC        | Sync processing mode is changed in accordance with the results obtained by the internal format detection circuits. Format detection is performed for a SYNC or HD/VD signal selected by SYNC SW. The result of detection is returned to H, V FORMAT and H, V FM2. The HV FREQ setting is invalid when this mode is active. | OFF<br>(0)   |

|               | 0: OFF (manual switching mode by HV FREQ setting)                                                                                                                                                                                                                                                                          |              |

|               | 1: ON                                                                                                                                                                                                                                                                                                                      |              |

|               | Switches sync output mode.                                                                                                                                                                                                                                                                                                 |              |

| S MODE        | This function sets the dummy HD/VD output mode when there is no input. The frequency of the dummy HD/VD output depends on the HV FREQ setting (when A-SYNC = OFF) or H, V FORMAT (when A-SYNC = ON).<br>H, V IN shows whether there is no input or not.                                                                    | OFF<br>(00)  |

|               | 0: OFF (No HD and free-run VD output (approx. 44 Hz), when there is no input. However, in 1250i mode, no HD and no VD output, when there is no input.)                                                                                                                                                                     | (00)         |

|               | 1: ON (Dummy HD/VD output when there is no input)                                                                                                                                                                                                                                                                          |              |

|               | Switches Y clamping mode.                                                                                                                                                                                                                                                                                                  | SYNC TIP     |

| CLAMP         | This function sets the clamping mode for pins 5, 14, 39.                                                                                                                                                                                                                                                                   | (0)          |

|               | 0: SYNC TIP CLAMP 1: BIAS                                                                                                                                                                                                                                                                                                  | (0)          |

|               | Switches the polarity of the HD/VD output.                                                                                                                                                                                                                                                                                 | Positive     |

| HV-POL        | This function sets the polarity of HD/VD OUT (pins 29, 30).                                                                                                                                                                                                                                                                | (0)          |

|               | 0: Positive 1: Negative                                                                                                                                                                                                                                                                                                    | (0)          |

|               | Switches the phase of dummy VD output.                                                                                                                                                                                                                                                                                     |              |

| VD PHS        | VD PHS compensates for delay time so that the dummy VD-OUT phase is the same as that form the separated V-sync.                                                                                                                                                                                                            | No-delay     |

|               | 0: No delay                                                                                                                                                                                                                                                                                                                | (0)          |

|               | 1: 0.2 H delay (0.15 H delay for 1125/50p)                                                                                                                                                                                                                                                                                 |              |

#### **Read Mode**

| Register Name | Function                                                                                                                                                                  |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               | LINE1 detection for D-pin (for the number of lines)                                                                                                                       |

| LINE1         | 00: 525 (480) 01: 750 (720) 10: 11: 1125 (1080)                                                                                                                           |

|               | Detects the voltage of LINE1 selected by YCbCr SW. 11 is returned when the pin is not connected.                                                                          |

|               | LINE2 detection for D-pin (for i/p)                                                                                                                                       |

| LINE2         | 0: Interlace 1: Progressive                                                                                                                                               |

|               | Detects the voltage of LINE2 selected by YCbCr SW. 1 is returned when the pin is not connected.                                                                           |

|               | LINE3 detection for D-pin (for aspect ratio)                                                                                                                              |

| LINE3         | 00: 4:3 01: 4:3 letter box 10: 11: 16:9                                                                                                                                   |

|               | Detects the voltage of LINE3 selected by YCbCr SW. 11 is returned when the pin is not connected.                                                                          |

| SW LINE1      | SW LINE1 (pin 48) detection for D-pin                                                                                                                                     |

| SVV LINE I    | 0: Connected 1: Not connected                                                                                                                                             |

|               | SW LINE1 (pin 9) detection for D-pin                                                                                                                                      |

| SW LINE2      | 0: Connected 1: Not connected                                                                                                                                             |

|               | Polarity detection to HD-IN                                                                                                                                               |

| HD-POL        | 0: Positive 1: Negative                                                                                                                                                   |

|               | Detects the width from the HD-IN pin to determine whether it is negative or not. When the High level of the input HD-IN is wider than approx 14 $\mu s$ , HD-POL shows 1. |

### TB1305FG, TB1308FG

| Register Name | Function                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|               | Polarity detection to VD-IN                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| VD-POL        | 0: Positive 1: Negative                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

|               | Detects the width from the VD-IN pin to determine whether it is negative or not. When the High level of the input VD-IN is wider than approx 4.5 ms, VD-POL shows 1.                                                                                                                                             |  |  |  |  |  |

|               | Horizontal format detection                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

|               | 0000: 15.625/15.75kHz 0001: 28.125kHz 0010: 31.25/31.5kHz 0011: 33.75kHz                                                                                                                                                                                                                                         |  |  |  |  |  |

|               | 0100: 37.5/37.9kHz 0101: 45/48kHz 0110: 64kHz/67.5kHz 0111: 75kHz                                                                                                                                                                                                                                                |  |  |  |  |  |

|               | 1000 56.25kHz 1001 ~ 1111: Undefined                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| H FORMAT      | Detects a horizontal format (horizontal frequency).                                                                                                                                                                                                                                                              |  |  |  |  |  |

|               | NOTE1: Format detection errors such as the following can occur when suppressed syncs are input. See<br>NOTE3 in the function description on Automatic sync processing mode, too.<br>525i input → 525p detected, 625i input → 625p detected, 1125i input → 1125p detected<br>525p/625p input → No V-sync detected |  |  |  |  |  |

|               | NOTE2: When 525i, 625i, 1125/50i or 1125/60i signal is input, H FORMAT data can be incorrect caused<br>by the pseudo-syncs for copy guard or the equalizing pulses.                                                                                                                                              |  |  |  |  |  |

|               | Vertical format detection                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| V FORMAT      | 00: 50 Hz 01: 60 Hz 10 ~ 11: Undefined                                                                                                                                                                                                                                                                           |  |  |  |  |  |

|               | Detects a vertical format (horizontal frequency) according to V FREQ DET data.                                                                                                                                                                                                                                   |  |  |  |  |  |

|               | Horizontal format detection 2                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

|               | 0: Known 1: Unknown                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| H FM2         | Detects whether an input is in one of the defined formats or not. This is based on H FORMAT data.                                                                                                                                                                                                                |  |  |  |  |  |

|               | NOTE: H FM2 may indicate Unknown, when 525p input with pseudo sync signal for copy guard is input.                                                                                                                                                                                                               |  |  |  |  |  |

|               | Vertical format detection 2                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| V FM2         | 0: Known 1: Unknown                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

|               | Detects whether an input is in one of the defined formats or not. This is based on V FORMAT data.                                                                                                                                                                                                                |  |  |  |  |  |

|               | Input detection to horizontal syncs                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| H IN          | 0: No signal 1: Signal                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| V/ INI        | Input detection to vertical syncs                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| V IN          | 0: No signal 1: Signal                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

|               | V-SYNC width detection                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

|               | 0: Wide 1: Narrow                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| V-SYNC-W      | Detects V-SYNC width for detecting 1250i format.<br>Under A-SYNC = 1 (ON), V-SYNC-W shows 1, when the VD width from the VD-IN pin is narrower than approx 69 $\mu$ s, or when the V-SYNC width from the SYNC-IN pin is narrower than approx 27 $\mu$ s.                                                          |  |  |  |  |  |

| VERSION       | IC version identification                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| VERSION       | 00: TB1305FG 01: TB1308FG 10: 11:                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|               | Counts the vertical frequency of an input selected by SYNC SW.                                                                                                                                                                                                                                                   |  |  |  |  |  |

|               | 0000000: Over 3.5kHz 1001111: 44Hz or less                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|               | 1010000~11111111: No signal                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| V FREQ DET    | How to calculate a vertical frequency (Y):                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|               | Convert data read from V FREQ DET into decimal value and call it X.                                                                                                                                                                                                                                              |  |  |  |  |  |

|               | Vertical frequency (Y) = $1 \div (X \times 2.8607 \times 10^{-4})$ [Hz]                                                                                                                                                                                                                                          |  |  |  |  |  |

|               | The error range of X is -1 to +1.                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|               | Counts the horizontal frequency of an input selected by SYNC SW.                                                                                                                                                                                                                                                 |  |  |  |  |  |

|               | 00000000: No signal 11111111: Over 85kHz                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| H FREQ DET    | How to calculate a horizontal frequency (Y):                                                                                                                                                                                                                                                                     |  |  |  |  |  |

|               | Convert data read from H FREQ DET into decimal value and call it X.                                                                                                                                                                                                                                              |  |  |  |  |  |

|               | Horizontal frequency (Y) = $1 \div (0.003 \div X)$ [Hz]                                                                                                                                                                                                                                                          |  |  |  |  |  |

|               | The error range of X is $-1$ to $+1$ .                                                                                                                                                                                                                                                                           |  |  |  |  |  |

- Note 1: In determining the decision algorithms (detection range, detection times and so on) for H/V frequency detection, it is necessary to take into account both previously mentioned cautions and other factors such as signal conditions and I<sup>2</sup>CBUS data transmission in the course of prototype TV set evaluation.

- Note 2: The READ BUS flags indicate that a certain signal is detected at a given moment. However, the detection result will not be very reliable if only one flag is checked. To obtain accuracy, it is recommended that a judgment will be made on the basis of confirming several times and verifying agreement among the majority of flags read in a sequence and/or at the same time.

#### **Function Descriptions**

#### Vertical sync separation for 1250i/50

When HV FREQ = 1000, the vertical sync separation for 1250i/50 is accomplished through the use of a special circuit. The phase of the VD-out (pin 29) depends on the H-SYNC timing shown in the figure below. There is no VD-out when there is no H-SYNC input.

In the manual sync processing mode (A-SYNC = OFF), use READ BUS functions, V-SYNC-W and H, V FORMAT (or H, V FREQ DET) to detect 1250i/50.

NOTE: The VD-OUT's tailing edge has a jitter. Use the leading edge only.

#### HD width

HD-OUT width is selectable by HD WIDTH, as below. HD WIDTH = 1 (NARROW) is recommended for the 1125/50p/60p format owing to crosstalk from HD-OUT to video signals so that spike noises on video signals will occur.

#### Automatic sync processing mode (A-SYNC)

Counted horizontal and vertical frequency data to input signal are returned to READ BUS functions, H, V FREQ DET. Also, the detected format is returned to H, V FORMAT and H, FM2 when the H/V frequencies are in internal defined ranges. Input detection results, which indicate whether there is an input or not, for H, V-SYNC or HD, VD are returned to H, V IN. In automatic sync processing mode (when A-SYNC = ON), the TB1305FG and TB1308FG operate as indicated in the following table according to these READ data.

| INPUT<br>CONDITION     | H, V FORMAT status                                                                    | H, V FM2 status                                                                              | H, V IN status | HD, VD outputs                                                                     |

|------------------------|---------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|----------------|------------------------------------------------------------------------------------|

| Standard format        | The format as input                                                                   | The format as input Known                                                                    |                | The separated sync as input                                                        |

| Non-standard<br>format | The status indicates not<br>the current condition<br>but the last detected<br>format. | Unknown                                                                                      | Signal         | The separated sync as input                                                        |

| No input               | The status indicates not<br>the current condition<br>but the last detected<br>format. | Known:<br>The status indicates not<br>the current condition but<br>the last detected format. | No signal      | Dummy HD and VD, of<br>which the frequency<br>depends on the H, V<br>FORMAT status |

NOTE 3: The following format detection errors can occur when suppressed syncs are input.

525i input  $\rightarrow$  525p detected, 625i input $\rightarrow$  625p detected, 1125i input $\rightarrow$  1125p detected 525p/625p inputs  $\rightarrow$  In case of the 525p/625p sync amplitude become bigger from zero to its standard gradually, V-sync of the input is not detected even though the sync amplitude is got back to its standard amplitude.

The V-sync separation performance to the suppressed sync input may be improved when VGA-SEP is set to 1 (VGA), though the H and V separation level are also changed.

- NOTE 4: We recommend recognizing a format by H/V FREQ DET rather than one by H/V FORMAT because H FORMAT and H FM2 can indicate an incorrect data for 525i, 625i, 525p, 1125/50i and 1125/60i caused by the pseudo-syncs for copy guard or the equalizing pulses.

- NOTE 5: Dummy HD and VD may become unstable while the mode is changing from one format to another.

By the way, in A-SYNC = OFF and S-MODE = ON mode, dummy HD and VD are output according to HV FREQ setting when there is no input.

#### Manual sync processing mode (A-SYNC = OFF \*NOTE6)

HV FREQ = 625p is required to separate H-SYNC and V-SYNC properly. Set HV FREQ = 625p to count H/V-SYNC for Manual sync processing mode.

The following is an example of how to detect H/V frequency when A-SYNC=OFF.

- 1. Set HV FREQ = 625p(0010) and read data such as H, V FREQ DET.

- 2. Detect the H/V frequencies by microprocessor or similar means, depending on the data obtained.

- 3. Set HV FREQ and so on to the detected mode.

- 4. Continue to monitor the obtained data such as H, V FREQ DET. When any alteration is recognized, set HV FREQ = 625p(0010) and detect again.

Decision algorithms (for detection range, detection times and so on) for H/V frequency detection should be determined taking into account the above-mentioned errors in measuring H/V frequencies and the other factors such as signal conditions and I<sup>2</sup>CBUS data transmission in the course of prototype TV set evaluation.

NOTE 6: We recommend recognizing formats for 525i and 625i signals by another device such as a color-decoder, not by this product, because 525i and 625i signals include non-standard signals.

However, if you use this product to recognize formats including the standard 525i and 625i, set "A-SYNC = ON". Otherwise, H/V FREQ DET and H/V FORMAT may indicate incorrect value and VD-OUT may lock irregularly for 525i and 625i signals. Refer to the "Application circuit 3 (system configuration)", too.

#### Sync separation level

The sync separation level is changed according to the ratio of H-sync width to one line and the connected resistance. Typical sync separation levels for each format are as follows. Then, VGA-SEP=1 for VGA to UXGA.

| Format   | H۷         | /-SEP = 0 (LO | W)         | ΗV         | /-SEP = 1 (HIG | GH)        |

|----------|------------|---------------|------------|------------|----------------|------------|

| Format   | R = 1.2 kΩ | R = 1.5 kΩ    | R = 1.8 kΩ | R = 1.2 kΩ | R = 1.5 kΩ     | R = 1.8 kΩ |

| 625/50i  | 22         | 28            | 33         | 24         | 32             | 37         |

| 525/60i  | 22         | 28            | 34         | 24         | 31             | 37         |

| 625/50p  | 22         | 28            | 34         | 25         | 31             | 38         |

| 525/60p  | 21         | 27            | 32         | 24         | 30             | 36         |

| 1125/50i | 31         | 39            | 45         | 40         | 49             | 54         |

| 1125/60i | 26         | 33            | 39         | 34         | 43             | 50         |

| 750/50p  | 29         | 37            | 43         | 37         | 46             | 52         |

| 750/60p  | 24         | 31            | 37         | 32         | 40             | 47         |

| 1250/50i | 25         | 32            | 37         | 32         | 41             | 47         |

| 1125/50p | 36         | 45            | 51         | 45         | 54             | 58         |

| 1125/60p | 31         | 39            | 45         | 39         | 49             | 55         |

| VGA/60   | 15         | 19            | 23         | 16         | 21             | 25         |

| SVGA/60  | 15         | 18            | 22         | 16         | 20             | 24         |

| XGA/60   | 17         | 22            | 26         | 19         | 24             | 28         |

| SXGA/60  | 27         | 33            | 39         | 30         | 37             | 43         |

Unit [%] ; where 286 mVp-p sync for 525/60i and 300 mVp-p sync for others

For "Sync on G" signal, HD-OUT is not output during V-sync period because there is no H-sync during V-sync period. Furthermore, for Sync on G of XGA input, HD-OUT disappears during active video period caused by unexpected lock of the internal V-BLK.

The format detection and sync separation performances are changed due to the separation level set by HV-SEP, VGA-SEP setting and/or the connected resistance with SYNC-IN pin. The careful evaluations are required to set the separation level under consideration of expected input conditions such as a suppressed sync input, an input with V-sag and APL (Average Picture Level) fluctuations.

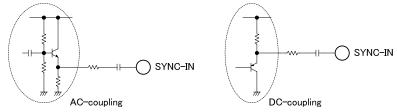

#### Note on Sync input pin

If the AC-coupling circuit is put before the SYNC-IN pin, the picture on the screen may be not stable. This is because the sync separation circuit is unable to follow the DC level fluctuation caused by APL (Average Picture Level) change in the input signal, and the HD and/or VD output is unable to synchronize the input.

It is recommended to input signals via the DC-coupling buffer if necessary.

For the DC level fluctuation caused by APL change, the sync separation ability may be improved to change the setting of HV-SEP, VGA-SEP and/or changing the resister R. Furthermore, adding a high-resistance around several  $M\Omega$  between SYNC-IN pin and GND (or Vcc) may improve the sync separation ability.