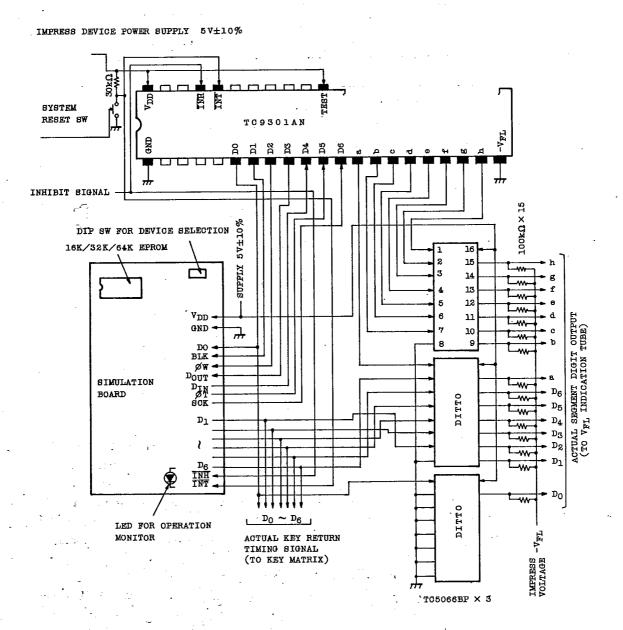

DTS MICRO CONTROLLER CONTAINING HIGH VOLTAGE VACUUM FLUORESCENT INDICATION TUBE DRIVER

TC9301AN is 4-bit CMOS micro controller for digital tuning system use having built-in high voltage driver able to directly drive vacuum fluorescent indication tube.

CPU has 4-bit parallel adittion and subtractions (AI, SI instructions, etc.), logical operations (OR, AN instructions, etc.), plural bit judge and comparison instructions (TM, SL instructions, etc.) and time base function.

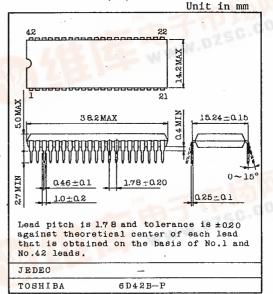

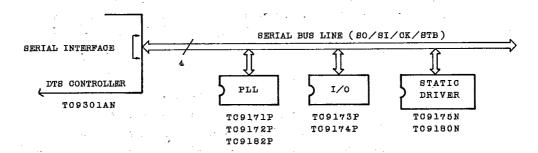

The equipment consists of shrink type DIP 42-pin and has abundant I/O ports and exclusive key input ports controlled by powerful input and output instruction (IO, KEY instructions, etc.), serial bus control function (SIO instruction) to control forcibly external PLL LSI and peripheral ICs.

Weight: 4.0g

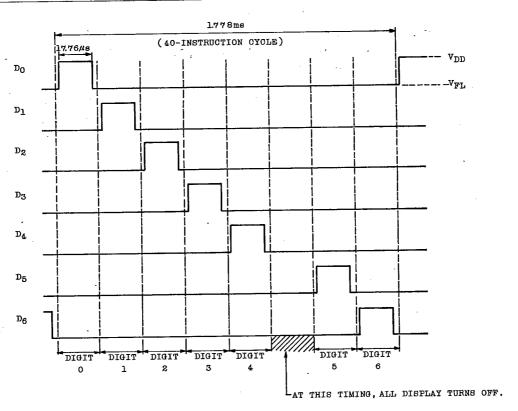

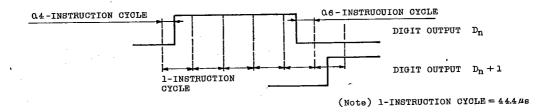

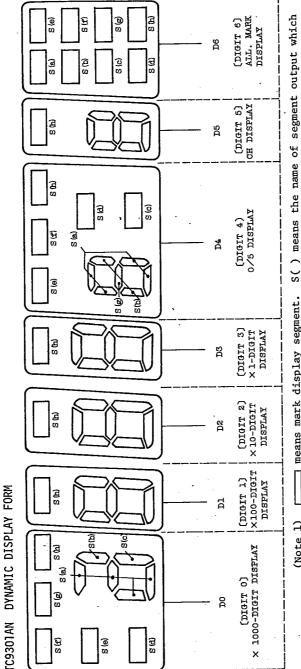

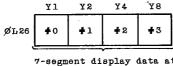

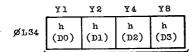

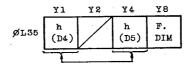

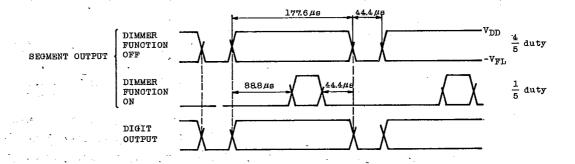

Moreover, it has exclusive output terminals of 7-digit, 8-segment dynamic display type VFL indication tube driver and exclusive terminal for outputting eight kinds of reference frequency signal to be supplied to PLL LSI.

And TC9301AN is pin-compatible with TC9303AN (program memory capacity, 1K-step type).

### FEATURES:

- . 4-bit micro controller for digital tuning system use.

- . Built-in VFL indication tube driving circuit of dynamic display type.

- . 5V±10% single power supply. CMOS structure and low power dissipation.

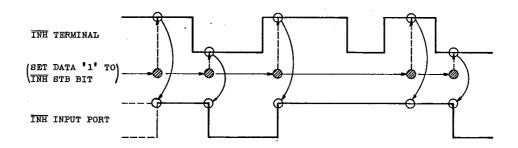

- . Backup of data memory (RAM) and each port is easily made (by INH terminal).

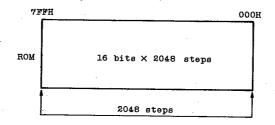

- . Program memory (ROM) : 16 bits X 2048 steps

- . Data memory (RAM) : 4 bits X 128 words

- . Powerful instruction sets of 62 kinds (all one-word instructions).

- . Basic instruction executing time 44.4µs (7.2MHz crystal connection).

- . Abundant addition and subtraction instructions (addition instructions 12 kinds, subtraction instructions 12 kinds).

- . Powerful compound judge instruction (TMTR, TMFR, TMT, TMF instruction).

THE REPORT OF THE PROPERTY OF

T-49-19-57

- . Data transfer in the same row address is possible.

- . Indirect transfer of register is possible (MVRD, MVRS, MVGD, MVGS instructions).

- . 16 powerful general registers (arranged in RAM).

- . Stack level : 1 level

- . Program memory (ROM) has no conception of page or field, and JUMP and CAL instructions can be freely made within 2048 steps.

- . It is possible to freely refer to the contents, 16 bits, of optional address within 1024 steps in program memory (ROM) (DAL instruction).

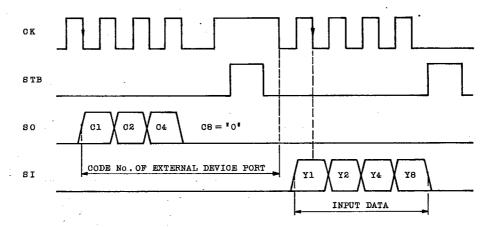

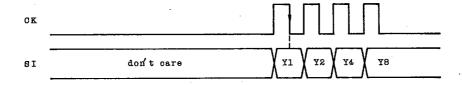

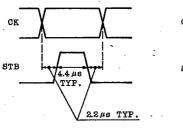

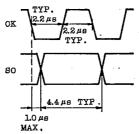

- . Built-in powerful exclusive serial bus control function.

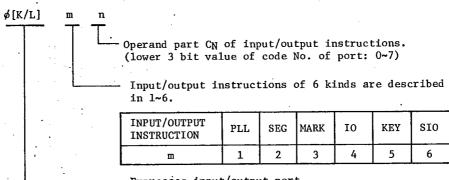

- . Powerful input and output instructions (6 kinds of instructions: IO, KEY, SIO, etc.).

- . Exclusive terminal is provided for display and key input (7-digit, 8-segment dynamic display type).

- . Direct drive of VFL indication tube is possible by both digit and segment.

- . Built-in P-ch high breakdown voltage FET and load resistor (withstand voltage 32V MAX.) in both digits (D0~D6) and segments (a~h).

- . Abundant 10 I/O ports (ports capable of input/output setting in 1-bit unit: 9, exclusive output port: 1).

- . Clock stop is possible by instruction (during CKSTP instruction: supply current,  $1\mu A$  or below).

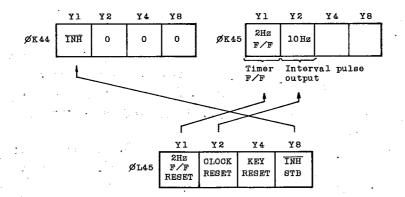

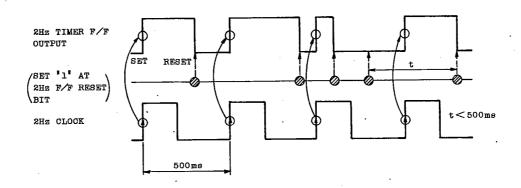

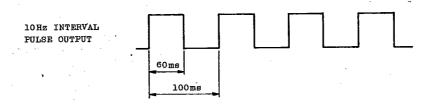

- . 2Hz timer F/F and 10Hz interval pulse output are contained (internal port for time base use).

- . Reference frequencies of eight kinds to be supplied to PLL LSI can be selected with program (1kHz, 5kHz, 9kHz, 10kHz, 12.5kHz, 25kHz, 50kHz or 100kHz).

- . Pin compatible with TC9303AN (ROM capacity: 16-bit X 1024 steps).

### MAXIMUM RATINGS (Ta=25°C)

| CHARACTERISTIC                      | SYMBOL           | RATING                                     | UNIT |

|-------------------------------------|------------------|--------------------------------------------|------|

| Supply Voltage                      | $v_{DD}$         | -0.3~6.0 -                                 | v    |

| Input Voltage                       | VIN              | -0.3~VDD+0.3                               | v    |

| Power Dissipation                   | PD               | 800                                        | mW   |

| Operation Temperature               | Topr             | 30~75                                      | °c   |

| Storage Temperature                 | Tstg             | -55~125                                    | °c   |

| Open Drain Output Breakdown Voltage | V <sub>BDS</sub> | 35 (Voltage between drain and source)      | v    |

| Key Input Voltage                   | VINK             | -V <sub>FL</sub> -0.3~V <sub>DD</sub> +0.3 | v    |

T-49-19-57

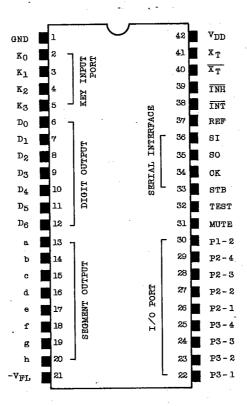

TERMINAL CONNECTION DIAGRAM

TOP VIEW SHRINK DIP-42 PIN

T-49-19-57

| ELECTRICAL CHARACTERISTICS                       | Ouress of          | therwise specified, Ta=25°C,                     | , עטע~.    | ον <i>)</i> |      |      |

|--------------------------------------------------|--------------------|--------------------------------------------------|------------|-------------|------|------|

| CHARACTERISTIC                                   | SYMBOL             | TEST CONDITION                                   | MIN.       | TYP.        | MAX. | UNIT |

| Operating Supply Voltage<br>Range                | v <sub>DD</sub>    | *                                                | 4.5        | 5.0         | 5.5  | V    |

| Memory Holding Voltage<br>Range                  | $v_{\mathrm{HD}}$  | Crystal oscillation stops*                       | 2.0        | ~           | 5.5  | ٧    |

| -V <sub>FL</sub> Applied Voltage<br>Range        | -V <sub>FL</sub>   | *                                                | -27        | ~           | 0    | V    |

| Operating Supply Current                         | IDD                | Normal operation (Output current exclude)        | _          | 1.0         | 3.0  | mA   |

| Memory Holding Supply                            | I <sub>HD1</sub>   | V <sub>DD</sub> =5V<br>Crystal oscillation stops | _          | 0.07        | 1.0  | μА   |

| Current                                          | I <sub>HD2</sub>   | V <sub>DD</sub> =2V<br>Crystal oscillation stops | <b>-</b> · | -           | 0.5  |      |

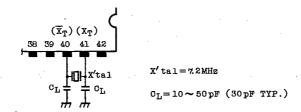

| Crystal Oscillation<br>Frequency                 | fXT                | *                                                | -          | 7.2         | 1.   | MHz  |

| KEY INPUT PORT (K <sub>0</sub> ~K <sub>3</sub> ) | *.                 |                                                  |            |             |      |      |

| High Level Input Voltage                         | $v_{\mathrm{IH1}}$ | -V <sub>FL</sub> =-27V                           | <b>-</b> 5 | ~           | 5    | V    |

| Low Level Input Voltage                          | V <sub>IL1</sub>   | -VFL=-27V                                        | -27        | ~           | -17  | V    |

| Pulldown Resistor                                | RIN1               | -V <sub>FL</sub> =-27V                           | 50         | 110         | 200  | kΩ   |

| DIGIT (D0~D6), SEGMENT (a                        | h) OUTPU           | T                                                |            |             |      |      |

| High Level Output Current (DIG.)                 | I <sub>OH1</sub>   | V <sub>OH</sub> =2V, -V <sub>FL</sub> =-27V      | -10        | -14         | -    | mA   |

| High Level Output Current (SEG.)                 | I <sub>OH2</sub>   | V <sub>OH</sub> =2V, -V <sub>FL</sub> =-27V      | -3.0       | -9.5        | _    | mA   |

| Output Off-leak Current                          | I <sub>OFF</sub>   | V <sub>OUT</sub> =-V <sub>FL</sub> =-27V         | _          | -           | -10  | μΑ   |

| Load Resistor                                    | 50                 | 110                                              | 200        | kΩ          |      |      |

| MUTE, REF OUTPUT, P1-2, P2-1                     | -4, P3-1~          | 4 PORT                                           |            |             |      |      |

| High Level Output Current | 1 <sub>0H3</sub> | VoH=4.0V              | -0.6 | -1.4 | 1 | mA      |

|---------------------------|------------------|-----------------------|------|------|---|---------|

| Low Level Output Current  | $I_{OL3}$        | V <sub>OL</sub> =1.0V | 0.6  | 1.4  | 1 | mA<br>~ |

| CLCCIRICAL CHARACIERISIICS (UNITESS OFFICEARISE SDECIFIED: 18=23 C. VNN=3) | ELECTRICAL CHARACTERISTICS | (Unless otherwise specified, | $Ta=25$ °C, $V_{DD}=5V$ ) |

|----------------------------------------------------------------------------|----------------------------|------------------------------|---------------------------|

|----------------------------------------------------------------------------|----------------------------|------------------------------|---------------------------|

| CHARACTERISTIC                         | SYMBOL             | TEST CONDITION        | MIN. | TYP. | MAX. | UNIT |

|----------------------------------------|--------------------|-----------------------|------|------|------|------|

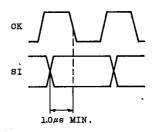

| SO, CK, STB OUTPUT                     |                    |                       |      |      | •    |      |

| High Level Output Current              | I <sub>OH</sub> 4  | V <sub>OH</sub> =4.0V | -1.0 | -2.0 | -    | mA   |

| Low Level Output Current               | I <sub>OL</sub> 4  | V <sub>OL</sub> =1.0V | 1.0  | 2.0  | -    | mA   |

| SI, INH, INT, P1-2, P2-1~4, I          | 23-1~4 POI         | RT                    |      |      |      |      |

| High Level Input Voltage<br>(TNH)      | $v_{\mathrm{IH2}}$ |                       | 4.3  | ~    | 5.0  | V    |

| Low Level Input Voltage (TNH)          | $v_{1L2}$          | :                     | 0    | 2    | 2.7  | v    |

| High Level Input Voltage<br>(Others)   | v <sub>IH3</sub>   |                       | 3.5  | ~    | 5.0  | V    |

| Low Level Input Voltage<br>(Others)    | V <sub>IL3</sub>   | ,                     | 0    | ?    | 1.5  | V    |

| High Level Input Current               | IIH                | V <sub>IH</sub> =5.0V | -    | -    | 1.0  | μА   |

| Low Level Input Current                | IIL                | V <sub>IL</sub> =0V   | _    | -    | -1.0 | μΑ   |

|                                        |                    |                       | •    |      |      |      |

| X <sub>T</sub> Input Feedback Resistor | R£                 |                       | 250  | 500  | 1000 | kΩ   |

Note: \* Marked items are guaranteed within a range of VDD=4.5~5.5V, Ta=-30~75°C.

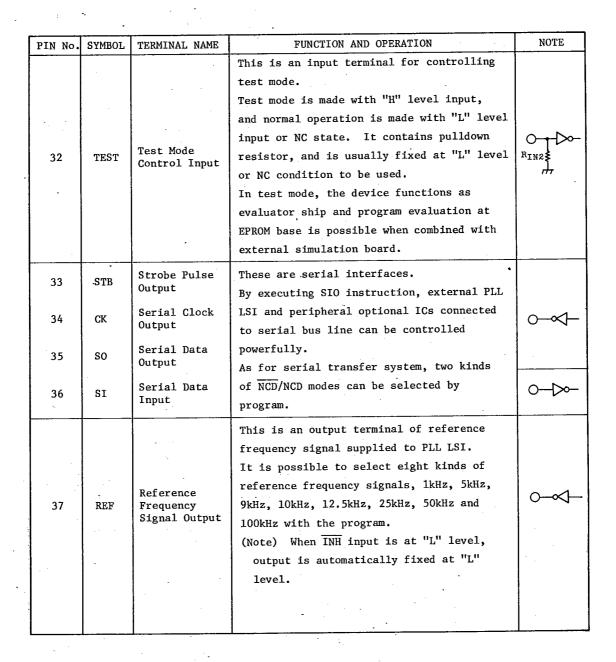

R<sub>IN2</sub>

TEST Terminal Pulldown

T-49-19-57

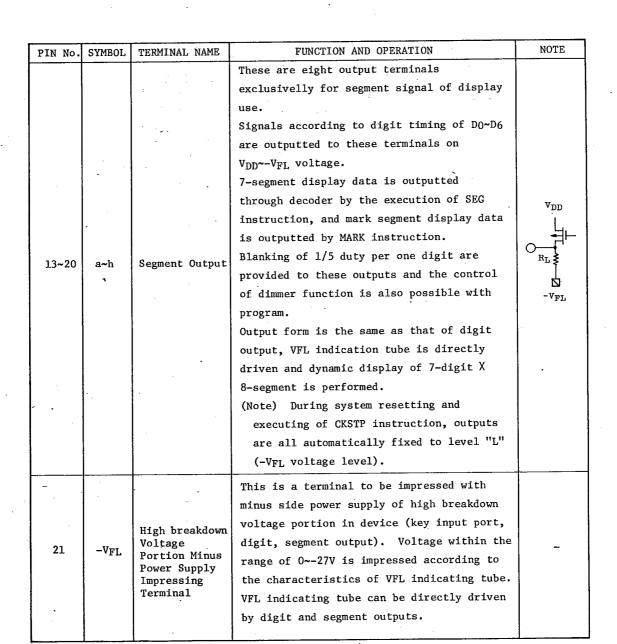

### FUNCTIONS OF EACH TERMINAL

| PIN No. | SYMBOL                         | TERMINAL NAME  | FUNCTION AND OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                     | NOTE             |

|---------|--------------------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 1       | GND                            | GND Terminal   | This is a ground terminal of device.                                                                                                                                                                                                                                                                                                                                                                                                                       | _ :              |

| 2~5     | к <sub>0</sub> ~к <sub>3</sub> | Key Input Port | They are 4-bit input ports exclusively for inputting key matrix. They have input latches in which input data at digit timing designated by program are read.  The read data is taken into data memory through executing KEY input instruction.  These are terminals of high withstand voltage structure containing pulldown resistor in which voltage VDD to -VFL can be input directly.  For key return timing signal source, use digit outputs of D0~D6. | R <sub>IN1</sub> |

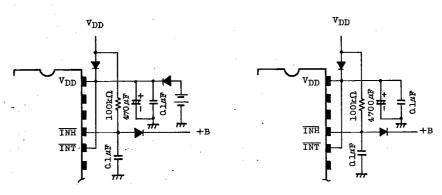

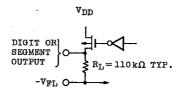

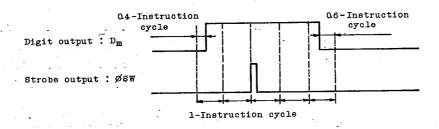

|         |                                |                | They are seven output terminals exclusively for digit signal of display use.  Signals of 1/10 duty are outputted to these terminals with cycle of 1.778ms on VDD~-VFL voltage level.  Output form is P-ch FET output of high breakdown voltage structured containing                                                                                                                                                                                       | vdd<br>L         |

| 6~12    | D0~D6                          | Digit Output   | load resistor and is able to drive VFL indication tube directly.  These terminals are used as key return timing signal outputs of key matrix.  (Note) During system resetting and executing of CKSTP instruction, outputs are all automatically fixed to level "L" (-VFL voltage level).                                                                                                                                                                   | R <sub>L</sub> & |

|         |                                |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                  |

T-49-19-57

|         | f                 | T                            |                                                                                                                                                                                                                                              |         |

|---------|-------------------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| PIN No. | SYMBOL            | TERMINAL NAME                | FUNCTION AND OPERATION                                                                                                                                                                                                                       | NOTE    |

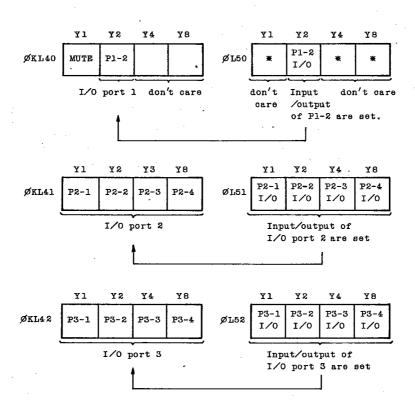

| 22~25   | P3-1<br>~<br>P3-4 | I/O Port 3                   | These are 4-bit I/O ports.  In these ports, input/output designation for every one bit can be made.  This designation is performed with the contents of internal port called PORT-3  I/O CONTROL.                                            | OUT     |

| 26~29   | P2-1<br>~<br>P2-4 | I/O Port 2                   | These are 4-bit I/O ports.  In these ports, input/output designation for every one bit can be made.  This designation is performed with the contents of internal port called PORT-2  I/O CONTROL.                                            | OUT     |

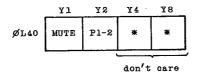

| 30      | P1-2              | I/O Port l                   | This is a 1-bit port. In this port, input/output designation is possible. This designation is performed with the contents of internal port called PORT-1 I/O CONTROL.                                                                        | OUT OUT |

| 31      | мите              | Muting Signal<br>Output Port | This is a 1-bit output port. It is usually used as the signal output of muting control. This port is arranged on the same port as I/O port 1.  (Note) When INH input is changing as "H" + "L", the output is automatically set to "H" level. | 0       |

|         |                   |                              |                                                                                                                                                                                                                                              |         |

T-49-19-57

| PIN No. | SYMBOL | TERMINAL NAME                           | FUNCTION AND OPERATION                                       | NOTE       |

|---------|--------|-----------------------------------------|--------------------------------------------------------------|------------|

|         |        |                                         | This is a system reset signal input                          |            |

| •       |        |                                         | terminal of the device.                                      | ÷          |

| -       |        |                                         | While $\overline{	ext{INT}}$ input is at "L" level, reset is |            |

|         |        |                                         | applied, and when it becomes "H" level,                      |            |

|         |        |                                         | the program starts from address zero.                        |            |

|         |        | ٠.,                                     | When the voltage, OV→4.5V, is supplied                       |            |

|         |        |                                         | to VDD terminal, system reset is applied                     |            |

| 38      | INT    | Initializing                            | usually (power-on reset), and so this                        | $\sim$     |

|         |        | Input                                   | terminal is fixed at "H" level to be used.                   |            |

|         |        | ·                                       | (Note) After system reset, all the I/O                       |            |

|         |        |                                         | ports are set at input mode, however,                        |            |

|         | ,      | ·                                       | since the contents of output port and                        |            |

|         |        |                                         | internal port are indefinite, perform                        |            |

|         |        | ·                                       | initialization with the program according                    | ,          |

|         |        | -                                       | to the necessity.                                            |            |

|         |        |                                         |                                                              |            |

|         |        | •                                       | This is a pulsing signal input port of                       |            |

|         | ·      |                                         | radio mode.                                                  |            |

|         | ,      | •                                       | It judges the mode as radio-on mode at                       |            |

|         |        |                                         | "H" level input and as radio off mode at                     |            |

|         | •      |                                         | "L" level input.                                             |            |

|         |        | ÷                                       | When this terminal is at "L" level, REF                      |            |

|         | •      |                                         | output is automatically fixed at "L" level.                  |            |

|         |        |                                         | Further, if CKSTP instruction is used in                     |            |

| 39      | INH    | Inhibit Input                           | the program, and this CKSTP instruction                      | $\bigcirc$ |

|         |        | e i i i i i i i i i i i i i i i i i i i | is executed while INH input is at "L"                        |            |

|         |        |                                         | level, the internal clock generator and                      |            |

|         |        | • . •                                   | CPU stop their operations and memory backup                  |            |

|         |        |                                         | condition can be realised at low current                     | ·          |

| •       |        | t e e                                   | consumption (1µA or less).                                   |            |

|         |        |                                         | At this time, all the output terminals                       |            |

|         |        |                                         | (indication output, output port, etc.) are                   |            |

| •       |        |                                         | automatically fixed at "L" level.                            |            |

| 1       |        | l                                       |                                                              | 1          |

:AUDIO DIGITAL IC:::

# TC9301AN

(Supplement)

CMOS input

CMOS input

CMOS input

CMOS input

Built-in pulldown resistor

High breakdown voltage

structured CMOS input (VSS=-VFL)

CMOS output

CMOS output

Clocked gate type

T-49-19-57

### EXPLANATION OF OPERATION

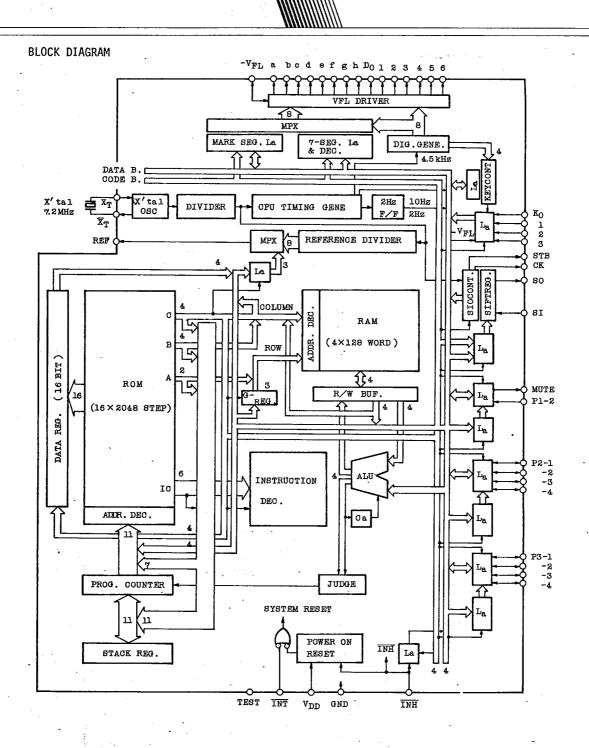

o cpu

CPU is composed of program counter, stack register, ALU, program memory, data memory, G-register, data resistor, carry F/F and judging circuit.

### 1. Program Counter (PC)

Program counter is the counter for addressing program memory (ROM), and is composed of 11-bit binary up counter.

This is cleared by system reset, and the program starts from address zero. Usually, increment is made one by one everytime one instruction is executed, but when the instruction of JUMP or CAL is executed, the address designated at operand of that instruction is loaded.

Further, when the instruction (AIS, SLT, TMT, RNS instructions, or others) having skip function is executed, two increments of program counter are made if the result is the condition to be skipped, and the succeeding instruction is skipped.

| MSB  | MSB     |     |     |     |     |     |     |     |     |                 |  |  |

|------|---------|-----|-----|-----|-----|-----|-----|-----|-----|-----------------|--|--|

| P010 | P09     | PC8 | PC7 | PC6 | PC5 | PC4 | PCg | PC2 | PC1 | PC <sub>O</sub> |  |  |

|      | ll bits |     |     |     |     |     |     |     |     |                 |  |  |

### 2. Stack Register (STACK)

This is a register composed of 1 X 11 bits. During the execution of sub-routine call instruction, the value obtained by adding +1 to the contents of program counter, namely return address, is loaded.

The contents of stack register are loaded on the program counter by the execution of return instructions (RN, RNS instructions).

This stack level is 1 level and nesting is 1 level.

#### 3. ALU

ALU has binary 4-bit parallel addition and subtraction, logical operation, comparison and plural bit judge functions.

This CPU has no accumulator, and all the operations directly treat the contents of data memory.

### 4. Program Memory (ROM)

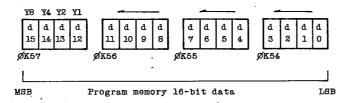

Program memory is composed of 16 bit  $\times$  2048 steps and stares the program. Applicable address range is 2048 steps of the address of 000H~7FFH.

Program memory has no concept of page or field, and JUMP and CAL instructions can be freely used among 2048 steps.

Optional address of program memory can be used as data area, and its contents, 16 bits, can be loaded on the data register by executing DAL instruction.

- (Note) Provide the data area in the program memory at the address outside the Program loop.

- (Note) In DAL instruction operation, the address of program memory can be designated as the data area becomes 1024 steps of 000H~3FFH.

### 5. Data Memory (RAM)

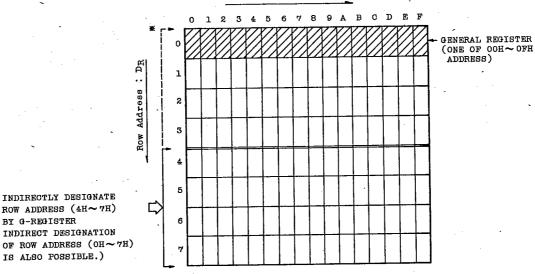

Data memory is composed of 4 bits X 128 words and is used for storing the data. These 128 words are expressed with row address (3 bits) and column address (4 bits). 64 words (row address=4H~7H address) in the data memory are the indirect addressing by G-register. For this reason, it is necessary in advance to designate row address by G-register when carrying out data processing within this territory.

$00H\sim0FH$  address in the data memory is called general register, and can be used only by designating column address (4 bits).

These 16 general registers can be used for operation and transfer between data memories. It can also be used as ordinary data memory.

- (Note) The column address (4 bits) to designate general register becomes general register number.

- (note) It is also possible to indirectly designate all the row addresses (OH~7H address) by G-register.

T-49-19-57

RAM ( 4 BITS  $\times$  128 WORDS )

G-register (G-REG.)

INDIRECTLY DESIGNATE ROW ADDRESS (4H~7H) BY G-REGISTER \*: INDIRECT DESIGNATION

IS ALSO POSSIBLE.)

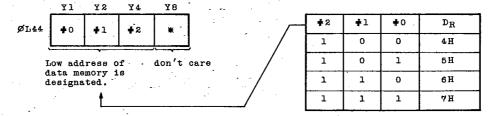

G-register is a 3-bit register for addressing 64-word row address (DR=4H~7H address) of data memory. Contents of this register are effective at executing MVGD instruction and MVGS instruction, and are not related with the execution of other instructions. This register is treated as one of the ports, and its contents are set by the execution of IO instruction among input/output instructions.

(→Refer to register port item 1. P. 50.)

7. Data Register (DATA REG.)

This is a register composed of 1 X 16 bits. In this register, 16-bit data of optional address among program memory of 000H~3FFH is loaded at the execution of DAL instruction. This register is treated as one of the ports, and the contents are read in the data memory in 4-bit unit when the KEY instruction among input/ output instructions is executed.

(→ Refer to register port item 2. P. 51.)

This is set when carry or borrow is produced as the result of executing the operational instruction, and is reset when it is not produced.

(Note) In all instruction operation, the contents of carry F/F always changes for the results.

### 9. Judge Circuit (J)

When skip function instruction is executed, this circuit judges its skip condition. When skip condition is satisfied, this circuit makes two steps increment of program counter, and skips the succeeding instruction.

29 kinds of instructions are available with abundant skip functions.

(→ Refer to \*marked instructions in item 11, list of explanations of instruction function and operation.)

### 10. Instruction Set List

62 kinds of instructions in all consisting of 1-word instruction are available. These instructions are expressed with 6-bit instruction code.

| HIGHER RANK<br>LOWER 2 BI<br>RANK 4 BITS | ITS | . 0        | 01        | 10         | 11          |

|------------------------------------------|-----|------------|-----------|------------|-------------|

| 0000                                     | 0   | AI M, I    | AD r, M   | LD r, M    | SLTI M, I   |

| 0001                                     | 1   | AIS M, I   | ADS r, M  | ST M, r    | SGEI M, I   |

| 0010                                     | 2   | AIN M, I   | ADN r, M  | MVRD r, M  | SEQI M, I   |

| 0011                                     | 3   | SI M, I    | SU r, M   | MVRS M, r  | SNEI M, I   |

| 0100                                     | 4   | SIS M, I   | SUS r, M  | MVSR M1,M2 | SLT r, M    |

| 0101                                     | 5   | SIN M, I   | SUN r, M  | MVIM M, I  | SGE r, M    |

| 0110                                     | 6   | CAL ADDR1  | ORR r, M  | MVGD r, M  | SEQ r, M    |

| 0111                                     | 7   | ·          | ANDR r, M | MVGS M, r  | SNE r, M    |

| 1000                                     | 8   | AIC M, I   | AC r, M   | PLL M, C   | TMTR r, M   |

| 1001                                     | 9   | AICS M, I  | ACS 'r, M | SEG M, C   | TMFR r, M   |

| 1010                                     | A   | AICN M, I  | ACN r, M  | MARK M, C  | TMT M, N    |

| 1011                                     | В   | SIB M, I   | SB r, M   | IO M, C    | TMF M, N    |

| 1100                                     | С   | SIBS M, I  | SBS r, M  | KEY M, C   | DAL ADDR2,r |

| 1101                                     | D   | SIBN M, I  | SBN r, M  | S10 M, C   | WAIT        |

| 1110                                     | E   | JUMP ADDR1 | ORIM M, I | RN         | CKSTP       |

| 1111                                     | F   | JUL INDIKI | ANIM M, I | RNS        | NOOP        |

11. Explanation List of Function and Operation of Instructions (Explanation of Symbols in the List)

M : data memory address

Normally, one of OOH~3FH addresses in data memory.

r : General register

One of OOH~OFH addresses in data memory.

PC: Program counter (11 bits)

STACK: Stack register (11 bits)

G : G-register

(3 bits)

Data: Data register (16 bits)

I : Immediate data (4 bits)

N: Bit position (4 bits)

- : ALL "0"

C: Code No. of port (4 bits).

CN: Lower rank 3 bits of port code No.

RN: General register No. (4 bits)

ADDR1: Program memory address in Page 0 or 1.(10 bits)

ADDR2: Higher rank 6 bits of program memory address in page 0.

Ca : Carry

b : Borrow

PLL: Port treated at execution of PLL instruction

SEG: Port treated at execution of SEG instruction

MARK: Port treated at execution of MARK instruction

IO: Port treated at execution of IO instruction.

KEY: Port treated at execution of KEY instruction

SIO: Port treated at execution of SIO instruction

( ) : Contents of register or data memory

[ ]C: Contents of port indicated with code No. C (4 bits)

[ ] : Contents of data memory indicated with contents of register or data memory

[ ]P : Contents of program memory (16 bits)

IC: Instruction code (6 bits)

\*: Instruction with skip function

DC: Data memory column address (4 bits)

DR : Data memory row address (2 bits)

(Note) Address 000H~3FFH of program memory : Page 0 area

(Note) Address 400H~7FFH of program memory: Page 1 area

=AUDIO DIGITAL IC===

# TOSHIBA, ELECTRONIC DE DE

| _                          |                          |           |                                                                                                         |        |                                                                                    |                                                                                        |                                         |                                                             |                                                                 |                                   |                                                    |                                                        |                                           |                                                               |

|----------------------------|--------------------------|-----------|---------------------------------------------------------------------------------------------------------|--------|------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-----------------------------------------|-------------------------------------------------------------|-----------------------------------------------------------------|-----------------------------------|----------------------------------------------------|--------------------------------------------------------|-------------------------------------------|---------------------------------------------------------------|

| MACHINE LANGUAGE (16 bits) |                          | Ü         | (4 bits)                                                                                                | H      | ı                                                                                  | н                                                                                      | I                                       | I                                                           | ·                                                               | RN                                | RN                                                 | RN                                                     | RN                                        | RN                                                            |

|                            |                          | В         | (2 bits) (4 bits)                                                                                       | DQ ·   | DC                                                                                 | DC                                                                                     | DC                                      | . DC                                                        | . DC                                                            | DC                                | DС                                                 | DC                                                     | DC                                        | DC                                                            |

|                            |                          | A         | (2 bits)                                                                                                | DR     | DR                                                                                 | JR.                                                                                    | DR                                      | DR ,                                                        | DR                                                              | DR                                | DR                                                 | DR                                                     | DR                                        | DR                                                            |

|                            |                          | ıc        | (6 bits)                                                                                                | 000000 | 000001                                                                             | 000010                                                                                 | 001000                                  | 001001                                                      | 001010                                                          | 000000                            | 010001                                             | 010010                                                 | 011000                                    | 011001                                                        |

|                            | EXPLANATION OF OPERATION |           | EXPLANATION OF OPERATION                                                                                |        | M←(M) + I<br>Skip if carry                                                         | $M \leftarrow (M) + I$<br>Skip if not carry                                            | M ← (M) + I + ca                        | $M \leftarrow (M) + I + ca$<br>Skip if carry                | $M \leftarrow (M) + I + ca$<br>Skip if not carry                | $r \leftarrow (r) + (M)$          | r←(r) + (M)<br>Skip if carry                       | $r \leftarrow (r) + (M)$<br>Skip if not carry          | $r \leftarrow (r) + (M) + ca$             | $r \leftarrow (r) + (M) + ca$<br>Skip if carry                |

|                            | EXPLANATION OF FUNCTION  |           | EXPLANATION OF FUNCTION  Add immediate data to memory  Add immediate data to memory, then skip if carry |        | Add immediate data to memory, $M \leftarrow (M) + I$ then skip if carry Skip if ca | Add immediate data to memory, $M \leftarrow (M) + I$ then skip if not carry Skip if no | Add immediate data to memory with carry | Add immediate data to memory with carry, then skip if carry | Add immediate data to memory with carry, then skip if not carry | Add memory to general<br>register | Add memory to general register, then skip if carry | Add memory to general register, then skip if not carry | Add memory to general register with carry | Add memory to general register with carry, then skip if carry |

|                            | NO                       | ICLI<br>L | EON<br>SKI                                                                                              |        | *                                                                                  | *                                                                                      |                                         | *                                                           | *                                                               |                                   | *                                                  | *                                                      |                                           | *                                                             |

|                            | -                        | DINC      | ,                                                                                                       | M, I   | M,I                                                                                | M, I                                                                                   | и, п                                    | Ι.Μ                                                         | M, I                                                            | r,M                               | ADS r,M                                            | т,М                                                    | г,М                                       | r,M                                                           |

|                            |                          | MNEMONIC  |                                                                                                         | AI     | AIS                                                                                | AIN                                                                                    | AIC M,I                                 | AICS M, I                                                   | AICN M,I                                                        | AD                                | ADS                                                | ADN                                                    | AC                                        | ACS                                                           |

| ADDITION INSTRUCTIONS Gr.  |                          |           |                                                                                                         |        |                                                                                    |                                                                                        |                                         |                                                             |                                                                 |                                   |                                                    |                                                        |                                           |                                                               |

T-49-19-57

|                  | lts)                     | ນ        | (4 bits)                                                                                                                                               | RN                                     | I                                                        | H                                                            | н                                              | н                                                                    | п                                                                              | H                                                | RN                                                         | RN                                                                    | RN                                             |

|------------------|--------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|----------------------------------------------------------|--------------------------------------------------------------|------------------------------------------------|----------------------------------------------------------------------|--------------------------------------------------------------------------------|--------------------------------------------------|------------------------------------------------------------|-----------------------------------------------------------------------|------------------------------------------------|

|                  | GE (16 bits)             | В        | (4 bits)                                                                                                                                               | DC                                     | ၁၉                                                       | DC                                                           | DC                                             | DC                                                                   | DC ,                                                                           | ЭG                                               | DC                                                         | DC                                                                    | DC                                             |

| MACHINE LANGUAGE |                          | A        | (2 bits)                                                                                                                                               | DR                                     | DR                                                       | DR                                                           | DR                                             | ĎR ,                                                                 | DR                                                                             | DR                                               | DR                                                         | DR                                                                    | DR                                             |

| 1                | MACHII                   | IC       | (6 bits)                                                                                                                                               | 011010                                 | 000011                                                   | 000100                                                       | 000101                                         | 001011                                                               | 001100                                                                         | 001101                                           | 010011                                                     | 010100                                                                | 010101                                         |

| -                | EXPLANATION OF OPERATION |          |                                                                                                                                                        | r ←(r) + (M) + ca<br>Skip if not carry | M ← (M) - I                                              | M←(M) - I<br>Skip if borrow                                  | M ← (M) - I<br>Skip if not borrow              | $M \leftarrow (M) - I - b$                                           | $M \leftarrow (M) - I - b$<br>Skip if borrow                                   | $M \leftarrow (M) - I - b$<br>Skip if not borrow | $\mathbf{r} \leftarrow (\mathbf{r}) - (\mathbf{M})$        | $\mathbf{r} \leftarrow (\mathbf{r}) - (\mathbf{M})$<br>Skip if borrow | $x \leftarrow (x) - (M)$<br>Skip if not borrow |

| -                | EXPLANATION OF FUNCTION  |          | EXPLANATION OF FUNCTION  Add memory to general register with carry, then skip if not carry Subtract immediate data from memory Subtract immediate data |                                        | Subtract immediate data from memory, then skip if borrow | Subtract immediate data from memory, then skip if not borrow | Subtract immediat data from memory with borrow | Subtract immediate data from memory with borrow, then skip if borrow | Subtract immediate data<br>from memory with borrow,<br>then skip if not borrow | Subtract memory from<br>general register         | Subtract memory from general register, then skip if borrow | Subtract memory from general register, then skip if not borrow        |                                                |

|                  |                          |          |                                                                                                                                                        | *                                      |                                                          | *                                                            | *                                              |                                                                      | *                                                                              | *                                                |                                                            | *                                                                     | *                                              |

|                  |                          | DINC     |                                                                                                                                                        | г,М                                    | п, и                                                     | I,M                                                          | I,M                                            | м, і                                                                 | SIBS M,I                                                                       | SIBN M,I                                         | r,M                                                        | π,π                                                                   | Μ, π                                           |

|                  |                          | MNEMONIC |                                                                                                                                                        | ACN                                    | IS                                                       | SIS                                                          | SIN                                            | SIB                                                                  | SIBS                                                                           | SIBN                                             | SU                                                         | SUS                                                                   | SUN                                            |

|                  |                          | .TS      | CL<br>IN                                                                                                                                               | 1                                      |                                                          | · :_ :                                                       | N                                              | OITOU                                                                | HISNI NO                                                                       | TTSASTE                                          | ıs                                                         |                                                                       |                                                |

|   | its)             | Ü                       | (4 bits)   | RN                                                               | RN                                                                     | RN                                                                         | н                                                                                                                                                                                                                                             | н                                                               | I                                         | I                                             | RN                                              | RN                                                                | RN                                          | RN                                                 |  |  |

|---|------------------|-------------------------|------------|------------------------------------------------------------------|------------------------------------------------------------------------|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|-------------------------------------------|-----------------------------------------------|-------------------------------------------------|-------------------------------------------------------------------|---------------------------------------------|----------------------------------------------------|--|--|

|   | AGE (16 bits)    | В                       | (4 bits)   | . DC                                                             | Ŋ                                                                      | DG<br>,                                                                    | DC                                                                                                                                                                                                                                            | DС                                                              | DC                                        | DC                                            | DC                                              | DC .                                                              | ,<br>DQ                                     | DC                                                 |  |  |

|   | MACHINE LANGUAGE | Ą                       | (2 bits)   | DR                                                               | DR                                                                     | JR                                                                         | DR                                                                                                                                                                                                                                            | DR                                                              | DR                                        | DR                                            | DR                                              | DR                                                                | DR                                          | DR                                                 |  |  |

|   | MACHI            | IC                      | (6 bits)   | 011011                                                           | 011100                                                                 | 011101                                                                     | 110000                                                                                                                                                                                                                                        | 110001                                                          | 110010                                    | 110011                                        | 110100                                          | 110101                                                            | 110110                                      | 110111                                             |  |  |

|   | EXPLANATION OF   | OPERATION               |            | $\mathbf{r} \leftarrow (\mathbf{r}) - (\mathbf{M}) - \mathbf{b}$ | $r \leftarrow (r) - (M) - b$<br>Skip if borrow                         | $r \leftarrow (r) - (M) - b$<br>Skip if not borrow                         | Skip if (M) <i< td=""><td>Skip if (M)≥I</td><td>Skip if (M)=I</td><td>Skip if (M)≒I</td><td>Skip if <math>(r) &lt; (M)</math></td><td>Skip if <math>(r) \ge (M)</math></td><td>Skip if <math>(r)=(M)</math></td><td>Skip if (r)≒(M)</td></i<> | Skip if (M)≥I                                                   | Skip if (M)=I                             | Skip if (M)≒I                                 | Skip if $(r) < (M)$                             | Skip if $(r) \ge (M)$                                             | Skip if $(r)=(M)$                           | Skip if (r)≒(M)                                    |  |  |

|   | -                | EXPLANATION OF FUNCTION |            | Subtract memory from general register with borrow                | Subtract memory from general register with borrow, then skip if borrow | Subtract memory from general register with borrow, then skip if not borrow | Skip if memory is less than immediate data                                                                                                                                                                                                    | Skip if memory is greater<br>than or equal to immediate<br>data | Skip if memory is equal to immediate data | Skip if memory is not equal to immediate data | Skip if general register<br>is less than memory | Skip if general register<br>is greater than or equal<br>to memory | Skip if general register is equal to memory | Skip if general register<br>is not equal to memory |  |  |

| Ī | NO               | CLI                     | LON<br>SKI |                                                                  | *                                                                      | *                                                                          | *                                                                                                                                                                                                                                             | *                                                               | *                                         | *                                             | *                                               | *                                                                 | *                                           | *                                                  |  |  |

|   |                  | MNEMONIC                | -          | SB r,M                                                           | SBS r,M                                                                | SBN r,M                                                                    | SLTI M,I                                                                                                                                                                                                                                      | SGEI M, I                                                       | SEQI M, I                                 | SNEI M,I                                      | SLT r,M                                         | SGE r,M                                                           | SEQ r,M                                     | SNE r,M                                            |  |  |

|   |                  |                         | 19<br>IN   | 1                                                                | TRACTION<br>TRUCTION                                                   | SNI                                                                        |                                                                                                                                                                                                                                               | COMPARISON INSTRUCTION                                          |                                           |                                               |                                                 |                                                                   |                                             |                                                    |  |  |

T-49-19-57

|     | its)             | υ                       | (4 bits)          | ,<br>RN                              | RN                                  | RN                                                                                    | RN                                                                               | DC2                                      | I                             | RN                                                                                    | RN                                                                              |

|-----|------------------|-------------------------|-------------------|--------------------------------------|-------------------------------------|---------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|------------------------------------------|-------------------------------|---------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| - 1 | AGE (16 bits)    | щ                       | (2 bits) (4 bits) | DC                                   | DC                                  | DC                                                                                    | DC                                                                               | DC1                                      | DC                            | )C                                                                                    | DC                                                                              |

|     | MACHINE LANGUAGE | ¥                       | (2 bits)          | DR                                   | DR                                  | DR                                                                                    | Æ                                                                                | DR.                                      | DR                            | DR                                                                                    | DR                                                                              |

|     | MACHI            | ΟI                      | (6 bits)          | 100000                               | 100001                              | 1.00010                                                                               | 100011                                                                           | 100100                                   | 100101                        | 100110                                                                                | 100111                                                                          |

|     | EXPLANATION OF   | OPERATION               |                   | $\mathbf{r} \leftarrow (\mathtt{M})$ | M ←(r)                              | [DR, (r)] ←(M)                                                                        | $M \leftarrow [DR, (r)]$                                                         | $(D_R, D_{C1}) \leftarrow (D_R, D_{C2})$ | M←I                           | $[(G),(\tau)]\leftarrow(M)$                                                           | $M \leftarrow [(G), (\pi)]$                                                     |

|     |                  | EXPLANATION OF FUNCTION | -                 | Load memory to general register      | Store general register<br>to memory | Move memory to destination<br>memory referring to general<br>register in the same row | Move source memory referring<br>to general register to<br>memory in the same row | Move memory to memory in the same row    | Move immediate data to memory | Move memory to destination<br>memory referring to G-<br>register and general register | Move source memory referring<br>to G-register and general<br>register to memory |

|     | NO               | CLI                     | EON<br>SKI        |                                      |                                     |                                                                                       |                                                                                  |                                          |                               |                                                                                       |                                                                                 |

|     | MNEMONIC         |                         | LD r,M            | ST M,r                               | MVRD r,M                            | MVRS M,r                                                                              | MVSR<br>M1,M2                                                                    | MVIM M,I                                 | MVGD r,M                      | MVGS M,r                                                                              |                                                                                 |

| Į   |                  | .T2                     | er<br>In          |                                      |                                     | NC                                                                                    | INSTRUCTIO                                                                       | NSEER                                    | TRAI                          |                                                                                       |                                                                                 |

:AUDIO DIGITAL IC:::

# TOSHIBA: ELECTRONIC DE TOSHIBA: ELECTRONIC DE

| - G              | υ                         | (4 bits)          | Š                                | CN                                       | CN                               | CM                                       | CN                                | CN                                        | CN                              | ĊN                                      | CN                            | CN                                       | CN                                                  | CN                                                          |

|------------------|---------------------------|-------------------|----------------------------------|------------------------------------------|----------------------------------|------------------------------------------|-----------------------------------|-------------------------------------------|---------------------------------|-----------------------------------------|-------------------------------|------------------------------------------|-----------------------------------------------------|-------------------------------------------------------------|

| ايتا             |                           | Č                 | 0                                | н                                        | 0                                | 1                                        | 0                                 | 1                                         | 0                               | $\dashv$                                | 0                             | ,                                        | 0                                                   | 1                                                           |

| AGE (16 bits)    | Д                         | (2 bits) (4 bits) | DС                               | DС                                       | DC                               | DC                                       | DC .                              | ЭC                                        | ЭC                              | DC                                      | DC                            | · DC                                     | DC                                                  | DC                                                          |

| MACHINE LANGUAGE | A                         | (2 bits)          | DR                               | DR                                       | DR                               | DR                                       | DR                                | DR                                        | DR                              | DR                                      | DR                            | DR                                       | DR                                                  | DR                                                          |

| MACHI            | IC                        | (6 bits)          | 000101                           | 000                                      | 100101                           | 100101                                   | 010101                            |                                           | 10101                           | 1<br>1<br>1<br>1<br>1                   | 101100                        |                                          | 101101                                              |                                                             |

| EXPLANATION OF   | OPERATION                 |                   | M ←[PLL]C                        | [PLL]C ←(M)                              | M ← [SEG]C                       | [SEG] <sub>C</sub> ←(M)                  | M ←[MARK]C                        | $[MARK]_C \leftarrow (M)$                 | M ←[10]C                        | [I0]C ← (M)                             | M ←[KEY]C                     | [KEY]C ←(M)                              | D[OIS]→ M                                           | [SIO]C ← (M)                                                |

|                  | , EXPLANATION OF FUNCTION |                   | Input PLL port data to<br>memory | Output contents of memory<br>to PLL port | Input SEG port data to<br>memory | Output contents of memory<br>to SEG port | Input MARK port data to<br>memory | Output contents of memory<br>to MARK port | Input IO port data to<br>memory | Output contents of memory<br>to 10 port | Input KEY port data to memory | Output contents of memory<br>to KEY port | Serial input port data of external device to memory | Serial output contents of memory to port of external device |

| NO               | ACL)                      | ENI<br>SKI        |                                  |                                          |                                  |                                          |                                   |                                           |                                 |                                         |                               |                                          |                                                     |                                                             |

|                  | MNEMONIC                  |                   |                                  | ) fi                                     | v X                              | ) fit                                    | MARK M,C                          |                                           | IO M, C                         |                                         | X KY                          |                                          | STO M.C                                             | 1                                                           |

|                  | TSI                       | II<br>Gi          |                                  |                                          |                                  |                                          | CTION                             | UNTENI                                    | TUTTU                           | NPUT/O                                  | II                            |                                          |                                                     |                                                             |

# TOSHIBA TELECTRONIC TC9301AN

T-49-19-57

|                  |                         |                   | <del>-</del>                                 |                                                          |                                            |                                             |                                                                                              |                                                                                               |                                                                  |                                                                   |

|------------------|-------------------------|-------------------|----------------------------------------------|----------------------------------------------------------|--------------------------------------------|---------------------------------------------|----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|------------------------------------------------------------------|-------------------------------------------------------------------|

| its)             | U                       | (4 bits)          | RN                                           | RN                                                       | н                                          | П                                           | RN                                                                                           | $R_{ m N}$                                                                                    | N                                                                | Z                                                                 |

| AGE (16 bits)    | В                       | (2 bits) (4 bits) | DС                                           | DC                                                       | DC                                         | DC                                          | DC                                                                                           | DC                                                                                            | DC                                                               | DC                                                                |

| MACHINE LANGUAGE | A                       | (2 bits)          | DR                                           | DR                                                       | DR .                                       | DR                                          | D <sub>R</sub>                                                                               | DR                                                                                            | DR                                                               | DR                                                                |

| MACHI            | IC                      | (6 bits)          | 01010                                        | 010111                                                   | 011110                                     | 011111                                      | 111000                                                                                       | 111001                                                                                        | 111010                                                           | 111011                                                            |

| EXPLANATION OF   | OPERATION               |                   | $r \leftarrow (r) \lor (M)$                  | $\mathtt{r} \leftarrow (\mathtt{r}) \wedge (\mathtt{M})$ | $M \leftarrow (M) \lor I$                  | I ∨ (W) → W                                 | Skip if<br>r[N(M)]=all "l"                                                                   | Skip if<br>r[N(M)]=all "0"                                                                    | Skip if M(N)=all "l"                                             | Skip if M(N)=all "0"                                              |

|                  | EXPLANATION OF FUNCTION |                   | Logical OR of general<br>register and memory | Logical AND of general register and memory               | Logical OR of memory<br>and immediate data | Logical AND of memory<br>and immediate data | Test general register bits<br>by memory bits, then skip<br>if all bits specified are<br>true | Test general register bits<br>by memory bits, then skip<br>if all bits specified are<br>false | Test memory bits, then skip<br>if all bits specified are<br>true | Test memory bits, then skip<br>if all bits specified are<br>falsē |

| NO               | ICLI<br>Lb              | ENI<br>SKI        |                                              |                                                          |                                            |                                             | *                                                                                            | *                                                                                             | *                                                                | *                                                                 |

| -                | MNEMONIC                | ,                 | ORR r,M                                      | ANDR r,M                                                 | ORIM M, I                                  | AMIM M, I                                   | TMTR r,M                                                                                     | TMFR r,M                                                                                      | TMT M,N                                                          | TMF M,N                                                           |

| INST.            |                         | اد حد خد          | CTION<br>CTION                               | INSTRU                                                   |                                            |                                             | INSTRUCTI                                                                                    | L                                                                                             | L                                                                |                                                                   |

AUDIO DIGITAL IC

| its)             | C<br>(4 bits)           | (0                        |                           | ı                       | 1                                               | its)                                       |                                            | RN                                             | ı                                          | <b>!</b>                           | l            |

|------------------|-------------------------|---------------------------|---------------------------|-------------------------|-------------------------------------------------|--------------------------------------------|--------------------------------------------|------------------------------------------------|--------------------------------------------|------------------------------------|--------------|

| AGE (16 bits)    | A B (2 bits) (4 bits)   | (10 14+6)                 |                           | ı                       | 1                                               | ADDR1 (10 bits)                            | •                                          | ADDR2 (6 bits)                                 | ı                                          | 1                                  | l            |

| MACHINE LANGUAGE | A<br>(2 bits)           | 4                         | awa a                     | 1                       | 1                                               | AD                                         |                                            | ADDR2                                          | ı                                          | <br>I                              | 1            |