查询TC94A48FG供应商 **TOSHIBA**

捷多邦,专业PCB打样工厂

TC94A48FG

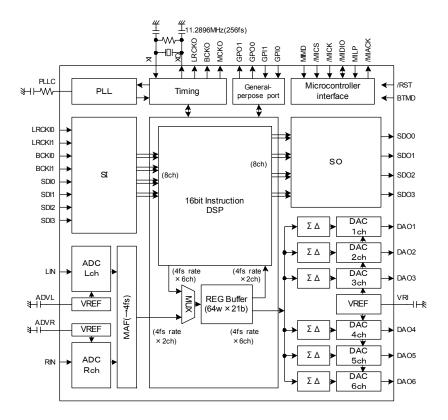

Single-chip Audio Digital Signal Processor

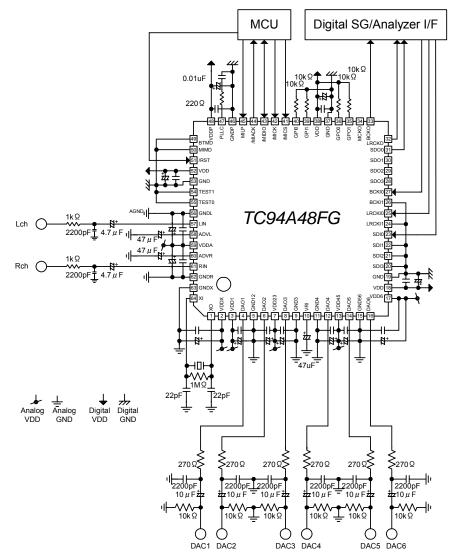

The TC94A48FG is a single-chip audio Digital Signal Processor, incorporating two channels AD converter and six channels DA converter.

It can realize many applications, including sound field control, such as hall simulation, digital filters, such as equalizers, surround sound, base boost and more.

:24 bits

### Features

- Incorporates a 1-bit Σ-Δ AD converter (2 channels). THD+N: -78 dB (typ.), S/N ratio: 92 dB (typ.)

- Incorporates a multi-bit Σ-Δ DA converter (6 channels). THD+N: -88 dB (typ.), S/N ratio: 98 dB (typ.)

- Digital input/output ports

Four input ports (8 channels)

Four output ports (8 channels)

• The DSP block specifications are as follows:

Data bus Multiplier/adder Accumulator Program ROM Program RAM XRAM YRAM CROM

51 bits (sign extension: 4 bits)

3072 words × 16 bits

1024 words × 16 bits

4096 words × 24 bits

1024 words × 24 bits

$:24 \text{ bits} \times 24 \text{ bits} + 51 \text{ bits} \rightarrow 51 \text{ bits}$

- $: 1024 \text{ words} \times 24 \text{ bits}$

- The microcontroller interface can be selected between serial mode and I<sup>2</sup>C bus mode.

- Operating supply voltage: 3.3 V (some pins accept 5 V)

- CMOS silicon structure supports high speed.

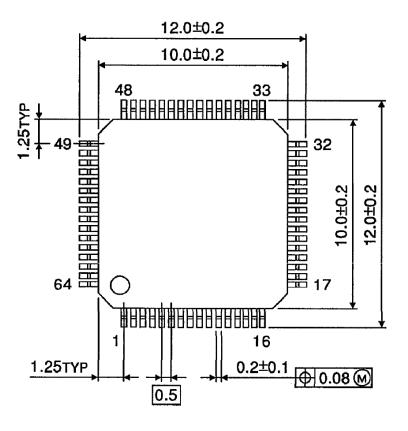

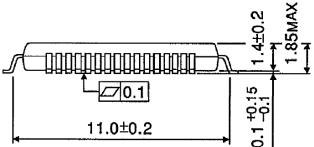

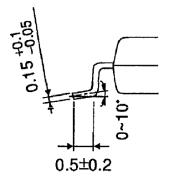

- Th<mark>e packa</mark>ge is a 64-pin LQFP (0.5-mm pitch) package.

,24小时加急出货

TC94A48FG

Weight: 0.4 g (typ.)

### **Block Diagram**

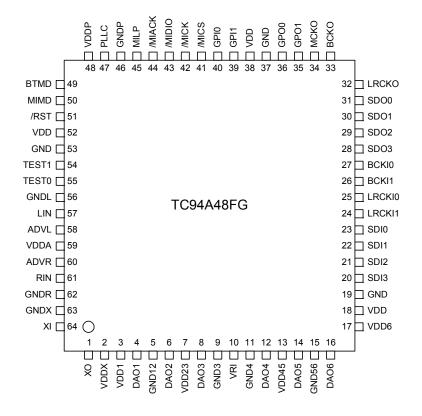

### **Pin Layout**

## **Pin Function**

| Pin<br>No. | Symbol            | I/O | Function                                                                                            | Remarks                      |

|------------|-------------------|-----|-----------------------------------------------------------------------------------------------------|------------------------------|

| 1          | ХО                | 0   | Crystal oscillator connecting or clock output pin                                                   |                              |

| 2          | V <sub>DDX</sub>  | -   | Power pin for oscillator circuit                                                                    |                              |

| 3          | V <sub>DD1</sub>  | _   | Analog power pin for DAC1                                                                           |                              |

| 4          | DAO1              | 0   | DAC1 signal output pin                                                                              |                              |

| 5          | GND12             | _   | Analog ground pin for DAC1/2                                                                        |                              |

|            |                   | 0   |                                                                                                     |                              |

| 6          | DAO2              | 0   | DAC2 signal output pin                                                                              |                              |

| 7          | V <sub>DD23</sub> | -   | Analog power pin for DAC2/3                                                                         |                              |

| 8          | DAO3              | 0   | DAC3 signal output pin                                                                              |                              |

| 9          | GND3              | —   | Analog power pin for DAC3                                                                           |                              |

| 10         | VRI               | Т   | Reference voltage pin for DAC                                                                       |                              |

| 11         | GND4              | -   | Analog ground pin for DAC4                                                                          |                              |

| 12         | DAO4              | 0   | DAC4 signal output pin                                                                              |                              |

| 13         | V <sub>DD45</sub> | _   | Analog power pin for DAC4/5                                                                         |                              |

| 14         | DAO5              | 0   | DAC5 signal output pin                                                                              |                              |

| 15         | GND56             | _   | Analog ground pin for DAC5/6                                                                        |                              |

|            |                   | _   |                                                                                                     |                              |

| 16         | DAO6              | 0   | DAC6 signal output pin                                                                              |                              |

| 17         | V <sub>DD6</sub>  | -   | Analog power pin for DAC6                                                                           |                              |

| 18         | V <sub>DD</sub>   | -   | Digital power pin                                                                                   |                              |

| 19         | GND               | -   | Digital ground pin                                                                                  |                              |

| 20         | SDI3              | Т   | Audio serial data input pin 3                                                                       | Schmitt input                |

|            |                   |     | It connects to GND or $V_{DD}$ pins when if it is unused this pin.<br>Audio serial data input pin 2 | 5V tolerant<br>Schmitt input |

| 21         | SDI2              | I   | It connects to GND or $V_{DD}$ pins when if it is unused this pin.                                  | 5V tolerant                  |

| 22         | SDI1              | 1   | Audio serial data input pin 1                                                                       | Schmitt input                |

|            | OBIT              |     | It connects to GND or $V_{DD}$ pins when if it is unused this pin.                                  | 5V tolerant                  |

| 23         | SDI0              | Т   | Audio serial data input pin 0<br>It connects to GND or $V_{DD}$ pins when if it is unused this pin. | Schmitt input<br>5V tolerant |

|            |                   |     | LR clock input pin 1                                                                                | Schmitt input                |

| 24         | LRCKI1            | I   | It connects to GND or V <sub>DD</sub> pins when if it is unused this pin.                           | 5V tolerant                  |

| 25         | LRCKI0            | I   | LR clock input pin 0                                                                                | Schmitt input                |

|            |                   |     | It connects to GND or V <sub>DD</sub> pins when if it is unused this pin.                           | 5V tolerant                  |

| 26         | BCKI1             | Т   | Bit clock input pin 1 It connects to GND or $V_{DD}$ pins when if it is unused this pin.            | Schmitt input<br>5V tolerant |

| 27         | BCKI0             | 1   | Bit clock input pin 0                                                                               | Schmitt input                |

| 27         | BCKIU             | -   | It connects to GND or $V_{DD}$ pins when if it is unused this pin.                                  | 5V tolerant                  |

| 28         | SDO3              | 0   | Audio serial data output pin 3<br>It leaves to open when if it is unused.                           | Push-pull output             |

|            |                   | _   | Audio serial data output pin 2                                                                      |                              |

| 29         | SDO2              | 0   | It leaves to open when if it is unused.                                                             | Push-pull output             |

| 30         | SDO1              | о   | Audio serial data output pin 1                                                                      | Push-pull output             |

|            |                   |     | It leaves to open when if it is unused.<br>Audio serial data output pin 0                           |                              |

| 31         | SDO0              | 0   | It leaves to open when if it is unused.                                                             | Push-pull output             |

| 32         | LRCKO             | 0   | LR clock output pin                                                                                 | Push-pull output             |

| 52         | LIVOKO            |     | It leaves to open when if it is unused.                                                             |                              |

| 33         | BCKO              | 0   | Bit clock output pin<br>It leaves to open when if it is unused.                                     | Push-pull output             |

|            |                   | 1   |                                                                                                     | I                            |

## TC94A48FG

| Pin<br>No. | Symbol           | I/O | Function                                                                                                                                     | Remarks                                                          |

|------------|------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|

| 34         | МСКО             | 0   | System clock output pin<br>It leaves to open when if it is unused.                                                                           | Push-pull output                                                 |

| 35         | GPO1             | 0   | General-purpose output pin 1<br>It leaves to open when if it is unused.                                                                      | Open-drain output<br>5V tolerant                                 |

| 36         | GPO0             | 0   | General-purpose output pin 0<br>It leaves to open when if it is unused.                                                                      | Open-drain output<br>5V tolerant                                 |

| 37         | GND              | _   | Digital ground pin                                                                                                                           |                                                                  |

| 38         | V <sub>DD</sub>  | _   | Digital power pin                                                                                                                            |                                                                  |

| 39         | GPI1             | I   | General-purpose input pin 1 It connects to GND or $V_{\text{DD}}$ pins when if it is unused this pin.                                        | Schmitt input<br>5V tolerant                                     |

| 40         | GPI0             | I   | General-purpose input pin 0<br>It connects to GND or $V_{DD}$ pins when if it is unused this pin.                                            | Schmitt input<br>5V tolerant                                     |

| 41         | /MICS            | I   | Microcontroller interface: Chip select signal input pin                                                                                      | Schmitt input<br>5V tolerant                                     |

| 42         | /MICK            | I   | Microcontroller interface: Clock input pin                                                                                                   | Schmitt input                                                    |

| 43         | /MIDIO           | I/O | Microcontroller interface: Data input/output pin                                                                                             | 5V tolerant<br>Schmitt input / Open-drain<br>output, 5V tolerant |

| 44         | /MIACK           | ο   | Microcontroller interface: Acknowledge signal output pin                                                                                     | Open-drain output<br>5V tolerant                                 |

| 45         | MILP             | I   | Microcontroller interface: Latch pulse input pin                                                                                             | Schmitt input<br>5V tolerant                                     |

| 46         | GNDP             | _   | Ground pin for PLL                                                                                                                           |                                                                  |

| 47         | PLLC             | I   | Charge pump for PLL                                                                                                                          |                                                                  |

| 48         | V <sub>DDP</sub> | _   | Power pin for PLL                                                                                                                            |                                                                  |

| 49         | BTMD             | I   | Boot mode setting pin<br>It is set to "L" when if software specification does not indicate<br>since there is deference by each program ROMs. | Schmitt input<br>5V tolerant                                     |

| 50         | MIMD             | I   | Microcontroller interface: Mode select input pin                                                                                             | Schmitt input<br>5V tolerant                                     |

| 51         | /RST             | I   | Reset input pin                                                                                                                              | Schmitt input<br>5V tolerant                                     |

| 52         | V <sub>DD</sub>  | _   | Digital power pin                                                                                                                            |                                                                  |

| 53         | GND              | _   | Digital ground pin                                                                                                                           |                                                                  |

| 54         | TEST1            | I   | Test setting pin 1<br>Usually it connects to GND pins.                                                                                       | Schmitt input<br>5V intolerant                                   |

| 55         | TEST0            | I   | Test setting pin 0<br>Usually it connects to GND pins.                                                                                       | Schmitt input<br>5V intolerant                                   |

| 56         | GNDL             | _   | Ground pin for ADC-Lch                                                                                                                       |                                                                  |

| 57         | LIN              | I   | ADC-Lch signal input pin                                                                                                                     |                                                                  |

| 58         | AVDL             | I   | Reference voltage pin for ADC-Lch                                                                                                            |                                                                  |

| 59         | V <sub>DDA</sub> | -   | Analog power pin for ADC                                                                                                                     |                                                                  |

| 60         | ADVR             | I   | Reference voltage pin for ADC-Rch                                                                                                            |                                                                  |

| 61         | RIN              | I   | ADC-Rch signal input pin                                                                                                                     |                                                                  |

| 62         | GNDR             | -   | Ground pin for ADC-Rch                                                                                                                       |                                                                  |

| 63         | GNDX             | -   | Ground pin for oscillator circuit                                                                                                            |                                                                  |

| 64         | XI               | I   | Crystal oscillator connecting or clock input pin                                                                                             | 5V intolerant                                                    |

Note 1: 5V tolerant pins can have voltage applied even when the power to the device is turned off.

4

### **Description of Operation**

### 1. Timing System

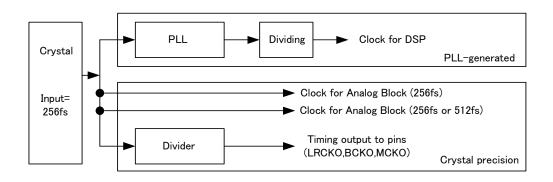

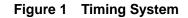

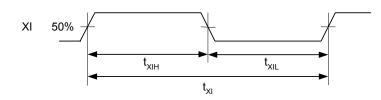

The TC94A48FG uses pulses from the XI-XO pins as the reference clock. The system is divided into blocks that use the reference clock directly or by dividing its frequency and blocks that operate on a clock the PLL generates based on the crystal resonation clock. The analog and microcontroller interface blocks operate on the crystal resonation clock while the DSP block operates on the PLL-generated clock.

The system can divide the clock from the crystal and provide three types of clock from output pins.

Figure 2 Block diagram of clock generator circuit

### 1.1 Timing register setting

### [AIFA]

| Bit   | Default | Contents                             |

|-------|---------|--------------------------------------|

| 15-14 |         | BCKi-1 clock frequency               |

|       | *       | 00 32fs                              |

|       |         | 01 48fs                              |

|       |         | 10 64fs                              |

|       |         | 11 64fs                              |

| 13-12 |         | BCKi-0 clock frequency               |

|       | *       | 00 32fs                              |

|       |         | 01 48fs                              |

|       |         | 10 64fs                              |

|       |         | 11 64fs                              |

| 11    |         | LRCKi-1 polarity                     |

|       | *       | 0 Lch=Low (interrupt by fall edge)   |

|       |         | 1 Lch=High (interrupt by rise edge)  |

| 10    |         | LRCKi-0 polarity                     |

|       | *       | 0 Lch=Low (interrupt by fall edge)   |

|       |         | 1 Lch=High (interrupt by rise edge)  |

| 9     |         | SDi clock select                     |

|       | *       | 0 LRCKi-0/BCKi-0                     |

|       |         | 1 LRCKi-1/BCKi-1                     |

| 8     |         | SDo clock select                     |

|       | *       | 0 LRCKi-0/BCKi-0<br>1 LRCKi-1/BCKi-1 |

| 7-6   |         |                                      |

| 7-0   | *       | SDi input format<br>00 LSB justified |

|       | *       | 00 LSB justified<br>01 MSB justified |

|       |         |                                      |

|       |         | $10 	ext{ I}^2 S$<br>11 	ext{ I}^2 S |

| 5-4   |         | SDi input bit clock                  |

| J-4   | *       | 00 16bit                             |

|       |         | 01 18bit                             |

|       |         | 10 20bit                             |

|       |         | 11 24bit                             |

| 3-2   |         | SDo output format                    |

|       | *       | 00 LSB justified                     |

|       |         | 01 MSB justified                     |

|       |         | 10 l <sup>2</sup> S                  |

|       |         | 11 I <sup>2</sup> S                  |

| 1-0   |         | SDo output bit clock                 |

|       | *       | 00 16bit                             |

|       |         | 01 18bit                             |

|       |         | 10 20bit                             |

|       |         | 11 24bit                             |

Note 2: In 48fs frequency setup of BCKi-1 and BCKi-0, LRCKi/BCKi coresponds only an input, and LRCKo / BCKo does not correspond.

# <u>TOSHIBA</u>

## [MOD\_O]

| Bit   | Default | Contents                                        |  |  |

|-------|---------|-------------------------------------------------|--|--|

| 15-12 |         | Reserved                                        |  |  |

|       |         | Fixed to "0"                                    |  |  |

| 11    |         | SDo3 is used as a general-purpose output Po5.   |  |  |

|       | *       | 0 Disable                                       |  |  |

|       |         | 1 Enable                                        |  |  |

| 10    |         | SDo2 is used as a general-purpose output Po4.   |  |  |

|       | *       | 0 Disable                                       |  |  |

|       |         | 1 Enable                                        |  |  |

| 9     |         | SDo1 is used as a general-purpose output Po3.   |  |  |

|       | *       | 0 Disable                                       |  |  |

|       |         | 1 Enable                                        |  |  |

| 8     |         | SDo0 is used as a general-purpose output Po2.   |  |  |

|       | *       | 0 Disable                                       |  |  |

|       |         | 1 Enable                                        |  |  |

| 7     |         | Reserved                                        |  |  |

|       |         | Fixed to "0"                                    |  |  |

| 6     |         | Reserved                                        |  |  |

|       |         | Fixed to "1"                                    |  |  |

| 5     | *       | Synchronization of LRCKi and LRCKo<br>0 Disable |  |  |

|       | *       | 1 Enable                                        |  |  |

| 4     |         | BCCMP/BCJMP Enable                              |  |  |

| 4     | *       | 0 Disable                                       |  |  |

|       |         | 1 Enable                                        |  |  |

| 3     |         | DAC Enable                                      |  |  |

| Ū     | *       | 0 Disable                                       |  |  |

|       |         | 1 Enable                                        |  |  |

| 2     |         | ADC Enable                                      |  |  |

|       | *       | 0 Disable                                       |  |  |

|       |         | 1 Enable                                        |  |  |

| 1     |         | LRCKo is connected to LRCKi1.                   |  |  |

|       | *       | 0 It does not connect.                          |  |  |

|       |         | 1 It connects.                                  |  |  |

| 0     |         | LRCKo is connected to LRCKi0.                   |  |  |

|       | *       | 0 It does not connect.                          |  |  |

|       |         | 1 It connects.                                  |  |  |

## TC94A48FG

## [TMGA]

| Bit   | Default | Contents                        |  |

|-------|---------|---------------------------------|--|

| 15-14 |         | Reserved                        |  |

|       |         | Fixed to "0"                    |  |

| 13    |         | DSP clock output select         |  |

|       | *       | 0 Disable                       |  |

|       |         | 1 Enable                        |  |

| 12-7  |         | Reserved                        |  |

|       |         | Fixed to "0"                    |  |

| 6     |         | MCKO clock output select        |  |

|       | *       | 0 1/1 Xi clock                  |  |

|       |         | 1 1/2 Xi clock                  |  |

| 5-3   |         | Reserved                        |  |

|       |         | Fixed to "0"                    |  |

| 2-0   |         | DSP clock divider setting (1/J) |  |

|       |         | 000 1/1                         |  |

|       |         | 001 1/2                         |  |

|       |         | 010 1/4                         |  |

|       |         | 011 1/8                         |  |

|       |         | 100 1/16                        |  |

|       | *       | <u>101</u> 1/3                  |  |

|       |         | <u>110</u> 1/6                  |  |

|       |         | 111 Prohibit                    |  |

### [TMGB]

|   | Bit   | Default |            | Contents                      |  |  |

|---|-------|---------|------------|-------------------------------|--|--|

|   | 15-14 |         | LRCKo/B    | CKo clock select              |  |  |

|   |       | *       | 00         | FS1/FS32(BCK=fs32)            |  |  |

|   |       |         | 01         | FS1/FS64(BCK=fs64)            |  |  |

|   |       |         | 10         | FS2/FS64(BCK=fs32)            |  |  |

|   |       |         | 11         | FS2/FS128(BCK=fs64)           |  |  |

| ľ | 13    |         | LRCKo/B    | CKo output clock select       |  |  |

|   |       | *       | 0          | Disable                       |  |  |

|   |       |         | 1          | Enable                        |  |  |

| ſ | 12-8  |         | Reference  | e clock divider setting (1/M) |  |  |

|   |       |         | 00h        | 1/1                           |  |  |

|   |       |         | 01h        | 1/2                           |  |  |

|   |       |         | •          |                               |  |  |

|   |       |         | •          |                               |  |  |

|   |       | *       | 09h        | 1/10                          |  |  |

|   |       |         | •          |                               |  |  |

|   |       |         | 1Fh        | 1/32                          |  |  |

| ľ | 7-0   |         | Variable c | lock divider setting (1/N)    |  |  |

|   |       |         | 00h        | 1/1                           |  |  |

|   |       |         | 01h        | 1/2                           |  |  |

|   |       |         |            |                               |  |  |

|   |       |         |            |                               |  |  |

|   |       | *       | 3Fh        | 1/64                          |  |  |

|   |       |         | •          |                               |  |  |

|   |       |         | FFh        | 1/256                         |  |  |

#### 1.2 Timing Output

#### LRCKO / BCKO Pin Output Settings

| Mode | LRCKO Pin Output | BCKO Pin Output | Remarks       |

|------|------------------|-----------------|---------------|

| 0    | Fixed to GND     | Fixed to ground | Initial Value |

| 1    | 1fs              | 32fs            |               |

| 2    | 1fs              | 64fs            |               |

| 3    | 2fs              | 64fs            |               |

| 4    | 2fs              | 128fs           |               |

#### **MCKO Pin Output Settings**

| Mode | MCKO Pin Output | Remarks                                   |

|------|-----------------|-------------------------------------------|

| 0    | Fixed to GND    | It can be initialized by reset.           |

| 1    | XCKI (=XI)      | Undefined until set by microcontroller or |

| 2    | 0.5 × XCKI      | built-in DSP program                      |

Note 3: A setup of a timing output is performed by the built-in firmware.

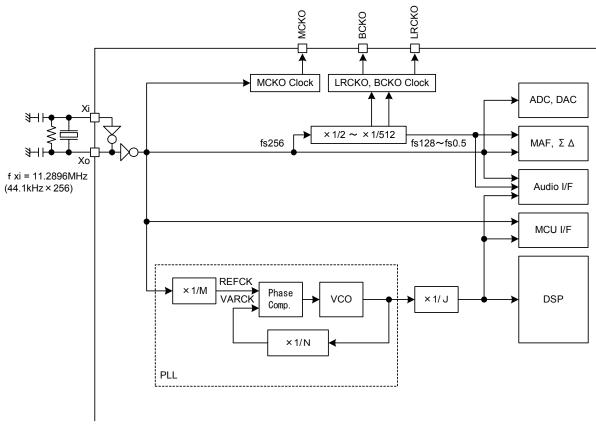

#### 1.3 Example of oscillator circuit

The example of a circuit at the time of the crystal oscillator use in an oscillation part is shown in figure 3.

Figure 3 Example of oscillator circuit

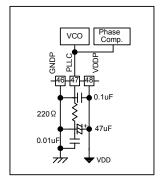

#### 1.4 Example of PLL circuit

A PLL circuit can consist of connecting LPF to a PLLC terminal easily. The example of a circuit is shown in figure 4.

Figure 4 Example of PLL circuit

The above-mentioned external constant is a reference value. It may change with application.

#### 1.5 Audio Input/Output Format

#### 1.5.1 Audio Serial Data Input Format

The TC94A48FG supports MSB-first input only. In slave mode, it supports all setting formats for the number of bit clock slots. In master mode, it does not support 24 slots.

| [        | M = MSB L = LSB don't care(invalid data, padded with "0" when read internal firmware) |                              |                                          |              |                                        |    |    |  |  |  |  |  |  |                  |  |

|----------|---------------------------------------------------------------------------------------|------------------------------|------------------------------------------|--------------|----------------------------------------|----|----|--|--|--|--|--|--|------------------|--|

| MO<br>DE | Number<br>of<br>Slots                                                                 | Data Word<br>Length<br>(bit) | Format                                   | Timing Chart | Remarks                                |    |    |  |  |  |  |  |  |                  |  |

| 0        | 16                                                                                    | 16                           | MSB-<br>justified<br>(LSB-<br>justified) |              | Initial<br>Value                       |    |    |  |  |  |  |  |  |                  |  |

| 1        |                                                                                       |                              | I²S                                      |              |                                        |    |    |  |  |  |  |  |  |                  |  |

| 2        |                                                                                       |                              | MSB-<br>justified                        |              |                                        |    |    |  |  |  |  |  |  |                  |  |

| 3        |                                                                                       | 16                           | LSB-<br>justified                        |              |                                        |    |    |  |  |  |  |  |  |                  |  |

| 4        | 24                                                                                    |                              | I <sup>2</sup> S                         |              | Unavailable<br>in master<br>mode(Note) |    |    |  |  |  |  |  |  |                  |  |

| 5        |                                                                                       | 24                           | MSB-<br>justified<br>(LSB-<br>justified) |              |                                        |    |    |  |  |  |  |  |  |                  |  |

| 6        |                                                                                       |                              | 24                                       | 24           | 21                                     | 21 | 2. |  |  |  |  |  |  | I <sup>2</sup> S |  |

| 7        |                                                                                       |                              | MSB-<br>justified                        |              |                                        |    |    |  |  |  |  |  |  |                  |  |

| 8        |                                                                                       | 16                           | LSB-<br>justified                        |              |                                        |    |    |  |  |  |  |  |  |                  |  |

| 9        | 32                                                                                    |                              | I <sup>2</sup> S                         |              |                                        |    |    |  |  |  |  |  |  |                  |  |

| 10       | 52                                                                                    |                              | MSB-<br>justified                        |              |                                        |    |    |  |  |  |  |  |  |                  |  |

| 11       |                                                                                       | 24                           | LSB-<br>justified                        |              |                                        |    |    |  |  |  |  |  |  |                  |  |

| 12       |                                                                                       |                              | I <sup>2</sup> S                         |              |                                        |    |    |  |  |  |  |  |  |                  |  |

Note 4: These formats cannot be used in master mode (when LRCK and BCK are supplied to external devices).

#### 1.5.2 Audio Serial Data Output Format

The valid part of data is the same as that for the input format. The TC94A48FG supports MSB-first output only. In slave mode, it supports all setting formats for the number of bit clock slots. In master mode, it does not support 24 slots.

| Μ        | =MS                  | BL                            | ]=LSB            | =fixed to "0" (data sent from DSP is ignored)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                        |

|----------|----------------------|-------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| MO<br>DE | Number<br>of<br>SLOT | Data Word<br>Length<br>(bits) | Format           | Timing Chart                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Remarks                                |

| 0        | 16                   | 16                            |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Initial<br>value                       |

| 1        |                      |                               | I <sup>2</sup> S | Image: Constraint of the second sec |                                        |

| 2        |                      |                               |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                        |

| 3        |                      | 16                            |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                        |

| 4        | 24                   |                               | I <sup>2</sup> S |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Unavailable<br>in master<br>mode(Note) |

| 5        |                      | 24                            |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                        |

| 6        |                      | 27                            | I <sup>2</sup> S |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                        |

| 7        |                      |                               |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                        |

| 8        |                      | 16                            |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                        |

| 9        | 32                   |                               | I²S              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                        |

| 10       | 32                   |                               |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                        |

| 11       |                      | 24                            |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                        |

| 12       |                      |                               | I²S              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                        |

Note 5: These formats cannot be used in master mode (when LRCK and BCK are supplied to external devices).

The audio input block and output block support different clock settings. Input and output port settings are, however, shared as follows:

#### LR Clock Setting for Input Block

| Mode        | Signal                                                           |

|-------------|------------------------------------------------------------------|

| Master Mode | Signal delivered to LRCKO pin (crystal resonation clock divided) |

| Slave Mode  | LRCKI0 pin input                                                 |

| Slave Mode  | LRCKI1 pin input                                                 |

#### **Bit Clock Setting for Input Block**

| Mode        | Signal                                                          |

|-------------|-----------------------------------------------------------------|

| Master Mode | Signal delivered to BCKO pin (crystal resonation clock divided) |

| Slave Mode  | BCKI0 pin input                                                 |

| Slave Mode  | BCKI1 pin input                                                 |

#### LR Clock Setting for Output Block

| Mode        | Signal                                                           |

|-------------|------------------------------------------------------------------|

| Master Mode | Signal delivered to LRCKO pin (crystal resonation clock divided) |

| Slave Mode  | LRCKI0 pin input                                                 |

| Slave Mode  | LRCKI1 pin input                                                 |

#### Bit Clock Setting for Input Block

| Mode        | Signal                                                          |

|-------------|-----------------------------------------------------------------|

| Master Mode | Signal delivered to BCKO pin (crystal resonation clock divided) |

| Slave Mode  | BCKI0 pin input                                                 |

|             | BCKI1 pin input                                                 |

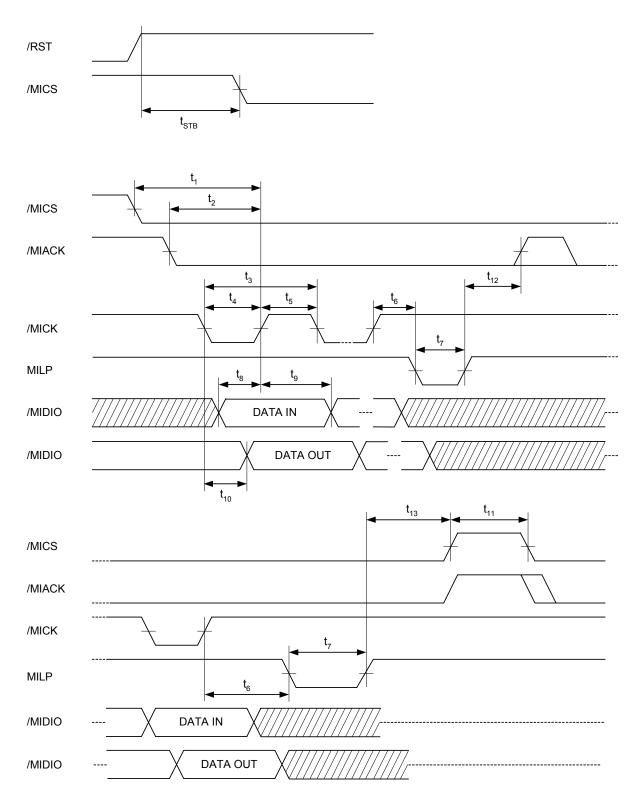

#### 2. Microcontroller Interface

The TC94A48FG can exchange data with a microcontroller in either normal transmission mode or I<sup>2</sup>C mode. It uses the MIMD pin to select the mode and inputs/outputs data in MSB-first format. Table 1 shows the features supported and the pins used in each mode. Table 2 shows the bit composition of a 24-bit command.

Note 6: This data sheet shows general control methods. Refer to the separate program explanation data sheet for a complete command list or detailed description of control methods.

### Table 1 Pins Used and Features Supported in Normal Transmission Mode and I<sup>2</sup>C Mode

| Transmission Mode |                                               | Normal Transmission Mode (MIMD=L) | I <sup>2</sup> C Mode (MIMD=H) |  |

|-------------------|-----------------------------------------------|-----------------------------------|--------------------------------|--|

| Pin               | Input/Output                                  | Function                          | Function                       |  |

| /MICS             | Input                                         | Chip select Input                 | Not used (fixed to "L")        |  |

| MILP              | Input                                         | Latch pulse input                 | Not used (fixed to "L")        |  |

| /MIDIO            | Input                                         | Data input / output               | Data input / output (SDA)      |  |

| /WIDIO            | Output (open-drain)                           |                                   | Data Input / Output (SDA)      |  |

| /MICK             | Input, Input / Output (I <sup>2</sup> C mode) | Clock input                       | Clock input (SCL)              |  |

| /MIACK            | Output (open-drain)                           | Acknowledge output                | Not used                       |  |

Note 7: The input High voltage for these pins should be  $V_{\text{DD}}\mbox{-}0.2$  V to 5.5V.

Note 8: The open-drain /MIDIO and /MIACK pins require external pull-up resistors.

In I<sup>2</sup>C mode, the /MICK pin also requires a pull-up resistor.

The pulled-up voltage for these pins should be  $V_{DD}$ -0.2V to 5.5V.

Note9: The I<sup>2</sup>C bus write address is 30 h and read address is 31h.

| Bit  | Function                                  | Remarks                                                          |  |  |  |  |  |

|------|-------------------------------------------|------------------------------------------------------------------|--|--|--|--|--|

| 23-8 | 16-bit address                            | Refer to the command list in the program explanation data sheet. |  |  |  |  |  |

| 7    | Not used                                  | _                                                                |  |  |  |  |  |

| 6    | Start program RAM boot                    | "1" starts program RAM boot.                                     |  |  |  |  |  |

| 5    | Specify soft reset                        | "1" triggers a soft reset.                                       |  |  |  |  |  |

| 4    | Specify read or write (R/W)               | "1" specifies a read.                                            |  |  |  |  |  |

| 3-0  | Set the number of words to be transmitted | 0h" ; 1word<br>↓<br>"7h" ; 8words                                |  |  |  |  |  |

### Table 2 Bit Composition of a 24-bit Command

#### 2.1 Normal Transmission Mode

#### 2.1.1 Data Transfer Format in Normal Transmission Mode

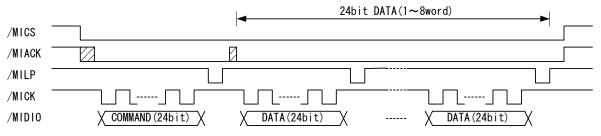

Figure 1 shows the data transfer format in normal transmission mode. In normal transmission mode, the system first drives /MICS low and then checks that /MIACK is low before transferring a 24-bit command MSB first. It cannot transfer data if /MIACK is high. The system then reads or writes as many 24-bit data words (one to eight) as specified with the 24-bit command and finally drives /MICS high. For a read, it should also make sure that /MIACK is low after transferring a 24-bit command because /MIACK becomes high temporarily after the command is transferred.

Figure 5(a) Data Transfer Format in Normal Transmission Mode

#### 2.1.2 Data Transfer Method in Normal Transmission Mode

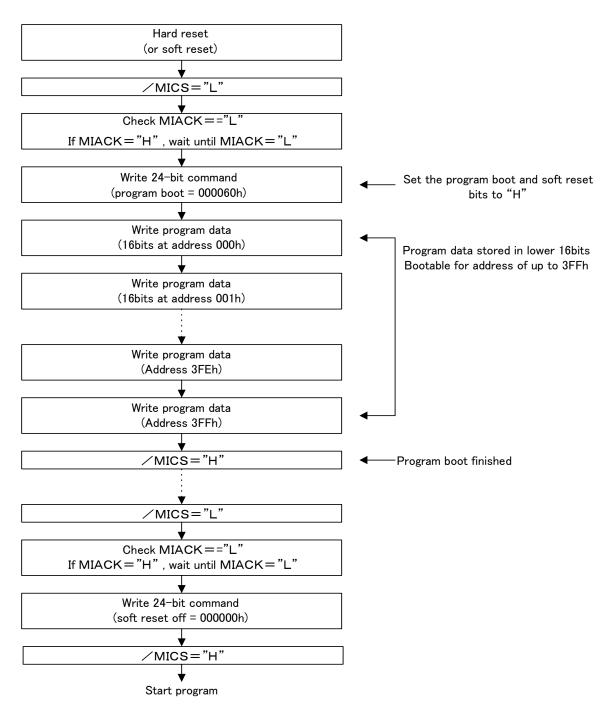

(1) Program boot and program start

The TC94A48FG has 1k-word RAM assigned to program addresses 000h to 3FFh, in which 000h to 003h are interrupt vector addresses. To enable the TC94A48FG to operate, a program must be booted to an interrupt vector address. If you want to store a program in the area from 004h to 3FFh, a program loading process must follow the interrupt vector address. For a program boot, the 24-bit command transferred upon a reset must have the program RAM boot start bit and soft reset bit set to "1" (command = xxxx60h).

The command must be followed by 16-bit program data, set in lower bits in 24-bit data.

The write address is automatically incremented (by one) from the command (000h). The program boot completes once /MICS is driven high upon transferring the required number of words.

The write address for a program boot always starts from the command (000h). To start the program, transfer a 24-bit command with the soft reset bit cleared and then drive /MICS high without transferring data.

Figure 6 shows the program boot and program start procedure.

(2) Writing 24-bit data

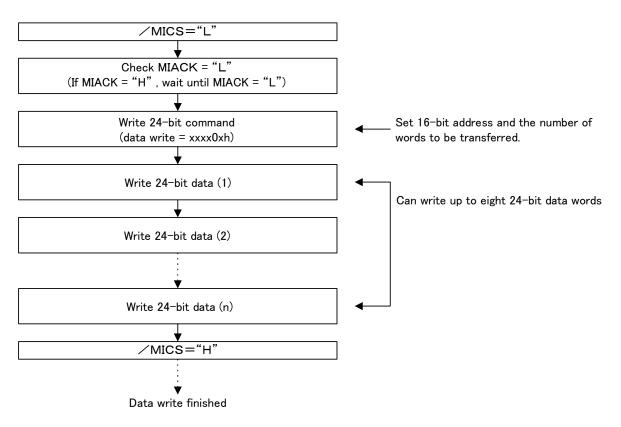

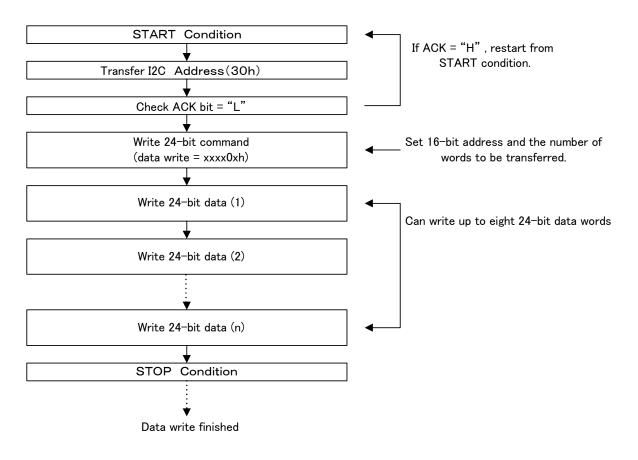

When the host microcontroller writes data to the TC94A48FG during the execution of a program, it sets a 16-bit address in a 24-bit command as well as sets its R/W bit to "0" and sets the number of words to be written. Then, it transfers the 24-bit command, followed by a required number of 24-bit data words.

Figure 7 shows the 24 bit data write procedure.

Figure 7 shows the 24-bit data write procedure.

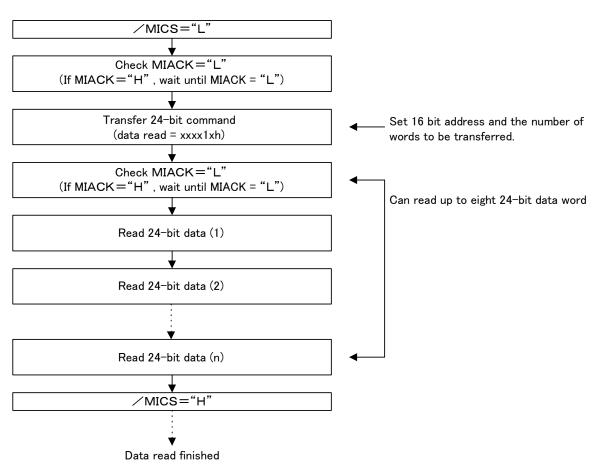

(3) Reading 24-bit data

When the host microcontroller reads data from the TC94A48FG during the execution of a program, it sets a 16-bit address in a 24-bit command as well as sets its R/W bit to "1" and sets the number of words to be read. Then, it transfers the 24-bit command, check that /MIACK = "L", and read a required number of 24-bit data words.

The host microcontroller should check that /MIACK = "L" because it has to wait until the data to be read is set in the data buffer.

Figure 8 shows the 24 bit data read procedure.

### Figure 8 shows the 24-bit data read procedure.

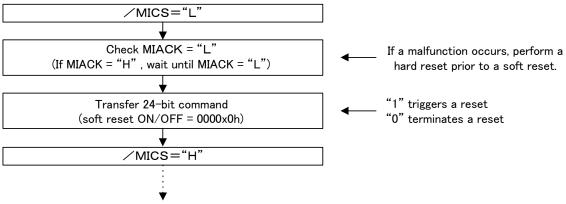

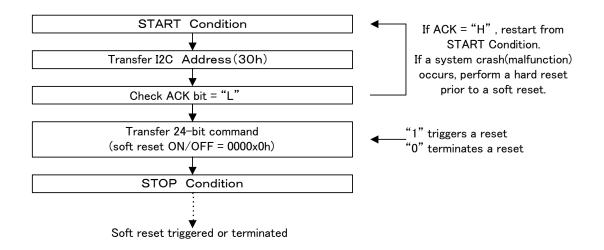

(4) Triggering and terminating a soft reset

A soft reset is required before the system can start a program after program boot or restart a program.

A 24-bit command with its soft reset bit set to "1" triggers a soft reset and a command with the bit cleared terminates a soft reset.

When trigging or terminating a soft reset, drive /MICS high after transferring the 24-bit command because no data needs to follow the command.

Figure 9 shows the procedure for trigging or terminating a soft reset.

Soft reset triggered or terminated

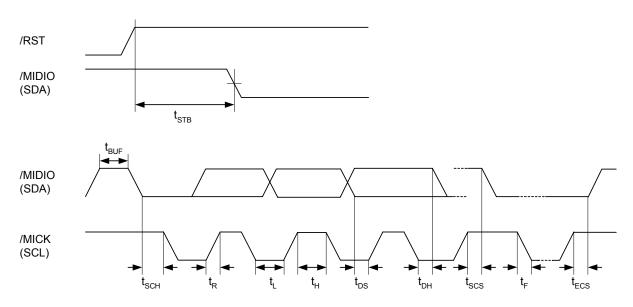

#### 2.2 I<sup>2</sup>C Bus Mode

#### 2.2.1 Data Transfer Format in I<sup>2</sup>C Bus Mode

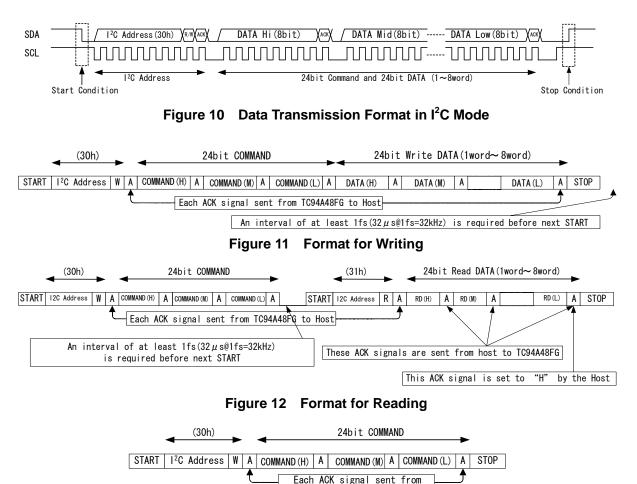

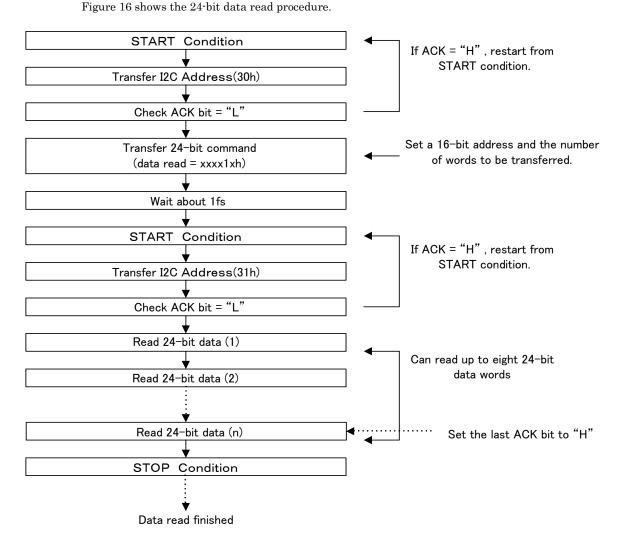

Figure 10 shows the data transfer format in  $I^2C$  bus mode.

In I<sup>2</sup>C bus mode, the host microcontroller first transfers an I<sup>2</sup>C address (write = 30h) and then checks that the ACK bit is low. If the ACK bit is high, it retransmits a start condition (without transmitting a stop condition) and then transfers an I<sup>2</sup>C address of 30h. After transferring an I<sup>2</sup>C address, the host microcontroller transfers a 24-bit command. When the host microcontroller writes data to the TC94A48FG, it writes as many 24-bit data words as specified with the 24-bit command (1 to 8 words) and then transfers an end condition.

When the host microcontroller reads data from the TC94A48FG, it transfers a 24-bit command and then, without transmitting an end condition, transfers an I<sup>2</sup>C address (read =31h) and check that the ACK bit is low. If the ACK bit is high, the host microcontroller retransmits a start condition (without transmitting a stop condition) and then transfers an I<sup>2</sup>C address of 31h. After checking that the ACK bit is low, the host microcontroller reads as many 24-bit data words as specified with the 24-bit command (1 to 8 words). During a read, the host microcontroller sets the ACK bit to low after reading every eight bits. The ACK bit accompanying the last eight bits must be set to high, after which the host microcontroller transmits a stop condition. When transferring only a 24-bit command without reading or writing data, transmit an end condition after transferring the command.

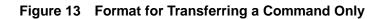

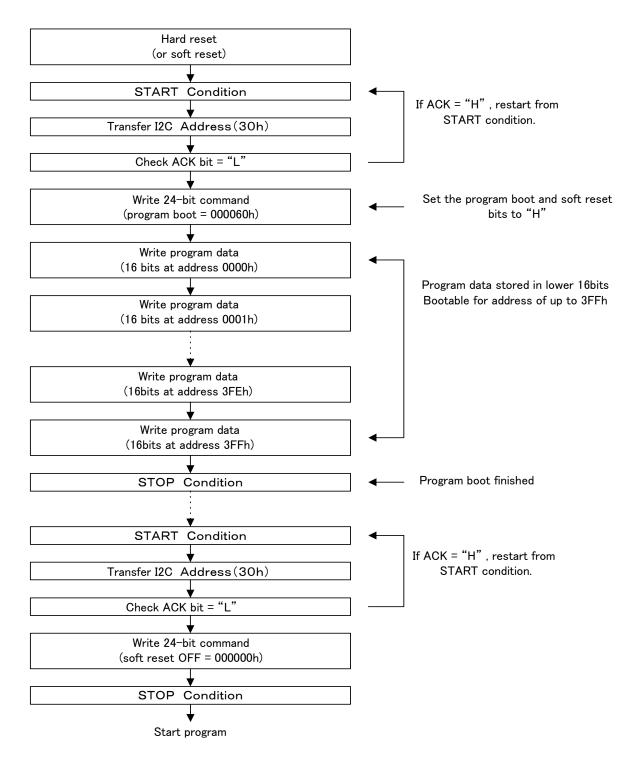

Figures 11 to 13 show the data transfer formats for writing, reading, and transferring a command only.

TC94A48FG to Host

#### 2.2.2 Data Transfer Method in I<sup>2</sup>C Mode

(1) Program boot and program start

The TC94A48FG has 1k-word RAM assigned to program addresses 000h to 3FFh, in which 000h to 003h are interrupt vector addresses. To enable the TC94A48FG to operate, a program must be booted to an interrupt vector address. If you want to store a program in the area from 004h to 3FFh, a program loading process must follow the interrupt vector address. For a program boot, the 24-bit command transferred upon a reset must have the program RAM boot start bit and soft reset bit set to "1" (command = xxxx60h).

The command must be followed by 16-bit program data, set in lower bits in 24-bit data.