# INTEGRATED CIRCUITS

# DATA SHEET

TDA8030; TDA8031 USB smart card reader (OTP or ROM)

**Product specification**

# **USB** smart card reader (OTP or ROM)

TDA8030; TDA8031

| CONTENT      | rs                                | 8.5            | USB INTERFACE                                            |

|--------------|-----------------------------------|----------------|----------------------------------------------------------|

| 1            | FEATURES                          | 8.5.1          | End-points                                               |

|              |                                   | 8.5.2          | Phase-locked loop                                        |

| 2            | APPLICATIONS                      | 8.5.3          | Bit clock recovery                                       |

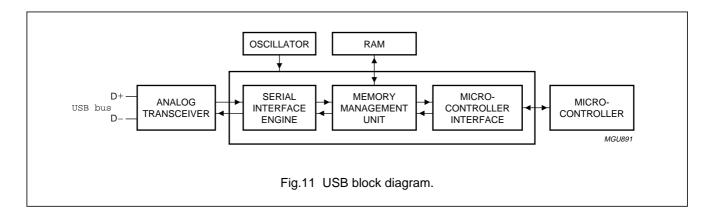

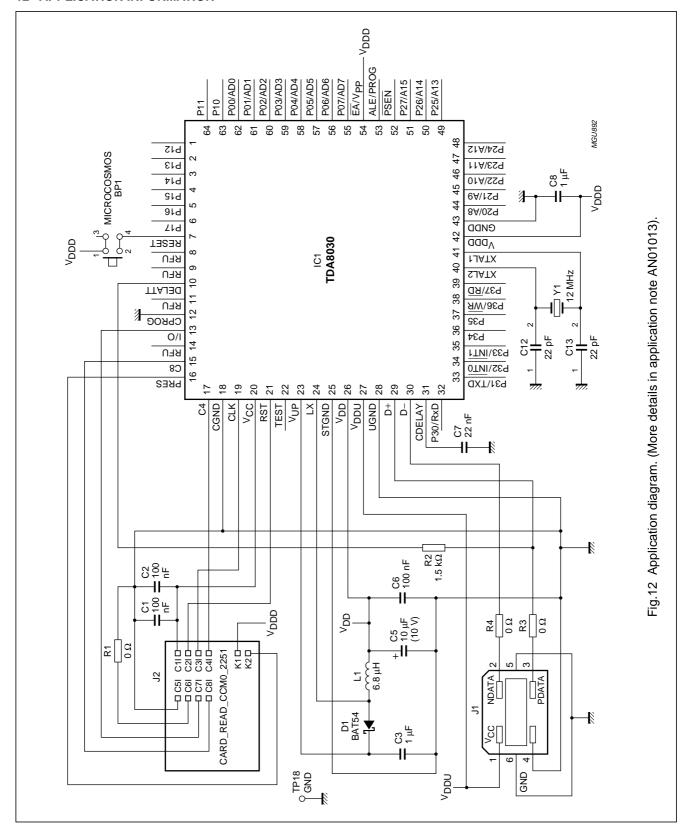

| 3            | GENERAL DESCRIPTION               | 8.5.4<br>8.5.5 | Interface signals with the microcontroller Block diagram |

| 4            | ORDERING INFORMATION              | 8.5.6          | USB registers                                            |

| 5            | QUICK REFERENCE DATA              | 8.5.7          | Instruction set                                          |

| 6            | BLOCK DIAGRAM                     | 8.5.8          | Analog interface                                         |

| 7            | PINNING                           | 8.5.9          | Suspend mode                                             |

| 7.1          | TDA8030                           | 9              | LIMITING VALUES                                          |

| 7.2          | TDA8031                           | 10             | THERMAL CHARACTERISTICS                                  |

| 8            | FUNCTIONAL DESCRIPTION            | 11             | CHARACTERISTICS                                          |

| 8.1          | ISO7816 UART AND ASSOCIATED LOGIC | 12             | APPLICATION INFORMATION                                  |

| 8.1.1        | Interface control                 | 13             | PACKAGE OUTLINE                                          |

| 8.1.2        | Control registers                 | 14             | SOLDERING                                                |

| 8.1.3        | General registers                 | 14.1           | Introduction to soldering surface mount                  |

| 8.1.4        | ISO UART REGISTERS                |                | packages                                                 |

| 8.1.5        | CARDS REGISTERS                   | 14.2           | Reflow soldering                                         |

| 8.1.6        | Registers summary<br>SUPPLY       | 14.3           | Wave soldering                                           |

| 8.2<br>8.2.1 | Power switch control              | 14.4           | Manual soldering                                         |

| 8.2.2        | 3.3 V regulator                   | 14.5           | Suitability of surface mount IC packages for             |

| 8.2.3        | DC-to-DC converter                |                | wave and reflow soldering methods                        |

| 8.2.4        | Supply supervisor                 | 15             | DATA SHEET STATUS                                        |

| 8.3          | ISO7816 SECURITY                  | 16             | DEFINITIONS                                              |

| 8.3.1        | Introduction                      |                |                                                          |

| 8.3.2        | Protections and limitations       | 17             | DISCLAIMERS                                              |

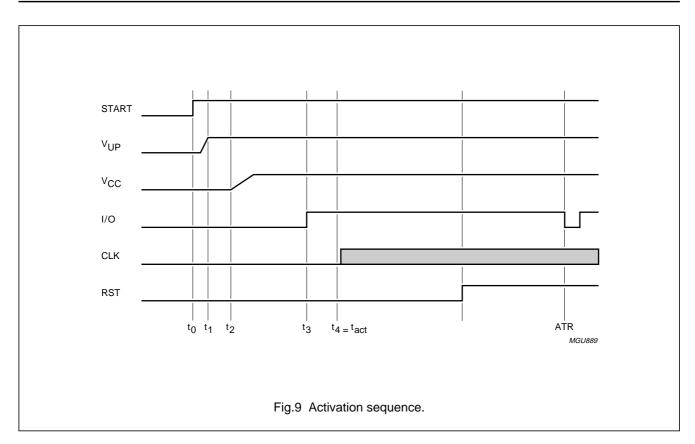

| 8.3.3        | Activation sequence               |                |                                                          |

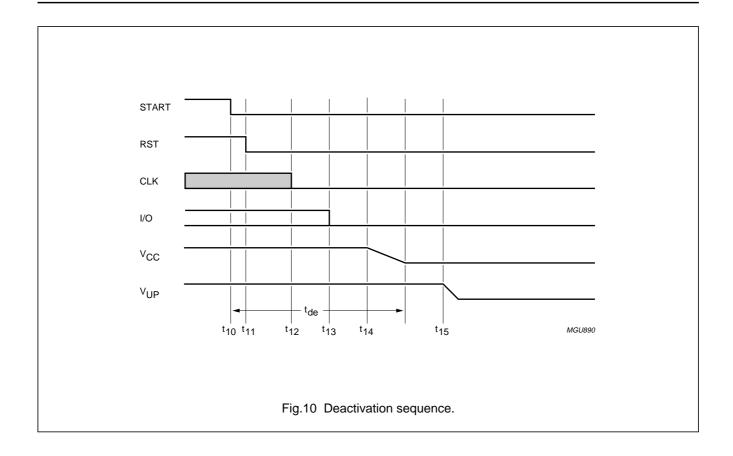

| 8.3.4        | Deactivation sequence             |                |                                                          |

| 8.4          | MICROCONTROLLER                   |                |                                                          |

| 8.4.1        | Low power modes                   |                |                                                          |

# USB smart card reader (OTP or ROM)

# TDA8030; TDA8031

#### 1 FEATURES

- 83C51 core with 16 kbytes EPROM (ROM); 256 bytes RAM; 512 bytes AUXRAM; Timer 0,1, 2 and enhanced HART

- Full speed USB interface device which complies with USB 1.1 specification; accessible with MOVX instructions

- Control input and output; 1 generic input and output and 2 generic input end-points

- Compatible with bus powered and suspend mode supply current requirements

- Specific ISO7816 UART; accessible with MOVX instructions for automatic convention processing; variable baud rate through frequency or division ratio programming; error management at character level for T = 0 protocol; extra guard time register

- V<sub>CC</sub> generation (5 or 3 V maximum current 55 mA or 1.8 V maximum current 35 mA) with controlled rise and fall times; current limitation and overload detection at 100 mA

- Cards clock generation with three times synchronous frequency doubling (12, 6, 3 and 1.5 MHz)

- Cards clock STOP HIGH or LOW or 1.25 MHz (from an integrated oscillator) for cards power reduction mode

- Automatic activation and deactivation sequences through an independent sequencer

- Supports the asynchronous protocols T = 0 and T = 1 in accordance with ISO7816 and EMV

- Versatile 24-bit time-out counter for Answer To Reset (ATR) and waiting times processing

- · Supports synchronous cards

- Specific Elementary Time Unit (ETU) counter for Block Guard Time (BGT)

- Current limitations on cards contacts and emergency deactivation in case of over consumption or overheating

- Special circuitry for killing spikes during power-on or power-off

- Supply supervisor for power-on or power-off reset

- High efficiency inductive DC-to-DC converter for V<sub>CC</sub> generation

- Soft switch on for avoiding current inrush at plug in

- Enhanced ESD protections on cards contacts (6 kV minimum)

- Software library for easy integration within the application.

### 2 APPLICATIONS

• Smart card readers for PC's or Set Top Boxes.

#### 3 GENERAL DESCRIPTION

The TDA8030; TDA8031 is a bus powered full-speed USB device. All analog and digital functions for an EMV compliant Smart Card Reader are built-in. The embedded 83C51 microcontroller has 16 kbytes EPROM (ROM for TDA8031), 256 bytes RAM and 512 bytes of AUXRAM.

# 4 ORDERING INFORMATION

| TYPE NUMBER |        | PACKAGE                                                                            |          |  |  |  |  |

|-------------|--------|------------------------------------------------------------------------------------|----------|--|--|--|--|

| TIPE NOWBER | NAME   | DESCRIPTION                                                                        | VERSION  |  |  |  |  |

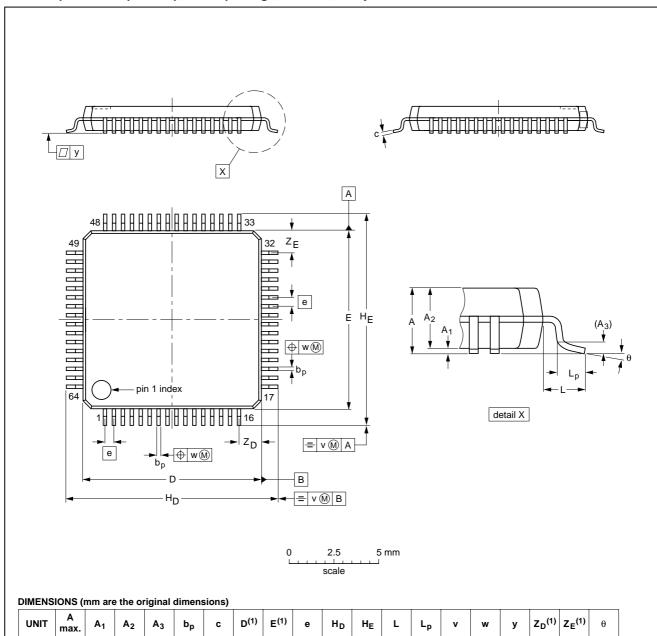

| TDA8030HL   | LQFP64 | plastic low profile quad flat package; 64 leads; body $10 \times 10 \times 1.4$ mm | SOT314-2 |  |  |  |  |

| TDA8031HL   |        |                                                                                    |          |  |  |  |  |

3

# USB smart card reader (OTP or ROM)

# TDA8030; TDA8031

# 5 QUICK REFERENCE DATA

| SYMBOL           | PARAMETER                             | CONDITIONS                                                                    | MIN. | TYP. | MAX. | UNIT |

|------------------|---------------------------------------|-------------------------------------------------------------------------------|------|------|------|------|

| V <sub>DDU</sub> | bus supply voltage                    |                                                                               | 4.2  | _    | 5.5  | V    |

| I <sub>DDU</sub> | bus supply current                    | $V_{CC} = 5 \text{ V; } I_{CC} = 40 \text{ mA;}$<br>$f_{clk} = 6 \text{ MHz}$ | _    | _    | 100  | mA   |

| I <sub>sus</sub> | suspend current                       | card inactive; microcontroller in Power-down mode                             | _    | _    | 500  | μΑ   |

| V <sub>CC</sub>  | card supply voltage                   | including static load; 5 V card                                               | 4.75 | 5    | 5.25 | V    |

|                  |                                       | with dynamic loads on 200 nF                                                  | 4.60 | _    | 5.40 | V    |

|                  |                                       | including static loads; 3 V card                                              | 2.85 | 3    | 3.15 | V    |

|                  |                                       | with dynamic loads on 200 nF                                                  | 2.75 | _    | 3.25 | V    |

|                  |                                       | including static loads; 1.8 V card                                            | 1.64 | 1.8  | 1.96 | V    |

|                  |                                       | with dynamic loads on 200 nF                                                  | 1.62 | _    | 1.98 | V    |

| Icc              | card supply current                   | 5 V card                                                                      | _    | _    | -55  | mA   |

|                  |                                       | 3 V card                                                                      | _    | _    | -55  | mA   |

|                  |                                       | 1.8 V card                                                                    | _    | _    | -35  | mA   |

| I <sub>lim</sub> | current limit on V <sub>CC</sub>      |                                                                               | _    | _    | 100  | mA   |

| I <sub>od</sub>  | overload detection on V <sub>CC</sub> |                                                                               | _    | _    | 100  | mA   |

| T <sub>amb</sub> | ambient temperature                   |                                                                               | -25  | _    | +85  | °C   |

# USB smart card reader (OTP or ROM)

# TDA8030; TDA8031

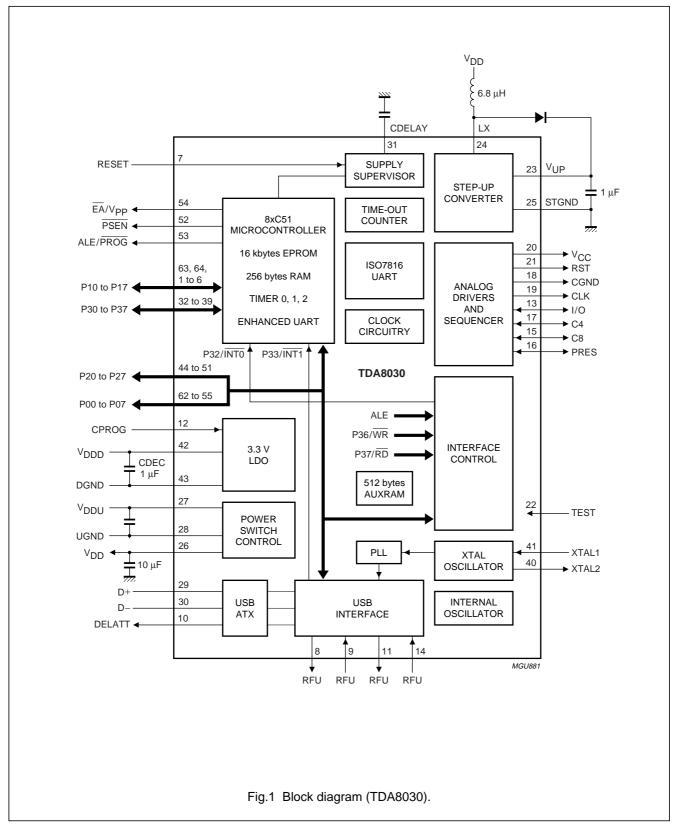

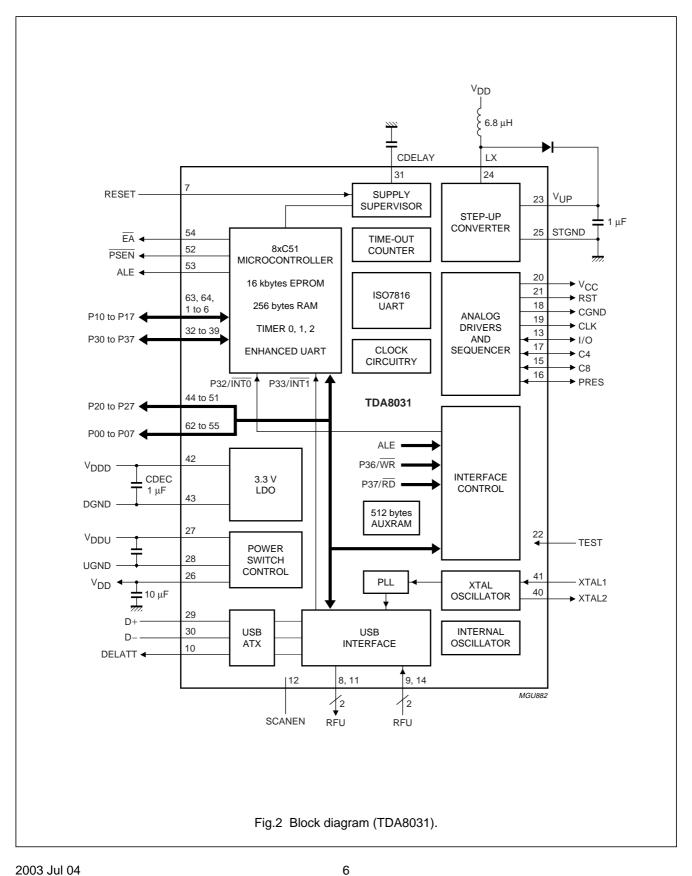

# 6 BLOCK DIAGRAM

5

# USB smart card reader (OTP or ROM)

TDA8030; TDA8031

TDA8030; TDA8031

# USB smart card reader (OTP or ROM)

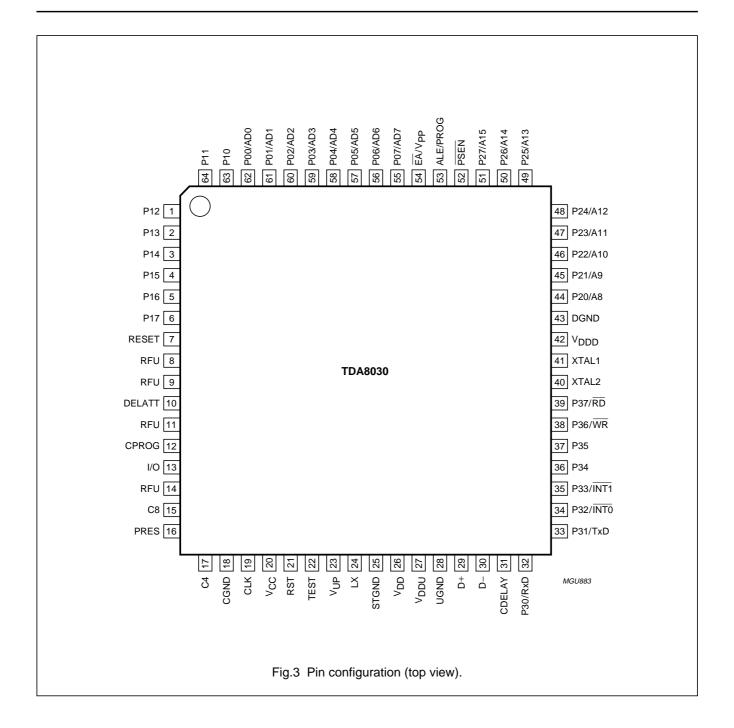

# 7 PINNING

# 7.1 TDA8030

| SYMBOL          | PIN | DESCRIPTION                                                                                                                                              |  |  |  |  |

|-----------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| P12             | 1   | 8xC51 general purpose I/O port (USB_MC_READY)                                                                                                            |  |  |  |  |

| P13             | 2   | 8xC51 general purpose I/O port (USB_CLK_EN_N)                                                                                                            |  |  |  |  |

| P14             | 3   | 8xC51 general purpose I/O port (USB_RESET_N)                                                                                                             |  |  |  |  |

| P15             | 4   | 8xC51 general purpose I/O port (USB_SOFTCONNECT_EXT)                                                                                                     |  |  |  |  |

| P16             | 5   | 8xC51 general purpose I/O port (available for the application)                                                                                           |  |  |  |  |

| P17             | 6   | 8xC51 general purpose I/O port (available for the application)                                                                                           |  |  |  |  |

| RESET           | 7   | reset input (active HIGH, integrated pull-down resistor to ground)                                                                                       |  |  |  |  |

| RFU             | 8   | test pin; leave open-circuit in the application                                                                                                          |  |  |  |  |

| RFU             | 9   | test pin; leave open-circuit in the application                                                                                                          |  |  |  |  |

| DELATT          | 10  | elayed attachment reference signal output for external pull-up resistor on pin D+ (an interna 5 k $\Omega$ pull-up resistor is already embedded on-chip) |  |  |  |  |

| RFU             | 11  | test pin; leave open-circuit in the application                                                                                                          |  |  |  |  |

| CPROG           | 12  | connect to GND within the application; for programming the EPROM connect to V <sub>DD</sub> as well as pin TEST (pin 22); also used for test purposes    |  |  |  |  |

| I/O             | 13  | data input/output from the card (C7); 14 kΩ integrated pull-up resistor connected to V <sub>CC</sub>                                                     |  |  |  |  |

| RFU             | 14  | test pin; leave open-circuit in the application                                                                                                          |  |  |  |  |

| C8              | 15  | auxiliary I/O for C8 contact; 14 k $\Omega$ integrated pull-up resistor connected to V <sub>CC</sub>                                                     |  |  |  |  |

| PRES            | 16  | card presence detection input (active HIGH; no need for external pull-up)                                                                                |  |  |  |  |

| C4              | 17  | auxiliary I/O for C4 contact; 14 k $\Omega$ integrated pull-up resistor connected to V <sub>CC</sub>                                                     |  |  |  |  |

| CGND            | 18  | cards ground (C5) Must be connected to GND                                                                                                               |  |  |  |  |

| CLK             | 19  | clock output (C30)                                                                                                                                       |  |  |  |  |

| V <sub>CC</sub> | 20  | card supply output voltage (ISO C1 contact); must be decoupled with two 100 nF low ESR ceramic capacitors to CGND                                        |  |  |  |  |

| RST             | 21  | cards reset output (C2)                                                                                                                                  |  |  |  |  |

| TEST            | 22  | test pin input                                                                                                                                           |  |  |  |  |

| V <sub>UP</sub> | 23  | output of the DC-to-DC converter (decouple with a 1 μF capacitor to STGND)                                                                               |  |  |  |  |

| LX              | 24  | DC-to-DC converter inductor connection (a Schottky diode should be tied to V <sub>UP</sub> )                                                             |  |  |  |  |

| STGND           | 25  | DC-to-DC converter ground connection                                                                                                                     |  |  |  |  |

| $V_{DD}$        | 26  | soft switched positive supply voltage (decouple with 10 μF capacitor to GND)                                                                             |  |  |  |  |

| $V_{DDU}$       | 27  | positive supply voltage for the bus (4.2 to 5.5 V)                                                                                                       |  |  |  |  |

| UGND            | 28  | bus ground                                                                                                                                               |  |  |  |  |

| D+              | 29  | USB D+ data line                                                                                                                                         |  |  |  |  |

| D-              | 30  | USB D- data line                                                                                                                                         |  |  |  |  |

| CDELAY          | 31  | connection for an external capacitor to ground determining the Power-on reset pulse width (typ 1 ms per 2 nF)                                            |  |  |  |  |

| P30/RxD         | 32  | 8xC51 general purpose I/O port/serial input port (available for the application)                                                                         |  |  |  |  |

| P31/TxD         | 33  | 8xC51 general purpose I/O port/serial output port (available for the application)                                                                        |  |  |  |  |

| P32/INT0        | 34  | 8xC51 general purpose I/O port/external interrupt 0 (used by the ISO UART))                                                                              |  |  |  |  |

| P33/INT1        | 35  | 8xC51 general purpose I/O port/external interrupt 1 (used by the USB interface)                                                                          |  |  |  |  |

TDA8030; TDA8031

# USB smart card reader (OTP or ROM)

| SYMBOL             | PIN | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P34                | 36  | 8xC51 general purpose I/O port (USB_SUSPEND in TDA8030)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| P35                | 37  | 8xC51 general purpose I/O port (USB_WAKEUP_N in TDA8031)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| P36/WR             | 38  | external data memory write strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| P37/RD             | 39  | external data memory read strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| XTAL2              | 40  | 12 MHz crystal output; leave open-circuit if an external clock is used                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| XTAL1              | 41  | external 12 MHz crystal connection or input for an external clock signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| $V_{DDD}$          | 42  | 3.3 V regulated digital supply voltage output (decouple with 1 μF ceramic capacitor)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| DGND               | 43  | Digital ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| P20/A8             | 44  | 8xC51 general purpose I/O port/address 8 (available for the application)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| P21/A9             | 45  | 8xC51 general purpose I/O port/address 9 (available for the application)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| P22/A10            | 46  | 8xC51 general purpose I/O port/address 10 (available for the application)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| P23/A11            | 47  | 8xC51 general purpose I/O port/address 11 (available for the application)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| P24/A12            | 48  | 8xC51 general purpose I/O port/address 12 (available for the application)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| P25/A13            | 49  | 8xC51 general purpose I/O port/address 13 (USB_MP_C)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| P26/A14            | 50  | 8xC51 general purpose I/O port/address 14 (USB_MP_SEL)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| P27/A15            | 51  | 8xC51 general purpose I/O port/address 15 (ISO_UART_CS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| PSEN               | 52  | Program Store Enable: read strobe to external program memory when executing code from the external program memory; $\overline{\text{PSEN}}$ is activated twice each machine cycle except when two $\overline{\text{PSEN}}$ activations are skipped during each access to external data memory. $\overline{\text{PSEN}}$ is not activated during fetches from internal program memory.                                                                                                                                                                                  |

| ALE/PROG           | 53  | Address Latch Enable/Program Pulse: output pulse for latching the low byte of the address during an access to external memory. In normal operation ALE is emitted at a constant rate of 1/6 the oscillator frequency and can be used for external timing or clocking. It should be noted that one ALE pulse is skipped during each access to external data memory. This pin is also the program pulse input (PROG) during EPROM programming. ALE can be disabled by setting SFR Auxiliary0. With this bit set ALE will be active only during a MOVX instruction.       |

| ĒĀ/V <sub>PP</sub> | 54  | External Access Enable/Programming Supply Voltage: $\overline{EA}$ must be externally held LOW to enable the device to fetch code from external program memory locations starting with 0000H. If $\overline{EA}$ is held HIGH the device executes from internal program memory unless the program counter contains an address greater than 3FFFH (16 kbytes boundary). This pin also receives the 12.75 V programming supply voltage (V <sub>PP</sub> ) during EPROM programming. If security bit 1 is programmed $\overline{EA}$ will be internally latched on reset. |

| P07/AD7            | 55  | 8xC51 general purpose I/O port/address/data 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| P06/AD6            | 56  | 8xC51 general purpose I/O port/address/data 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| P05/AD5            | 57  | 8xC51 general purpose I/O port/address/data 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| P04/AD4            | 58  | 8xC51 general purpose I/O port/address/data 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| P03/AD3            | 59  | 8xC51 general purpose I/O port/address/data 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| P02/AD2            | 60  | 8xC51 general purpose I/O port/address/data 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| P01/AD1            | 61  | 8xC51 general purpose I/O port/address/data 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| P00/AD0            | 62  | 8xC51 general purpose I/O port/address/data 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| P10                | 63  | 8xC51 general purpose I/O port (USB_INT_MASK)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| P11                | 64  | 8xC51 general purpose I/O port (USB_SOFTCONNECT_INT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

# USB smart card reader (OTP or ROM)

TDA8030; TDA8031

9

TDA8030; TDA8031

# USB smart card reader (OTP or ROM)

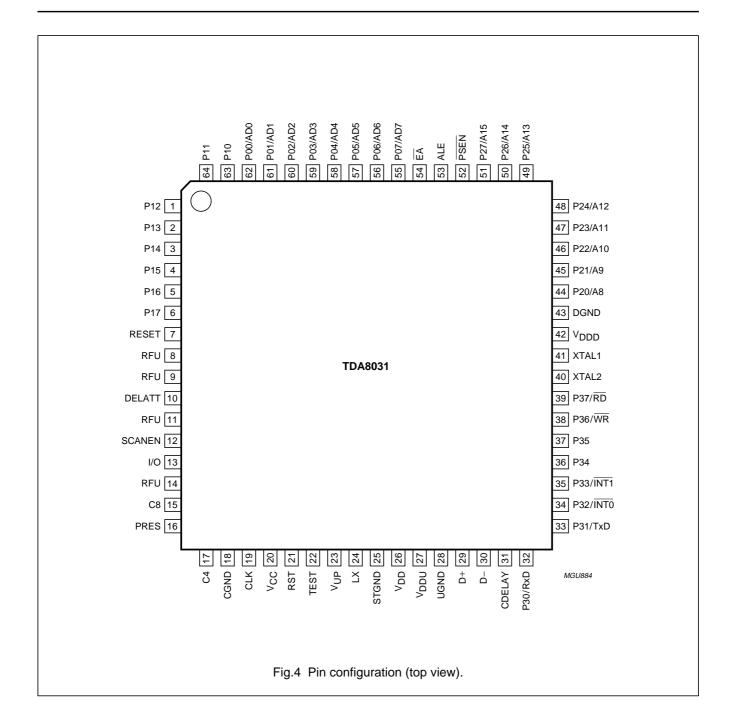

# 7.2 TDA8031

| SYMBOL           | PIN | DESCRIPTION                                                                                                                                                      |

|------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P12              | 1   | 8xC51 general purpose I/O port (USB_MC_READY)                                                                                                                    |

| P13              | 2   | 8xC51 general purpose I/O port (USB_CLK_EN_N)                                                                                                                    |

| P14              | 3   | 8xC51 general purpose I/O port (USB_RESET_N)                                                                                                                     |

| P15              | 4   | 8xC51 general purpose I/O port (USB_SOFTCONNECT_EXT)                                                                                                             |

| P16              | 5   | 8xC51 general purpose I/O port (available for the application)                                                                                                   |

| P17              | 6   | 8xC51 general purpose I/O port (available for the application)                                                                                                   |

| RESET            | 7   | reset input (active HIGH, integrated pull-down resistor to ground)                                                                                               |

| RFU              | 8   | test pin; leave open-circuit in the application                                                                                                                  |

| RFU              | 9   | test pin; leave open-circuit in the application                                                                                                                  |

| DELATT           | 10  | delayed attachment reference signal output for external pull-up resistor on pin D+ (an internal 1.5 k $\Omega$ pull-up resistor is already embedded in the chip) |

| RFU              | 11  | test pin; leave open-circuit in the application                                                                                                                  |

| SCANEN           | 12  | connect to GND within the application; for programming the EPROM connect to $V_{DD}$ as well as pin TEST (pin 22); also used for test purposes                   |

| I/O              | 13  | data input/output from the card (C7); 14 kΩ integrated pull-up resistor connected to V <sub>CC</sub>                                                             |

| RFU              | 14  | test pin; leave open-circuit in the application                                                                                                                  |

| C8               | 15  | auxiliary I/O for C8 contact; 14 kΩ integrated pull-up resistor connected to V <sub>CC</sub>                                                                     |

| PRES             | 16  | card presence detection input (active HIGH; no need for external pull-up)                                                                                        |

| C4               | 17  | auxiliary I/O for C4 contact; 14 kΩ integrated pull-up resistor connected to V <sub>CC</sub>                                                                     |

| CGND             | 18  | cards ground (C5) Must be connected to GND                                                                                                                       |

| CLK              | 19  | clock output (C30)                                                                                                                                               |

| V <sub>CC</sub>  | 20  | card supply output voltage (ISO C1 contact); must be decoupled with two 100 nF low ESR ceramic capacitors to CGND                                                |

| RST              | 21  | cards reset output (C2)                                                                                                                                          |

| TEST             | 22  | test pin input                                                                                                                                                   |

| V <sub>UP</sub>  | 23  | output of the DC-to-DC converter (decouple with a 1 μF capacitor to STGND)                                                                                       |

| LX               | 24  | DC-to-DC converter inductor connection (a Schottky diode should be tied to V <sub>UP</sub> )                                                                     |

| STGND            | 25  | DC-to-DC converter ground connection                                                                                                                             |

| V <sub>DD</sub>  | 26  | soft switched positive supply voltage (decouple with 10 μF capacitor to GND)                                                                                     |

| V <sub>DDU</sub> | 27  | positive supply voltage for the bus (4.2 to 5.5 V)                                                                                                               |

| UGND             | 28  | bus ground                                                                                                                                                       |

| D+               | 29  | USB D+ data line                                                                                                                                                 |

| D-               | 30  | USB D- data line                                                                                                                                                 |

| CDELAY           | 31  | connection for an external capacitor to ground determining the Power-on reset pulse width (typ 1 ms per 2 nF)                                                    |

| P30/RxD          | 32  | 8xC51 general purpose I/O port/serial input port (available for the application)                                                                                 |

| P31/TxD          | 33  | 8xC51 general purpose I/O port/serial output port (available for the application)                                                                                |

| P32/INT0         | 34  | 8xC51 general purpose I/O port/external interrupt 0 (used by the ISO UART))                                                                                      |

| P33/INT1         | 35  | 8xC51 general purpose I/O port/external interrupt 1 (used by the USB interface)                                                                                  |

| P34              | 36  | 8xC51 general purpose I/O port (USB_SUSPEND in TDA8030)                                                                                                          |

TDA8030; TDA8031

# USB smart card reader (OTP or ROM)

| SYMBOL           | PIN | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P35              | 37  | 8xC51 general purpose I/O port (USB_WAKEUP_N in TDA8030)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| P36/WR           | 38  | external data memory write strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| P37/RD           | 39  | external data memory read strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| XTAL2            | 40  | 12 MHz crystal output; leave open-circuit if an external clock is used                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| XTAL1            | 41  | external 12 MHz crystal connection or input for an external clock signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| V <sub>DDD</sub> | 42  | 3.3 V regulated digital supply voltage output (decouple with 1 μF ceramic capacitor)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| DGND             | 43  | Digital ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| P20/A8           | 44  | 8xC51 general purpose I/O port/address 8 (available for the application)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| P21/A9           | 45  | 8xC51 general purpose I/O port/address 9 (available for the application)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| P22/A10          | 46  | 8xC51 general purpose I/O port/address 10 (available for the application)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| P23/A11          | 47  | 8xC51 general purpose I/O port/address 11 (available for the application)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| P24/A12          | 48  | 8xC51 general purpose I/O port/address 12 (available for the application)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| P25/A13          | 49  | 8xC51 general purpose I/O port/address 13 (USB_MP_C)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| P26/A14          | 50  | 8xC51 general purpose I/O port/address 14 (USB_MP_SEL)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| P27/A15          | 51  | 8xC51 general purpose I/O port/address 15 (ISO_UART_CS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| PSEN             | 52  | Program Store Enable: read strobe to external program memory when executing code from the external program memory; $\overline{PSEN}$ is activated twice each machine cycle except when two $\overline{PSEN}$ activations are skipped during each access to external data memory. $\overline{PSEN}$ is not activated during fetches from internal program memory.                                                                                                                                                                                                       |

| ALE              | 53  | Address Latch Enable/Program Pulse: output pulse for latching the low byte of the address during an access to external memory. In normal operation ALE is emitted at a constant rate of 1/6 the oscillator frequency and can be used for external timing or clocking. It should be noted that one ALE pulse is skipped during each access to external data memory. This pin is also the program pulse input (PROG) during EPROM programming. ALE can be disabled by setting SFR Auxiliary0. With this bit set ALE will be active only during a MOVX instruction.       |

| ĒĀ               | 54  | External Access Enable/Programming Supply Voltage: $\overline{EA}$ must be externally held LOW to enable the device to fetch code from external program memory locations starting with 0000H. If $\overline{EA}$ is held HIGH the device executes from internal program memory unless the program counter contains an address greater than 3FFFH (16 kbytes boundary). This pin also receives the 12.75 V programming supply voltage (V <sub>PP</sub> ) during EPROM programming. If security bit 1 is programmed $\overline{EA}$ will be internally latched on reset. |

| P07/AD7          | 55  | 8xC51 general purpose I/O port/address/data 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| P06/AD6          | 56  | 8xC51 general purpose I/O port/address/data 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| P05/AD5          | 57  | 8xC51 general purpose I/O port/address/data 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| P04/AD4          | 58  | 8xC51 general purpose I/O port/address/data 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| P03/AD3          | 59  | 8xC51 general purpose I/O port/address/data 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| P02/AD2          | 60  | 8xC51 general purpose I/O port/address/data 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| P01/AD1          | 61  | 8xC51 general purpose I/O port/address/data 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| P00/AD0          | 62  | 8xC51 general purpose I/O port/address/data 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| P10              | 63  | 8xC51 general purpose I/O port (USB_INT_MASK)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| P11              | 64  | 8xC51 general purpose I/O port (USB_SOFTCONNECT_INT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

# USB smart card reader (OTP or ROM)

TDA8030; TDA8031

# USB smart card reader (OTP or ROM)

TDA8030; TDA8031

#### 8 FUNCTIONAL DESCRIPTION

Throughout this specification, it is assumed that the reader is aware of ISO7816 and USB norms terminology.

#### 8.1 ISO7816 UART AND ASSOCIATED LOGIC

This section describes how the integrated ISO7816 UART operates, how it can be programmed by means of its control registers and how it is internally interfaced to the embedded microcontroller.

#### 8.1.1 INTERFACE CONTROL

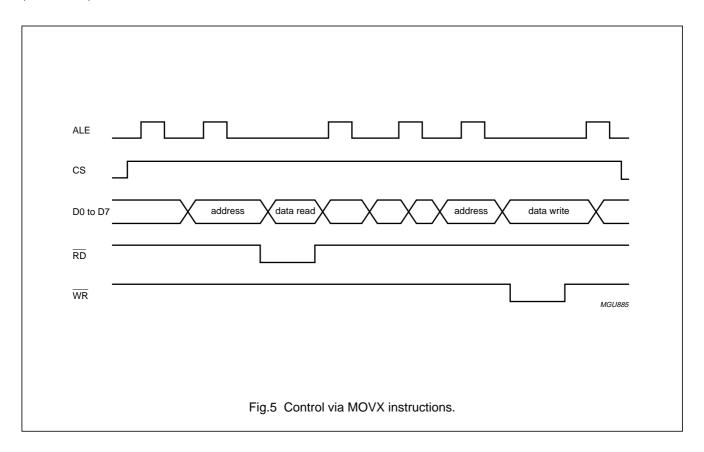

The ISO7816 UART can be controlled via an 8-bit parallel bus. This bus is directly (internally) connected to Port 0 (P07 to P00) of the embedded 83C51 microcontroller.

The registers within the ISO7816 UART may be written to or read from by using the standard 83C51 MOVX instructions. It should be noted, that only if pin P27/A15 is HIGH, can the UART be accessed.

When pin P27/A15 is HIGH, the demultiplexing of address and data is done internally by means of the ALE signal. A LOW pulse on pin P37/RD enables the selected register to be read, a LOW pulse on pin P36/WR enables the selected register to be written to.

The ISO UART interrupt line is directly connected to the microcontrollers External Interrupt 0 input, pin P32/INT0. For that reason, the External Interrupt 0 of the 83C51 microcontroller must be enabled to ensure a proper function.

# USB smart card reader (OTP or ROM)

TDA8030; TDA8031

#### 8.1.2 CONTROL REGISTERS

The TDA8030; TDA8031 has 1 analog interface for 7 contacts cards. The data to and from the cards is fed into an ISO UART.

The Card Select Register (CSR) contains one bit for resetting the ISO UART ( $\overline{RIU}$ , active LOW). This bit is reset after power-on and must be set HIGH before starting any operation. It may be reset by software when necessary.

The following dedicated registers enable the parameters of the ISO UART and the ETU counters to be set:

- Programmable Divider Register (PDR)

- Guard Time Register (GTR)

- Two UART Control Registers (UCR1 and UCR2)

- Clock Configuration Register (CCR)

- Time-Out Configuration Register (TOCR)

- Three Time-Out Registers (TOR1, TOR2 and TOR3).

There is also a dedicated Power Control Register (PCR) for controlling the power to the card.

When the specific parameters of the card have been programmed, the UART may be used with the following registers:

- UART Receive Register (URR)

- UART Transmit Register (UTR)

- UART Status Register (USR)

- Mixed Status Register (MSR).

In the reception mode, a FIFO of 1 to 8 characters may be used and is configured with the FIFO Control Register (FCR). This register may also be used for programming an automatic repetition of NAKed characters in the transmission mode.

The Hardware Status Register (HSR) gives the status of the supply voltage, of the hardware protections and of the card movements.

The USR and HSR give interrupts on pins INT when some of their bits have been changed.

The MSR does not give interrupts and may be used in the polling mode for some operations; when this is the case, the bit Transmit Buffer Empty/Receive Buffer Full (TBE/RBF) within the USR may be masked.

A 24-bit time-out counter may be started to provide an interrupt after a number of ETUs programmed in time-out registers TOR1, TOR2 and TOR3. This will help the microcontroller when processing different real-time tasks (ATR, WWT and BWT etc.), mainly if the microcontrollers and cards clock are asynchronous.

This counter is configured with a Time-Out Counter Configuration register (TOCC) and may be used as a 24-bit or as a 16 + 8-bit counter. Each counter may be set to start counting once data has been written, or on detection of a start bit on the I/O or as autoreload.

#### 8.1.3 GENERAL REGISTERS

### 8.1.3.1 Card select register

The Card Select Register (CSR) is used for resetting the ISO UART.

The bit Reset ISO UART (RIU) must be set to logic 1 by software before any action on the UART. When set to logic 0, this bit resets a large part of the UART registers to their default value; see Table 1. A minimum pulse of 10 ns is needed on RIU. This bit must be reset before any new activation.

Table 1 Card select register (address 00H; write and read); note 1

| 7 | 6 | 5 | 4 | 3   | 2 | 1 | 0 |

|---|---|---|---|-----|---|---|---|

| _ | _ | _ | _ | RIU | _ | _ | _ |

#### Note

1. All bits are cleared after reset.

# USB smart card reader (OTP or ROM)

TDA8030; TDA8031

# 8.1.3.2 Hardware status register

The Hardware Status Register (HSR) gives the status of the chip after a hardware problem has been detected.

Table 2 Hardware Status Register (address 0FH; read only); note 1

| 7 | 6 | 5    | 4    | 3 | 2   | 1 | 0   |

|---|---|------|------|---|-----|---|-----|

| _ | _ | PRTL | SUPL | _ | PRL | - | PTL |

#### Note

1. All bits are cleared after reset.

Table 3 Description of the HSR bits

| BIT     | SYMBOL | DESCRIPTION                                                                                                                                         |

|---------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 7 and 6 | _      | not used                                                                                                                                            |

| 5       | PRTL   | Protection 1: Bit PRTL = 1 when a default has been detected on card reader. Bit PRTL is the OR function of the protection on pins $V_{CC}$ and RST. |

| 4       | SUPL   | Supervisor Latch: Bit SUPL = 1 when the supervisor has been activated.                                                                              |

| 3       | _      | not used                                                                                                                                            |

| 2       | PRL    | Presence Latch: Bit PRL = 1 when a change has occurred on pin PRES.                                                                                 |

| 1       | _      | not used                                                                                                                                            |

| 0       | PTL    | Overheating: Bit PTL = 1 if overheating has occurred.                                                                                               |

When either bits PRTL, PRL or PTL is logic 1, then pin  $\overline{INT0}$  is LOW. The bits having caused the interrupt are cleared when the HSR has been readout (2 × f<sub>int</sub> cycles after the rising edge of  $\overline{RD}$ ).

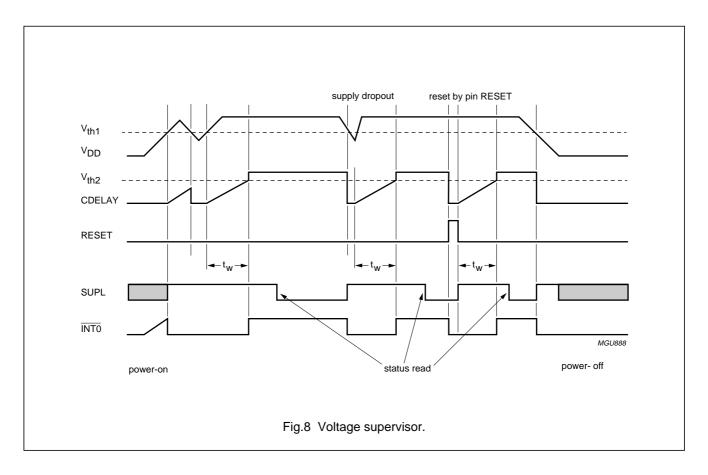

At power-on, or after a supply voltage drop-out, SUPL is set and  $\overline{\text{INT0}}$  is LOW.  $\overline{\text{INT0}}$  will return HIGH at the end of the internal Power-on reset pulse defined by the value of the capacitor connected to pin CDELAY. SUPL will be reset only after a status register readout outside the Power-on reset pulse; see Fig.8.

In the event of emergency deactivation (by PRTL, SUPL, PRL and PTL), bit START will be automatically reset by hardware.

# 8.1.3.3 Time-out registers

The three Time-Out Registers TOR1, TOR2 and TOR3 form a programmable 24-bit ETU counter, or two independant counters (one 16-bit and one 8-bit).

The value to load in TOR1, TOR2 and TOR3 is the number of ETUs to count.

Table 4 Time-out register 1 (address 09H; write only); note 1

| 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|------|------|------|------|------|------|------|------|

| TOL7 | TOL6 | TOL5 | TOL4 | TOL3 | TOL2 | TOL1 | TOL0 |

# Note

1. All bits are cleared after reset.

# USB smart card reader (OTP or ROM)

TDA8030; TDA8031

Table 5 Time-out register 2 (address 0AH; write only); note 1

| 7     | 6     | 5     | 4     | 3     | 2     | 1    | 0    |

|-------|-------|-------|-------|-------|-------|------|------|

| TOL15 | TOL14 | TOL13 | TOL12 | TOL11 | TOL10 | TOL9 | TOL8 |

### Note

1. All bits are cleared after reset.

Table 6 Time-out register 3 (address 0BH; write only); note 1

| 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|-------|-------|-------|-------|-------|-------|-------|-------|

| TOL23 | TOL22 | TOL21 | TOL20 | TOL19 | TOL18 | TOL17 | TOL16 |

# Note

1. All bits are cleared after reset.

# 8.1.3.4 Time-out configuration register

The Time-Out Configuration register (TOCR) is used for setting different configurations of the time-out counter according to Table 8; all other configurations are undefined.

The timers can operate in 3 modes:

- 1. Software triggered

- 2. Start bit triggered

- 3. Autoreload.

Table 7 Time-out configuration register (address 08H; read and write); note 1

| 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|------|------|------|------|------|------|------|------|

| TOC7 | TOC6 | TOC5 | TOC4 | TOC3 | TOC2 | TOC1 | TOC0 |

### Note

1. All bits are cleared after reset.

# USB smart card reader (OTP or ROM)

Table 8 Time-out counter configuration

| TOC VALUE | OPERATING MODE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00H       | All counters are stopped.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 05H       | Counters 2 and 3 are stopped; counter 1 continues to operate in autoreload mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 61H       | Counter 1 is stopped and counters 3 and 2 form a 16-bit counter. Counting the value stored in TOR3 and TOR2 is started after 6H is written in the TOCR. An interrupt is given and bit TO3 is set within the USR when the terminal count is reached. The counter is stopped by writing 00H in the TOCR and will be stopped before reloading a new value in TOR2 and TOR3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 65H       | Counter 1 is an 8-bit autoreload counter and counters 3 and 2 form a 16-bit counter. Counter 1 starts counting the content of TOR1 on the first START bit (reception or transmission) detected on I/O after 65H is written in the TOCR. When Counter 1 reaches its terminal count, an interrupt is given, bit TO1 in the USR is set and the counter automatically restarts the same count until it is stopped. It is not allowed to change the content of TOR1 during a count. Counters 3 and 2 are wired as a single 16-bit counter and starts counting the value TOR3 and TOR2 when 65H is written in the TOCR. When the counter reaches its terminal count, an interrupt is given and bit TO3 is set within the USR. Both counters are stopped when 00H is written in the TOCR. Counters 3 and 2 will be stopped by writing 05H in the TOCR before reloading a new value in TOR2 and TOR3. |

| 68H       | Counters 3, 2 and 1 are wired as a single 24-bit counter. Counting the value stored in TOR3, TOR2 and TOR1 is started after 68H is written in the TOCR. The counter is stopped by writing 00H in the TOCR. It is not allowed to change the content of TOR3, TOR2 and TOR1 within a count.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 7CH       | Counters 3, 2 and 1 are wired as a single 24-bit counter. Counting the value stored in TOR3, TOR2 and TOR1 on the first start bit detected on I/O (reception or transmission) after the value has been written. It is possible to change the content of TOR3, TOR2 and TOR1 during a count; the current count will not be affected and the new count value will be taken into account at the next start bit. The counter is stopped by writing 00H in the TOCR. In this configuration TOR3, TOR2 and TOR1 must not be all zero.                                                                                                                                                                                                                                                                                                                                                               |

| 85H       | Same as 05H, except that all the counters will be stopped at the end of the 12th ETU following the first received start bit detected after 85H has been written in the TOCR.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |