# **TDA9108**

# MONITOR HORIZONTAL PROCESSOR

- POS/NEG SYNC INPUT

- SYNC POLARITY DETECTION

- 2 PLLs CONCEPT

- 2 COMPLEMENTARY OUTPUTS

- DC ADJUSTABLE FREQUENCY

- DC ADJUSTABLE DUTY CYCLE

- X-RAY PROT INPUT

- BACK PORCH CLAMPING PULSE GENER-ATOR

- H-DRIVE INHIBITION WHEN V<sub>S</sub> < V<sub>S</sub> START

# DIP14 (Plastic Package) ORDER CODE: TDA9108

# **DESCRIPTION**

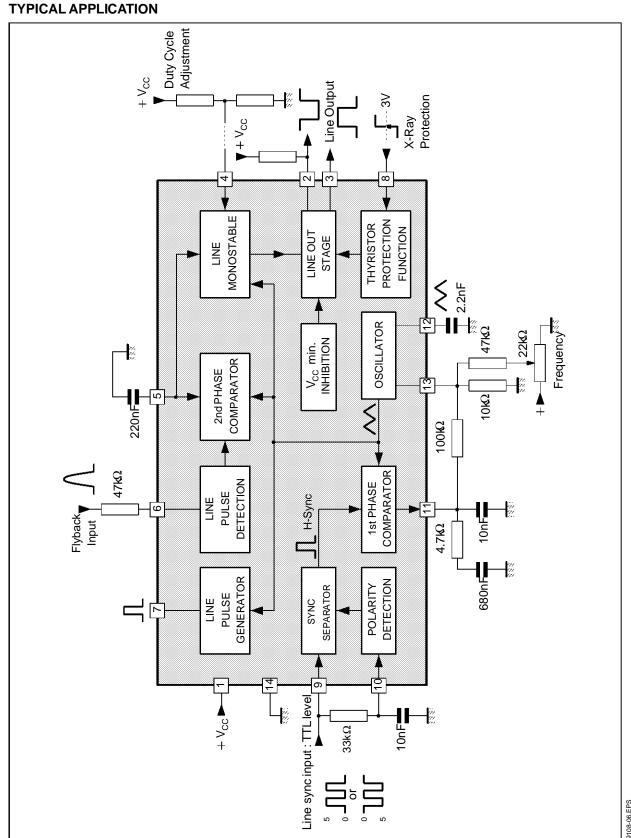

The TDA9108 is a horizontal deflection processor specially designed for monitor applications. The H-drive output duty cycle, the horizontal frequency and the horizontal position are DC adjustable; it accepts both POS/NEG polarity on sync input and delivers polarity information on a dedicated pin. All these features make the device a good choice for multifrequency application. In addition to this, X-ray protection, 2 complementary H-drive output, and a back porch clamping pulse generator are also included. It is a monolithic integrated circuit encapsulated in a 14 lead dual line plastic package.

### **PIN CONNECTIONS**

| 7777                             | N. Land | •                      |

|----------------------------------|---------|------------------------|

| SUPPLY VOLTAGE                   | 1 14    | GROUND                 |

| NEGATIVE H-DRIVE                 | 2 13    | H-FREQUENCY SETTING    |

| POSITIVE H-DRIVE                 | 3 12    | H-OSCILLATOR CAPACITOR |

| DUTY CYCLE ADJUSTMENT            | 4 11    | 1st PLL LOOP FILTER    |

| 2nd PLL LOOP FILTER              | 5 10    | SYNC POLARITY          |

| FLYBACK INPUT                    | 6 9     | SYNC INPUT             |

| BACK PORCH CLAMPING PULSE OUTPUT | 7 8     | X-RAY PROTECTION INPUT |

108-01.EPS

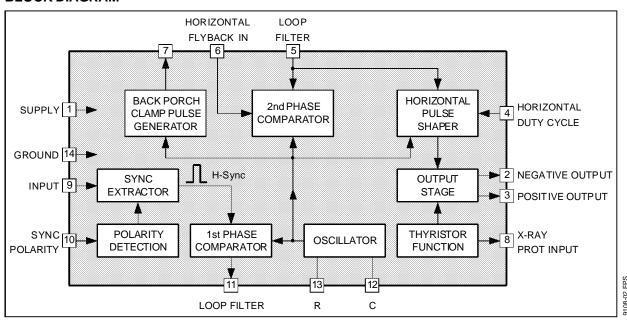

### **BLOCK DIAGRAM**

### **ABSOLUTE MAXIMUM RATINGS**

| Symbol                            | Parameter                                          | Value              | Unit |

|-----------------------------------|----------------------------------------------------|--------------------|------|

| Vs                                | Supply Voltage (Pin 1)                             | 15                 | V    |

| V <sub>2</sub>                    | Voltage at Pin 2                                   | 18                 | V    |

| V <sub>4</sub>                    | Voltage at Pin 4                                   | 0, Vs              | V    |

| V <sub>8</sub>                    | Voltage at Pin 8                                   | 0 , V <sub>S</sub> | V    |

| V <sub>9</sub>                    | Voltage at Pin 9                                   | 0 , V <sub>S</sub> | V    |

| V <sub>10</sub>                   | Voltage at Pin 10                                  | 0, V <sub>S</sub>  | V    |

| l <sub>2</sub>                    | Pin 2 Peak Current                                 | 1                  | А    |

| l <sub>3</sub>                    | Pin 3 Peak Current                                 | 0.5                | Α    |

| l <sub>6</sub>                    | Pin 6 Input Current                                | 30                 | mA   |

| l <sub>7</sub>                    | Pin 7 Input Current                                | 10                 | mA   |

| P <sub>tot</sub>                  | Total Power Dissipation at T <sub>amb</sub> ≤ 70°C | 0.9                | W    |

| T <sub>stg</sub> , T <sub>j</sub> | Storage and Junction Temperature                   | - 40 , + 150       | °C   |

### **THERMAL DATA**

| Symbol                | Parameter                                | Value | Unit |   |

|-----------------------|------------------------------------------|-------|------|---|

| R <sub>th (j-a)</sub> | Thermal Resistance Junction-ambient Max. | 90    | °C/W | Ī |

### **ELECTRICAL CHARACTERISTICS**

(refer to the test circuit,  $V_S = 12V$ ,  $T_A = 25^{\circ}C$ , unless otherwise specified)

| Symbol | Parameter                                                                   | Test conditions    | Min. | Тур. | Max. | Unit |

|--------|-----------------------------------------------------------------------------|--------------------|------|------|------|------|

| Vs     | Supply Voltage Range                                                        |                    | 10   | 12   | 13.2 | V    |

| Is     | Supply Current (Pin 1)                                                      | I <sub>3</sub> = 0 |      | 38   | 55   | mA   |

| Vs     | Supply voltage at which the output pulses (at Pin 2 and 3) are switched off |                    |      |      | 4    | V    |

108-03.TBL

**ELECTRICAL CHARACTERISTICS** (continued) (refer to the test circuit,  $V_S = 12V$ ,  $T_A = 25^{\circ}C$ , unless otherwise specified)

| Symbol                | Parameter                                                                                                                | Test conditions                                                                                | Min.                 | Тур.                | Max.                  | Unit     |  |  |  |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|----------------------|---------------------|-----------------------|----------|--|--|--|

| HORIZONTALSYNC. INPUT |                                                                                                                          |                                                                                                |                      |                     |                       |          |  |  |  |

| V <sub>9SW</sub>      | Sync Input Threshold                                                                                                     | Sync high     Sync Low                                                                         | 2                    |                     | V <sub>S</sub><br>0.8 | V        |  |  |  |

| I <sub>9SW</sub>      | Sync Input Current                                                                                                       | <ul><li>Sync high</li><li>Sync Low</li></ul>                                                   | -20                  | -7                  | 1                     | μA<br>μA |  |  |  |

| SYNC PO               | LARITY SELECTION                                                                                                         |                                                                                                |                      |                     |                       |          |  |  |  |

| V <sub>10th</sub>     | Polarity Selection Threshold                                                                                             |                                                                                                | 2.3                  | 2.5                 | 2.7                   | V        |  |  |  |

|                       | Positive sync on Pin 9 for V <sub>10</sub> < V <sub>10th</sub>                                                           |                                                                                                |                      |                     |                       |          |  |  |  |

|                       | Negative sync on Pin 9 for $V_{10} > V_{10th}$                                                                           |                                                                                                |                      |                     |                       |          |  |  |  |

| I <sub>10</sub>       | Input Current                                                                                                            | V <sub>10</sub> = 2V<br>V <sub>10</sub> = 3V                                                   |                      |                     | 1<br>12               | μA<br>μA |  |  |  |

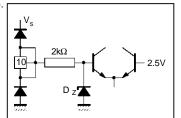

| V <sub>10ZL</sub>     | Low Impedance (2kΩ) Threshold                                                                                            | (see note 1)                                                                                   |                      | 6.3                 |                       | V        |  |  |  |

| X-RAY PR              | OTECTION CIRCUIT                                                                                                         |                                                                                                |                      |                     |                       |          |  |  |  |

| V <sub>8th</sub>      | X-ray Prot Input Threshold Voltage<br>(when $V_8 > V_{8th}$ Pin 2 and 3 are inhibited<br>until $V_S$ is switched off/on) |                                                                                                | 2.6                  | 2.9                 | 3.2                   | V        |  |  |  |

| l <sub>8</sub>        | Input Current                                                                                                            | $V_8 \le 2.5 \\ V_8 \ge 3.3$                                                                   | -0.5                 |                     | 0.5                   | μA<br>μA |  |  |  |

| FLYBACK               | INPUT                                                                                                                    |                                                                                                |                      |                     |                       |          |  |  |  |

| V <sub>6</sub>        | Phase Comparator Input Threshold                                                                                         |                                                                                                |                      |                     | 10                    | V        |  |  |  |

| l <sub>6</sub>        | Input Switching Current                                                                                                  |                                                                                                | 0.1                  |                     |                       | mΑ       |  |  |  |

| OUTPUT                | PULSE                                                                                                                    |                                                                                                |                      |                     |                       |          |  |  |  |

| V <sub>2</sub>        | Saturation Voltage (Pin 3 grounded)                                                                                      | I <sub>2</sub> = 150mA                                                                         |                      | 2.2                 | 3.2                   | V        |  |  |  |

| l <sub>2</sub>        | Output Current (Pin 3 grounded)                                                                                          | V <sub>2</sub> = 5V                                                                            |                      |                     | 150                   | mΑ       |  |  |  |

| V <sub>3</sub>        | Output Voltage (Pin 2 connected to supply)                                                                               | <ul><li>High level (I<sub>3</sub> = 150mA)</li><li>Low level (I<sub>3</sub> = 100mA)</li></ul> | 8.8                  | 9.8<br>1.5          | 10.8<br>2.7           | V<br>V   |  |  |  |

| l <sub>3</sub>        | Output Current Capability                                                                                                | <ul><li>Source</li><li>Sink</li></ul>                                                          |                      |                     | 150<br>100            | mA<br>mA |  |  |  |

| R <sub>3</sub>        | Output Resistance                                                                                                        | At leading edge of output pulse                                                                |                      | 3                   |                       | Ω        |  |  |  |

|                       |                                                                                                                          | At falling edge of output pulse                                                                |                      | 20                  |                       | Ω        |  |  |  |

| DUTY CY               | CLE ADJUSTMENT                                                                                                           |                                                                                                |                      |                     |                       |          |  |  |  |

| tp                    | Horizontal Output Pulse Duty Cycle on Pin 3 (high level, line transistor off time)                                       | f = 31.5kHz<br>Pin 4 not connected                                                             | 26                   | 30                  | 34                    | %        |  |  |  |

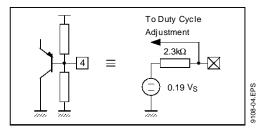

| V <sub>4</sub>        | Voltage on Pin 4 (see note 2)                                                                                            | Pin 4 not connected                                                                            | 0.178 V <sub>S</sub> | 0.19 V <sub>S</sub> | 0.202 V <sub>S</sub>  | V        |  |  |  |

| R <sub>4</sub>        | Serial Equivalent Resistor on Pin 4 (see note 2)                                                                         | Pin 4 not connected                                                                            | 1.7                  | 2.3                 | 2.9                   | kΩ       |  |  |  |

$\textbf{Note 1:} \ \ \text{The voltage} \ on \ \ \text{the polarity detection comparator is clamped by an internal Zener diode} \ \ (V_Z).$ When voltage on Pin 10 reaches Vz, then  $I_{Pin~10} = \frac{V_{Pin~10} - V_Z}{2k\Omega}$

Note 2: Pin 4 internal schematic

**ELECTRICAL CHARACTERISTICS** (continued) (refer to the test circuit,  $V_S = 12V$ ,  $T_A = 25^{\circ}C$ , unless otherwise specified)

| Symbol                          | Parameter                                                                          | Test conditions                                  | Min. | Тур.                            | Max. | Unit             |

|---------------------------------|------------------------------------------------------------------------------------|--------------------------------------------------|------|---------------------------------|------|------------------|

| DUTY CY                         | CLE ADJUSTMENT (continued)                                                         | •                                                | •    |                                 |      |                  |

| t <sub>pADJ</sub>               | Max. Horizontal Output Duty Cycle Range                                            | f = 31.5kHz                                      |      | 50                              |      | %                |

|                                 | (function of V <sub>4</sub> ) $t_p = K4 \cdot \frac{V_4}{V_S}$ (see note 3)        |                                                  |      |                                 |      |                  |

| K4                              | Duty Cycle Adjustment Coefficient                                                  |                                                  | 1.6  | 1.8                             | 2    |                  |

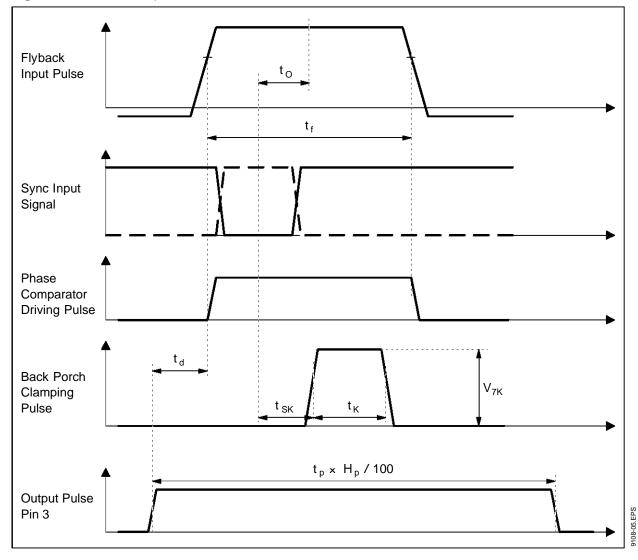

| KEY PULS                        | SE OUTPUT                                                                          |                                                  |      |                                 |      |                  |

| V <sub>7k</sub>                 | Key Pulse Output Peak Voltage (emitter follower)                                   | I <sub>7</sub> = 5mA                             | 4    | 5                               |      | V                |

| V <sub>7</sub> L                | Low Level (outside the key pulse)                                                  |                                                  |      | 0.2                             | 0.5  | V                |

| t <sub>SK</sub>                 | Phase Relation between Trailing Edge of Key Pulse and Middle of Sync. Input Pulse  | f = 31.5kHz<br>Sync width = 2μs                  | 1.1  | 1.5                             | 1.9  | μs               |

| t <sub>K</sub>                  | Key Pulse Duration                                                                 |                                                  | 1.25 | 1.7                             | 2.15 | μs               |

| DSCILLAT                        | OR                                                                                 |                                                  |      |                                 |      |                  |

| V <sub>12</sub>                 | Low Level Threshold Voltage                                                        |                                                  |      | 5.4                             |      | V                |

| V <sub>12</sub>                 | High Level Threshold Voltage                                                       |                                                  |      | 8.2                             |      | V                |

| I <sub>12</sub>                 | Charge Current                                                                     | $R_{13} = 10k\Omega$                             |      | 0.6                             |      | mA               |

| I <sub>12</sub>                 | Discharge Current                                                                  | $R_{13} = 10k\Omega$                             |      | 0.3                             |      | mA               |

| V <sub>13</sub>                 | Reference Voltage on Pin 13                                                        |                                                  | 2.6  | 2.9                             | 3.2  | V                |

| f <sub>O</sub>                  | Free Running Frequency                                                             | $R_{13} = 10k\Omega$<br>$C_{12} = 2.2nF$         | 27   | 30                              | 33   | kHz              |

| f <sub>Max</sub> .              | Maximum Oscillator Frequency                                                       | $R_{13} = 47k\Omega$<br>$C_{12} = 2.2nF$         | 66   |                                 |      | kHz              |

| Jitt.                           | Horizontal Jitter                                                                  | f = 31.5kHz                                      |      | 5                               |      | ns               |

| $\Delta f_{O}$                  | Frequency Control Sensitivity                                                      | $R_{13} = 10k\Omega$                             |      | 100                             |      | <u>Hz</u>        |

| $\Delta I_{13}$                 |                                                                                    | $C_{12} = 2.2nF$                                 |      |                                 |      | μΑ               |

| $\Delta f_{O}$                  | Frequency Change when V <sub>S</sub> Drops to 7.5V                                 |                                                  |      |                                 | -6   | %                |

| PHASE CO                        | OMPARATOR                                                                          |                                                  |      |                                 |      |                  |

| $V_5$                           | Control Voltage Range                                                              |                                                  | 9    | 9.4 to 8.2                      | 2    | V                |

| <b>I</b> 5                      | Peak Control Current                                                               | During flyback pulse                             |      | ± 0.85                          |      | mA               |

| l <sub>5</sub>                  | Input Current (blocked Phase Detector)                                             | Outside flyback pulse                            |      |                                 | 5    | μΑ               |

| t <sub>D</sub>                  | Permissible Delay between Output Pulse Leading Edge and Flyback Pulse Leading Edge |                                                  |      | t <sub>p</sub> - t <sub>f</sub> |      | μs               |

| $\frac{\Delta t}{\Delta t_{D}}$ | Static Control Error                                                               |                                                  |      |                                 | 0.2  | %                |

| SYNC PUI                        | LSE-OSCILLATOR PHASE COMPARATOR                                                    |                                                  | •    |                                 |      |                  |

| V <sub>11</sub>                 | Control Voltage Range                                                              |                                                  |      | 4.6 to 1.4                      | 4    | V                |

| I <sub>11</sub>                 | Control Peak Current                                                               | During Sync Pulse                                |      | ± 2.3                           |      | mA               |

| $\frac{\Delta f}{\Delta t}$     | Phase Lock Loop Gain                                                               | $R_{11-13} = 100k\Omega$                         |      | 4                               |      | <u>kHz</u><br>μs |

| f                               | Catching and Holding Range                                                         | See Typical Application                          |      | ± 700                           |      | Hz               |

| OVERALL                         | PHASE RELATIONSHIP                                                                 |                                                  |      |                                 | •    | •                |

| to                              | Phase Relation between Middle of Flyback Pulse and Middle of Sync. Pulse           | $R_{13} = 10k\Omega$<br>$C_{12} = 2.2nF$         |      | 1.1                             |      | μs               |

|                                 | <u> </u>                                                                           | <del>                                     </del> | +    |                                 |      |                  |

| $\frac{\Delta V_5}{\Delta t_O}$ | Adjustment Sensitivity                                                             |                                                  |      | 130                             |      | <u>mV</u><br>μs  |

Note 3:  $t_d$  must be  $\geq (H_{period} \left[ \frac{t_p}{100} - 0.25 \right] - \frac{t_{fly}}{2})$  in order to have  $\pm$  5% horizontal phase adjustment range.

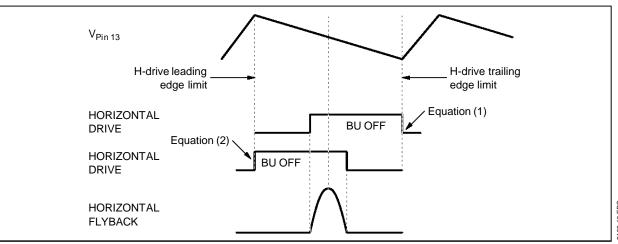

Figure 1: Relation Ship of Main Waveform Phases

### APPLICATION INFORMATION

### Sync Extractor and Polarity Detection

This circuit is able to handle both positive or negative TTL input signal on Pin 9. The voltage on Pin 10 drives an internal inverter providing a constant sync polarity to the 1st phase comparator.

When using a RC network between Pin 9 and 10 (see Typical Application), the IC will adapt itself automatically to positive or negative sync. On an other hand, and in order to simplified the application, the Pin 10 can be connected to ground or supply (through a resistor), in this case the IC will work only with one sync polarity.

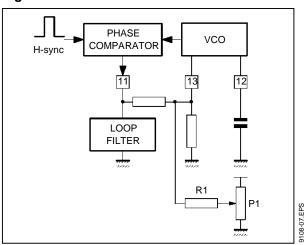

### 1st PLL

It is composed by a phase comparator, the oscillator and an external loop filter (see Figure 2)

- The phase comparator receives the H-sync signal (with positive polarity) and a signal coming from the internal current controlled oscillator. The loop is closed through an external resistor between Pin 11 and 13.

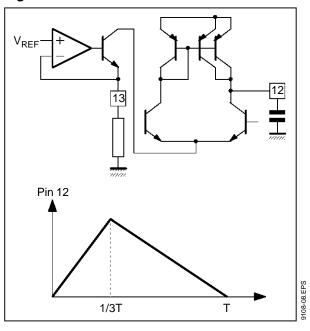

- The oscillatorgenerates a sawtooth waveform on Pin 12 by charging and discharging the external capacitor. The capacitor is discharging by the current flowing Pin 13 and charged by two times this latter (see Figure 3).

The sawtooth is used internally to generate all the required timings.

It is possible to DC control the frequency by adding or substracting a DC current on Pin 13 (see Figure 2).

Figure 2

Figure 3

# 2nd Phase Locked Loop

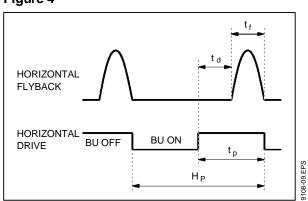

To compensate the delay introduced by the horizontal final stage, the flyback pulse (Pin 6) and the oscillator waveform (Pin 12) are compared in the 2nd phase comparator. The result of the comparison is a control current which, after it has been filtered by the external capacitor on Pin 5, is sent to a phase shifter which adequately regulates the horizontal output pulses phase.

The maximum phase shift allowed is  $t_d = t_p - t_f$  where  $t_f$  is the flyback duration (see Figure 4).

If  $t_d > t_p - t_f$ , then the horizontal output transistor will be tunned on during flyback distroying it.

Figure 4

\_,\_

### **TDA9108**

### X-Ray Protection Input (Pin 8)

When the voltage on this pin becomes higher then 2.9V (typ.), the horizontal outputs are inhibited (Pins 2 and 3) and will remains in this condition until a reset is made on supply voltage (power-off/power-on).

### H-Duty Cycle (see Figure 5)

The output duty cycle is variable between 0 and 50% by varying the voltage on Pin 4.

In order to maintain  $\pm$  5% horizontal phase adjustment possibilities the following equation must be respected.

$$(1) \quad H_{period} \bigg[ \frac{t_p}{100} - 0.25 \bigg] - \frac{t_{fly}}{2} \leq t_d \quad \Rightarrow \quad \text{If not, } t_p \text{ will decrease because of H-drive trailing edge wrong position (phase shifter saturation)}$$

(2)

$$t_d \le 0.36 \, H_p - \frac{t_{fly}}{2} - 2\mu s$$

$\Rightarrow$  If not,  $t_p$  will decrease because of H-drive leading edge wrong position (phase shifter saturation)

### Figure 5

9108-10.EPS

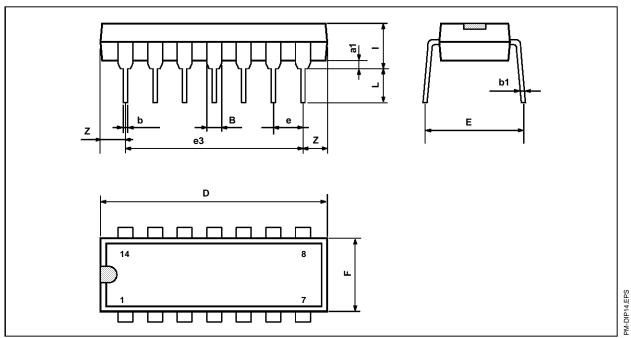

### **PACKAGE MECHANICAL DATA**

14 PINS - PLASTIC DIP

| Dimensions   |      | Millimeters |      |       | Inches |       |

|--------------|------|-------------|------|-------|--------|-------|

| Dillicipions | Min. | Тур.        | Max. | Min.  | Тур.   | Max.  |

| a1           | 0.51 |             |      | 0.020 |        |       |

| В            | 1.39 |             | 1.65 | 0.055 |        | 0.065 |

| b            |      | 0.5         |      |       | 0.020  |       |

| b1           |      | 0.25        |      |       | 0.010  |       |

| D            |      |             | 20   |       |        | 0.787 |

| E            |      | 8.5         |      |       | 0.335  |       |

| е            |      | 2.54        |      |       | 0.100  |       |

| e3           |      | 15.24       |      |       | 0.600  |       |

| F            |      |             | 7.1  |       |        | 0.280 |

| i            |      |             | 5.1  |       |        | 0.201 |

| L            |      | 3.3         |      |       | 0.130  |       |

| Z            | 1.27 |             | 2.54 | 0.050 |        | 0.100 |

Information furnished is believed to be accurate and reliable. However, SGS-THOMSON Microelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No licence is granted by implication or otherwise under any patent or patent rights of SGS-THOMSON Microelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. SGS-THOMSON Microelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of SGS-THOMSON Microelectronics.

© 1994 SGS-THOMSON Microelectronics - All Rights Reserved

Purchase of I $^{\circ}$ C Components of SGS-THOMSON Microelectronics, conveys a license under the Philips I $^{\circ}$ C Patent. Rights to use these components in a I $^{\circ}$ C system, is granted provided that the system conforms to the I $^{\circ}$ C Standard Specifications as defined by Philips.

### SGS-THOMSON Microelectronics GROUP OF COMPANIES

Australia - Brazil - China - France - Germany - Hong Kong - Italy - Japan - Korea - Malaysia - Malta - Morocco The Netherlands - Singapore - Spain - Sweden - Switzerland - Taiwan - Thailand - United Kingdom - U.S.A.