# **THS8083**

Triple 8-Bit, 80 MSPS, 3.3-V Video and Graphics Digitizer With Digital PLL

# Data Manual

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Customers are responsible for their applications using TI components.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, license, warranty or endorsement thereof.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations and notices. Representation or reproduction of this information with alteration voids all warranties provided for an associated TI product or service, is an unfair and deceptive business practice, and TI is not responsible nor liable for any such use.

Resale of TI's products or services with <u>statements different from or beyond the parameters</u> stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service, is an unfair and deceptive business practice, and TI is not responsible nor liable for any such use.

Also see: Standard Terms and Conditions of Sale for Semiconductor Products, www.ti.com/sc/docs/stdterms.htm

Mailing Address:

Texas Instruments Post Office Box 655303 Dallas, Texas 75265

# **Contents**

| Se | ection | Title                               |       |  |  |  |  |  |  |  |

|----|--------|-------------------------------------|-------|--|--|--|--|--|--|--|

| 1  | Introd | duction                             | . 1–1 |  |  |  |  |  |  |  |

|    | 1.1    | Features                            | . 1–1 |  |  |  |  |  |  |  |

|    | 1.2    | Functional Block Diagram            | . 1–3 |  |  |  |  |  |  |  |

|    | 1.3    | Terminal Assignments                | . 1–4 |  |  |  |  |  |  |  |

|    | 1.4    | Ordering Information                | . 1–4 |  |  |  |  |  |  |  |

|    | 1.5    | Abbreviations Used in This Document | . 1–5 |  |  |  |  |  |  |  |

|    | 1.6    | Conventions                         | . 1–5 |  |  |  |  |  |  |  |

|    | 1.7    | THS8083 Terminal Functions Order    | . 1–5 |  |  |  |  |  |  |  |

| 2  | Funct  | tional Description                  | . 2–1 |  |  |  |  |  |  |  |

|    | 2.1    | Analog Channel                      |       |  |  |  |  |  |  |  |

|    | 2.2    | Clamping Circuit                    | . 2–1 |  |  |  |  |  |  |  |

|    | 2.3    | Composite Sync Slicer               |       |  |  |  |  |  |  |  |

|    | 2.4    | Programmable Gain Amplifier (PGA)   | . 2–4 |  |  |  |  |  |  |  |

|    | 2.5    | A/D Converter                       |       |  |  |  |  |  |  |  |

|    | 2.6    | PLL                                 |       |  |  |  |  |  |  |  |

|    |        | 2.6.1 Analog PLL                    |       |  |  |  |  |  |  |  |

|    |        | 2.6.2 Digital PLL                   |       |  |  |  |  |  |  |  |

|    | 2.7    | Output Formatter                    |       |  |  |  |  |  |  |  |

|    | 2.8    | Power Down                          |       |  |  |  |  |  |  |  |

|    | 2.9    | Input Mode Detection                |       |  |  |  |  |  |  |  |

| _  | 2.10   | Test Mode                           |       |  |  |  |  |  |  |  |

| 3  | _      | ster Definition                     |       |  |  |  |  |  |  |  |

|    | 3.1    | I <sup>2</sup> C Protocol           |       |  |  |  |  |  |  |  |

|    |        | 3.1.1 Write Format                  |       |  |  |  |  |  |  |  |

|    |        | 3.1.2 Read Format                   |       |  |  |  |  |  |  |  |

|    | 3.2    | Register Description                |       |  |  |  |  |  |  |  |

|    |        | 3.2.1 Register Name: TERM_CNT_0     |       |  |  |  |  |  |  |  |

|    |        | 3.2.2 Register Name: TERM_CNT_1     |       |  |  |  |  |  |  |  |

|    |        | 3.2.3 Register Name: NOM_INC_0      |       |  |  |  |  |  |  |  |

|    |        | 3.2.4 Register Name: NOM_INC_1      |       |  |  |  |  |  |  |  |

|    |        | 3.2.5 Register Name: NOM_INC_2      |       |  |  |  |  |  |  |  |

|    |        | 3.2.6 Register Name: NOM_INC_3      |       |  |  |  |  |  |  |  |

|    |        | 3.2.7 Register Name: NOM_INC_4      |       |  |  |  |  |  |  |  |

|    |        | 3.2.8 Register Name: VCODIV         |       |  |  |  |  |  |  |  |

|    |        | 3.2.10 Register Name: PHASESEL      |       |  |  |  |  |  |  |  |

|    |        | 3.2.10 Register Name: PLLFILT       |       |  |  |  |  |  |  |  |

|    |        | 3.2.11 Register Name. FLLFILL       | . 5–7 |  |  |  |  |  |  |  |

|   |     | 3.2.12    | Register Name:    | HS_WIDTH        | 3–7  |

|---|-----|-----------|-------------------|-----------------|------|

|   |     | 3.2.13    | Register Name:    | VS_WIDTH        | 3–8  |

|   |     | 3.2.14    | Register Name:    | SYNC_CTRL       | 3–8  |

|   |     | 3.2.15    | Register Name:    | LD_THRES        | 3–8  |

|   |     | 3.2.16    | -                 | PLL_CTRL        |      |

|   |     | 3.2.17    | Register Name:    | HS_COUNT_0      | 3–9  |

|   |     | 3.2.18    | Register Name:    | HS_COUNT_1      | 3–10 |

|   |     | 3.2.19    | Register Name:    | VS_COUNT_0      | 3–10 |

|   |     | 3.2.20    | Register Name:    | VS_COUNT_1      | 3–10 |

|   |     | 3.2.21    | Register Name:    | DTO_INC_0       | 3–10 |

|   |     | 3.2.22    | Register Name:    | DTO_INC_1       | 3–10 |

|   |     | 3.2.23    | Register Name:    | DTO_INC_2       | 3–11 |

|   |     | 3.2.24    | Register Name:    | DTO_INC_3       | 3–11 |

|   |     | 3.2.25    | Register Name:    | DTO_INC_4       | 3–11 |

|   |     | 3.2.26    | Register Name:    | SYNC_DETECT     | 3–11 |

|   |     | 3.2.27    | •                 | CLP_CTRL        |      |

|   |     | 3.2.28    | Register Name:    | CLP_START_0     | 3–12 |

|   |     | 3.2.29    | Register Name:    | CLP_START_1     | 3–12 |

|   |     | 3.2.30    | Register Name:    | CLP_STOP_0      | 3–12 |

|   |     | 3.2.31    | Register Name:    | CLP_STOP_1      | 3–12 |

|   |     | 3.2.32    | •                 | CH1_CLP         |      |

|   |     | 3.2.33    | Register Name:    | CH1_COARSE      | 3–13 |

|   |     | 3.2.34    | Register Name:    | CH1_FINE        | 3–13 |

|   |     | 3.2.35    | •                 | CH2_CLP         |      |

|   |     | 3.2.36    | •                 | CH2_COARSE      |      |

|   |     | 3.2.37    | •                 | CH2_FINE        |      |

|   |     | 3.2.38    | -                 | CH3_CLP         |      |

|   |     | 3.2.39    | •                 | CH3_COARSE      |      |

|   |     | 3.2.40    | Register Name:    | CH3_FINE        | 3–14 |

|   |     | 3.2.41    | Register Name:    | PIX_TRAP_0      | 3–14 |

|   |     | 3.2.42    | _                 | PIX_TRAP_1      |      |

|   |     | 3.2.43    | -                 | PWDN_CTRL       |      |

|   |     | 3.2.44    | •                 | AUX_CTRL        |      |

|   |     | 3.2.45    | •                 | CH1_RDBK        |      |

|   |     | 3.2.46    | •                 | CH2_RDBK        |      |

|   |     | 3.2.47    | •                 | CH3_RDBK        |      |

|   |     | 3.2.48    | •                 | OFM_CTRL        |      |

| 4 |     |           |                   | nation          | 4–1  |

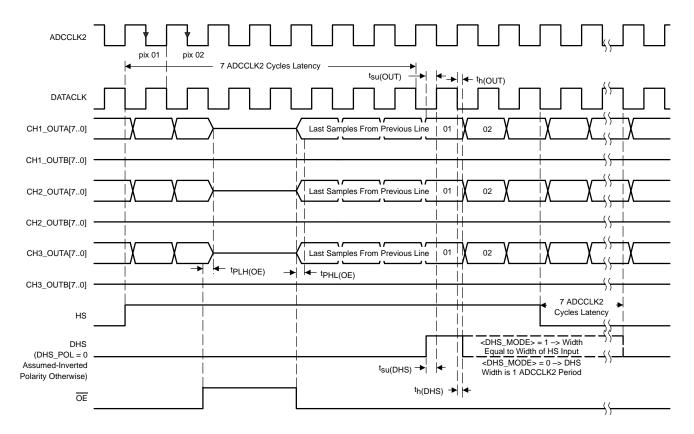

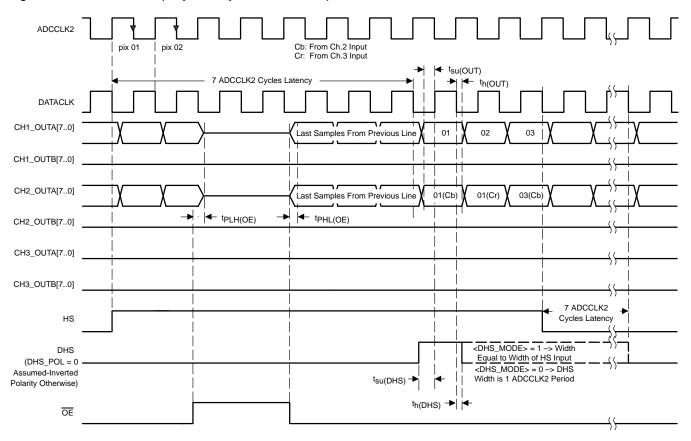

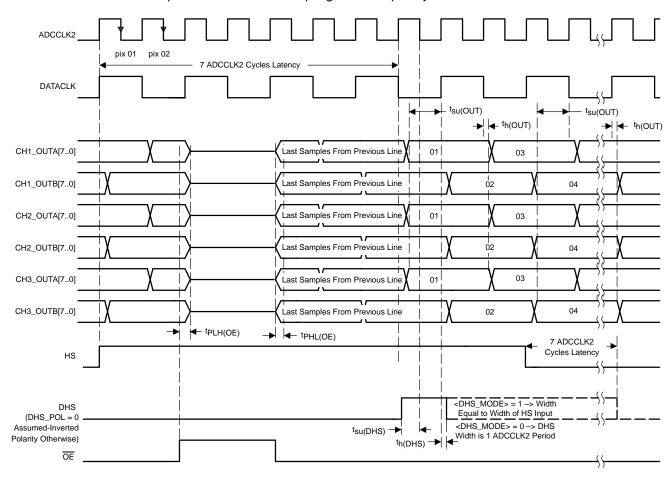

|   | 4.1 | -         | -                 | arallel Mode    |      |

|   | 4.2 | _         | -                 | arallel Mode    |      |

|   | 4.3 | _         | -                 | nterleaved Mode | 4–3  |

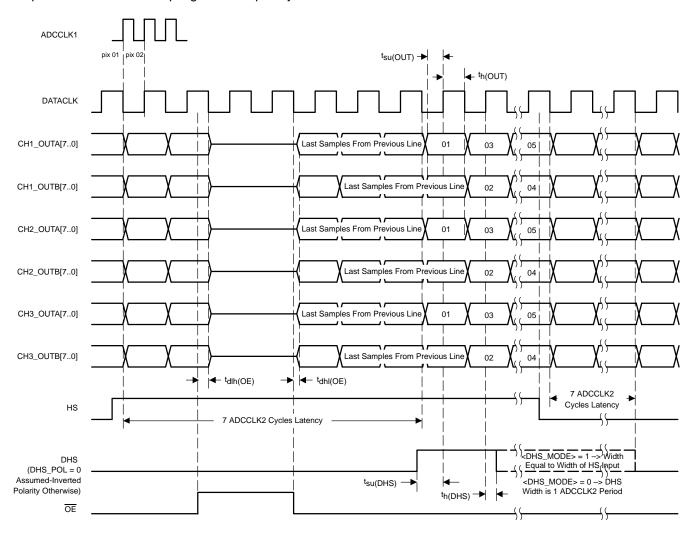

|   | 4.4 | Timing Di | ıagram – 48-Bit P | arallel Mode    | 4–4  |

|   |     |           |                   |                 |      |

| 5  | Electri | ical Speci | fication                                                                                                  | 5–1 |

|----|---------|------------|-----------------------------------------------------------------------------------------------------------|-----|

|    | 5.1     | Definition | of Test Conditions                                                                                        | 5–1 |

|    | 5.2     |            | Maximum Ratings Over Operating Free-Air cure Range                                                        | 5–2 |

|    | 5.3     | Recomm     | ended Operating Conditions Over Operating Free-Air<br>cure Range, T <sub>A</sub> = 0°C to 70°C            | 5–2 |

|    |         | 5.3.1      | Power Supply                                                                                              | 5–2 |

|    |         | 5.3.2      | Analog and Reference Inputs                                                                               | 5–2 |

|    |         | 5.3.3      | Digital Inputs                                                                                            | 5–2 |

|    | 5.4     |            | Characteristics Over Recommended Operating Temperature Range, T <sub>A</sub> = 0°C to 70°C                | 5–3 |

|    |         | 5.4.1      | Power Supply                                                                                              | 5–3 |

|    |         | 5.4.2      | Digital Logic Inputs (HS, VS, S <u>CL</u> , <u>SDA, I2</u> CA, XTL1_MCLK, EXT_ADCCLK, OE, RESET, EXT_CLP) | 5–3 |

|    |         | 5.4.3      | Logic Outputs (SDA, CHn_OUTA[70], CHn_OUTB[70], DTOCLK3, ADCCLK2, DATACLK1, DHS, LOCK)                    | 5–3 |

|    |         | 5.4.4      | I <sup>2</sup> C Interface                                                                                | 5–4 |

|    |         | 5.4.5      | ADC Channel                                                                                               | 5–4 |

|    |         | 5.4.6      | Coarse PGA                                                                                                | 5–5 |

|    |         | 5.4.7      | Fine PGA                                                                                                  | 5–5 |

|    |         | 5.4.8      | Output Formatter/Timing Requirements                                                                      | 5–6 |

|    |         | 5.4.9      | PLL                                                                                                       | 5–6 |

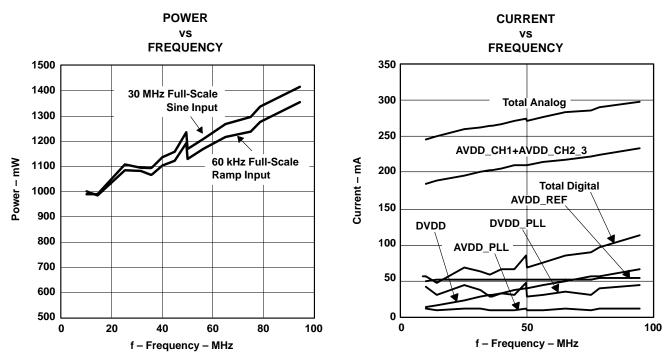

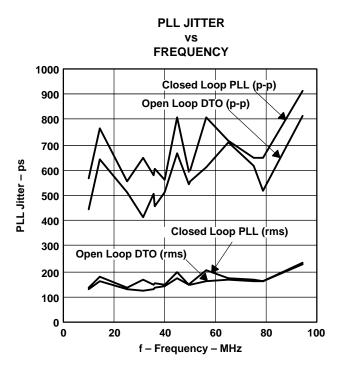

|    |         | 5.4.10     | Typical Plots                                                                                             | 5–7 |

| 6  | Applic  | ation Info | ormation                                                                                                  | 6–1 |

|    | 6.1     | Designing  | g With PowerPAD™                                                                                          | 6–1 |

| 7  | Mecha   | nical Dat  | a                                                                                                         | 7–1 |

| Аp | •       |            |                                                                                                           | A-1 |

|    | A 1     | PH Form    | nula and Register Settings                                                                                | A-1 |

# **List of Illustrations**

| Figu | ure Title                                              | Page |

|------|--------------------------------------------------------|------|

| 2–1  | Analog Channel Architecture                            | 2–1  |

| 2–2  | Bottom-Level Clamping                                  | 2–2  |

| 2–3  | Mid-Level Clamping                                     | 2–2  |

| 2–4  | Using THS8083 With a Composite Sync                    | 2–3  |

| 2–5  | Analog PLL                                             | 2–5  |

| 2–6  | Digital PLL                                            | 2–7  |

| 2–7  | Output Formatter                                       | 2–8  |

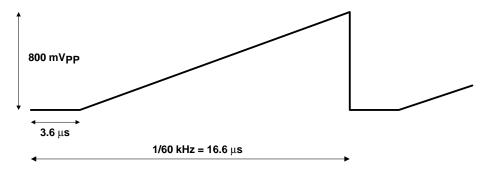

| 5–1  | Input Test Waveform                                    | 5–1  |

| 5–2  | Power Consumption                                      | 5–7  |

| 5–3  | PLL Jitter                                             | 5–8  |

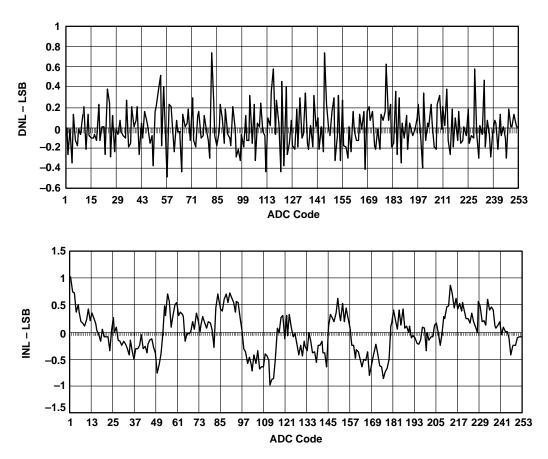

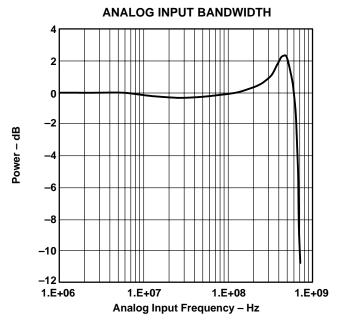

| 5–4  | Linearity of AGY Channel at 80 MSPS (external clock)   | 5–8  |

| 5–5  | Analog Input Bandwidth                                 | 5–9  |

|      |                                                        |      |

|      | List of Tables                                         |      |

| Tabi | le Title                                               | Page |

| 3–1  | I <sup>2</sup> C Register Map                          | 3–3  |

| 3–2  | Output Formatter                                       | 3–16 |

| 6–1  | Junction-Ambient and Junction-Case Thermal Resistances | 6–1  |

# 1 Introduction

The THS8083 is a solution for digitizing video and graphic signals in RGB or YUV/YCbCr color spaces. The device supports pixel rates up to 80 MHz. Therefore, it can be used for PC graphics digitizing up to the VESA standard of XGA (1024 X 768) resolution at 75 Hz screen refresh rate, and in video environments for the digitizing of digital TV formats, including HDTV.

The THS8083 is powered from a single 3.3-V supply and integrates a triple high-performance A/D converter with clamping functions and variable gain, independently programmable for each channel. Separate clamping ranges are provided for RGB and YUV operation modes of the device. The clamp timing window is provided by an external pulse or can be generated internally.

The programmable gain amplifiers consist of coarse and fine gain control blocks. The THS8083 includes slicing circuitry on the Y or G input to support sync-on-green or sync-on-luminance extraction. The THS8083 further contains a completely digital PLL block, consisting of phase-frequency detector (PFD), discrete time oscillator (DTO) and programmable divider to generate the (sampling) clock from the incoming horizontal sync (HS) signal, depending on the incoming video resolution. Any pixel rate can be generated in the 10-80 MHz range. Moreover, the output phase of the synthesized clock can be controlled with sub-pixel accuracy (31 uniform settings).

Programmable time constants allow the PLL loop bandwidth to be changed by the integrated PLL loop filter. Alternatively, the user may bypass the PLL when an external pixel clock is available. Even then the DTO synthesized clock is still available externally and can therefore be used in other parts of the (graphics) system. Extensive PLL and input monitoring functions are integrated for typical functionality required in LCD/DMD monitor/projection systems (input format detection, autocalibration).

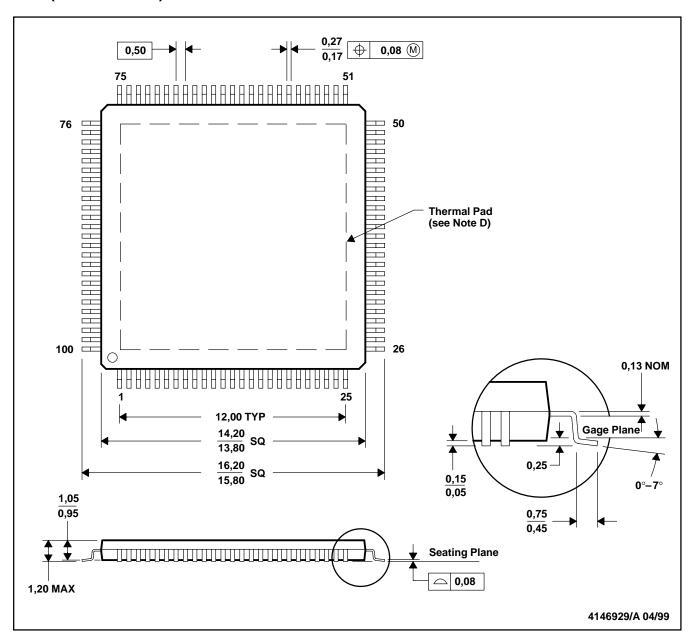

All programming of the part is done via an industry-standard normal/fast I<sup>2</sup>C interface, which supports both reading and writing of register settings. The THS8083 is available in a space-saving TQFP 100-pin PowerPAD™ package.

#### 1.1 Features

The THS8083 supports the following features:

- Analog Channels Three digitizing channels, each with independently controllable clamp, PGA, and ADC.

- Clamp: 256-step programmable RGB or YUV clamping during external or internal clamp timing window

- PGA: 6-bit coarse/5-bit fine programmable gain amplifier

- ADC: 8 bit 80 MSPS A/D converter

- Composite sync: Integrated sync-on-green/sync-on-luminance extraction

- Support for ac-coupled input signals

#### PLL

- Fully integrated digital PLL (including loop filter) for pixel clock generation

- 10-80 MHz pixel clock generation from reference input

- Adjustable PLL loop bandwidth for minimum jitter or fast acquisition/wide capture range modes

- 5-bit programmable subpixel accuracy positioning of sampling phase

- Noise gates on HS input to avoid false PLL updating

### Output Formatter

- Single and double pixel width output data bus for reduced board clock frequency and EMI

- Support for 4:4:4 and 4:2:2 (ITU.BT-601 style) output modes to reduce board traces to video ASICs

- Dedicated DATACLK1 output for easy latching of output data

#### System

- Industry-standard normal/fast I<sup>2</sup>C interface with register readback capability

- Support for input format detection via integrated monitoring of HS, VS, and pixel clock frequencies

- Support for multidevice operation (master/slave operation for SXGA resolution)

- Space-saving TQFP-100 pin package

- Thermally-enhanced PowerPAD package for better heat dissipation

### Applications

- LCD desktop monitors and LCD or DMD-based projection systems

- Videoconferencing

- PCTV set-top boxes, digital TV sets, and multimedia cards

- Scan rate/image resolution converters

- Video/graphics digitizing equipment (RGB or YUV-based)

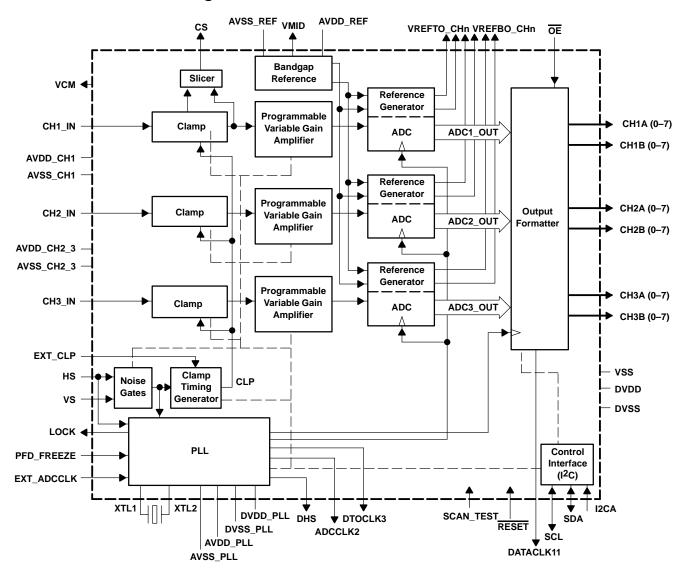

# 1.2 Functional Block Diagram

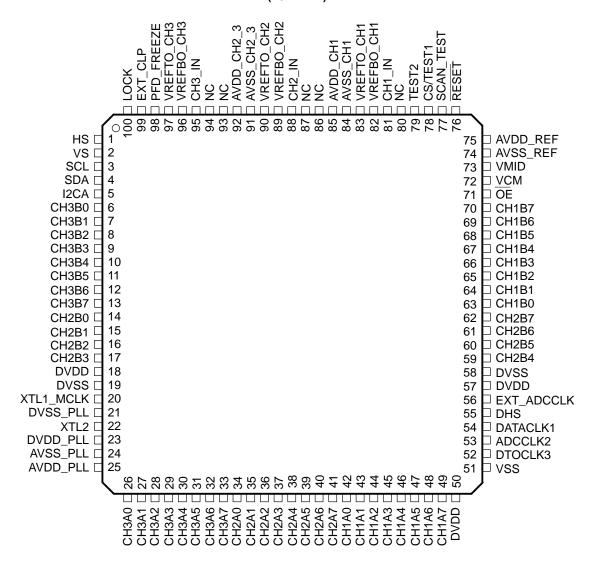

# 1.3 Terminal Assignments

# TQFP PowerPAD™ PACKAGE (TOP VIEW)

# 1.4 Ordering Information

| TA                      | PACKAGED DEVICES |  |  |

|-------------------------|------------------|--|--|

|                         | TQFP-100         |  |  |

| Maximum clock frequency | 80 MSPS          |  |  |

| 0°C to 70°C             | THS8083CPZP      |  |  |

#### 1.5 Abbreviations Used in This Document

| PGA                                        | Programmable gain amplifier |  |  |  |  |  |

|--------------------------------------------|-----------------------------|--|--|--|--|--|

| PLL                                        | Phase-locked loop           |  |  |  |  |  |

| I <sup>2</sup> C Inter-IC interface        |                             |  |  |  |  |  |

| EMI Electro-magnetic interference          |                             |  |  |  |  |  |

| NTSC National Television Systems Committee |                             |  |  |  |  |  |

| PAL                                        | Phase alternating line      |  |  |  |  |  |

| DTV                                        | Digital TV                  |  |  |  |  |  |

| VBI                                        | Vertical blanking interval  |  |  |  |  |  |

| CS                                         | Composite sync              |  |  |  |  |  |

#### 1.6 Conventions

Throughout this document, the term YUV refers to a video/graphics signal, consisting of three components, of which one component (Y) has its blanking level corresponding to the bottom level of the video signal range. The other two components (U&V) have their blanking level at the mid-scale of the video signal range (since U&V are color difference signals and thus, can go positive or negative with respect to blanking).

YUV, therefore should not be restricted to NTSC/PAL component formats, but also includes baseband component video formats used in DTV that should in a strict sense be denoted as analog YCbCr or YPbPr.

The term RGB refers to a video/graphics signal, consisting of three components, of which all components have their blanking level corresponding to the bottom level of the video signal range. Therefore, it relates to both RGB PC formats as well as red-green-blue video component signals, sometimes denoted as GBR instead of RGB in video broadcast environments.

#### 1.7 THS8083 Terminal Functions Order

| TERMINAL   |                |        |       |                                                                   |  |  |  |  |  |

|------------|----------------|--------|-------|-------------------------------------------------------------------|--|--|--|--|--|

| NAME       | NO.            | I/O/B† | TYPE‡ | DESCRIPTION                                                       |  |  |  |  |  |

|            | POWER SUPPLIES |        |       |                                                                   |  |  |  |  |  |

| AVSS_PLL   | 24             | I      | Α     | Analog ground for PLL (XTL oscillator and analog PLL)             |  |  |  |  |  |

| AVDD_PLL   | 25             | I      | Α     | Analog supply (3.3 V) for analog PLL                              |  |  |  |  |  |

| DVSS_PLL   | 21             | I      | Α     | Digital ground for digital PLL                                    |  |  |  |  |  |

| DVDD_PLL   | 23             | I      | Α     | Digital supply (3.3 V) for digital PLL                            |  |  |  |  |  |

| AVSS_CH1   | 84             | I      | Α     | Analog ground for A/D channel 1                                   |  |  |  |  |  |

| AVDD_CH1   | 85             | I      | Α     | Analog supply (3.3 V) for A/D channel 1                           |  |  |  |  |  |

| AVSS_CH2_3 | 91             | I      | Α     | Analog ground for A/D channel 2 and channel 3                     |  |  |  |  |  |

| AVDD_CH2_3 | 92             | I      | Α     | Analog supply (3.3 V) for A/D channel 2 and channel 3             |  |  |  |  |  |

| DVDD       | 18, 50, 57     | I      | Α     | Digital supply for all logic, except digital PLL                  |  |  |  |  |  |

| DVSS       | 19, 58         | I      | Α     | Digital ground for all logic, except digital PLL                  |  |  |  |  |  |

| VSS        | 51             | I      | Α     | Substrate ground                                                  |  |  |  |  |  |

| AVDD_REF   | 75             | I      | Α     | Analog supply (3.3 V) for voltage and current reference generator |  |  |  |  |  |

| AVSS_REF   | 74             | I      | Α     | Analog ground (3.3 V) for voltage and current reference generator |  |  |  |  |  |

$<sup>\</sup>dagger$  I = input to device: O = output from device B = bidirectional

$<sup>\</sup>ddagger A = \text{analog pin: } D = \text{digital pin}$

# 1.7 THS8083 Terminal Functions Order (Continued)

| TERMINA    |     |                    |       |                                                                                                                                                                                                                            |  |  |  |  |

|------------|-----|--------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| NAME       | NO. | I/O/B <sub>†</sub> | TYPE‡ | DESCRIPTION                                                                                                                                                                                                                |  |  |  |  |

|            |     | <u> </u>           |       | CLOCK I/O                                                                                                                                                                                                                  |  |  |  |  |

| XTL1_MCLK  | 20  | I                  | Α     | Master crystal connection 1 (connects 14.318-MHz crystal) or master clock input (at 14.318 MHz)                                                                                                                            |  |  |  |  |

| XTL2       | 22  | 0                  | Α     | Master crystal connection 2 (connects 14.318-MHz crystal)                                                                                                                                                                  |  |  |  |  |

| DATACLK1   | 54  | 0                  | D     | 1 <sup>St</sup> clock output: DATACLK1 This is a clock of which the rising edge can be used by an external device to clock in THS8083 output data in all modes (see output timing diagrams in Section 4 for more details). |  |  |  |  |

| ADCCLK2    | 53  | 0                  | D     | 2 <sup>nd</sup> clock output: ADCCLK<br>This clock output is equal to the clock of the ADC converter, optionally inverted and/o<br>divided-by-2.                                                                           |  |  |  |  |

| DTOCLK3    | 52  | 0                  | D     | 3 <sup>rd</sup> clock output: DTOCLK. This clock output is the output of the DTO.                                                                                                                                          |  |  |  |  |

| EXT_ADCCLK | 56  | I                  | D     | External clock input for A/D channels, at pixel clock frequency                                                                                                                                                            |  |  |  |  |

|            |     | -                  | -     | ANALOG SIGNAL I/O                                                                                                                                                                                                          |  |  |  |  |

| CH1_IN     | 81  | I                  | Α     | Analog input channel 1. Since this channel includes the composite sync slicer and is not downsampled in 4:2:2 mode, this channel should be used for green or luminance input, if any of these features are used.           |  |  |  |  |

| CH2_IN     | 88  | I                  | Α     | Analog input channel 2. In YUV 4:2:2 sampling mode, Pb should be connected to this input to generate a ITU.BT-601 style output.                                                                                            |  |  |  |  |

| CH3_IN     | 95  | I                  | А     | Analog input channel 3. In YUV 4:2:2 sampling mode, Pr should be connected to this input generate a ITU.BT-601 style output.                                                                                               |  |  |  |  |

| VREFBO_CH1 | 82  | В                  | Α     | Reference voltage bottom output channel 1. In normal operation: output. For a specific configuration, this terminal becomes an input terminal (see Powerdown section in Functional Description).                           |  |  |  |  |

| VREFTO_CH1 | 83  | В                  | Α     | Reference voltage top output channel 1. In normal operation it is an output. For a specific configuration, this terminal becomes an input terminal (see Powerdown section in Functional Description).                      |  |  |  |  |

| VREFBO_CH2 | 89  | В                  | Α     | Reference voltage bottom output channel 2. See VREFBO_CH1.                                                                                                                                                                 |  |  |  |  |

| VREFTO_CH2 | 90  | В                  | Α     | Reference voltage top output channel 2. See VREFTO_CH1.                                                                                                                                                                    |  |  |  |  |

| VREFBO_CH3 | 96  | В                  | Α     | Reference voltage bottom output channel 3. See VREFBO_CH1.                                                                                                                                                                 |  |  |  |  |

| VREFTO_CH3 | 97  | В                  | Α     | Reference voltage top output channel 3. See VREFTO_CH1.                                                                                                                                                                    |  |  |  |  |

| VMID       | 73  | В                  | Α     | Midlevel input range (input common mode). In normal operation it is an output. For a specific configuration, this terminal becomes an input terminal (see Powerdown section in Functional Description).                    |  |  |  |  |

| VCM        | 72  | 0                  | Α     | Common mode voltage output (approximately 1.5 V)                                                                                                                                                                           |  |  |  |  |

|            |     |                    |       | DIGITAL SIGNAL I/O                                                                                                                                                                                                         |  |  |  |  |

| CH1A0      | 42  | 0                  | D     | Display output channel 1, bus A, bit 0 (LSB)                                                                                                                                                                               |  |  |  |  |

| CH1A1      | 43  | 0                  | D     | Display output channel 1, bus A, bit 1                                                                                                                                                                                     |  |  |  |  |

| CH1A2      | 44  | 0                  | D     | Display output channel 1, bus A, bit 2                                                                                                                                                                                     |  |  |  |  |

| CH1A3      | 45  | 0                  | D     | Display output channel 1, bus A, bit 3                                                                                                                                                                                     |  |  |  |  |

| CH1A4      | 46  | 0                  | D     | Display output channel 1, bus A, bit 4                                                                                                                                                                                     |  |  |  |  |

| CH1A5      | 47  | 0                  | D     | Display output channel 1, bus A, bit 5                                                                                                                                                                                     |  |  |  |  |

| CH1A6      | 48  | 0                  | D     | Display output channel 1, bus A, bit 6                                                                                                                                                                                     |  |  |  |  |

| CH1A7      | 49  | 0                  | D     | Display output channel 1, bus A, bit 7 (MSB)                                                                                                                                                                               |  |  |  |  |

| CH1B0      | 63  | 0                  | D     | Display output channel 1, bus B, bit 0 (LSB)                                                                                                                                                                               |  |  |  |  |

| CH1B1      | 64  | 0                  | D     | Display output channel 1, bus B, bit 1                                                                                                                                                                                     |  |  |  |  |

<sup>†</sup> I = input to device: O = output from device B = bidirectional ‡ A = analog pin: D = digital pin

# 1.7 THS8083 Terminal Functions Order (Continued)

| TERMINAL<br>NAME NO. |    |        |       | DESCRIPTION                                  |  |  |  |

|----------------------|----|--------|-------|----------------------------------------------|--|--|--|

|                      |    | I/O/B† | TYPE‡ |                                              |  |  |  |

|                      |    |        |       | DIGITAL SIGNAL I/O (Continued)               |  |  |  |

| CH1B2                | 65 | 0      | D     | Display output channel 1, bus B, bit 2       |  |  |  |

| CH1B3                | 66 | 0      | D     | Display output channel 1, bus B, bit 3       |  |  |  |

| CH1B4                | 67 | 0      | D     | Display output channel 1, bus B, bit 4       |  |  |  |

| CH1B5                | 68 | 0      | D     | Display output channel 1, bus B, bit 5       |  |  |  |

| CH1B6                | 69 | 0      | D     | Display output channel 1, bus B, bit 6       |  |  |  |

| CH1B7                | 70 | 0      | D     | Display output channel 1, bus B, bit 7 (MSB) |  |  |  |

| CH2A0                | 34 | 0      | D     | Display output channel 2, bus A, bit 0 (LSB) |  |  |  |

| CH2A1                | 35 | 0      | D     | Display output channel 2, bus A, bit 1       |  |  |  |

| CH2A2                | 36 | 0      | D     | Display output channel 2, bus A, bit 2       |  |  |  |

| CH2A3                | 37 | 0      | D     | Display output channel 2, bus A, bit 3       |  |  |  |

| CH2A4                | 38 | 0      | D     | Display output channel 2, bus A, bit 4       |  |  |  |

| CH2A5                | 39 | 0      | D     | Display output channel 2, bus A, bit 5       |  |  |  |

| CH2A6                | 40 | 0      | D     | Display output channel 2, bus A, bit 6       |  |  |  |

| CH2A7                | 41 | 0      | D     | Display output channel 2, bus A, bit 7 (MSB) |  |  |  |

| CH2B0                | 14 | 0      | D     | Display output channel 2, bus B, bit 0 (LSB) |  |  |  |

| CH2B1                | 15 | 0      | D     | Display output channel 2, bus B, bit 1       |  |  |  |

| CH2B2                | 16 | 0      | D     | Display output channel 2, bus B, bit 2       |  |  |  |

| CH2B3                | 17 | 0      | D     | Display output channel 2, bus B, bit 3       |  |  |  |

| CH2B4                | 59 | 0      | D     | Display output channel 2, bus B, bit 4       |  |  |  |

| CH2B5                | 60 | 0      | D     | Display output channel 2, bus B, bit 5       |  |  |  |

| CH2B6                | 61 | 0      | D     | Display output channel 2, bus B, bit 6       |  |  |  |

| CH2B7                | 62 | 0      | D     | Display output channel 2, bus B, bit 7 (MSB) |  |  |  |

| CH3A0                | 26 | 0      | D     | Display output channel 3, bus A, bit 0 (LSB) |  |  |  |

| CH3A1                | 27 | 0      | D     | Display output channel 3, bus A, bit 1       |  |  |  |

| CH3A2                | 28 | 0      | D     | Display output channel 3, bus A, bit 2       |  |  |  |

| CH3A3                | 29 | 0      | D     | Display output channel 3, bus A, bit 3       |  |  |  |

| CH3A4                | 30 | 0      | D     | Display output channel 3, bus A, bit 4       |  |  |  |

| CH3A5                | 31 | 0      | D     | Display output channel 3, bus A, bit 5       |  |  |  |

| CH3A6                | 32 | 0      | D     | Display output channel 3, bus A, bit 6       |  |  |  |

| CH3A7                | 33 | 0      | D     | Display output channel 3, bus A, bit 7 (MSB) |  |  |  |

| CH3B0                | 6  | 0      | D     | Display output channel 3, bus B, bit 0 (LSB) |  |  |  |

| CH3B1                | 7  | 0      | D     | Display output channel 3, bus B, bit 1       |  |  |  |

| CH3B2                | 8  | 0      | D     | Display output channel 3, bus B, bit 2       |  |  |  |

| СН3В3                | 9  | 0      | D     | Display output channel 3, bus B, bit 3       |  |  |  |

| CH3B4                | 10 | 0      | D     | Display output channel 3, bus B, bit 4       |  |  |  |

| CH3B5                | 11 | 0      | D     | Display output channel 3, bus B, bit 5       |  |  |  |

| CH3B6                | 12 | 0      | D     | Display output channel 3, bus B, bit 6       |  |  |  |

| CH3B7                | 13 | 0      | D     | Display output channel 3, bus B, bit 7 (MSB) |  |  |  |

<sup>†</sup> I = input to device: O = output from device B = bidirectional ‡ A = analog pin: D = digital pin

# 1.7 THS8083 Terminal Functions Order (Continued)

| TERMINA    | \L                       |        |                   |                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|------------|--------------------------|--------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME       | NO.                      | I/O/B† | TYPE <sup>‡</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|            |                          |        |                   | DIGITAL CONTROL I/O                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| SCL        | 3                        | В      | D                 | Clock for $I^2C$ . Although the device is an $I^2C$ slave, this signal can be held low by the device to signal contention, therefore it is flagged bidirectional.                                                                                                                                                                                                                      |  |  |  |

| SDA        | 4                        | В      | D                 | Serial data for I <sup>2</sup> C                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| I2CA       | 5                        | I      | D                 | Address select for I <sup>2</sup> C  0 = LSB of device address 0  1 = LSB of device address 1                                                                                                                                                                                                                                                                                          |  |  |  |

| EXT_CLP    | 99                       | I      | D                 | External clamp timing pulse. Positive polarity required.                                                                                                                                                                                                                                                                                                                               |  |  |  |

| HS         | 1                        | I      | D                 | Reference clock input for PLL (horizontal sync input). Polarity selectable via $I^2C$ register <hs_pol>. 5 V tolerant input</hs_pol>                                                                                                                                                                                                                                                   |  |  |  |

| VS         | 2                        | I      | D                 | Vertical sync input. Polarity selectable via I <sup>2</sup> C register <vs_pol>. 5 V tolerant input</vs_pol>                                                                                                                                                                                                                                                                           |  |  |  |

| DHS        | 55                       | 0      | D                 | Display horizontal sync. This output can be generated as either a delayed version of input HS or as output pulse from the PLL feedback divider. See Display Horizontal Sync section Functional Description.                                                                                                                                                                            |  |  |  |

| CS/TEST1   | 78                       | 0      | A/D               | Composite sync output. This output will produce a 3-V logic-compatible sliced output of CH1. When present and enabled, CS will carry the composite sync embedded in Ch1. See Composite Sync Slicer section in Functional Description. For TI internal testing, this pin can also be configured as a test pin. Leave unconnected when CS output signal is not used.                     |  |  |  |

| LOCK       | 100                      | 0      | D                 | Lock detect output 0 = unlocked 1 = locked                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| PFD_FREEZE | 98                       | I      | D                 | Freezes the PLL output frequency by stopping the PFD output (i.e., keeping last increment to DTO). See section 2.3 <i>Composite Sync Slicer.</i> 0 = updating 1 = frozen                                                                                                                                                                                                               |  |  |  |

| ŌĒ         | 71                       | I      | D                 | Output enable for data output busses A and B. Data outputs are active only when $\overline{OE} = L$ and the corresponding bus is active for the current output formatter mode (register OFM_CTRL). When data outputs are <u>not</u> active or when DVDD = 0 V, data output is Hi-Z. The clock outputs are not affected by $\overline{OE}$ . $0 = \text{enabled}$ $1 = \text{disabled}$ |  |  |  |

| RESET      | 76                       | I      | D                 | General chip reset (active low). The reset is a synchronous reset. Therefore, a master clock on                                                                                                                                                                                                                                                                                        |  |  |  |

|            |                          |        |                   | XTL1–MCLK needs to be present for proper reset.                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| CS/TEST1   | 78                       | 0      | A/D               | TEST I/O  See description for this terminal under DIGITAL CONTROL I/O higher.                                                                                                                                                                                                                                                                                                          |  |  |  |

| TEST2      | 79                       | 0      | A/D<br>A/D        | Test mode analog output 2. Leave unconnected for normal use.                                                                                                                                                                                                                                                                                                                           |  |  |  |

| SCAN_TEST  | 77                       | ı      | D D               | Input for scan-path activation:                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| OOAN_TEOT  | ,,                       | '      |                   | 0 = disabled 1 = enabled. This pin MUST be tied low for normal operation and is of use for TI internal testing only.                                                                                                                                                                                                                                                                   |  |  |  |

|            |                          | •      | •                 | UNUSED PINS                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| NC         | 80, 86,<br>87, 93,<br>94 | I      | А                 | Not connected. Tie to a fixed high or low level on board.                                                                                                                                                                                                                                                                                                                              |  |  |  |

<sup>†</sup> I = input to device: O = output from device B = bidirectional ‡ A = analog pin: D = digital pin

# 2 Functional Description

# 2.1 Analog Channel

The THS8083 contains three identical analog channels that are independently programmable. Each channel consists of a clamping circuit, a programmable gain amplifier, and an A/D converter.

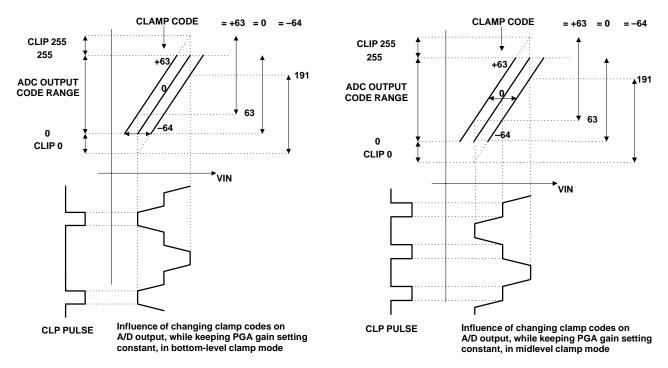

# 2.2 Clamping Circuit

The purpose of clamping is to provide the input signal with a known dc-value. Typically, video signals will be ac-coupled into the part. The signal needs to be level-shifted to fall in the reference voltage range (VREFB...VREFT) of the A/D converter. By supplying a programmable clamp, the user can shift the input signal with respect to the A/D range. This has the same effect as keeping the input signal constant and applying offset to both A/D reference voltages while keeping the VREFT–VREFB difference equal. However, no external adjustments are needed with this implementation.

For video, the clamping circuit can only be active during the non-active video portion of each line to avoid changes in brightness along the line. Clamping is done during the horizontal blanking interval, either on the backporch of sync or during the sync tip (in the case of a sync present on at least one of the video channels). If HS is carried on a separate line, as is typically the case for PC graphics, clamping is done during blanking. When the Y or G input channel contains an embedded sync, then alternatively clamping can be done during the sync-tip. This is not supported on the THS8083, since it is expected that the input signal level during clamping, of which position and width are determined by the clamp timing pulse (as shown later) corresponds to the blanking level. Since (for RGB type inputs) the blanking level will correspond to a low output code of the A/D, it makes sense to center the clamp range around an A/D output code of 0. The user can adjust this level up or down, symmetrically around 0. If the clamping is set such that the blanking level corresponds to a level below 0, the A/D output is clipped at code 0.

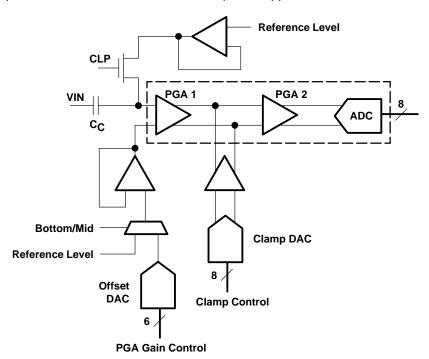

Figure 2-1. Analog Channel Architecture

In the case of YUV input signals, blanking levels for U and V correspond to the mid-level analog input. To handle these signals the clamping range should be centered on the mid-level output code of the A/D.

The clamp code is 8 bits wide and spans 128 ADC output codes (a 2 LSB change to clamp code corresponds nominally to 1 LSB change in ADC output). The programmed clamp code is independent of the PGA setting (see later). This ensures independent brightness/clamping control.

The clamp pulse defines the timing window during which the clamp circuit is internally enabled, and is either generated externally and supplied to the device, or it can be internally generated. In the latter case, the user can program both the position and width of the clamp pulse with respect to the horizontal sync (HS) input.

Figure 2-2. Bottom-Level Clamping

Figure 2-3. Mid-Level Clamping

### 2.3 Composite Sync Slicer

The THS8083 includes a circuit that will compare the input signal on Ch.1 to a level 150 mV below the blanking level. This slicer will output on the composite sync (CS) pin a 3-V compatible digital output. The intended use of this circuit is for input video signals that have an embedded (negative or trilevel) sync. This is the case for workstation-type input signals or the DTV analog interface that mandates sync-on-Y. Since the sync amplitude is ~300 mV, the slicing level is at about 50% of the sync level. When enabled, the CS output is available even when the device is powered down.

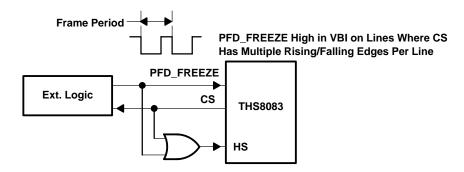

CS will output the extracted composite sync. Since the PLL will be prevented from updating its phase detector while the PFD\_FREEZE pin is kept high, the user asserts PFD\_FREEZE during the VBI (when CS has multiple transitions per line). This puts the PLL in free-run. While it cannot be guaranteed with devices that have analog PLL's, the digital PLL in the THS8083 is assured to keep a constant output frequency and avoid frequency drift while the PLL is in free-run. There is also no maximum on the time that PFD\_FREEZE can be kept asserted to still keep a stable PLL output frequency. In this case, the CS output can be directly connected to the THS8083's HS input for purposes of locking the PLL. However, the frequency monitoring of HS, that works off signal edges, will produce invalid numbers on those lines where CS is present because of the multiple low-high transitions on these lines.

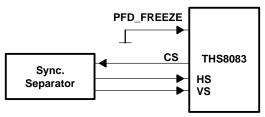

Alternatively, if an external sync separator is present that generates HS and VS from CS, the separated signals can be fed to the corresponding inputs on the THS8083 and PFD\_FREEZE can be left unused. As long as both signals generate only 1 pulse per line respectively frame, the PLL will lock correctly and HS/VS frequency monitoring will be accurate. Both options are shown in Figure 2–4.

Option 1: Using PFD\_FREEZE

Option 2: Using HS Derived From CS

Figure 2-4. Using THS8083 With a Composite Sync

Note that the slicer will only work when no video levels are lower than the blanking level and when the internal clamp circuit is used. This is normally satisfied for G and Y channels, but not for U and V channels. To prevent unnecessary toggling of the CS output signal, the CS output is switched off automatically when mid-level clamping is chosen for channel 1 (i.e., CLP1\_RG=1 in register <CLP\_CTRL>). CS can be permanently disabled by setting CS\_DIS=1 in register <AUX\_CTRL>.

When CS is disabled, the CS output will be Hi-Z.

#### NOTE:

While PFD\_FREEZE keeps the DTO output frequency constant, it does not disable the phase/frequency detector (PFD) from internally updating its error value at every active edge on HS. Therefore, when deasserting PFD\_FREEZE and no external sync separator is used, a discontinuity on the frequency increment to the DTO occurs which will cause an instantaneous frequency shift. To prevent this, the user should gate the CS signal externally with the PFD\_FREEZE signal as shown in Figure 2.4. This will keep the PFD from updating during PFD\_FREEZE high, since HS will remain low during the VBI. By using both PFD\_FREEZE and gating during the vertical blanking interval, THS8083 can be locked to signals with a composite sync.

To support sync-on-Y/sync-on-G extraction, the user should provide an external dc biasing to the Y/G channel. This can be done by establishing a dc clamp through a diode with its cathode connected to the ac-coupling capacitor (at the side of THS8083) on the AGY channel and anode connected to a dc level. Since the slicing level is around 1.35 V and the sync amplitude is ~300 mV, the negative sync-tip should be clamped by the diode to a level of approximately 1.2 V. For example, using a Schottky switching diode (type 1N5711) with a low forward voltage drop of maximum 0.4 V, the dc level at the anode can be approximately 1.6 V. This level can be derived through a resistive voltage divider off the power supply.

# 2.4 Programmable Gain Amplifier (PGA)

Each video channel is passed through a programmable gain amplifier, to provide a full-scale signal to each A/D. The user can change this gain via register programming. A gain change becomes effective immediately.

The range of the PGA is such that an input ac range from 0.4 Vpp to 1.2 Vpp can be scaled to ADC full scale, by maximum gain and minimum gain settings respectively.

The PGA is split into a 6-bit coarse gain control and 5-bit fine gain control. Their combination leads to a PGA resolution of better than 1 LSB on the ADC output code.

The bandwidth of the PGA is by design constant, resulting in a constant analog video input bandwidth.

The coarse PGA, with its 64 settings, covers a 4/3 x to 4x gain change, used for a 0.4 V (0.4 Vpp  $\times$  4 = 1.6 Vpp) respectively 1.2 Vpp (1.2 Vpp  $\times$  4/3 = 1.6 Vpp) input range swing.

While an amplifier with variable gain implements the coarse PGA, the fine PGA is implemented by slightly changing the top and bottom reference levels that are also independently controllable for each ADC channel. The fine range, with its 32 settings, covers a range of 16 LSBs.

The fine and coarse PGA settings can be combined into a single PGA gain formula as follows:

$$GAIN = (4/3 + C/24)(1 + (F-15)/512)$$

Where C is the coarse gain setting (0..63) and F the fine gain setting (0..31).

#### 2.5 A/D Converter

The A/D converter is based on the core used in the TLV5580 (single 8-bit 80 MSPS A/D). The switched-capacitor single-pipeline CMOS architecture combines excellent signal-to-noise characteristics with a very wide 3-dB analog input bandwidth of typically 500 MHz. The A/D block contains an internal reference voltage generator, providing stable bottom and top references derived from an internal bandgap reference. The reference voltages are made available externally. The THS8083 supports ac-coupled input (clamping circuit).

The A/D converter will have no missing codes up to 80 MSPS if used as defined in section 5, *Electrical Specification*. The sampling clock of the A/D converter is either fed from external or generated internally by the PLL.

#### 2.6 PLL

The PLL is a fully contained functional block consisting of:

- An analog PLL operating at a fixed output frequency of N times the master (crystal) clock frequency

- A digital PLL containing a digital phase-frequency detector (PFD), a discrete time oscillator (DTO), a digital loop filter, a feedback divider, a programmable clock output divider, and a programmable phase shifter

#### 2.6.1 Analog PLL

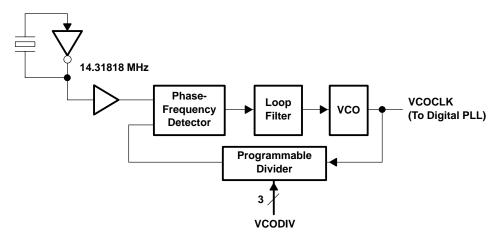

The analog PLL generates a high-frequency internal clock that will be used by the DTO in the digital PLL to derive the pixel output frequency with programmable phase. The reference signal for this PLL is the master clock frequency supplied on the XTL1-MCLK terminal.

Two options exist for connecting a master clock:

- A crystal can be connected between the XTL1-MCLK and XTL2 terminals. The device provides internal

oscillator circuitry.

- A 3.3-V CMOS/TTL clock signal can be connected to XTL1-MCLK from an external oscillator. In this case XTL2 must be left unconnected.

The port is designed to operate from a master clock frequency of 14.31818 MHz, which is a standard frequency in video applications: 4x the subcarrier frequency for NTSC. Many low-cost crystals are available for this frequency. The default internal oscillator operates at 8x the master clock frequency, so operating frequency is about 114 MHz. This setting of 8x, which is the value of the feedback divider in the analog PLL loop, is programmable (VCODIV register value). The user can change this value when a master clock of a different frequency is connected. In this case care should be taken to keep the internal high-frequency clock (i.e., master clock frequency x analog feedback divider) lower than 120 MHz. The higher this internal frequency, the better the frequency resolution of the DTO.

When a crystal is used as the master clock source, it is not advised to use another frequency than the recommended 14.31818 MHz, since the internal oscillator circuitry is not production tested at other frequencies. If another master clock is used, it is recommended to drive XTL1–MCLK by a direct clock signal. VCODIV should be programmed such that the internal clock remains close to but less than 120 MHz.

Figure 2-5. Analog PLL

# 2.6.2 Digital PLL

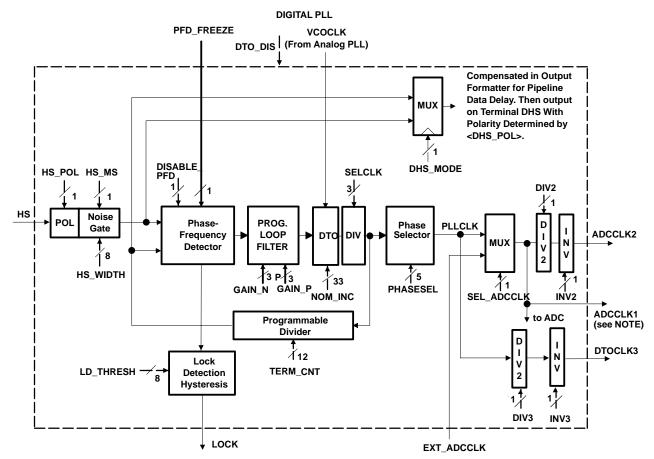

The digital PLL loop derives the ADC (pixel) clock frequency from the high-speed internal clock. A DTO will generate an output frequency from a user-programmable DTO increment. To operate over the 13.5–80 MHz range, an extra DTO clock output divider can be switched in. Appendix A shows the formula that relates the frequency of the internal high-speed clock, the DTO increment value, and the DTO clock output divider to the PLL output frequency.

The PLL output, after the clock divider, is sent to the programmable feedback divider (TERM\_CNT register value). This value will typically be programmed to the number of total pixels per line for a given video/graphics format. The output of this divider is then one input to the phase-frequency detector. Its other input is typically the horizontal sync (HS) reference of a graphics/video signal. HS needs to be provided as a separate TTL/CMOS type signal to the dedicated input terminal; See section 2.3 *Composite Sync Slicer*, to use the PLL in the case of input signals with a composite sync. The polarity of HS is programmable (HS\_POL register value).

Both HS and VS inputs on the THS8083 can accept a 3-V and a 5-V logic-compliant signal.

On the HS input, as on the VS input, a digital noise gate can be optionally switched in (HS\_MS respectively VS\_MS register values). The user can program the minimum number of clock cycles that HS and VS have to be present before they are interpreted as a valid HS and VS. This avoids having any spikes being interpreted as e.g. an active HS and falsely updating the PLL.

The PFD produces a digital error value, signaling the phase/frequency difference between the HS input and the divided PLL output clock. The integrated digital PLL loop filter subsequently filters this error value. This filter consists of a proportional and integrator (accumulator) part. Gains of both parts are programmable (GAIN\_N and GAIN\_P register values), each with eight settings. The higher the programmed value, the higher the gain in either the proportional or integrator portions of the filter, which translates into a wider capture range and faster acquisition but also higher steady-state jitter.

The PFD also provides a LOCK output on a dedicated output terminal. This output has a programmable hysteresis (LD\_THRES register value). Details are explained in the section that describes the register map of this device. The LOCK output is made available on a dedicated pin so that the user could implement additional functionality before using this output (e.g., implement sticky nature of an unlock condition by routing it through an external set/reset flip-flop).

By integrating the loop filter and making it programmable, the user can trade off both at runtime depending on the quality of the incoming HS signal (inaccurate frequency, jitter content).

The filtered phase/frequency error value is now used to correct the programmed nominal DTO increment (NOM\_INC register value) to the instantaneous DTO increment (DTO\_INC reported value). This updated DTO increment determines the instantaneous DTO output frequency. By making DTO\_INC available as a read-only register, the user can read out via I<sup>2</sup>C and calculate the instantaneous frequency of the DTO generated clock.

Because of the digital nature of the PLL, the loop can be opened while still keeping an accurate frequency output. Therefore, the PLL can also be used as a frequency synthesizer, without any HS reference. This is done by disabling the PFD (PFD\_DISABLE register value). This will keep DTO\_INC always equal to NOM\_INC, thereby producing a DTO output frequency always equal to the desired programmed frequency, irrespective of HS.

There is a second option to operate in open loop though. In some video/graphics modes no valid HS is present during a part of the frame/field period, typically during some lines of the VBI (vertical blanking interval). In order to have an accurate PLL output clock and avoid clock drift, the PFD output needs to be held constant during this time. The PFD FREEZE pin provides this option. Asserting this will freeze DTO\_INC to its present value, thereby producing a constant PLL output clock frequency, not necessarily equal to the nominal desired frequency programmed by NOM\_INC. Together with the composite sync slicer, this feature allows the use of the PLL for input signals with embedded composite sync with minimal external logic. See Composite Sync Slicer section.

The phase of the PLL generated clock can be programmed in 31 uniform steps over a single clock period (360/31 = 11.6 degrees phase resolution) so that the sampling phase of the ADC's can be controlled accurately.

Next to sourcing the ADC channel clock from the PLL, the option exists to use an external pixel clock (from terminal EXT\_ADCCLK). If configured this way (via SEL\_ADCCLK register value), a clock signal of the required sampling frequency should be applied to EXT\_ADCCLK and this signal, instead of the PLL generated clock, is routed to the ADC channels. No phase control is available in this case on the external clock signal. Still, the internal PLL can be used and its output available externally as explained below. This means two clock domains can be implemented on THS8083: a first one from externally fed, a second one, possibly asynchronous to the first, generated by the internal PLL. This provides considerable flexibility in the design of video/graphics equipment that implements scaling and frame rate conversion.

NOTE: ADCCLK1 is used by the output formatter to generate the DATACLK1 output.

#### Figure 2-6. Digital PLL

The device provides three clock outputs. One of these output signals, DATACLK1, is derived from the ADC clock output. It is actually equal to the sampling clock but compensated in phase so that its rising edge always corresponds to the center valid region of the output data. Output data timing (setup/hold) is specified with respect to this rising edge. Therefore, DATACLK1 is typically used for clocking the THS8083's output data. The frequency of DATACLK1 will be either equal or 1/2 of the sampling clock, depending on the operation mode of the output formatter. When the THS8083 is clocked with an external sampling clock, this external clock is used as the source to generate DATACLK1 in the output formatter.

The second clock output, ADCCLK2, is equal to the ADC sampling clock but can optionally be divided by 2 and inverted.

Finally, the third clock output, DTOCLK3, is always derived from the PLL output clock, irrespective of the use of an external sampling clock on EXT\_ADCCLK. So, when operating with an external sampling clock, the DTOCLK3 output can be used to generate a second, possibly asynchronous, clock signal in either open loop operation or in closed loop locked to a reference HS input. Also, DTOCLK3 can be optionally divided by 2 and inverted.

The divide and invert functions are implemented to enable a master/slave operation of two parts in case higher sampling speeds than 80 MSPS are required. In this case the master will use its PLL to generate a line-locked clock, of which the inverse will be used as an external sampling clock by the second slave device.

# 2.7 Output Formatter

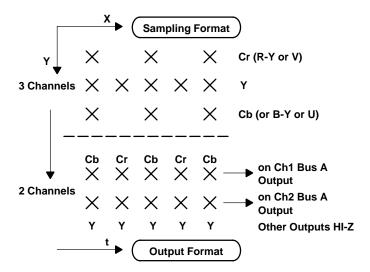

This block enables either a 4:4:4 24-bit output or 4:4:4 48-bit output at half the pixel clock or a 4:2:2 16-bit output, useful for YUV digitizing (ITU.BT-601 style). In the latter case, an 8-bit port is used for the Y output, while a second 8-bit port is used alternately for Cr and Cb. As per ITU BT-601, Cb is the first video data word for each line, as shown in Figure 2-7.

The first color sample after an incoming HS will be Cb. The output signal DHS is synchronized to the first pixel of a line and can therefore be used to uniquely identify Cb from Cr output data in downsampled modes.

Figure 2-7. Output Formatter

### 2.8 Power Down

In the I<sup>2</sup>C power-down register, four power down modes are defined:

- Chip power down: PWDN\_ALL

When PWDN\_ALL=1, all analog circuits are powered down except the internal bandgap reference, the circuit that generates the clamping voltages and the sync reference voltage. All these are kept active for the composite sync slicer that remains active during power down. The clock frequency of the digital circuitry will be lowered to reduce power consumption when in power down.

- Internal reference power down: PWDN\_REF

When PWDN\_REF=1, bottom and top references (VREFB, VREFT) on all channels become inputs and should be driven from external.

- Bandgap reference power down: PWDN\_BGAP

When PWDN\_BGAP=1, the internal bandgap reference voltage is inactive and terminal VMID should be driven from external.

- DTO power down: DTO\_DIS

When DTO\_DIS=1, the DTO frequency is lowered to reduce power dissipation. When an external sampling clock is used (EXT\_ADCCLK), this power down can be activated.

# 2.9 Input Mode Detection

The THS8083 supports detection of the graphics input format in co-operation with an external microcontroller. Via the microcontroller interface the period of incoming HS and VS signals can be measured (HS\_COUNT, VS\_COUNT register values), as well as the frequency of the DTO clock (DTO\_INC register value) and the PLL lock condition (terminal LOCK).

#### 2.10 Test Mode

The ADC output data on each of the three channels can be sampled at a programmable position on each line (PIXTRAP register value) and latched into pixel readback registers (CH<n>\_RDBK register values) that can be read by the microcontroller at lower speed via the I<sup>2</sup>C interface. When programmed to read back during the horizontal blanking interval this can be a test for accurate positioning of the blanking level.

# 3 Register Definition

# 3.1 I<sup>2</sup>C Protocol

The THS8083 is a slave I<sup>2</sup>C device on which both write and read are supported. As shown in the register map, there are some status control registers that can only be read.

The device can support FAST I<sup>2</sup>C mode (SCL up to 400 kHz) when the DTO clock is running at over 25 MHz; at lower DTO frequencies only NORMAL I<sup>2</sup>C mode (SCL up to 100 kHz) is supported.

To discriminate between write and read operations, the device is addressed at separate device addresses. There is an automatic internal subaddress increment counter to efficiently write/read multiple bytes in the register map during one write/read operation. Furthermore, bit1 of the I<sup>2</sup>C device address is dependent upon the setting of the I2CA pin, as follows:

If address selecting pin I2CA = 0, then

WRITE address is 40 hex (01000000)

READ address is 41 hex (01000001)

If address selecting pin I2CA = 1, then

WRITE address is 42 hex (01000010)

READ address is 43 hex (01000011)

# 3.1.1 Write Format

| S Slave address(v | v) A                                    | Sub-address                                                         | Α | Data0 | Α |  | Data(N-1) A P |  |  |  |  |

|-------------------|-----------------------------------------|---------------------------------------------------------------------|---|-------|---|--|---------------|--|--|--|--|

| S                 | Start co                                | Start condition                                                     |   |       |   |  |               |  |  |  |  |

| Slave address(w)  | 010000                                  | 0100000 (0x40) if I2CA=0 / 01000010 (0x42) if I2CA=1                |   |       |   |  |               |  |  |  |  |

| Α                 | Acknowledge, it is generated by THS8083 |                                                                     |   |       |   |  |               |  |  |  |  |

| Subaddress        | Subadd                                  | Subaddress of the 1 <sup>st</sup> register to write, length: 1 byte |   |       |   |  |               |  |  |  |  |

| Data0             | First byte of the data                  |                                                                     |   |       |   |  |               |  |  |  |  |

| Data(N-1)         | Nth byte                                | Nth byte of the data                                                |   |       |   |  |               |  |  |  |  |

| Р                 | Stop co                                 | ndition                                                             |   |       |   |  |               |  |  |  |  |

#### 3.1.2 Read Format

First write the subaddress, where data needs to be read out, to THS8083 in the format as follows:

| S | Slave address(w) | Α | Subaddress | Α | Р |

|---|------------------|---|------------|---|---|

|---|------------------|---|------------|---|---|

#### Then:

| S | Slave address(r) | Α | DataN | AM | Data(N+1) | AM | <br>NAM | Р |

|---|------------------|---|-------|----|-----------|----|---------|---|

S Start condition

Slave address(r) 01000001 (0x41) if I2CA=0 / 01000011 (0x43) if I2CA=1

A Acknowledge, it is generated by THS8083; if the transmission is successful, then A = 0, else

A = 1

AM Acknowledge, it is generated by a master

NAM Not acknowledge, it is generated by a master

Subaddress Subaddress of the first register to read, length = one byte

Data0 First byte of the data read

Data(N-1) Nth byte of the data read

P Stop condition

In both write and read operations, the subaddress will be incremented automatically when multiple bytes are written/read. So, only the first subaddress needs to be supplied to the THS8083.

R/W registers can be written and read.

R registers are read-only.

Table 3-1. I<sup>2</sup>C Register Map

| REGISTER<br>NAME | RW  | SUB<br>ADDRESS | Bit 7     | Bit 6     | Bit 5       | Bit 4      | Bit 3      | Bit 2      | Bit 1      | Bit 0      |

|------------------|-----|----------------|-----------|-----------|-------------|------------|------------|------------|------------|------------|

| TERM_CNT_0       | RW  | 00             | TERM_CNT7 | TERM_CNT6 | TERM_CNT5   | TERM_CNT4  | TERM_CNT3  | TERM_CNT2  | TERM_CNT1  | TERM_CNT0  |

| TERM_CNT_1       | RW  | 10             |           |           |             |            | TERM_CNT11 | TERM_CNT10 | TERM_CNT9  | TERM_CNT8  |

| NOM_INC_0        | RW  | 02             | NOM_INC7  | NOM_INC6  | NOM_INC5    | NOM_INC4   | NOM_INC3   | NOM_INC2   | NOM_INC1   | NOM_INC0   |

| NOM_INC_1        | R/W | 03             | NOM_INC15 | NOM_INC14 | NOM_INC13   | NOM_INC12  | NOM_INC11  | NOM_INC10  | NOM_INC9   | NOM_INC8   |

| NOM_INC_2        | RW  | 04             | NOM_INC23 | NOM_INC22 | NOM_INC21   | NOM_INC20  | NOM_INC19  | NOM_INC18  | NOM_INC17  | NOM_INC16  |

| NOM_INC_3        | RW  | 90             | NOM_INC31 | NOM_INC30 | NOM_INC29   | NOM_INC28  | NOM_INC27  | NOM_INC26  | NOM_INC25  | NOM_INC24  |

| NOM_INC_4        | RW  | 90             |           |           |             |            |            |            |            | NOM_INC32  |

| VCODIV           | R/W | 20             |           |           |             |            |            | VCODIV2    | VCODIV1    | 0/VIGOD/V  |

| SELCLK           | R/W | 80             |           |           |             |            |            |            | SELCLK1    | SELCLKO    |

| PHASESEL         | R/W | 60             |           |           |             | PHASE_SEL4 | PHASE_SEL3 | PHASE_SEL2 | PHASE_SEL1 | PHASE_SEL0 |

| PLLFILT          | R/W | 0A             |           |           | GAIN_N2     | GAIN_N1    | GAIN_N0    | GAIN_P2    | GAIN_P1    | GAIN_P0    |

| HS_WIDTH         | R/W | 90             | HS_WIDTH7 | HS_WIDTH6 | HS_WIDTH5   | HS_WIDTH4  | HS_WIDTH3  | HS_WIDTH2  | HS_WIDTH1  | онтаім_гн  |

| VS_WIDTH         | RW  | 00             | VS_WIDTH7 | VS_WIDTH6 | VS_WIDTH5   | VS_WIDTH4  | VS_WIDTH3  | VS_WIDTH2  | VS_WIDTH1  | VS_WIDTH0  |

| SYNC_CTRL        | RW  | <b>Q</b> 0     |           |           |             |            | HS_POL     | HS_MS      | VS_POL     | SM_SV      |

| LD_THRES         | RW  | <b>3</b> 0     | LD_THRES7 | LD_THRES6 | LD_THRES5   | LD_THRES4  | LD_THRES3  | LD_THRES2  | LD_THRES1  | LD_THRES0  |

| PLL_CTRL         | RW  | 90F            |           |           | DISABLE_PFD | SEL_ADCCLK | INV2       | DIV2       | INV3       | E/II       |

| HS_COUNT_0       | Ж   | 10             | HS_COUNT7 | HS_COUNT6 | HS_COUNT5   | HS_COUNT4  | HS_COUNT3  | HS_COUNT2  | HS_COUNT1  | HS_COUNT0  |

| HS_COUNT_1       | Ж   | 11             |           |           |             |            | HS_COUNT11 | HS_COUNT10 | HS_COUNT9  | HS_COUNT8  |

| VS_COUNT_0       | Ж   | 12             | VS_COUNT7 | VS_COUNT6 | VS_COUNT5   | VS_COUNT4  | VS_COUNT3  | VS_COUNT2  | VS_COUNT1  | VS_COUNT0  |

| VS_COUNT_1       | Ж   | 13             |           |           |             |            | VS_COUNT11 | VS_COUNT10 | VS_COUNT9  | VS_COUNT8  |

| DTO_INC_0        | Ж   | 14             | DTO_INC7  | DTO_INC6  | DTO_INC5    | DTO_INC4   | DTO_INC3   | DTO_INC2   | DTO_INC1   | DTO_INC0   |

| DTO_INC_1        | Ж   | 15             | DTO_INC15 | DTO_INC14 | DTO_INC13   | DTO_INC12  | DTO_INC11  | DTO_INC10  | DTO_INC9   | DTO_INC8   |

| DTO_INC_2        | Ж   | 16             | DTO_INC23 | DTO_INC22 | DTO_INC21   | DTO_INC20  | DTO_INC19  | DTO_INC18  | DTO_INC17  | DTO_INC16  |

| DTO_INC_3        | Ж   | 17             | DTO_INC31 | DTO_INC30 | DTO_INC29   | DTO_INC28  | DTO_INC27  | DTO_INC26  | DTO_INC25  | DTO_INC24  |

| DTO_INC_4        | Ж   | 18             |           |           |             |            |            |            |            | DTO_INC32  |

| SYNC_DETECT      | Ж   | 19             |           |           |             |            |            |            |            | NO_SYNC    |

| Reserved         |     | 1A-1F          |           |           |             |            |            |            |            |            |

Table 3-1. I<sup>2</sup>C Register Map (continued)

| REGISTER<br>NAME | RW  | SUB<br>ADDRESS | Bit 7      | Bit 6      | Bit 5       | Bit 4       | Bit 3       | Bit 2       | Bit 1       | Bit 0       |

|------------------|-----|----------------|------------|------------|-------------|-------------|-------------|-------------|-------------|-------------|

| CLP_CTRL         | RW  | 20             |            | CLP_SEL    | CLP1_EN     | CLP1_RG     | CLP2_EN     | CLP2_RG     | CLP3_EN     | CLP3_RG     |

| CLP_START_0      | RW  | 21             | CLP_START7 | CLP_START6 | CLP_START5  | CLP_START4  | CLP_START3  | CLP_START2  | CLP_START1  | CLP_START0  |