捷多邦,专业PCB打样工厂,24小时加急出货

TOSHIBA

#### 查询TMP19A71CYFG供应商

# 32 bit TX System RISC TX19 Family TMP19A71CYFG/UG TMP19A71FYFG/UG

# Rev 2.0 (Feb.2007)

TOSHIBA CORPORATION

## Contents

| Features                                               | . 1-1                                                                                                                                                                                                                          |

|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Assignments and Pin Functions                      | . 2-1                                                                                                                                                                                                                          |

| Prosessor Core                                         | . 3-1                                                                                                                                                                                                                          |

| Memory Map                                             | . 4-1                                                                                                                                                                                                                          |

| Clock / Standby Control                                | . 5-1                                                                                                                                                                                                                          |

| Watchdog Timer                                         | . 6-1                                                                                                                                                                                                                          |

| Exceptions/Interrupts                                  | . 7-1                                                                                                                                                                                                                          |

| I/O Ports                                              | . 8-1                                                                                                                                                                                                                          |

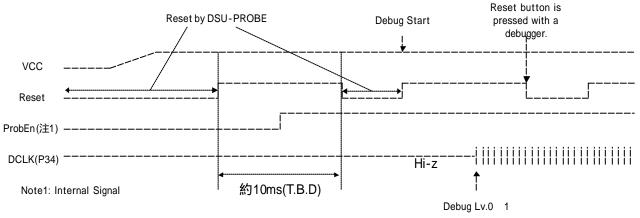

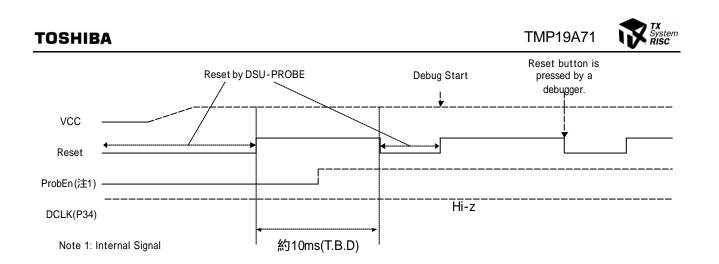

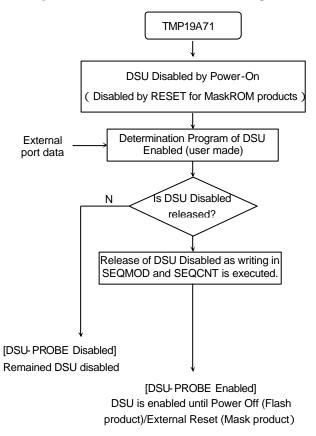

| Debug Support Unit (DSU)                               | . 9-1                                                                                                                                                                                                                          |

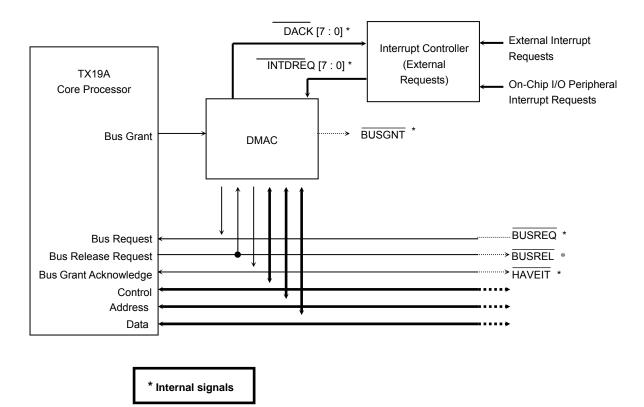

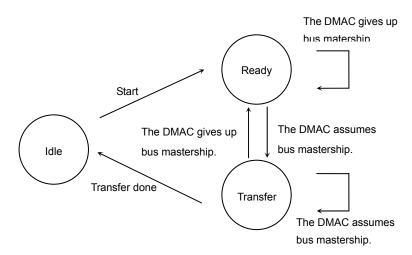

| DMA Controller (DMAC)                                  | 10-1                                                                                                                                                                                                                           |

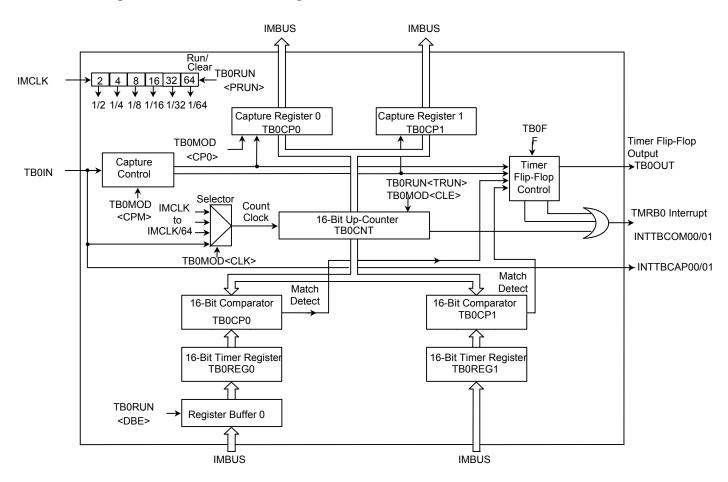

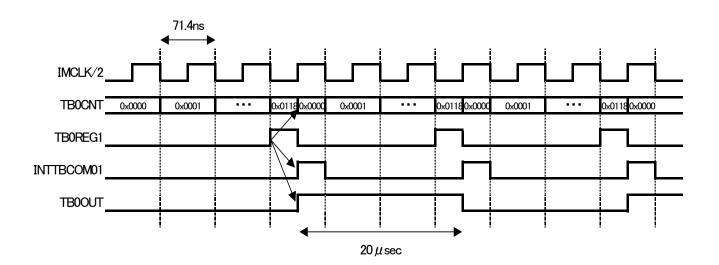

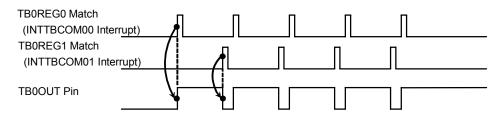

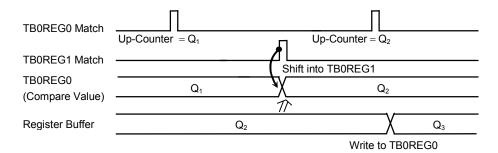

| 16-Bit Timer/Event Counters (TMRBs)                    | 11-1                                                                                                                                                                                                                           |

| Serial I/O (SIO)                                       | 12-1                                                                                                                                                                                                                           |

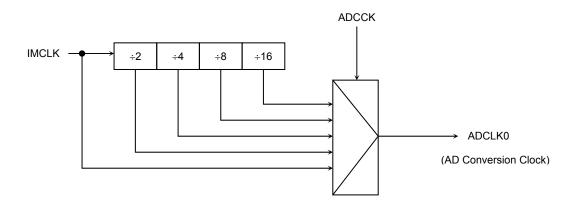

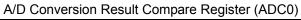

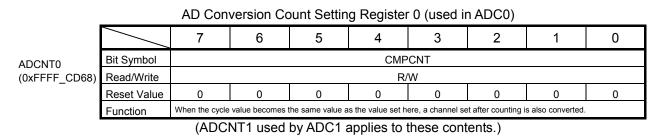

| Analog-to-Digital Converters (ADCs)                    | 13-1                                                                                                                                                                                                                           |

| Motor Control Circuit (PMD: Programmable Motor Driver) | 14-1                                                                                                                                                                                                                           |

| Encoder Input Circuit                                  | 15-1                                                                                                                                                                                                                           |

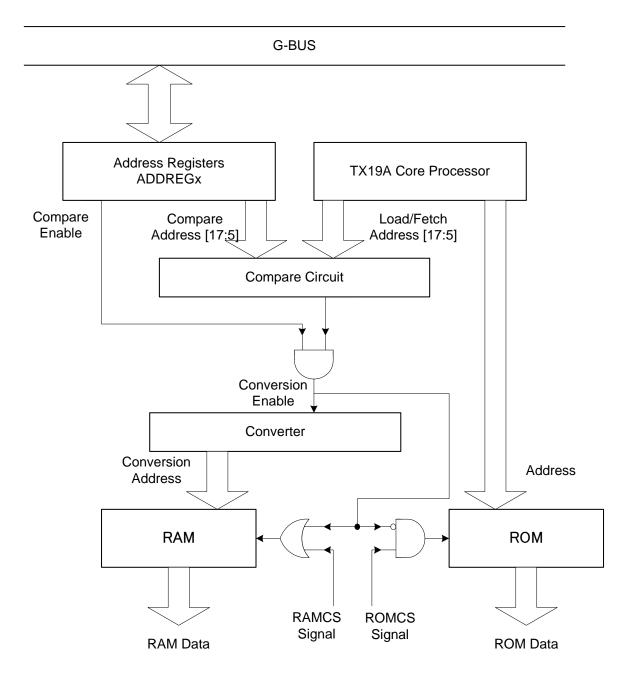

| ROM Correction                                         | 16-1                                                                                                                                                                                                                           |

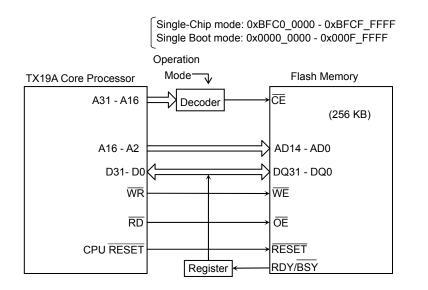

| Flash Memory                                           | 17-1                                                                                                                                                                                                                           |

| I/O Register Summary                                   | 18-1                                                                                                                                                                                                                           |

| Electrical Characteristics                             | 19-1                                                                                                                                                                                                                           |

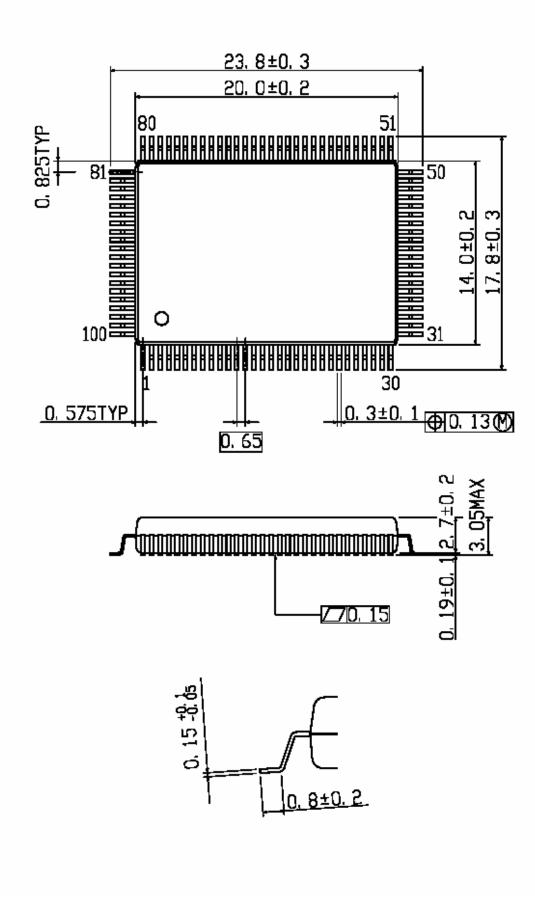

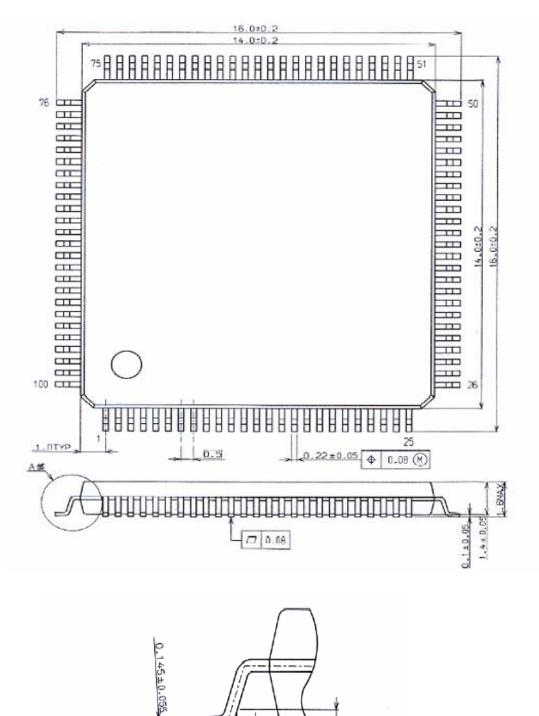

| Package Dimensions                                     | 20-1                                                                                                                                                                                                                           |

|                                                        | Features Pin Assignments and Pin Functions Prosessor Core Memory Map Clock / Standby Control Watchdog Timer Exceptions/Interrupts //O Ports Debug Support Unit (DSU) DMA Controller (DMAC) 16-Bit Timer/Event Counters (TMRBs) |

## 32-Bit RISC Microprocessor TX19 Family TMP19A71FYFG/FYUG/CYFG/CYUG

## 1. Features

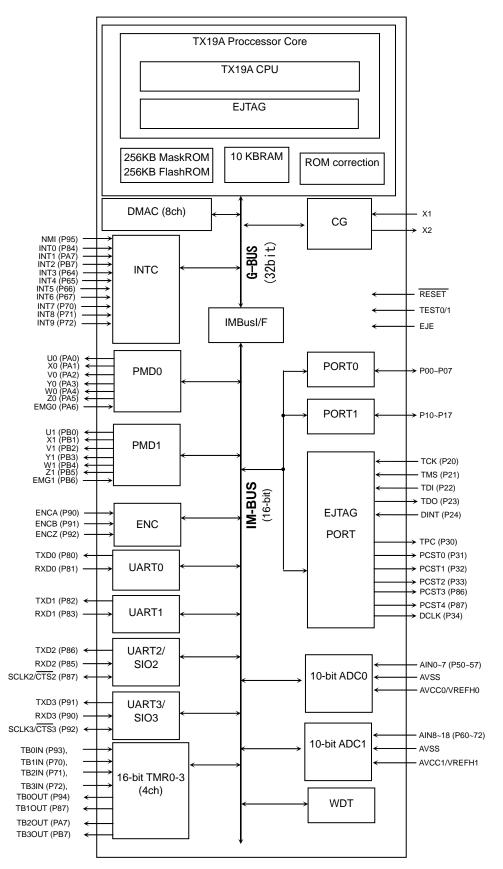

The TX19A core processor contained in the TMP19A71 is a family of high-performance 32-bit microprocessors that offers the speed of a 32-bit RISC solution with the added advantage of a significantly reduced code size of a 16-bit architecture. The instruction set of the TX19A includes the high-performance MIPS32ISA, and is enhanced by the MIPS16e-TX<sup>TM</sup> Application-Specific Extensions (ASE) based on the highly code-efficient MIPS16eISA of MIPS Technologies, Inc. and with added instructions by Toshiba.

The TMP19A71 is built on a TX19A core processor and contains a selection of intelligent peripherals. It is suitable for low-voltage and low-power applications.

The TMP19A71 has the following features:

- (1) TX19A core processor (For details, refer to the TX19A Architecture manual.)

- 1) Two instruction set architecture (ISA) modes: 16-bit ISA for code density and 32-bit ISA for speed

- The 16-bit ISA is object-code compatible with the code-efficient MIPS16e<sup>TM</sup>ASE.

- The 32-bit ISA is object-code compatible with the high-performance TX39 Family.

- 2) Combines high performance with low power consumption.

- High performance

- Single clock cycle execution (except for save, restore, jump/branch instructions)

- 3-operand computational instructions for high instruction throughput

- 5-stage pipeline

- On-chip high-speed memory

- DSP function: Executes 32-bit multiply-accumulate operations (32-bit x 32-bit + 64-bit = 64-bit) in a single clock cycle.

- Low power consumption

- Optimized design using a low-power cell library

<sup>•</sup> The information contained herein is subject to change without notice. 021023\_D

<sup>•</sup> TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property.

In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc. 021023\_A

<sup>•</sup> The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunctionor failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer's own risk. 021023\_B

<sup>•</sup> The products described in this document shall not be used or embedded to any downstream products of which manufacture, use and/or sale are prohibited under any applicable laws and regulations. 060106\_Q

<sup>•</sup> The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of TOSHIBA or others. 021023\_C

<sup>•</sup> The products described in this document are subject to the foreign exchange and foreign trade laws. 021023\_E

<sup>•</sup> For a discussion of how the reliability of microcontrollers can be predicted, please refer to Section 1.3 of the chapter entitled Quality and Reliability Assurance/Handling Precautions. 030619\_S

• Programmable standby modes in which processor clocks are stopped

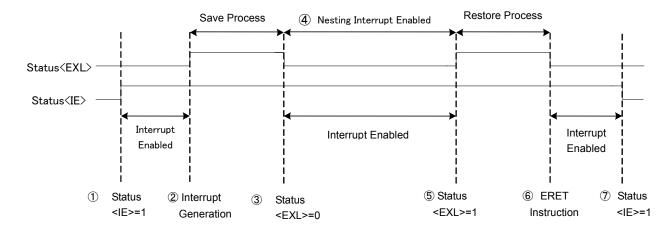

3) Fast interrupt response suitable for real-time control

- Distinct starting locations for each interrupt service routine

- Automatically generated vectors for each interrupt source

- Automatic updates of the interrupt mask level

#### (2) On-chip program memory and data memory

| Product         | On-Chip ROM             | On-Chip RAM |

|-----------------|-------------------------|-------------|

| TMP19A71FYFG/UG | 256 Kbytes<br>Flash ROM | 10 Kbytes   |

| TMP19A71CYFG/UG | 256 Kbytes<br>Mask ROM  | 10 Kbytes   |

- ROM correction logic (8 words x 8 blocks)

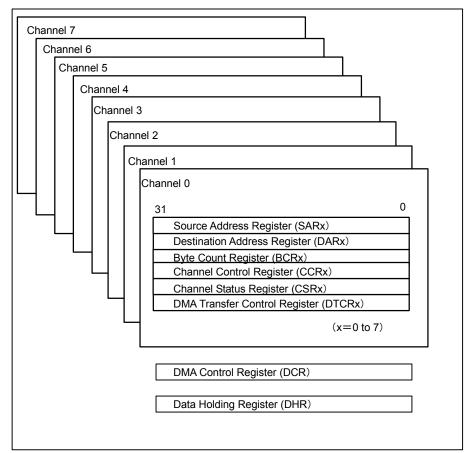

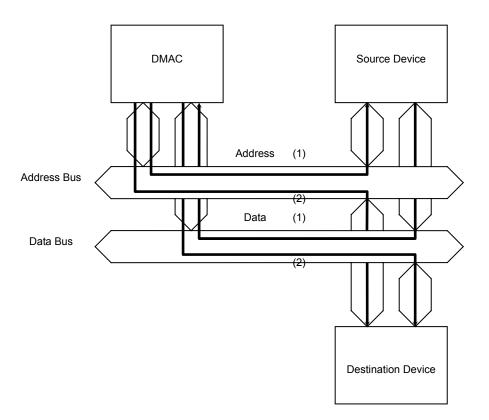

- (3) 8-channel DMA controller

- Interrupt- or software-triggered

- Transfer destination: On-chip memory, on-chip peripherals

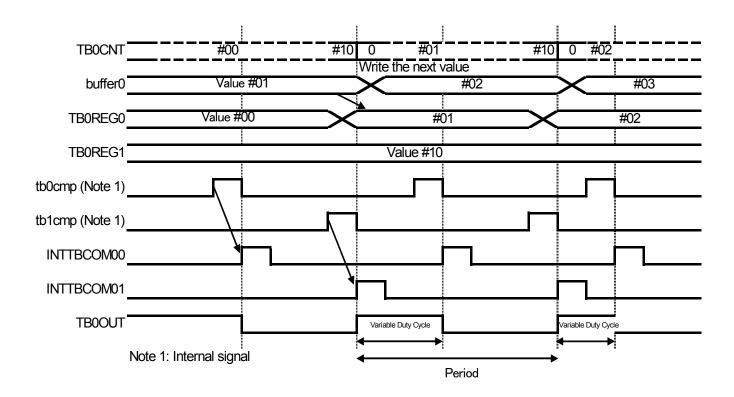

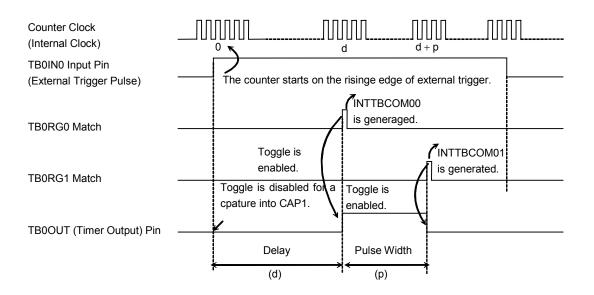

- (4) 4-channel 16-bit timer

- 16-Bit Interval Timer mode

- 16-Bit Event Counter mode

- 16-Bit PPG output

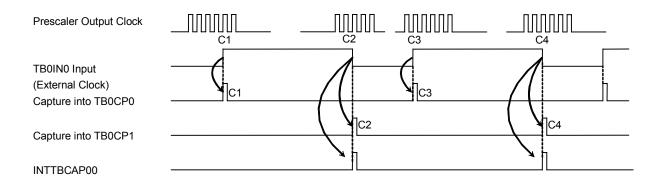

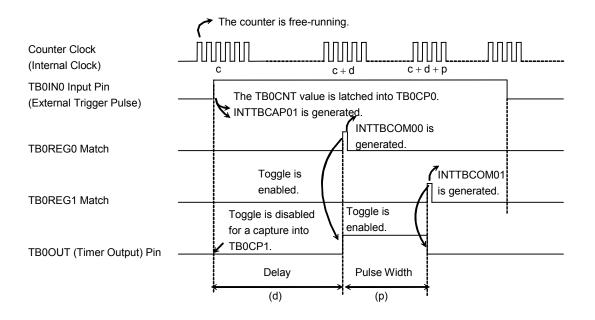

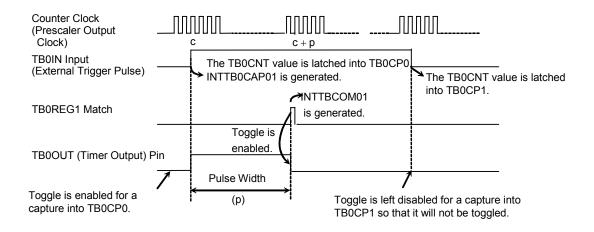

- Input capture

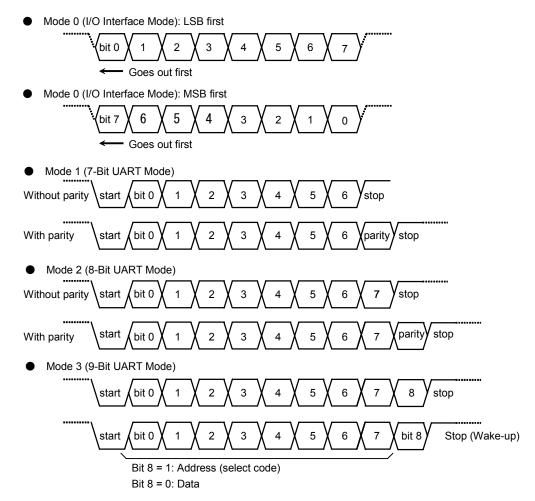

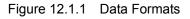

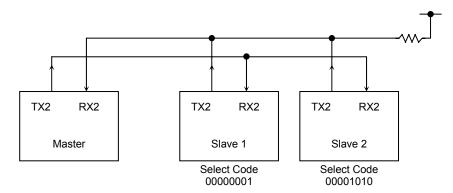

- (5) 4-channel general-purpose serial interface

- Either UART mode or Synchronous mode can be selected for 2 channels; the other 2 channels are UART only.

- 50% duty cycle generation (for UART mode only)

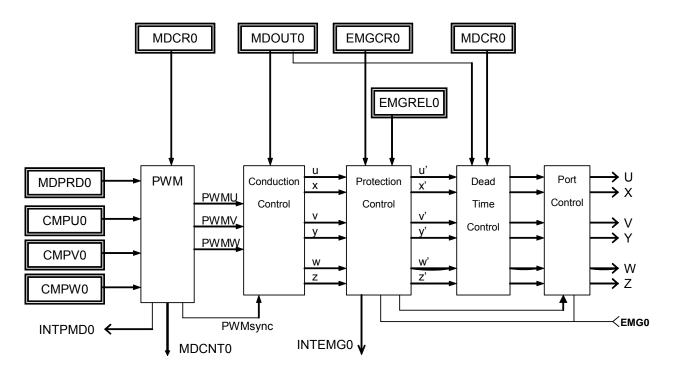

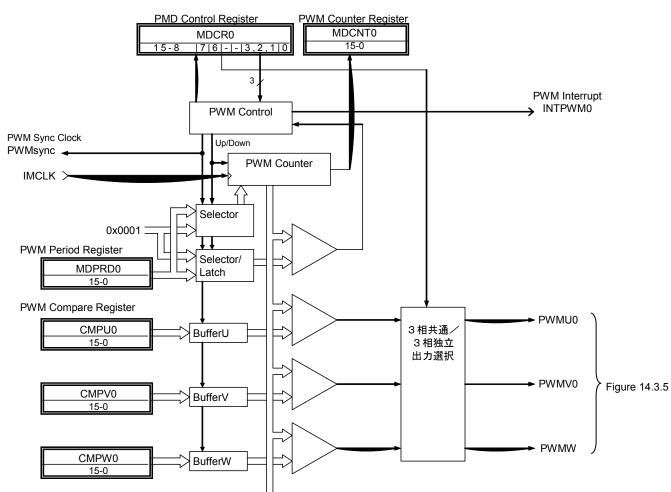

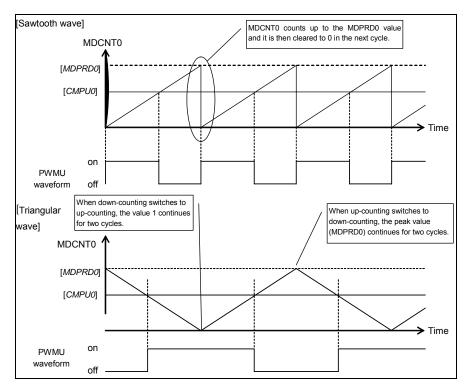

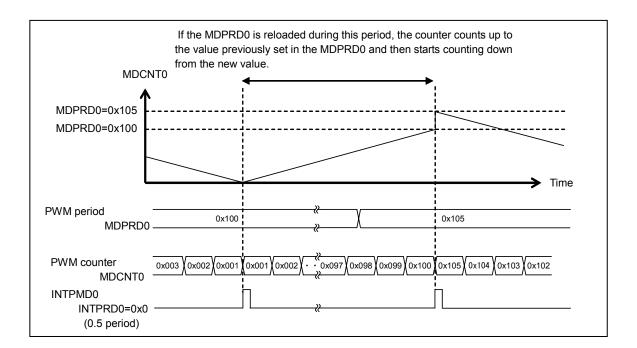

- (6) 2-channel 3-phase PWM generation (PMD)

- Generating 3-phase PWM with a resolution of 35.7 ns (at IMCLK = 28 MHz)

- Dead time insertion

- 3-phase PWM generation disabled under abnormal condition

- Two channels can be started synchronously.

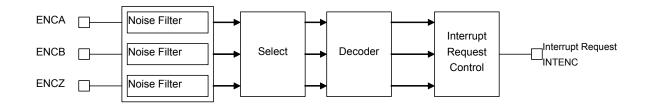

- (7) 1-channel ABZ encoder

- Supporting incremental encoder

- Rotation direction detection circuit

- Absolute position detection circuit

- Position comparison circuit

- On-chip noise filter

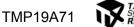

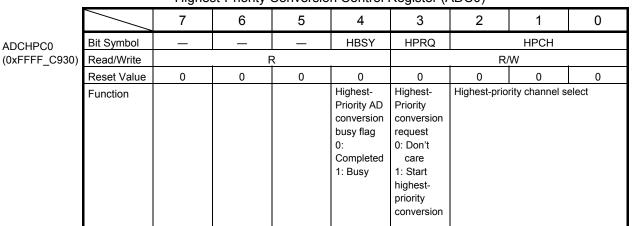

- (8) 19-channel 10-bit AD converter (with internal sample and hold)

- High-speed conversion (min: 2.36 µs)

- Input voltage range: 0 V to 3.3 V

- External trigger supported

- Fixed-Channel or Channel Scan mode

- Single Conversion or Continuous Conversion mode

- AD conversion monitoring

- PMD mode

- (9) 1-channel watchdog timer

- (10) Interrupt sources

- 2 CPU interrupts: Software interrupt (within the co-processor)

- 37 internal interrupts: 7 priority levels (excluding the watchdog timer interrupt)

- 11 external interrupts: 7 priority levels (excluding the NMI interrupt)

- (11) 75-pin input/output ports

- (12) Standby modes

- Three standby modes: DOZE, HALT, STOP

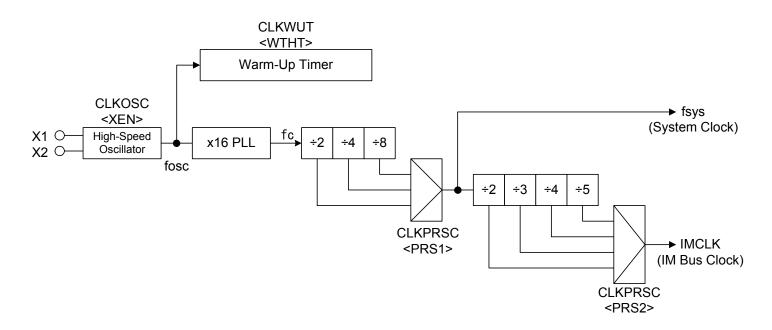

- (13) Clock generator

- On-chip PLL (x 16)

- Clock gear: Divides the high-speed clock to 1/2, 1/4 or 1/8.

- (14) Endian

- Little-endian fixed

- (15) Power voltage

- Peripheral I/O: Vcc3 = 3.3V ±0.3 V (TMP19A71FYFG/UG, TMP19A71CYFG/UG)

- Internal:  $Vcc2 = 2.5V \pm 0.2 V (MP19A71FYFG/UG)$

- Internal:  $VccC15 = 1.5V \pm 0.15 V (TMP19A71CYFG/UG)$

#### (16) Operating frequency

- 56 MHz (Vcc2 =  $2.5V \pm 0.2 V$ : TMP19A71FYFG/UG)

- 56 MHz (Vcc15 = 1.5V ±0.15 V: TMP19A71CYFG/UG)

(17) Package

- P-LQFP100-1414-0.50F (14mm × 14mm, 0.5-mm pitch): TMP19A71FYUG/CYUG

- P-QFP100-1420-0.65A (14mm × 20mm, 0.65-mm pitch): TMP19A71FYFG/CYFG

(): Default function after reset

## 2. Pin Assignments and Pin Functions

This section contains pin assignments for the TMP19A71 as well as brief descriptions of the TMP19A71 input and output signals.

## 2.1 TMP19A71CYFG/UG Pin Assignments

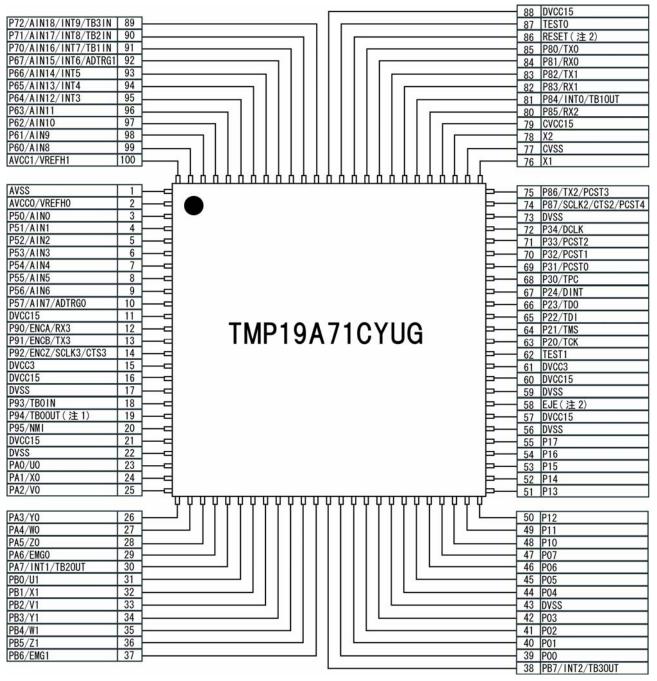

Figure 2.1 shows the pin assignments of the TMP19A71CYUG.

Figure 2.1 TMP19A71CYUG Pin Assignments (100-pin LQFP)

- Note 1: This pin should be set to High during a reset sequence.

- Note 2: These signals are Low active.

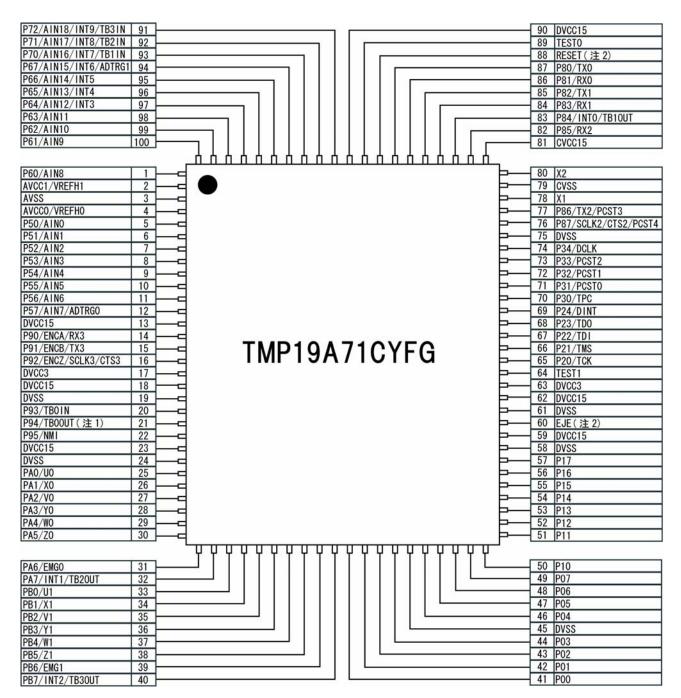

Figure 2.2 shows the pin assignments of the TMP19A71CYFG.

Figure 2.2 TMP19A71CYFG Pin Assignments (100-pin QFP)

- Note 1: This pin should be set to High during a reset sequence.

- Note 2: These signals are Low active.

#### 2.2 TMP19A71FYFG/UG Pin Assignments

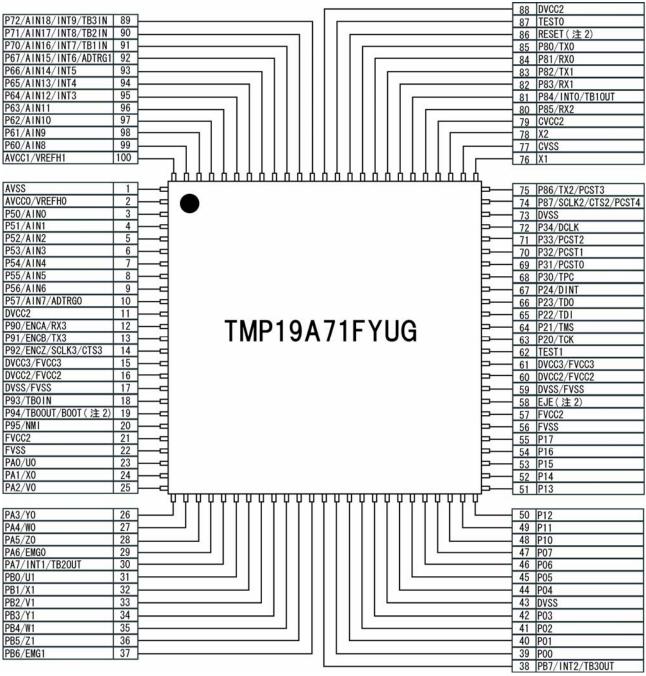

Figure 2.3 shows the pin assignments of the TMP19A71FYUG.

Figure 2.3 TMP19A71FYUG Pin Assignments (100-pin LQFP)

Note 1: This pin should be set to High during a reset sequence.

Note 2: These signals are Low active.

| P72/AIN18/INT9/TB3IN 91                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              | 90 DVCC2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P71/AIN17/INT8/TB2IN 92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              | 89 TEST0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| P70/AIN16/INT7/TB1IN 93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              | 88 RESET (注2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| P67/AIN15/INT6/ADTRG1 94                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |              | 87 P80/TX0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| P66/AIN14/INT5 95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |              | 86 P81/RX0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| P65/AIN13/INT4 96                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |              | 85 P82/TX1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| P64/AIN12/INT3 97                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |              | 84 P83/RX1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| P63/AIN11 98                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |              | 83 P84/INT0/TB10UT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| P62/AIN10 99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |              | 82 P85/RX2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| P61/AIN9 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |              | 81 CVCC2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <u> </u>     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| P60/AIN8 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |              | ⊐ <u>80 X2</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| AVCC1/VREFH1 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| AVSS 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -            | <b>P</b> 78 X1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| AVCCO/VREFH0 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| P50/AIN0 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4            | 76 P87/SCLK2/CTS2/PCST4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| P51/AIN1 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| P52/AIN2 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| P53/AIN3 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| P54/AIN4 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1            | □ 72 P32/PCST1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| P55/AIN5 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4            | - 71 P31/PCST0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| P56/AIN6 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |              | 70 P30/TPC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| P57/AIN7/ADTRG0 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |              | - 69 P24/DINT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| DVCC2 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |              | - 68 P23/TD0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| P90/ENCA/RX3 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              | - 67 P22/TD1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| P91/ENCB/TX3 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | TMP19A71FYFG | -66 P21/TMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| D00 /FN07 /COLV2 /0TC2 16 -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| P92/ENCZ/SCLK3/CTS3 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |              | 65 P20/TCK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| DVCC3/FVCC3 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |              | 65 P20/TCK     64 TEST1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| DVCC3/FVCC3 17<br>DVCC2/FVCC2 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |              | 65         P20/TCK           64         TEST1           63         DVCC3/FVCC3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| DVCC3/FVCC3         17           DVCC2/FVCC2         18           DVSS/FVSS         19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |              | 65 P20/TCK     64 TEST1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| DVCC3/FVCC3         17           DVCC2/FVCC2         18           DVSS/FVSS         19           P93/TB01N         20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |              | 65         P20/TCK           64         TEST1           63         DVCC3/FVCC3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| DVCC3/FVCC3         17           DVCC2/FVCC2         18           DVSS/FVSS         19           P93/TB01N         20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |              | 65         P20/TCK           64         TEST1           63         DVCC3/FVCC3           62         DVCC2/FVCC2           61         DVSS/FVSS                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| DVCC3/FVCC3         17           DVCC2/FVCC2         18           DVSS/FVSS         19           P93/TB01N         20           P94/TB00UT/B00T(注2)         21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |              | 65         P20/TCK           64         TEST1           63         DVCC3/FVCC3           62         DVCC2/FVCC2           61         DVSS/FVSS           60         EJE(注2)                                                                                                                                                                                                                                                                                                                                                                                                                       |

| DVCC3/FVCC3         17           DVCC2/FVCC2         18           DVSS/FVSS         19           P93/TB01N         20           P94/TB00UT/B00T(注2)         21           P95/NMI         22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |              | 65         P20/TCK           64         TEST1           63         DVCC3/FVCC3           62         DVCC2/FVCC2           61         DVSS/FVSS           60         EJE(注2)           59         FVCC2                                                                                                                                                                                                                                                                                                                                                                                            |

| DVCC3/FVCC3         17           DVCC2/FVCC2         18           DVSS/FVSS         19           P93/TB01N         20           P94/TB00UT/B00T(注2)         21           P95/NMI         22           FVCC2         23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |              | 65         P20/TCK           64         TEST1           63         DVCC3/FVCC3           62         DVCC2/FVCC2           61         DVSS/FVSS           60         EJE (注 2)           59         FVCC2           58         FVSS                                                                                                                                                                                                                                                                                                                                                                |

| DVCC3/FVCC3         17           DVCC2/FVCC2         18           DVSS/FVSS         19           P93/TB01N         20           P94/TB00UT/B00T(注2)         21           P95/NMI         22           FVCC2         23           FVSS         24                                                                                                                                                                                                                                                                                                                                                                                                                                                               |              | 65         P20/TCK           64         TEST1           63         DVCC3/FVCC3           62         DVCC2/FVCC2           61         DVSS/FVSS           60         EJE (注 2)           59         FVCC2           58         FVSS           57         P17                                                                                                                                                                                                                                                                                                                                       |

| DVCC3/FVCC3         17           DVCC2/FVCC2         18           DVSS/FVSS         19           P93/TB01N         20           P94/TB00UT/B00T(注2)         21           P95/NMI         22           FVCC2         23           FVSS         24           PA0/U0         25                                                                                                                                                                                                                                                                                                                                                                                                                                   |              | 65         P20/TCK           64         TEST1           63         DVCC3/FVCC3           62         DVCC2/FVCC2           61         DVSS/FVSS           60         EJE (注 2)           59         FVCC2           58         FVSS           57         P17           56         P16                                                                                                                                                                                                                                                                                                              |

| DVCC3/FVCC3         17           DVCC2/FVCC2         18           DVSS/FVSS         19           P93/TB01N         20           P94/TB00UT/B00T(注2)         21           P95/NMI         22           FVCC2         23           FVSS         24           PA0/U0         25           PA1/X0         26                                                                                                                                                                                                                                                                                                                                                                                                       |              | 65         P20/TCK           64         TEST1           63         DVCC3/FVCC3           62         DVCC2/FVCC2           61         DVSS/FVSS           60         EJE (注 2)           59         FVCC2           58         FVSS           57         P17           56         P16           55         P15                                                                                                                                                                                                                                                                                     |

| DVCC3/FVCC3         17           DVCC2/FVCC2         18           DVSS/FVSS         19           P93/TB01N         20           P94/TB00UT/B00T(注2)         21           P95/NMI         22           FVCC2         23           FVSS         24           PA0/U0         25           PA1/X0         26           PA2/V0         27                                                                                                                                                                                                                                                                                                                                                                           |              | 65         P20/TCK           64         TEST1           63         DVCC3/FVCC3           62         DVCC2/FVCC2           61         DVSS/FVSS           60         EJE (注 2)           59         FVCC2           58         FVSS           57         P17           56         P16           55         P15           54         P14                                                                                                                                                                                                                                                            |

| DVCC3/FVCC3         17           DVCC2/FVCC2         18           DVSS/FVSS         19           P93/TB01N         20           P94/TB00UT/B00T(注2)         21           P95/NMI         22           FVCC2         23           FVCC2         23           FVSS         24           PA0/U0         25           PA1/X0         26           PA2/V0         27           PA3/Y0         28                                                                                                                                                                                                                                                                                                                    |              | 65         P20/TCK           64         TEST1           63         DVCC3/FVCC3           62         DVCC2/FVCC2           61         DVSS/FVSS           60         EJE (注 2)           59         FVCC2           58         FVSS           57         P17           56         P16           55         P15           54         P14           53         P13                                                                                                                                                                                                                                   |

| DVCC3/FVCC3         17           DVCC2/FVCC2         18           DVSS/FVSS         19           P93/TB01N         20           P94/TB00UT/B00T(注2)         21           P95/NMI         22           FVCC2         23           FVSS         24           PA0/U0         25           PA1/X0         26           PA2/V0         27                                                                                                                                                                                                                                                                                                                                                                           |              | 65         P20/TCK           64         TEST1           63         DVCC3/FVCC3           62         DVCC2/FVCC2           61         DVSS/FVSS           60         EJE (注 2)           59         FVCC2           58         FVSS           57         P17           56         P16           55         P15           54         P14                                                                                                                                                                                                                                                            |

| DVCC3/FVCC3         17           DVCC2/FVCC2         18           DVSS/FVSS         19           P93/TB01N         20           P94/TB00UT/B00T(注2)         21           P95/NMI         22           FVCC2         23           FVCC2         23           FVSS         24           PA0/U0         25           PA1/X0         26           PA2/V0         27           PA3/Y0         28                                                                                                                                                                                                                                                                                                                    |              | 65         P20/TCK           64         TEST1           63         DVCC3/FVCC3           62         DVCC2/FVCC2           61         DVSS/FVSS           60         EJE (注 2)           59         FVCC2           58         FVSS           57         P17           56         P16           55         P15           54         P14           53         P13                                                                                                                                                                                                                                   |

| DVCC3/FVCC3         17           DVCC2/FVCC2         18           DVSS/FVSS         19           P93/TB01N         20           P94/TB00UT/B00T(注2)         21           P95/NMI         22           FVCC2         23           FVCC2         23           FVSS         24           PA0/U0         25           PA1/X0         26           PA2/V0         27           PA3/Y0         28           PA4/WO         29                                                                                                                                                                                                                                                                                        |              | 65         P20/TCK           64         TEST1           63         DVCC3/FVCC3           62         DVCC2/FVCC2           61         DVSS/FVSS           60         EJE (注 2)           59         FVCC2           58         FVSS           57         P17           56         P16           55         P15           54         P14           53         P13           52         P12                                                                                                                                                                                                          |

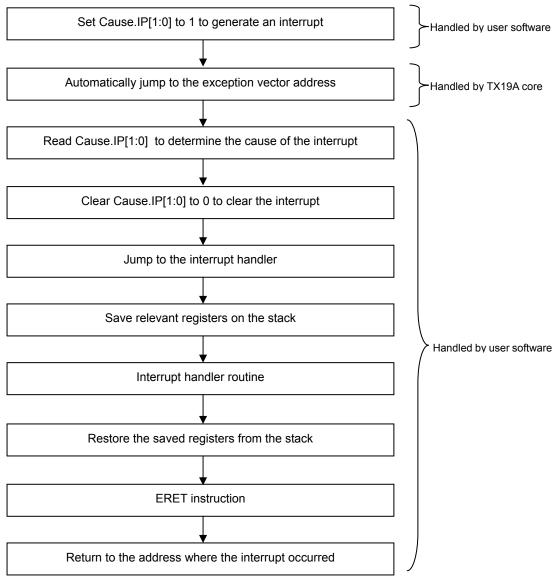

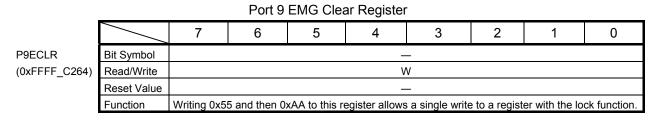

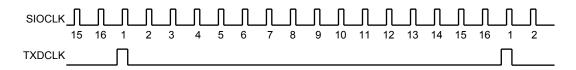

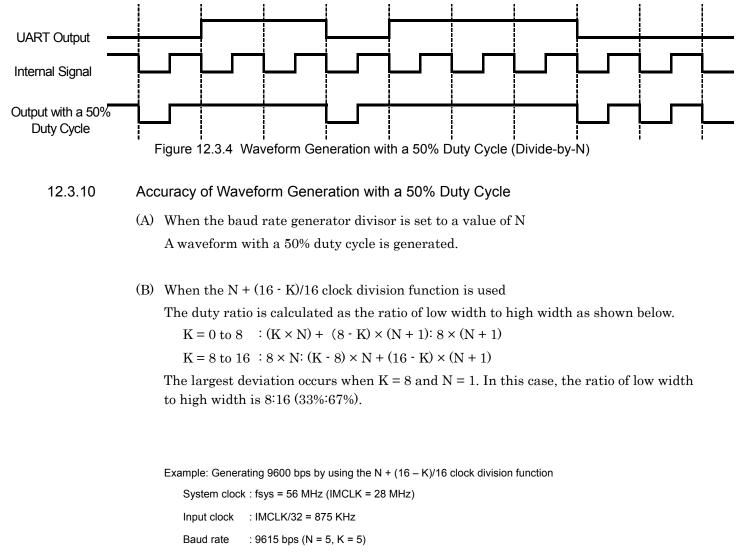

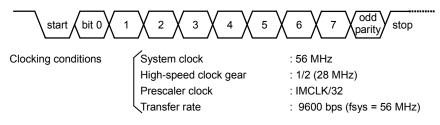

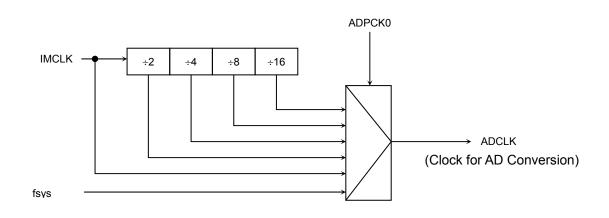

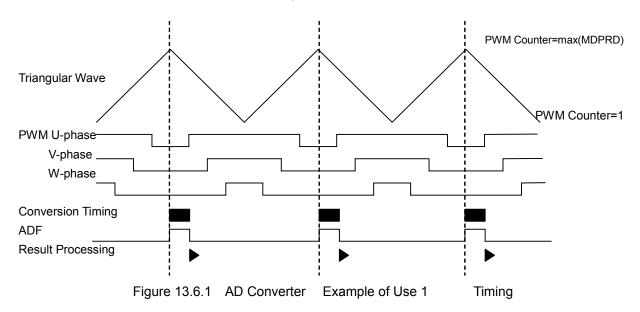

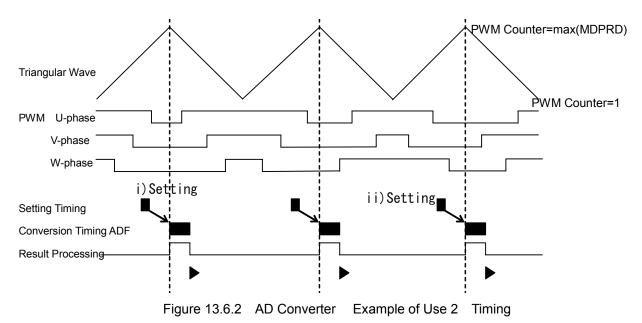

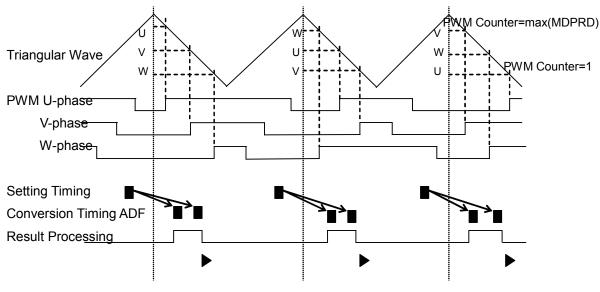

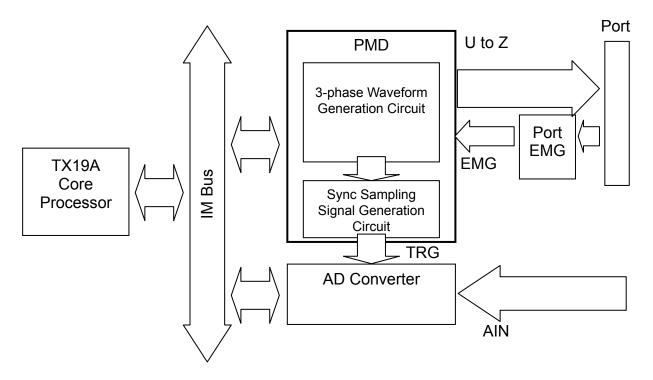

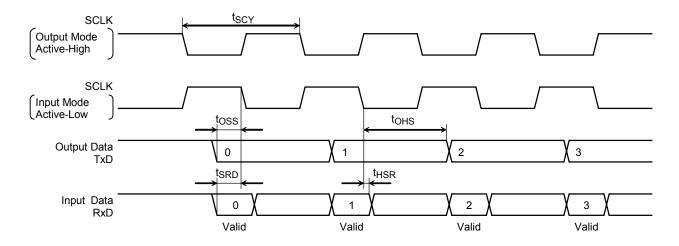

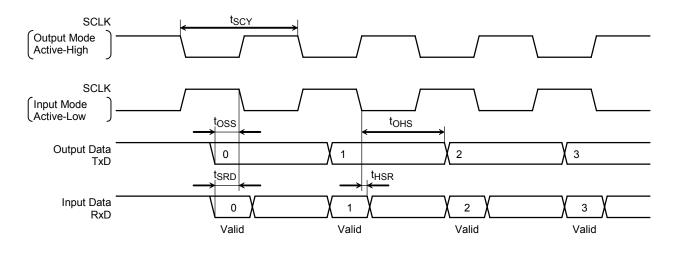

| DVCC3/FVCC3         17           DVCC2/FVCC2         18           DVSS/FVSS         19           P93/TB01N         20           P94/TB00UT/B00T(注2)         21           P95/NMI         22           FVCC2         23           FVCC2         23           FVSS         24           PA0/U0         25           PA1/X0         26           PA2/V0         27           PA3/Y0         28           PA4/W0         29           PA5/Z0         30                                                                                                                                                                                                                                                            |              | 65         P20/TCK           64         TEST1           63         DVCC3/FVCC3           62         DVCC2/FVCC2           61         DVSS/FVSS           60         EJE (注 2)           59         FVCC2           58         FVSS           57         P17           56         P16           55         P15           54         P14           52         P12           51         P11                                                                                                                                                                                                          |