The information contained herein is subject to change without notice.

The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of TOSHIBA or others.

TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress.

It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property.

In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications.

Also, please keep in mind the precautions and conditions set forth in the 'Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc..

The Toshiba products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.).

These Toshiba products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of Toshiba products listed in this document shall be made at the customer's own risk.

The products described in this document may include products subject to the foreign exchange and foreign trade laws.

The products described in this document contain components made in the United States and subject to export control of the U.S. authorities. Diversion contrary to the U.S. law is prohibited.

TOSHIBA products should not be embedded to the downstream products which are prohibited to be produced and sold, under any law and regulations.

MIPS16, application Specific Extensions and R3000A are a trademark of MIPS Technologies, Inc.

# Table of Contents

## Handling precautions

| 1. Outline a   | nd Features                                                                                      | 1-1         |

|----------------|--------------------------------------------------------------------------------------------------|-------------|

| 1.1 Out        | ine                                                                                              | 1-1         |

| 1.2 Nota       | ation Used in This Manual                                                                        | 1-2         |

| 1.2.1          | Numerical Notation                                                                               |             |

| 1.2.2          | Data Notation                                                                                    |             |

| 1.2.3          | Signal Notation                                                                                  |             |

| 1.2.4          | Register Notation                                                                                |             |

| 1.3 Feat       | ures                                                                                             | 1-3         |

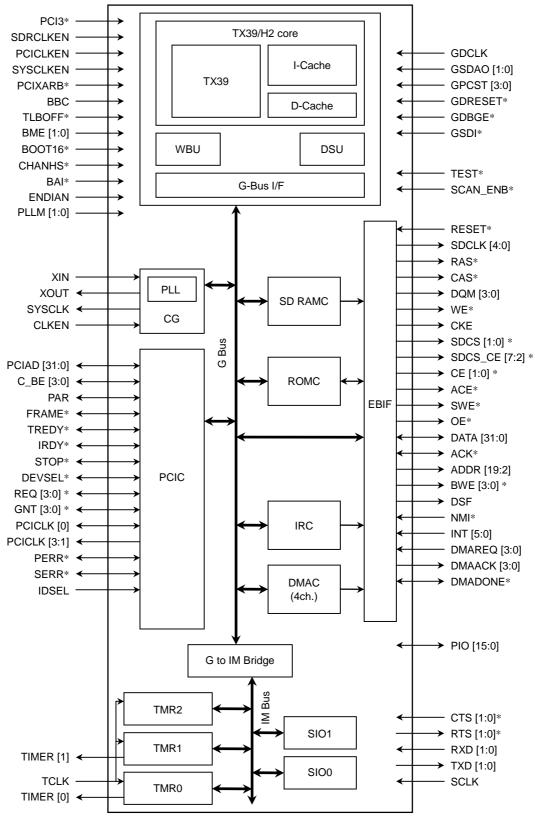

| 2. Structure   |                                                                                                  | 2-1         |

| 2.1 Bloc       | k Diagram                                                                                        | 2-1         |

| 3. Pins        |                                                                                                  | 3-1         |

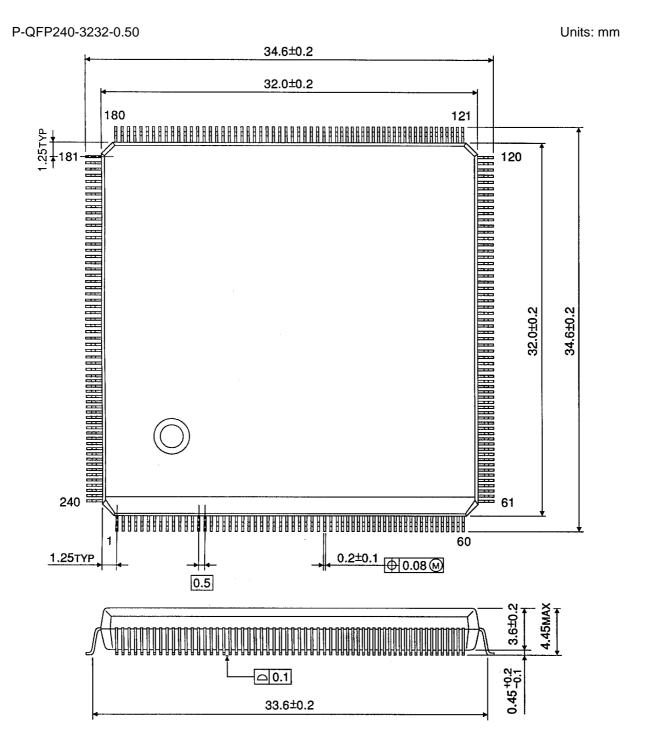

| 3.1 Pino       | out                                                                                              | 3-1         |

| 3.2 Pin        | Description                                                                                      | 3-3         |

| 3.3 Pin        | Multiplexing                                                                                     | 3-9         |

|                | al Setting Signals                                                                               |             |

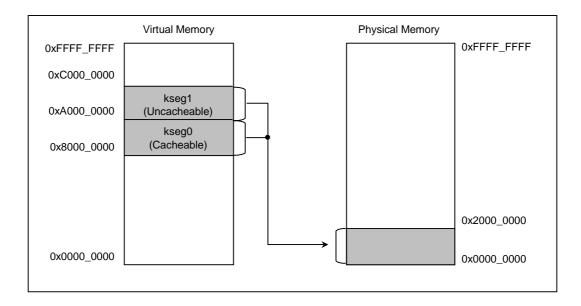

| 4 Address M    | Ларрing                                                                                          | <i>A</i> _1 |

|                | nory Mapping                                                                                     |             |

|                | ister Mapping                                                                                    |             |

| Č              |                                                                                                  |             |

| •              | tion                                                                                             |             |

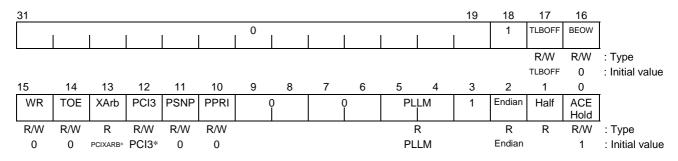

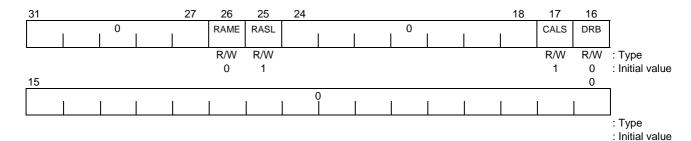

| -              | Configuration Register (CCFG) 0xFFFE_E000                                                        |             |

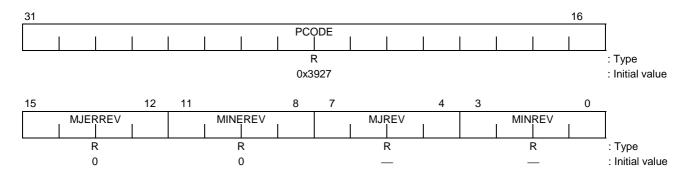

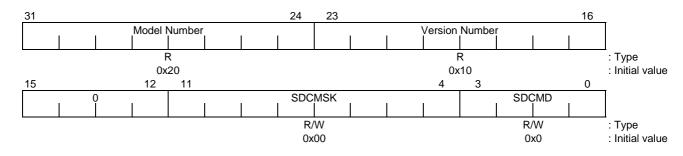

| 5.1.1          | Chip Revision ID Register (CRIR) 0xFFFE_E004                                                     |             |

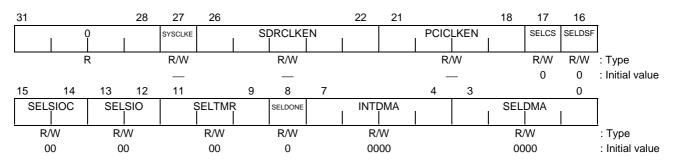

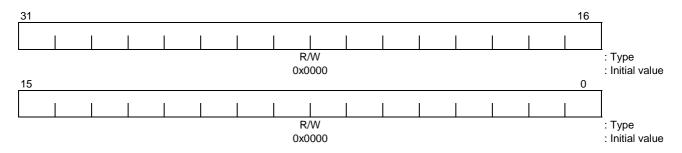

| 5.1.2<br>5.1.3 | Pin Configuration Register (PCFG) 0xFFFE_E008  Timeout Error Address Register (TEAR) 0xFFFE_E00C |             |

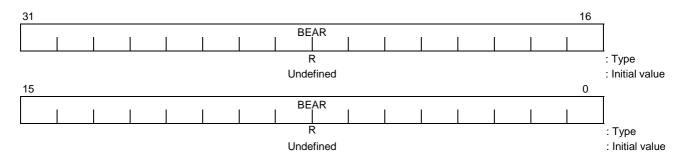

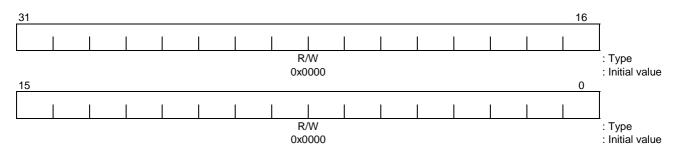

|                |                                                                                                  |             |

| 6. Clocks      |                                                                                                  |             |

|                | k Generator                                                                                      |             |

| 6.2 Syst       | em Control Clock (SYSCLK)                                                                        | 6-1         |

|                | er-Down Mode                                                                                     |             |

| 6.3.1          | Operation                                                                                        |             |

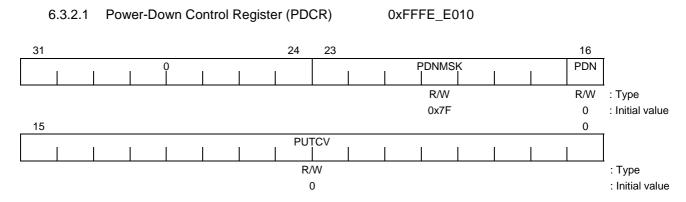

| 6.3.2          | Register                                                                                         |             |

| 7. Bus Oper    | ation                                                                                            | 7-1         |

|                | Mastership                                                                                       |             |

| 7.1.1          | Snoop Function                                                                                   |             |

| 7.1.2          | Relationship Between the Endian Mode and Data Bus                                                |             |

|                | Operation                                                                                        |             |

| 7.2.1          | Bus Error                                                                                        | 7-4         |

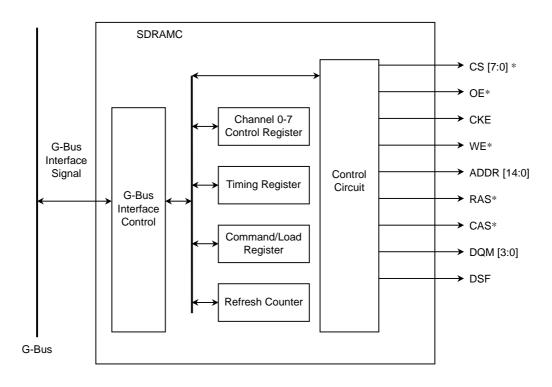

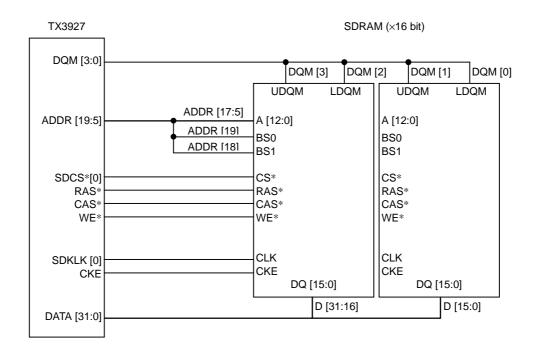

| 8. SDRAM       | Controller                                                                                       | 8-1         |

| 8.1 Feat       | ures                                                                                             | 8-1         |

| 8.2 SDF        | AM Block Diagram                                                                                 | 8-3         |

| 8.3 Mer        | nory Configuration                                                                               | 8-4         |

| 8.4 Reg        | isters                                                                                           | 8-5         |

| 8.4.1          | Register Mapping                                                                                 | 8-5         |

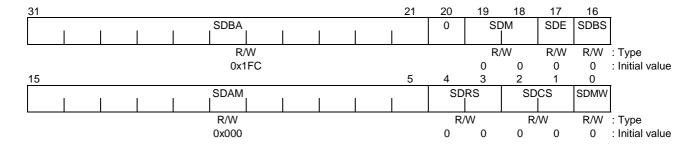

| 8.4.2          | SDRAM Channel Control Registers (SDCCR0-SDCCR7) 0xFFFE_8000 (ch.0)                               |             |

|                | 0xFFFE_8004 (ch.1) 0xFFFE_8008 (ch.2) 0xFFFE_800C (ch.3) 0xFFFE_8010 (ch.4)                      | 0.6         |

| 8.4.3          | 0xFFFE_8014 (ch.5) 0xFFFE_8018 (ch.6) 0xFFFE_801C (ch.7)                                         |             |

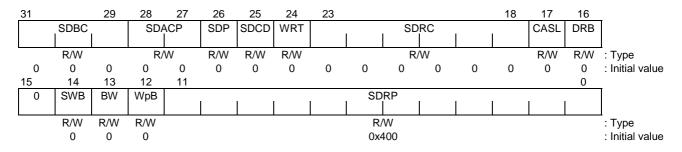

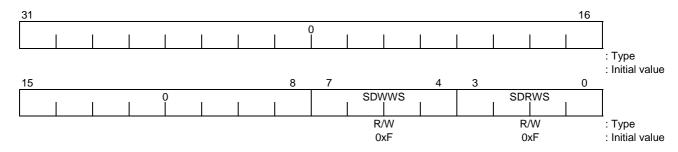

| 8.4.4          | SDRAM Timing Register 1 (for SDRAM/SGRAM) (SDCTR1) 0xFFFE_6020                                   |             |

| 8.4.5          | SDRAM Timing Register 3 (for SMROM) (SDCTR3) 0xFFFE_8028                                         |             |

|                |                                                                                                  |             |

|    | 8.4.6                                                                                                                                                            | SDRAM Command Register (SDCCMD) 0xFFFE_802C                                                                                                                                                                                                                                                                                                                                                                               | 8-12                                                            |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

|    | 8.4.7                                                                                                                                                            | SGRAM Load Mask Register (SDCSMRS1) 0xFFFE_8030                                                                                                                                                                                                                                                                                                                                                                           | 8-13                                                            |

|    | 8.4.8                                                                                                                                                            | SGRAM Load Color Register (SDCSMRS2) 0xFFFE_8034                                                                                                                                                                                                                                                                                                                                                                          | 8-13                                                            |

|    | 8.5 Ope                                                                                                                                                          | ration                                                                                                                                                                                                                                                                                                                                                                                                                    | 8-14                                                            |

|    | 8.5.1                                                                                                                                                            | TX3927 Signals for Different Memory Types                                                                                                                                                                                                                                                                                                                                                                                 |                                                                 |

|    | 8.5.2                                                                                                                                                            | SDRAM Operation                                                                                                                                                                                                                                                                                                                                                                                                           | 8-15                                                            |

|    | 8.5.3                                                                                                                                                            | DIMM Flash Memory Operation                                                                                                                                                                                                                                                                                                                                                                                               | 8-22                                                            |

|    | 8.5.4                                                                                                                                                            | SMROM Operation                                                                                                                                                                                                                                                                                                                                                                                                           | 8-25                                                            |

|    | 8.5.5                                                                                                                                                            | SGRAM Operation                                                                                                                                                                                                                                                                                                                                                                                                           | 8-27                                                            |

|    | 8.5.6                                                                                                                                                            | Notes on Programming                                                                                                                                                                                                                                                                                                                                                                                                      | 8-28                                                            |

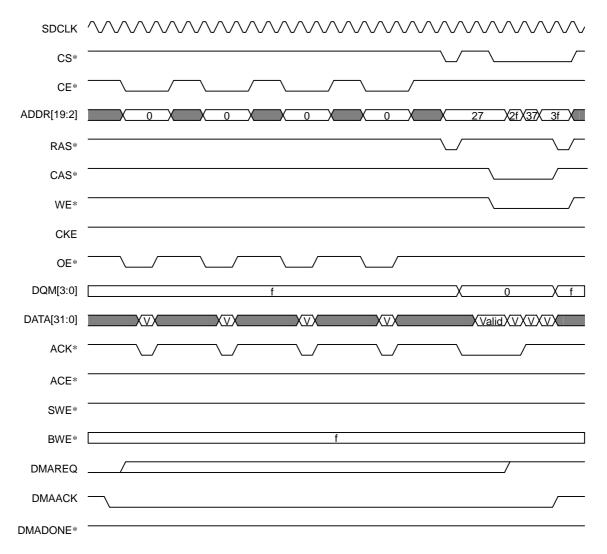

|    | 8.6 Tim                                                                                                                                                          | ing Diagrams                                                                                                                                                                                                                                                                                                                                                                                                              | 8-29                                                            |

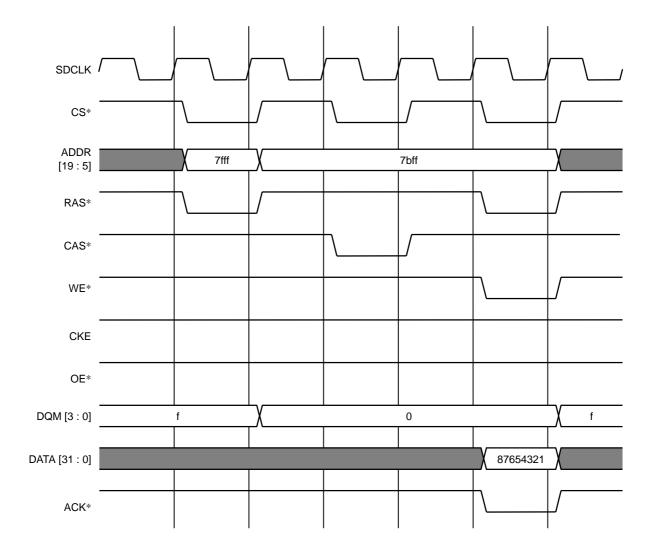

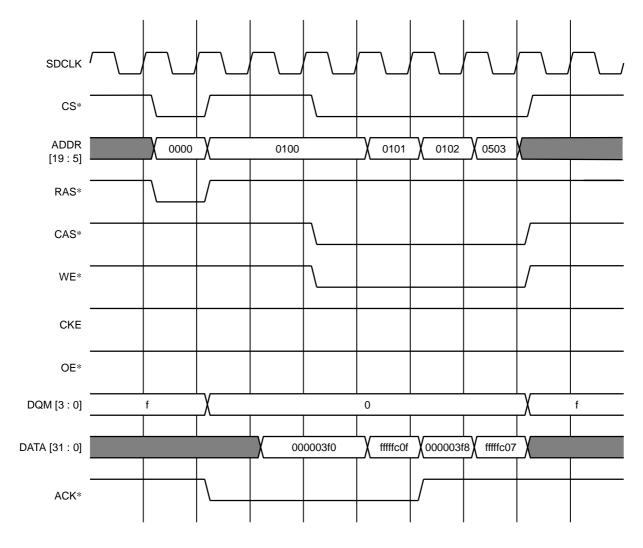

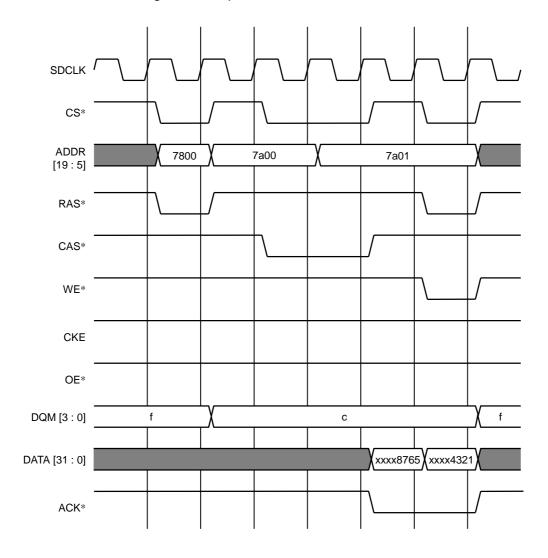

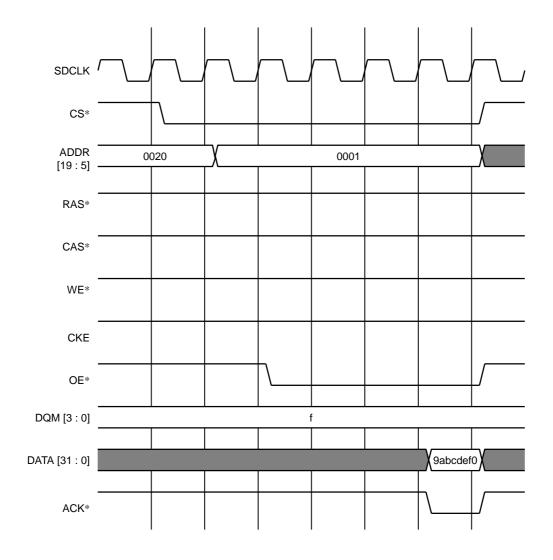

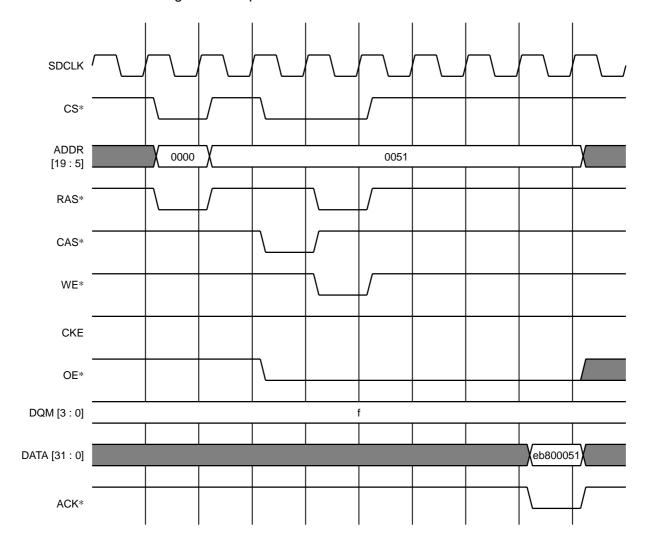

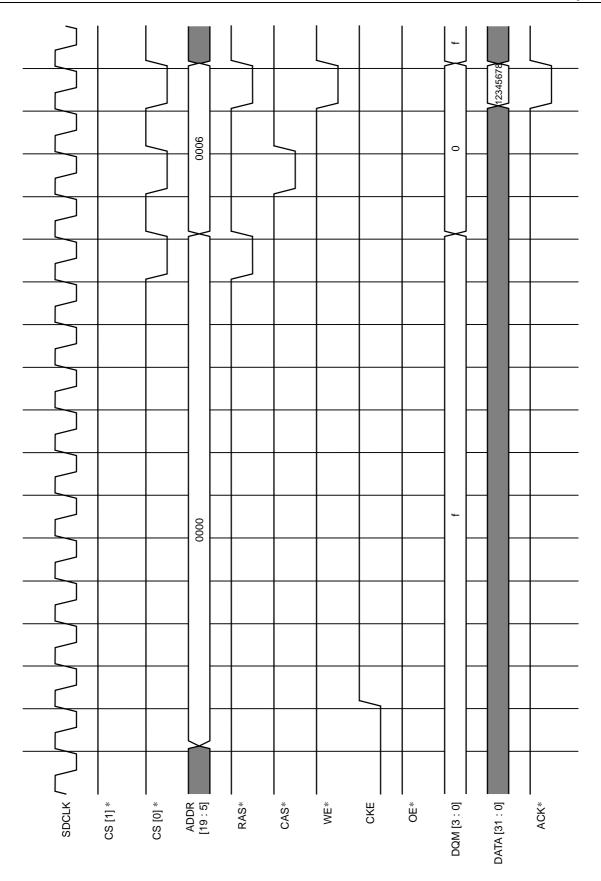

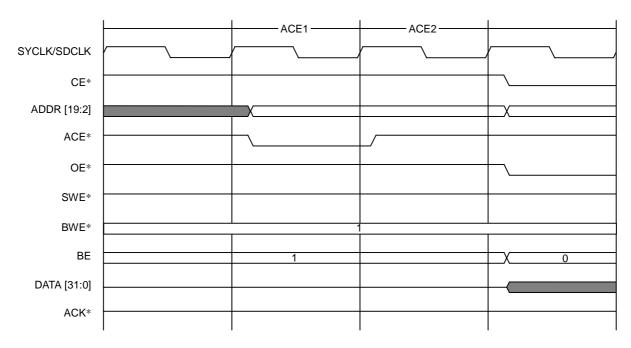

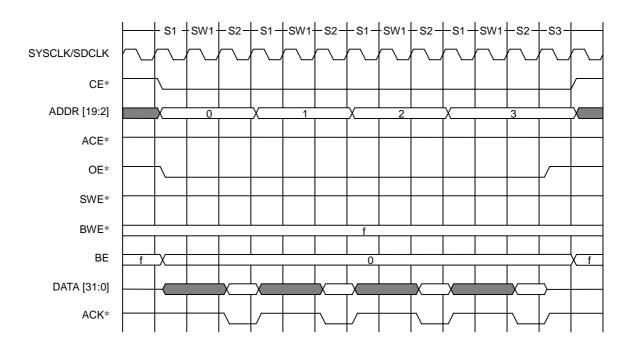

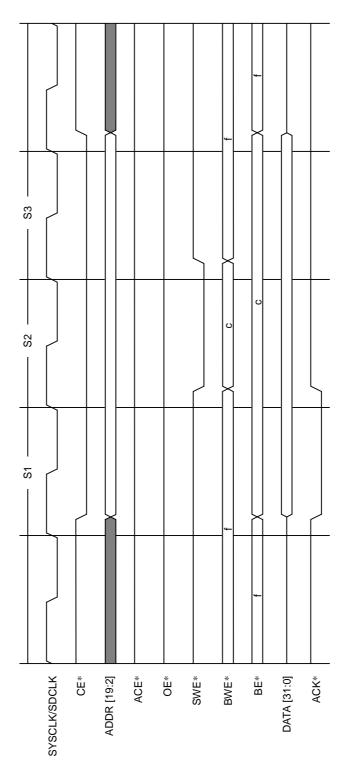

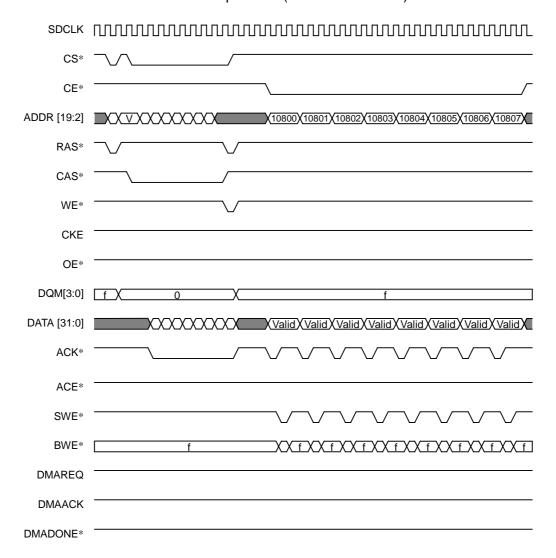

|    | 8.6.1                                                                                                                                                            | SDRAM Single Read Operation in 32-bit Bus Mode                                                                                                                                                                                                                                                                                                                                                                            |                                                                 |

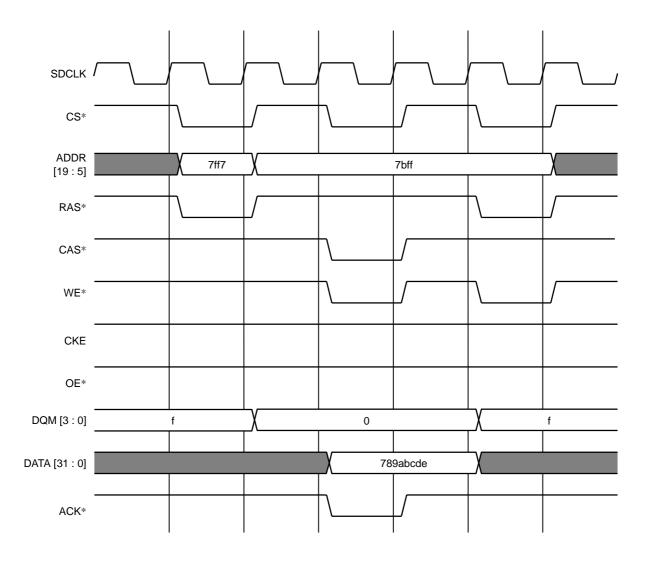

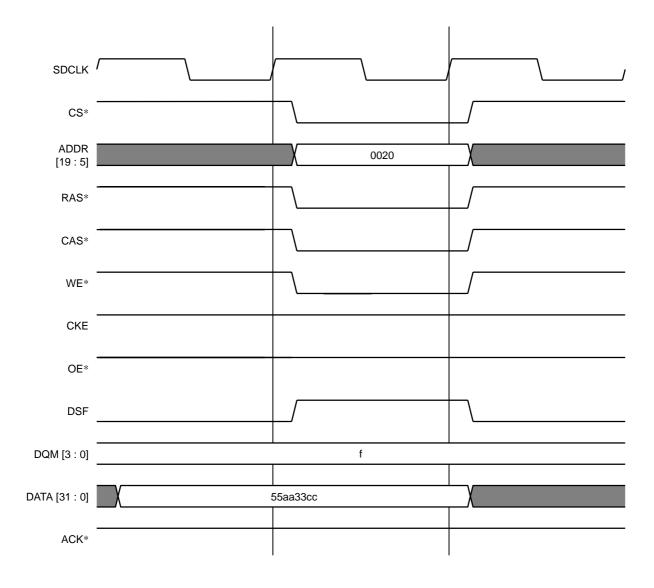

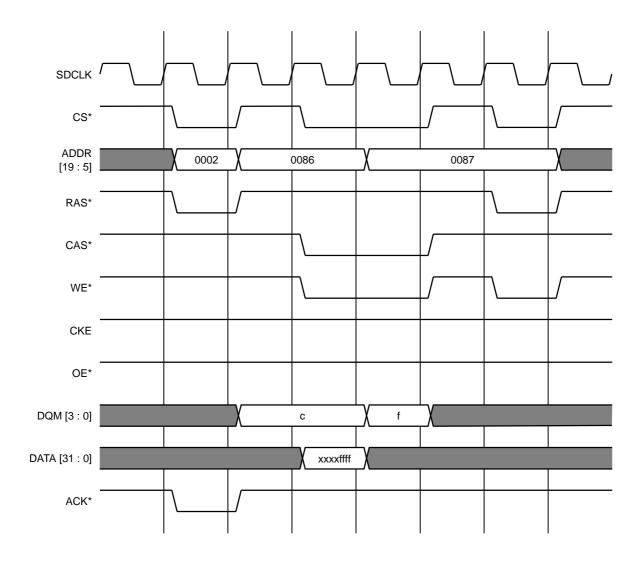

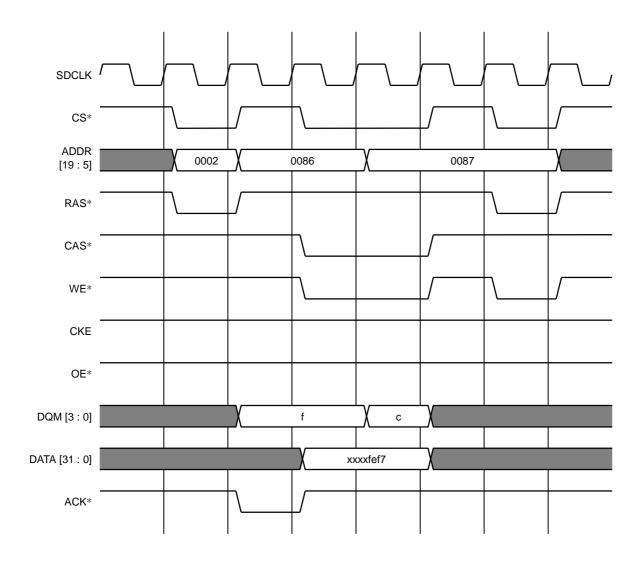

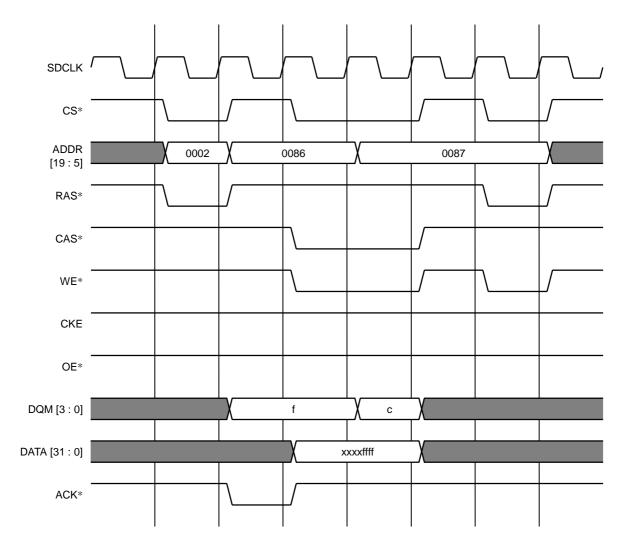

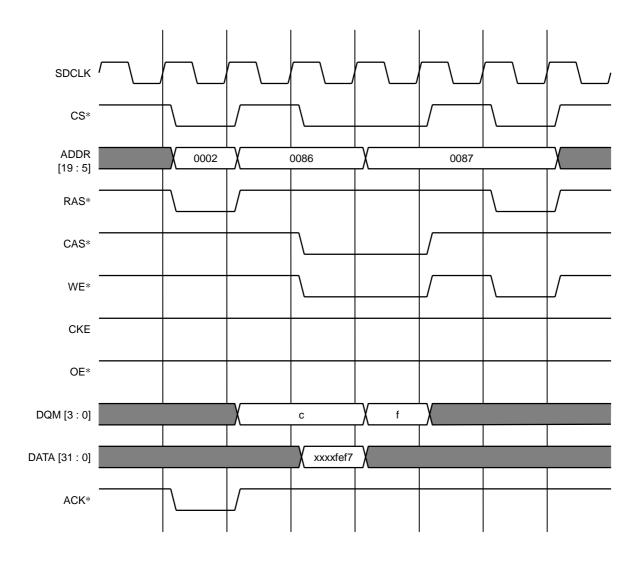

|    | 8.6.2                                                                                                                                                            | SDRAM Single Write Operation in 32-bit Bus Mode                                                                                                                                                                                                                                                                                                                                                                           |                                                                 |

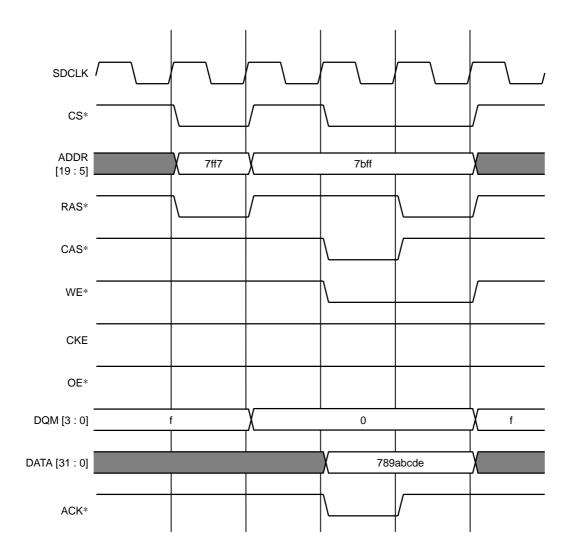

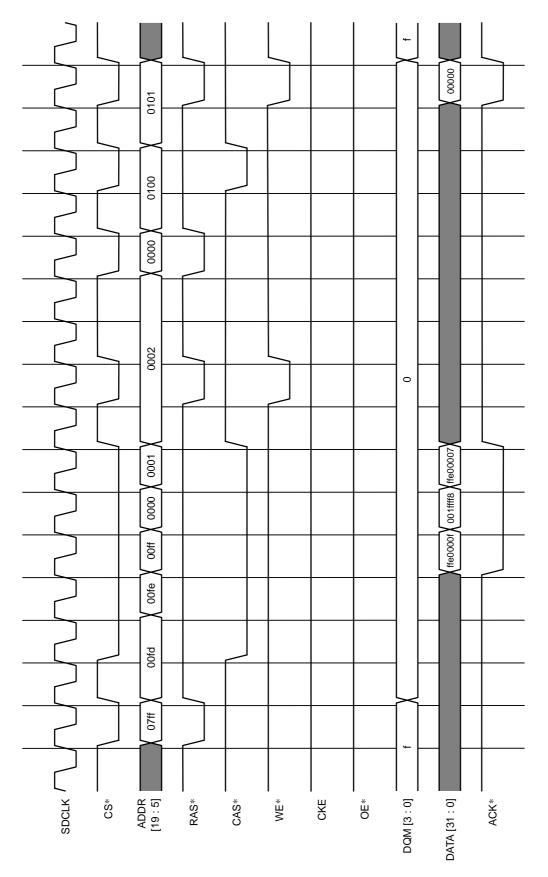

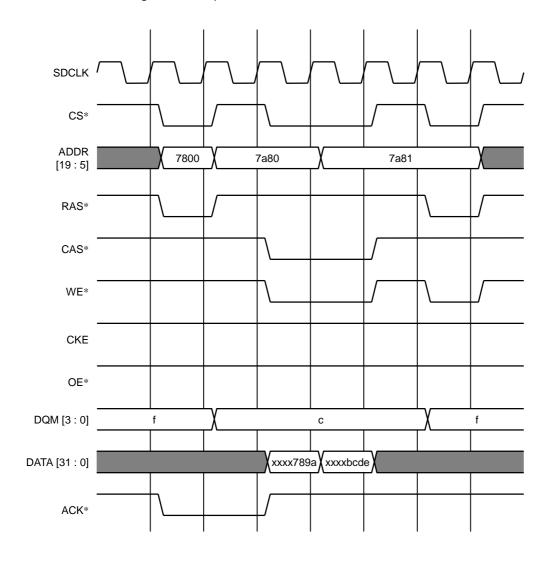

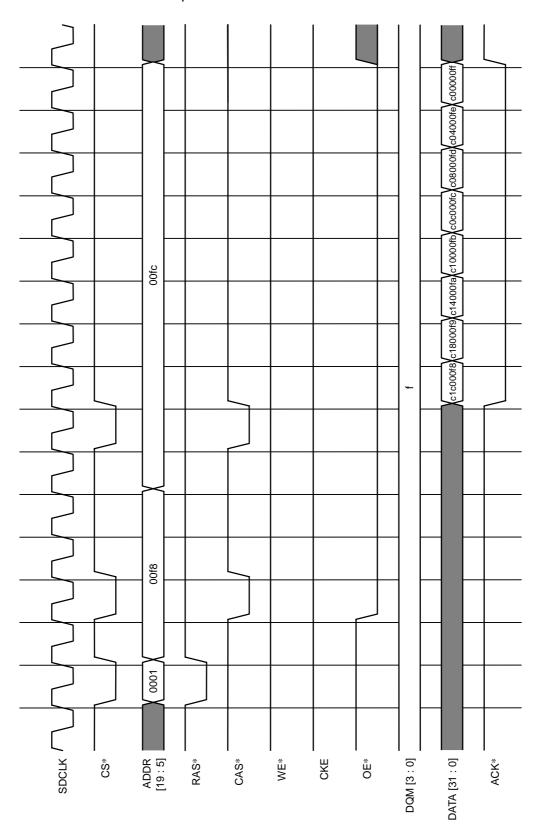

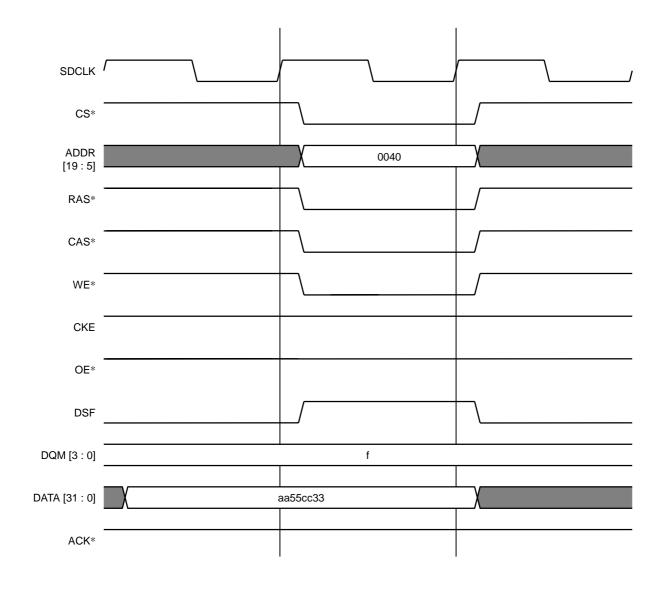

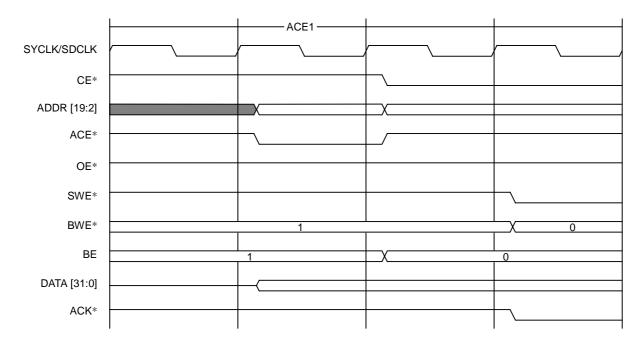

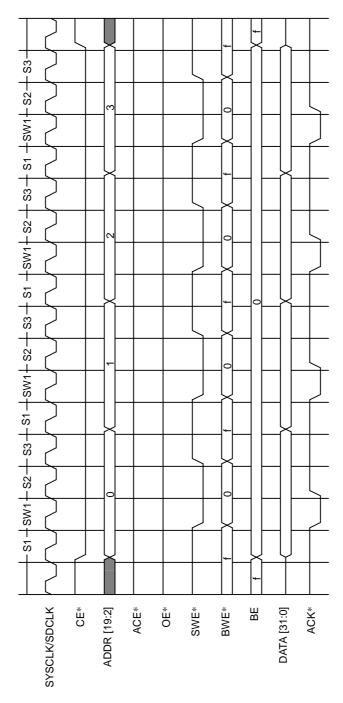

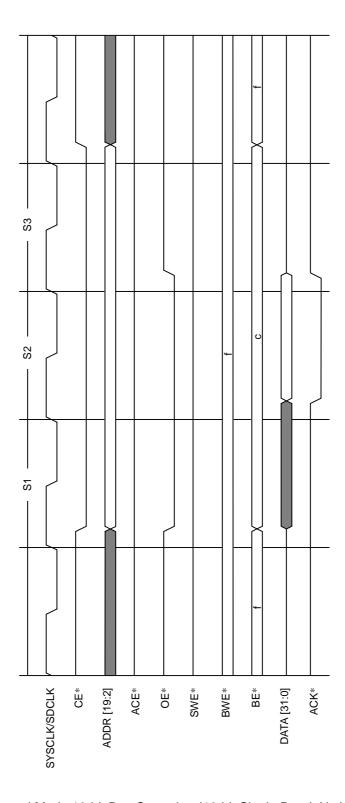

|    | 8.6.3                                                                                                                                                            | SDRAM Burst Read Operation in 32-bit Bus Mode                                                                                                                                                                                                                                                                                                                                                                             |                                                                 |

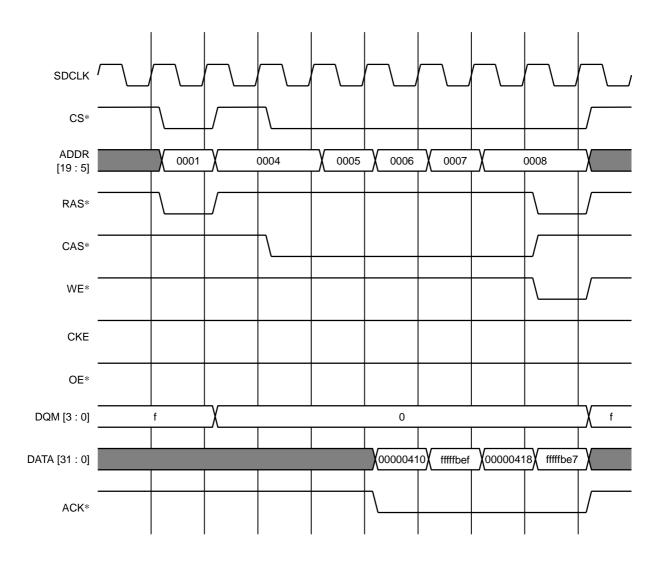

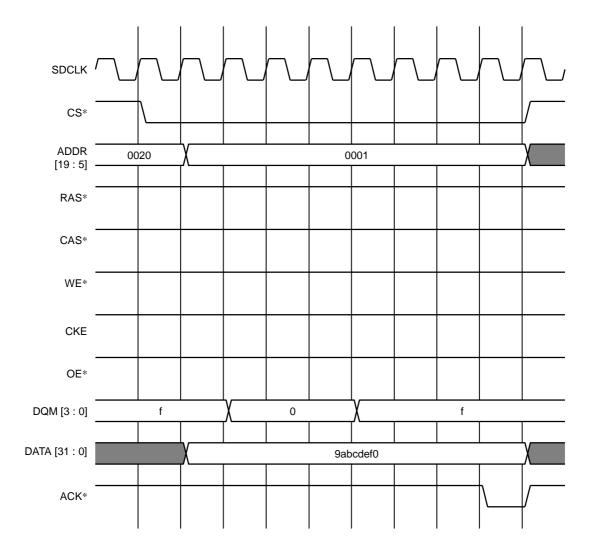

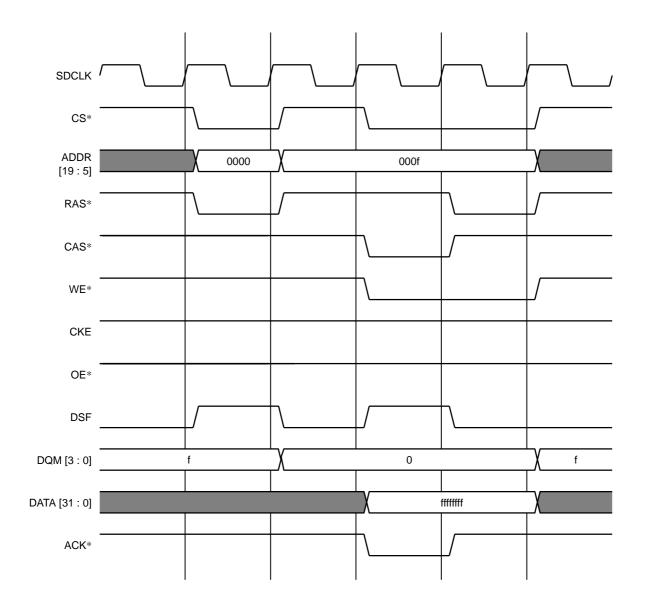

|    | 8.6.4                                                                                                                                                            | SDRAM Burst Write Operation in 32-bit Bus Mode                                                                                                                                                                                                                                                                                                                                                                            |                                                                 |

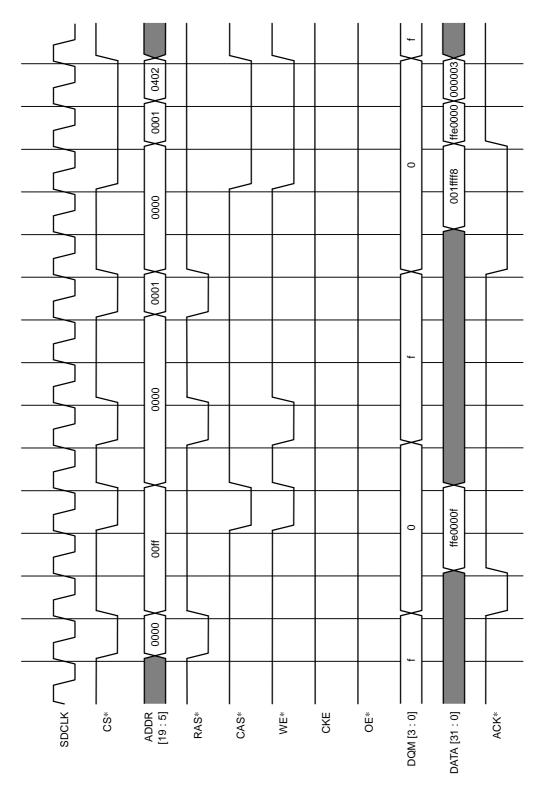

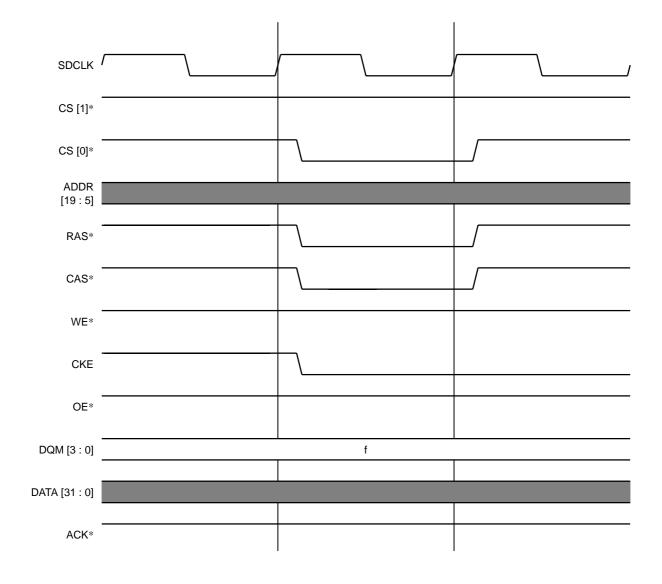

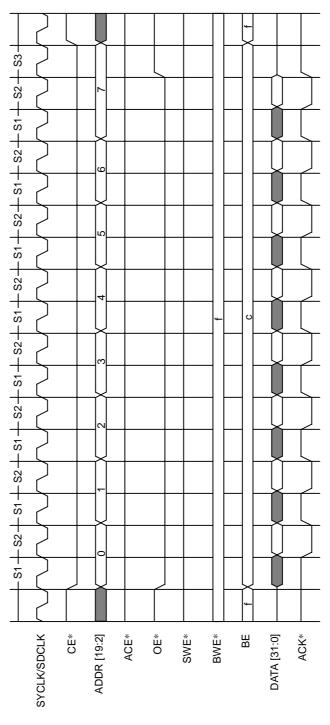

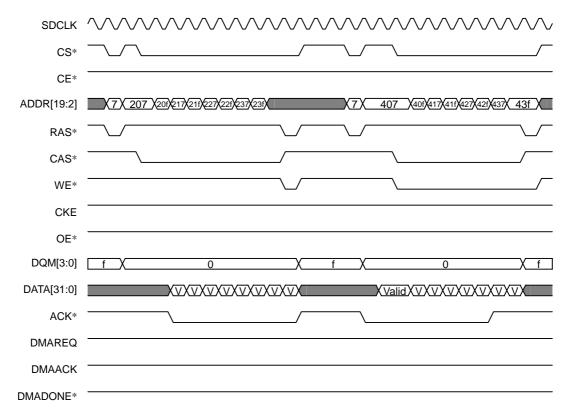

|    | 8.6.5                                                                                                                                                            | SDRAM Read in 32-bit Bus Mode (Crossing Page Boundary)                                                                                                                                                                                                                                                                                                                                                                    |                                                                 |

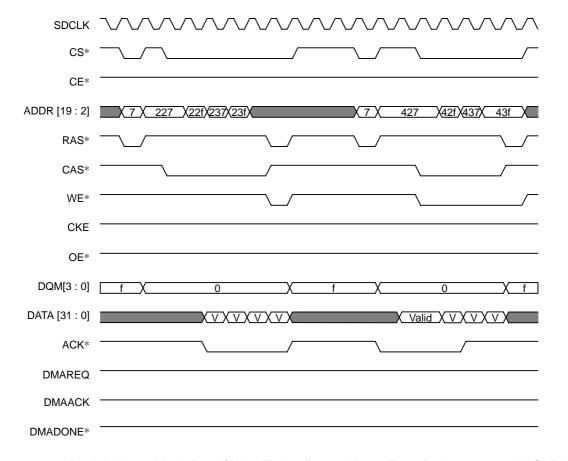

|    | 8.6.6                                                                                                                                                            | SDRAM Write in 32-bit Bus Mode (Crossing Page Boundary)                                                                                                                                                                                                                                                                                                                                                                   |                                                                 |

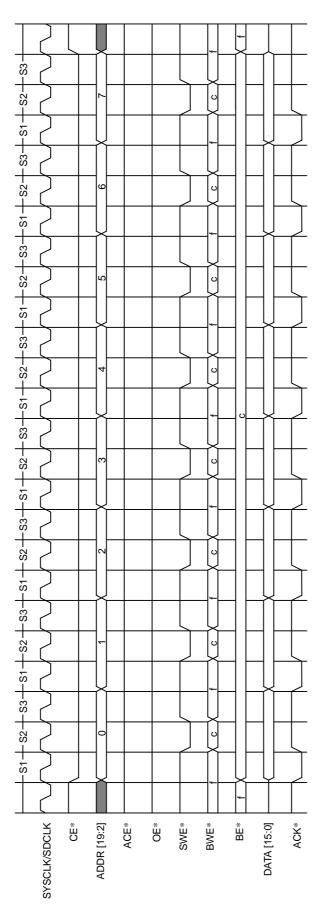

|    | 8.6.7                                                                                                                                                            | SDRAM Slow Burst Write Operation in 32-bit Bus Mode                                                                                                                                                                                                                                                                                                                                                                       | 8-36                                                            |

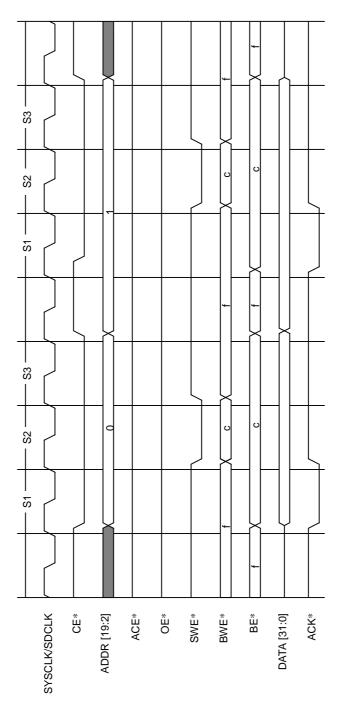

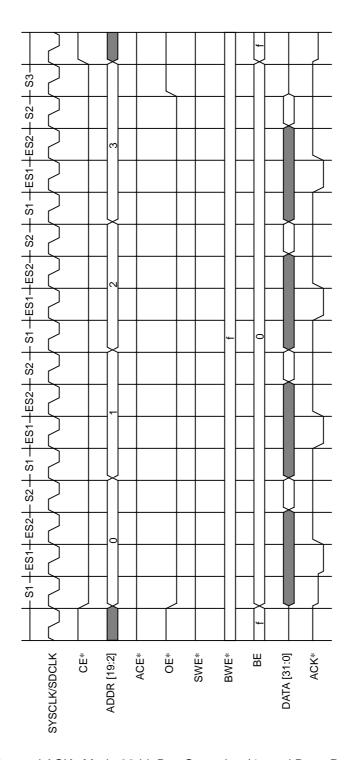

|    | 8.6.8                                                                                                                                                            | SDRAM Single Read Operation in 16-bit Bus Mode                                                                                                                                                                                                                                                                                                                                                                            | 8-37                                                            |

|    | 8.6.9                                                                                                                                                            | SDRAM Single Write Operation in 16-bit Bus Mode                                                                                                                                                                                                                                                                                                                                                                           | 8-38                                                            |

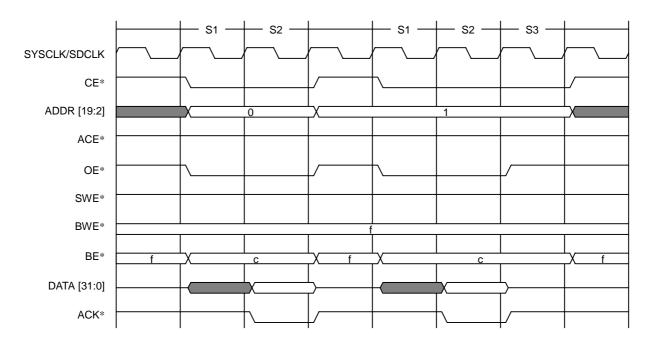

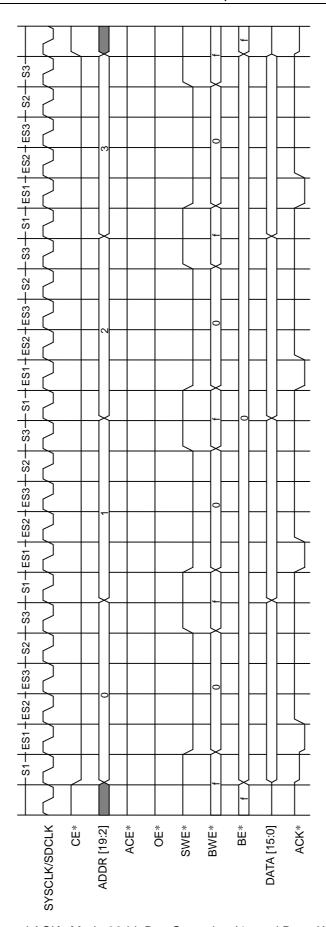

|    | 8.6.10                                                                                                                                                           | DIMM Flash Memory Single Read Operation in 32-bit Bus Mode                                                                                                                                                                                                                                                                                                                                                                | 8-39                                                            |

|    | 8.6.11                                                                                                                                                           | DIMM Flash Memory Single Write Operation in 32-bit Bus Mode                                                                                                                                                                                                                                                                                                                                                               | 8-40                                                            |

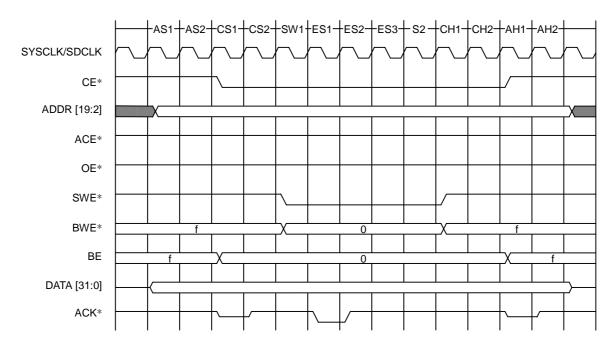

|    | 8.6.12                                                                                                                                                           | SMROM Single Read Operation in 32-bit Bus Mode                                                                                                                                                                                                                                                                                                                                                                            | 8-41                                                            |

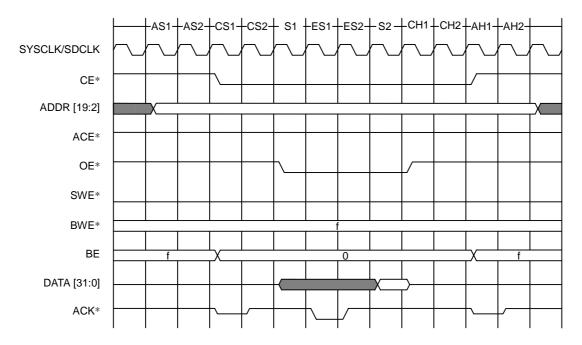

|    | 8.6.13                                                                                                                                                           | SMROM Burst Read Operation in 32-bit Bus Mode                                                                                                                                                                                                                                                                                                                                                                             | 8-42                                                            |

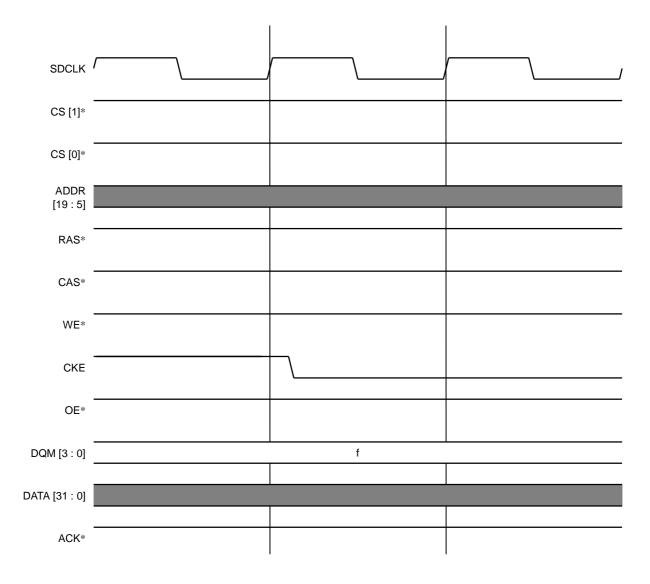

|    | 8.6.14                                                                                                                                                           | Low Power and Power-down Mode                                                                                                                                                                                                                                                                                                                                                                                             | 8-43                                                            |

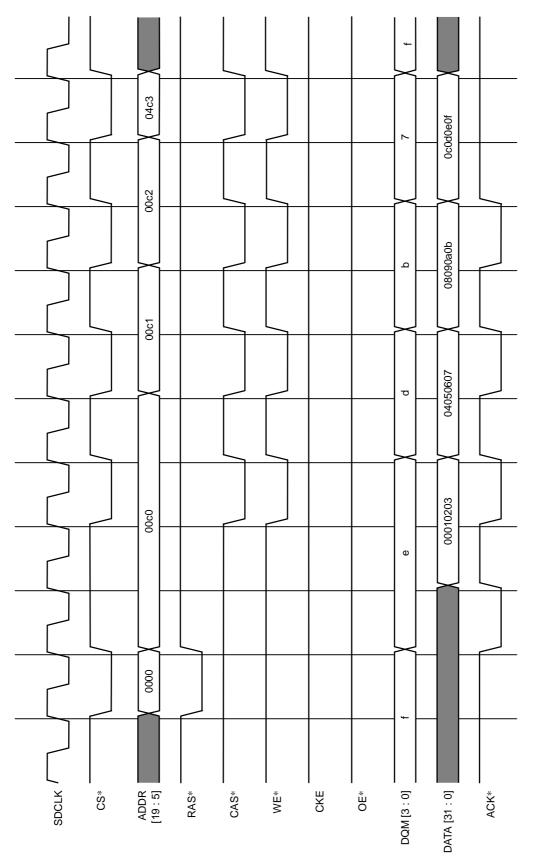

|    | 8.6.15                                                                                                                                                           | SGRAM in 32-bit Bus Mode                                                                                                                                                                                                                                                                                                                                                                                                  | 8-46                                                            |

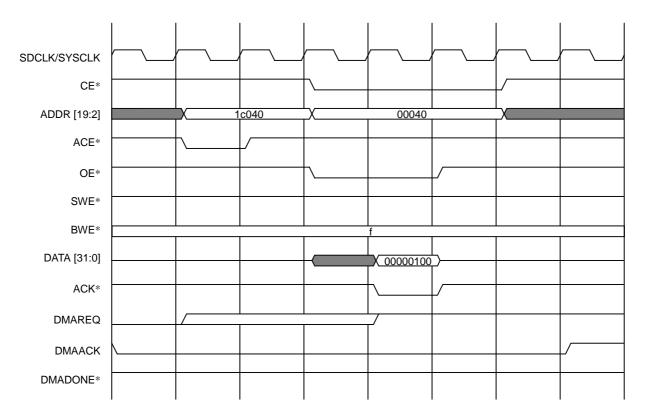

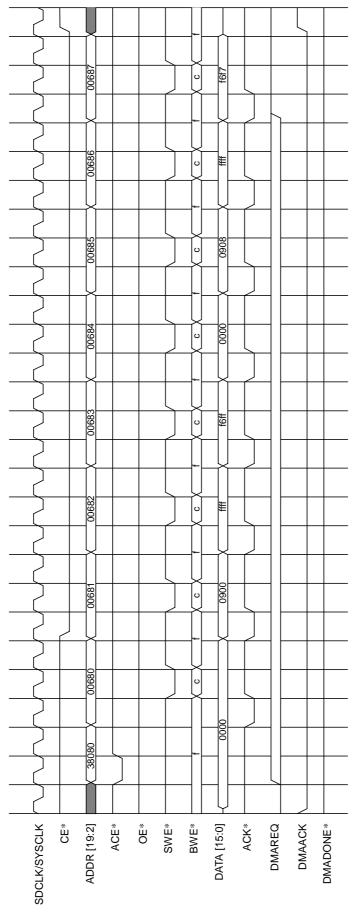

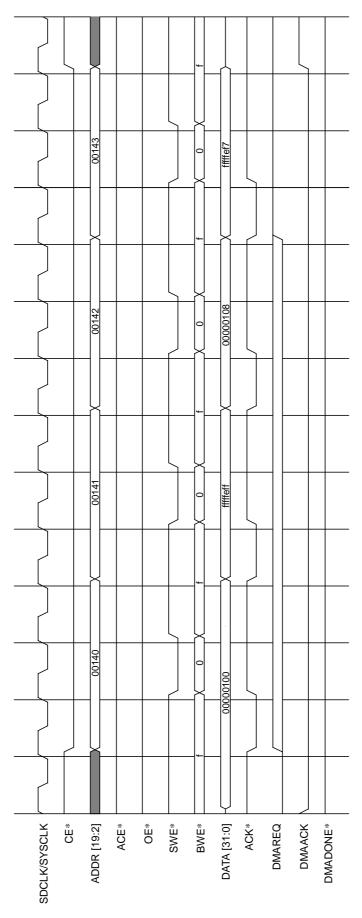

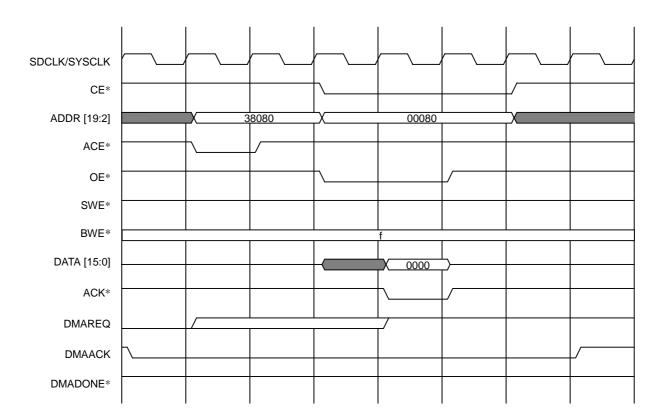

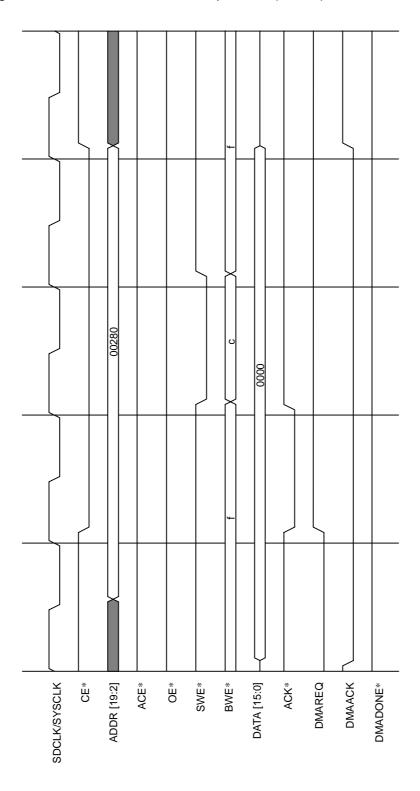

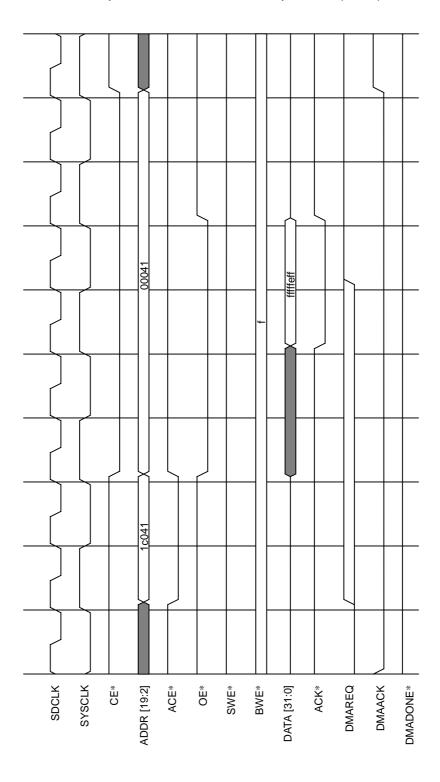

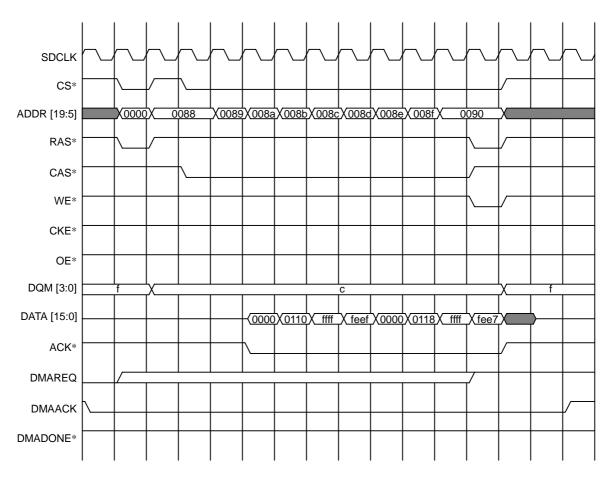

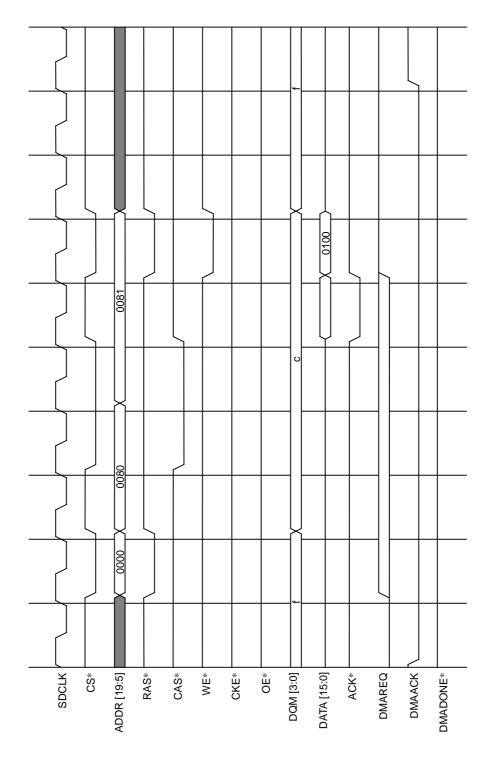

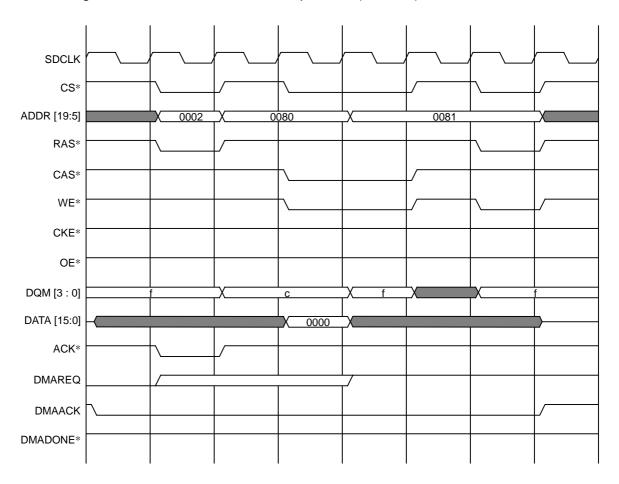

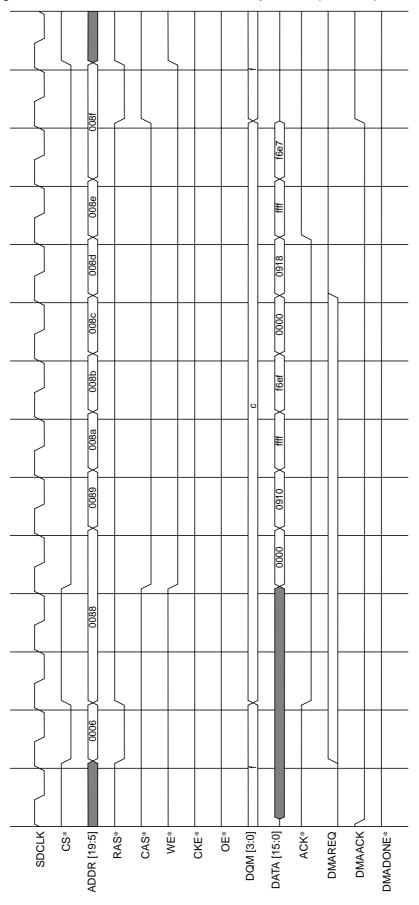

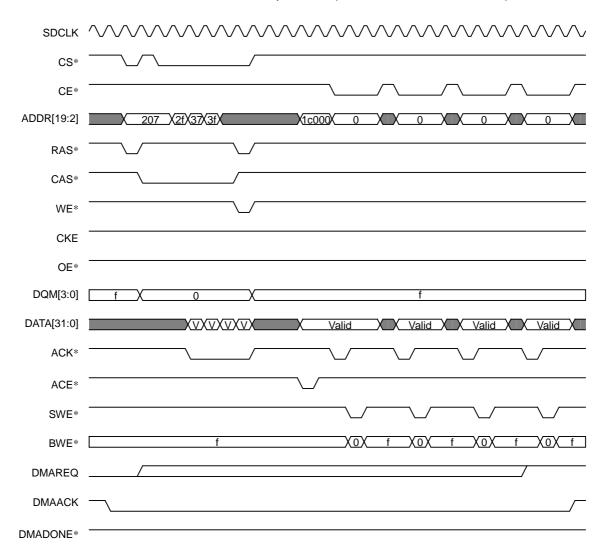

|    | 8.6.16                                                                                                                                                           | External DMA Operation (Big Endian)                                                                                                                                                                                                                                                                                                                                                                                       | 8-49                                                            |

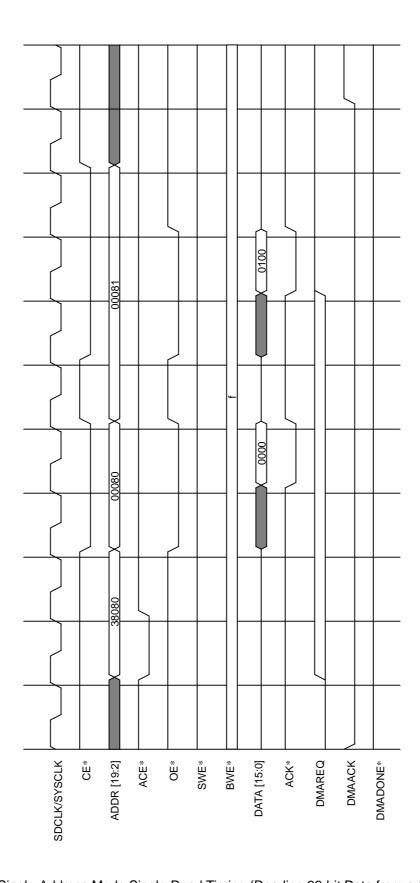

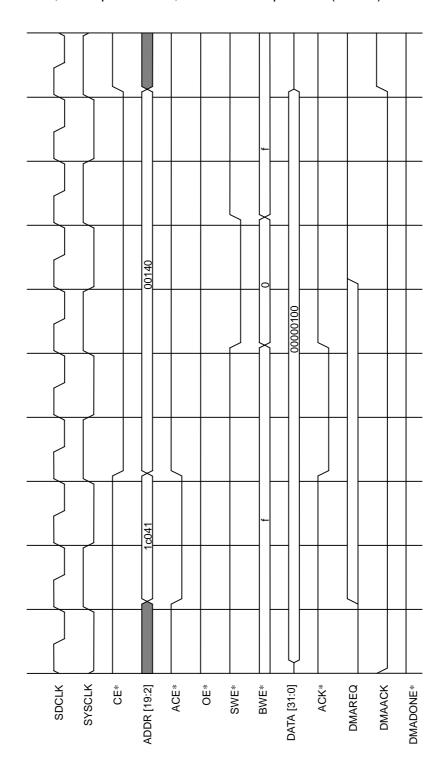

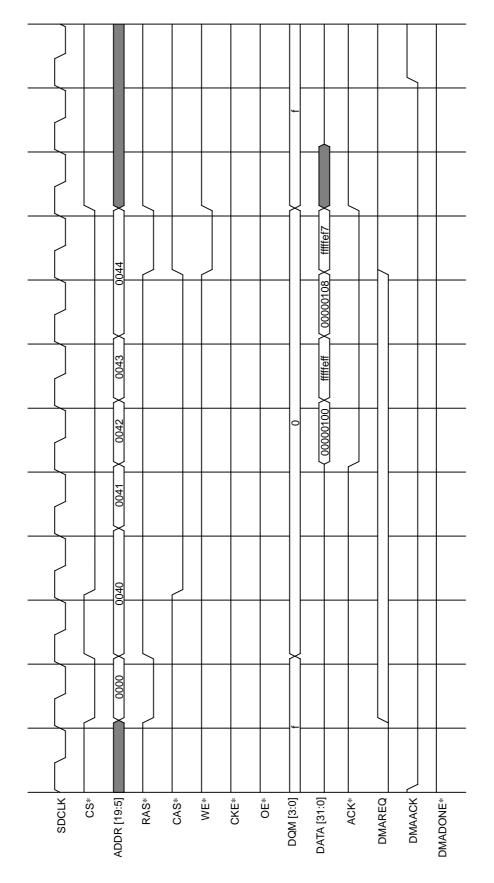

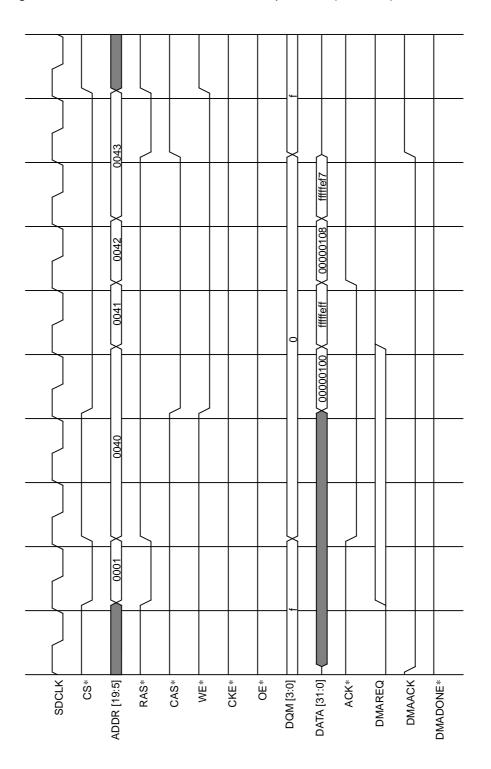

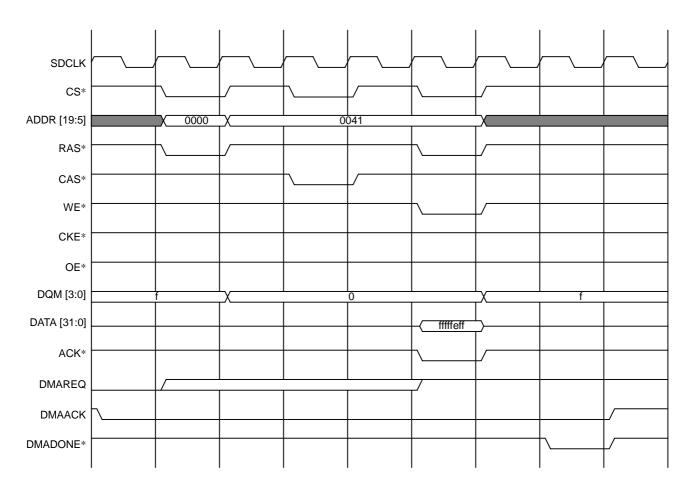

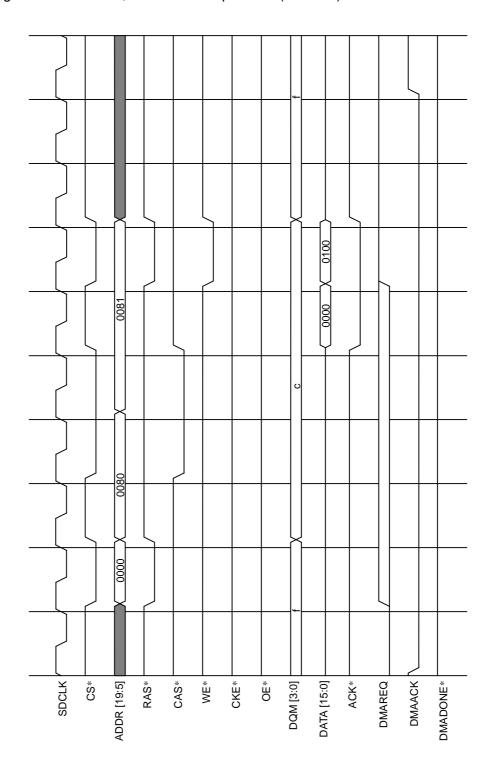

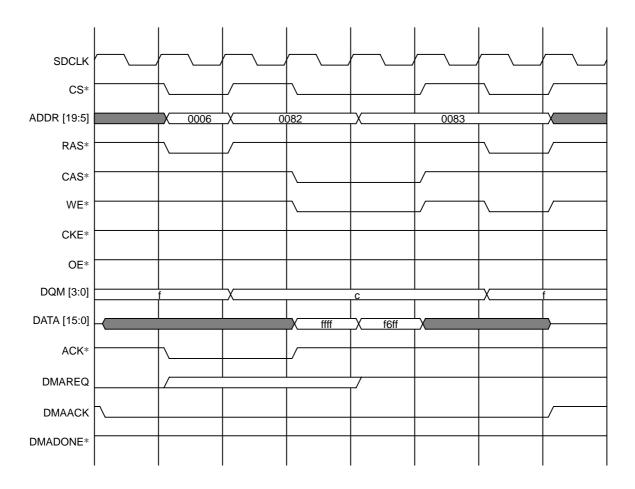

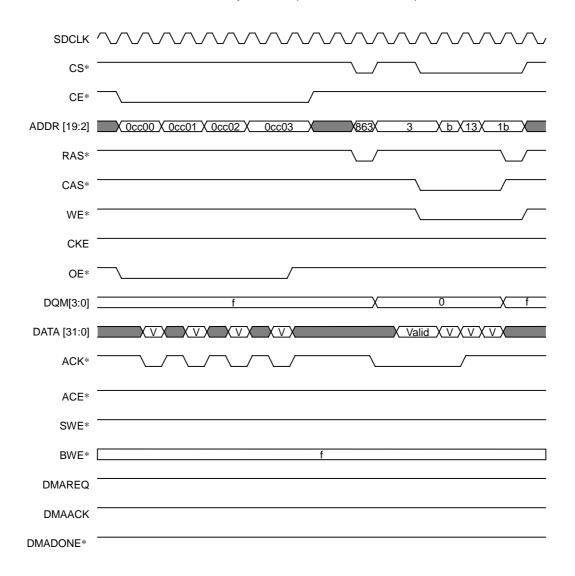

|    | 8.6.17                                                                                                                                                           | External DMA Operation (Little Endian)                                                                                                                                                                                                                                                                                                                                                                                    | 8-51                                                            |

|    | 8.7 Exa                                                                                                                                                          | mples of Using SDRAM                                                                                                                                                                                                                                                                                                                                                                                                      | 8-53                                                            |

|    |                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                 |

| `  | Г ( 11                                                                                                                                                           | 0 0 11                                                                                                                                                                                                                                                                                                                                                                                                                    | 0.1                                                             |

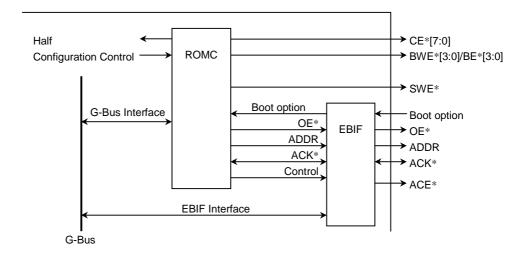

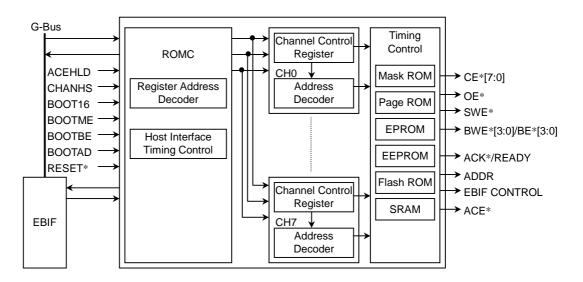

| 9. | External l                                                                                                                                                       | Bus Controller                                                                                                                                                                                                                                                                                                                                                                                                            | 9-1                                                             |

| 9. |                                                                                                                                                                  | Bus Controllerures                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                 |

| 9. | 9.1 Feat                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                           | 9-1                                                             |

| 9. | 9.1 Feat<br>9.2 Bloo                                                                                                                                             | uresk Diagram                                                                                                                                                                                                                                                                                                                                                                                                             | 9-1<br>9-2                                                      |

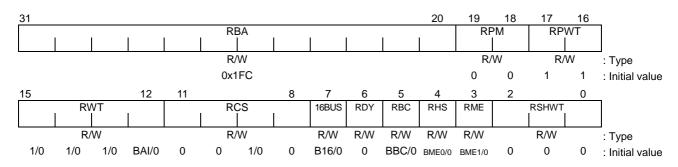

| 9. | 9.1 Feat<br>9.2 Bloo                                                                                                                                             | uresk Diagramisters                                                                                                                                                                                                                                                                                                                                                                                                       | 9-1<br>9-2<br>9-3                                               |

| 9. | <ul><li>9.1 Feat</li><li>9.2 Bloc</li><li>9.3 Reg</li></ul>                                                                                                      | ures                                                                                                                                                                                                                                                                                                                                                                                                                      | 9-1<br>9-2<br>9-3                                               |

| 9. | 9.1 Feat<br>9.2 Bloo<br>9.3 Reg<br>9.3.1                                                                                                                         | rures                                                                                                                                                                                                                                                                                                                                                                                                                     | 9-1<br>9-2<br>9-3                                               |

| 9. | 9.1 Feat<br>9.2 Bloo<br>9.3 Reg<br>9.3.1                                                                                                                         | Register Map                                                                                                                                                                                                                                                                                                                                                                                                              | 9-1<br>9-2<br>9-3<br>9-3                                        |

| 9. | 9.1 Feat<br>9.2 Blood<br>9.3 Reg<br>9.3.1<br>9.3.2                                                                                                               | rures                                                                                                                                                                                                                                                                                                                                                                                                                     | 9-1<br>9-2<br>9-3<br>9-3                                        |

| 9. | 9.1 Feat<br>9.2 Blood<br>9.3 Reg<br>9.3.1<br>9.3.2                                                                                                               | rures                                                                                                                                                                                                                                                                                                                                                                                                                     | 9-1<br>9-2<br>9-3<br>9-3                                        |

| 9. | 9.1 Feat<br>9.2 Blood<br>9.3 Reg<br>9.3.1<br>9.3.2<br>9.4 Ope<br>9.4.1                                                                                           | rures                                                                                                                                                                                                                                                                                                                                                                                                                     | 9-1<br>9-2<br>9-3<br>9-3<br>9-4<br>9-6<br>9-6                   |

| 9. | 9.1 Feat<br>9.2 Blood<br>9.3 Reg<br>9.3.1<br>9.3.2<br>9.4 Ope<br>9.4.1<br>9.4.2                                                                                  | rures                                                                                                                                                                                                                                                                                                                                                                                                                     | 9-1<br>9-2<br>9-3<br>9-3<br>9-6<br>9-6<br>9-7                   |

| 9. | 9.1 Feat<br>9.2 Blood<br>9.3 Reg<br>9.3.1<br>9.3.2<br>9.4 Ope<br>9.4.1<br>9.4.2<br>9.4.3                                                                         | rures                                                                                                                                                                                                                                                                                                                                                                                                                     | 9-1<br>9-2<br>9-3<br>9-3<br>9-6<br>9-6<br>9-7                   |

| 9. | 9.1 Feat<br>9.2 Blood<br>9.3 Reg<br>9.3.1<br>9.3.2<br>9.4 Ope<br>9.4.1<br>9.4.2<br>9.4.3<br>9.4.4                                                                | rures.  ck Diagram  isters  Register Map  ROM Channel Control Registers (RCCR0-RCCR7) 0xFFFE_9000 (ch.0) 0xFFFE_9004 (ch.1) 0xFFFE_9008 (ch.2) 0xFFFE_900C (ch.3) 0xFFFE_9010 (ch.4) 0xFFFE_9014 (ch.5) 0xFFFE_9018 (ch.6) 0xFFFE_901C (ch.7)  ration  Bootup Options  Global Options  ROM Channel Control Registers  Clock Options                                                                                       | 9-1<br>9-2<br>9-3<br>9-3<br>9-4<br>9-6<br>9-6<br>9-7<br>9-7     |

| 9. | 9.1 Feat 9.2 Bloc 9.3 Reg 9.3.1 9.3.2  9.4 Ope 9.4.1 9.4.2 9.4.3 9.4.4 9.4.5                                                                                     | rures                                                                                                                                                                                                                                                                                                                                                                                                                     | 9-19-29-39-49-69-69-79-79-8                                     |

| 9. | 9.1 Feat<br>9.2 Blood<br>9.3 Reg<br>9.3.1<br>9.3.2<br>9.4 Ope<br>9.4.1<br>9.4.2<br>9.4.3<br>9.4.4<br>9.4.5<br>9.4.6                                              | rures                                                                                                                                                                                                                                                                                                                                                                                                                     | 9-19-29-39-49-69-69-79-79-8                                     |

| 9. | 9.1 Feat 9.2 Bloc 9.3 Reg 9.3.1 9.3.2  9.4 Ope 9.4.1 9.4.2 9.4.3 9.4.4 9.4.5 9.4.6 9.4.7                                                                         | Register Map. ROM Channel Control Registers (RCCR0-RCCR7) 0xFFFE_9000 (ch.0) 0xFFFE_9004 (ch.1) 0xFFFE_9008 (ch.2) 0xFFFE_900C (ch.3) 0xFFFE_9010 (ch.4) 0xFFFE_9014 (ch.5) 0xFFFE_9018 (ch.6) 0xFFFE_901C (ch.7).  ration  Bootup Options Global Options ROM Channel Control Registers Clock Options ROM Channel Control Registers Clock Options Base Address and Channel Size Operating Modes 16-Bit Data Bus Operation | 9-19-29-39-49-69-69-79-79-89-89-10                              |

| 9. | 9.1 Feat<br>9.2 Blood<br>9.3 Reg<br>9.3.1<br>9.3.2<br>9.4 Ope<br>9.4.1<br>9.4.2<br>9.4.3<br>9.4.4<br>9.4.5<br>9.4.6<br>9.4.7<br>9.4.8                            | ures                                                                                                                                                                                                                                                                                                                                                                                                                      | 9-19-29-39-49-69-79-79-89-89-10                                 |

| 9. | 9.1 Feat 9.2 Bloc 9.3 Reg 9.3.1 9.3.2  9.4 Ope 9.4.1 9.4.2 9.4.3 9.4.4 9.4.5 9.4.6 9.4.7 9.4.8 9.4.9                                                             | ures                                                                                                                                                                                                                                                                                                                                                                                                                      | 9-19-29-39-49-69-79-79-89-109-11                                |

| 9. | 9.1 Feat 9.2 Bloc 9.3 Reg 9.3.1 9.3.2  9.4 Ope 9.4.1 9.4.2 9.4.3 9.4.4 9.4.5 9.4.6 9.4.7 9.4.8 9.4.9 9.4.10                                                      | ures                                                                                                                                                                                                                                                                                                                                                                                                                      | 9-19-29-39-49-69-69-79-79-19-109-119-12                         |

| 9. | 9.1 Feat 9.2 Bloo 9.3 Reg 9.3.1 9.3.2  9.4 Ope 9.4.1 9.4.2 9.4.3 9.4.4 9.4.5 9.4.6 9.4.7 9.4.8 9.4.9 9.4.10 9.4.11                                               | ures                                                                                                                                                                                                                                                                                                                                                                                                                      | 9-19-29-39-49-69-69-79-79-89-109-109-119-12                     |

| 9. | 9.1 Feat 9.2 Bloc 9.3 Reg 9.3.1 9.3.2  9.4 Ope 9.4.1 9.4.2 9.4.3 9.4.4 9.4.5 9.4.6 9.4.7 9.4.8 9.4.9 9.4.10 9.4.11 9.4.12                                        | ures                                                                                                                                                                                                                                                                                                                                                                                                                      | 9-19-29-39-49-69-69-79-79-89-109-119-129-13                     |

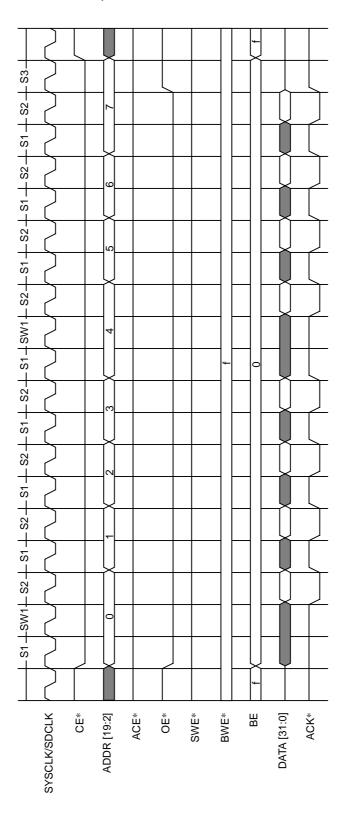

| 9. | 9.1 Feat 9.2 Bloc 9.3 Reg 9.3.1 9.3.2  9.4 Ope 9.4.1 9.4.2 9.4.3 9.4.4 9.4.5 9.4.6 9.4.7 9.4.8 9.4.9 9.4.10 9.4.11 9.4.12  9.5 Tim                               | ures                                                                                                                                                                                                                                                                                                                                                                                                                      | 9-19-29-39-49-69-79-79-89-109-119-129-139-14                    |

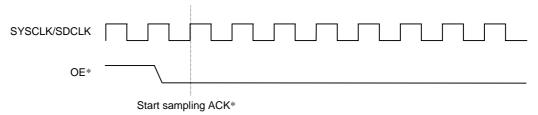

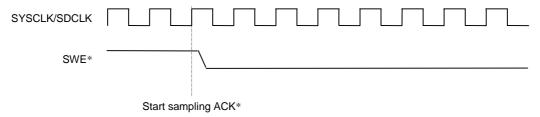

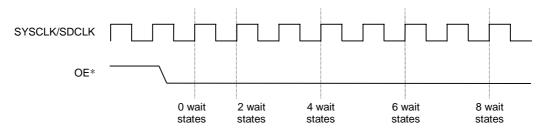

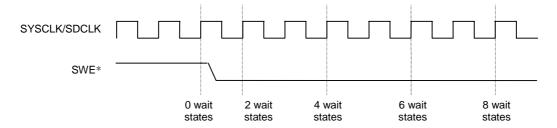

| 9. | 9.1 Feat 9.2 Bloc 9.3 Reg 9.3.1 9.3.2  9.4 Ope 9.4.1 9.4.2 9.4.3 9.4.4 9.4.5 9.4.6 9.4.7 9.4.8 9.4.9 9.4.10 9.4.11 9.4.12  9.5 Tim 9.5.1                         | ures                                                                                                                                                                                                                                                                                                                                                                                                                      | 9-19-29-39-49-69-79-79-89-109-119-129-139-139-14                |

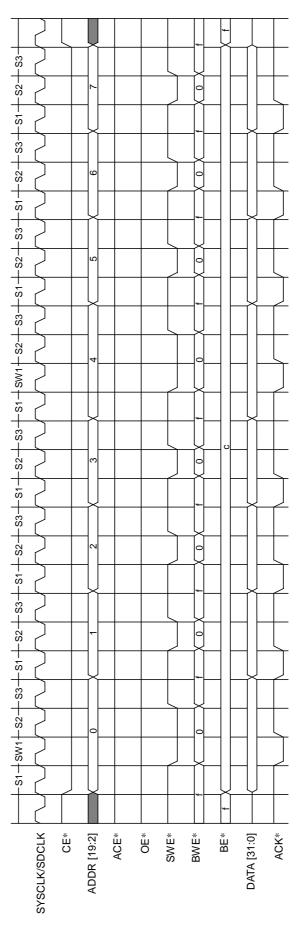

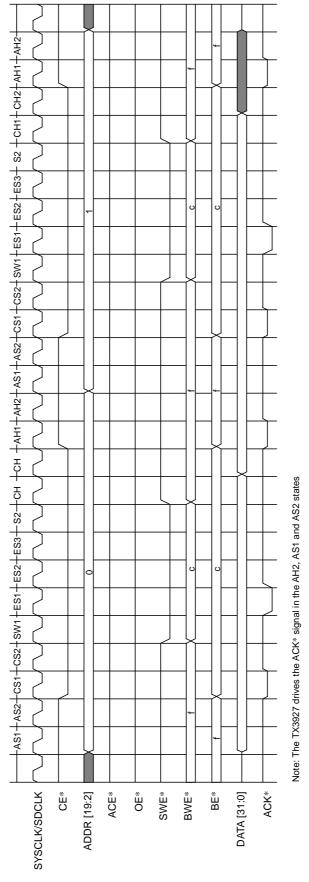

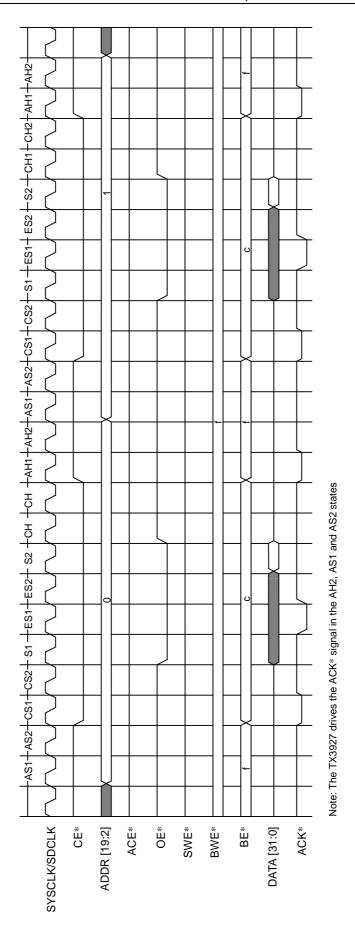

| 9. | 9.1 Feat 9.2 Bloo 9.3 Reg 9.3.1 9.3.2  9.4 Ope 9.4.1 9.4.2 9.4.3 9.4.4 9.4.5 9.4.6 9.4.7 9.4.8 9.4.9 9.4.10 9.4.11 9.4.12  9.5 Tim 9.5.1 9.5.2                   | ures                                                                                                                                                                                                                                                                                                                                                                                                                      | 9-19-29-39-49-69-69-79-79-89-109-119-129-139-139-159-16         |

| 9. | 9.1 Feat 9.2 Bloo 9.3 Reg 9.3.1 9.3.2  9.4 Ope 9.4.1 9.4.2 9.4.3 9.4.4 9.4.5 9.4.6 9.4.7 9.4.8 9.4.9 9.4.10 9.4.11 9.4.12  9.5 Tim 9.5.1 9.5.2 9.5.3             | ures                                                                                                                                                                                                                                                                                                                                                                                                                      | 9-19-29-39-49-69-69-79-79-89-109-109-119-129-139-159-169-17     |

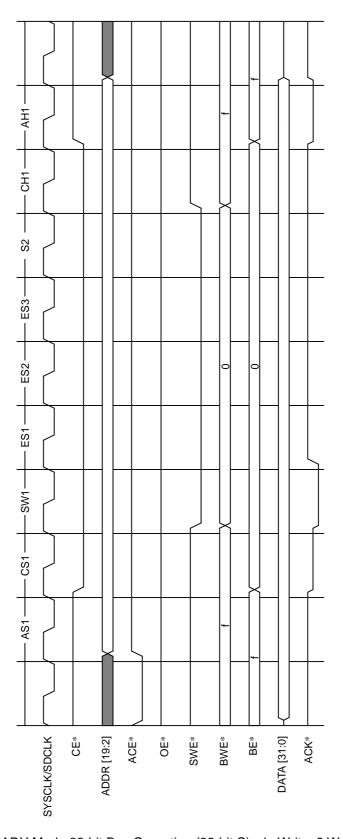

| 9. | 9.1 Feat 9.2 Bloo 9.3 Reg 9.3.1 9.3.2  9.4 Ope 9.4.1 9.4.2 9.4.3 9.4.4 9.4.5 9.4.6 9.4.7 9.4.8 9.4.9 9.4.10 9.4.11 9.4.12  9.5 Tim 9.5.1 9.5.2 9.5.3 9.5.4       | ures                                                                                                                                                                                                                                                                                                                                                                                                                      | 9-19-29-39-49-69-69-79-79-89-109-119-129-139-139-159-169-17     |

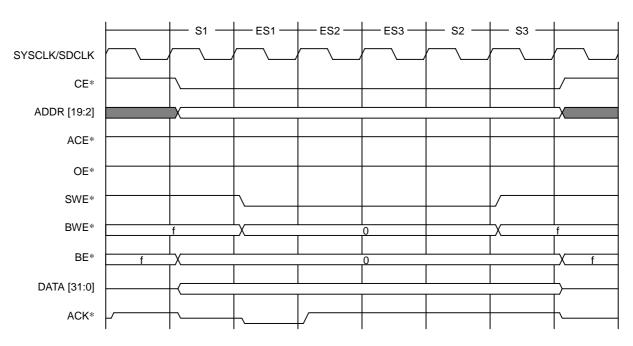

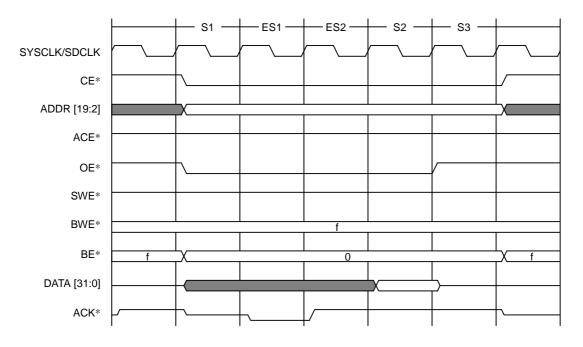

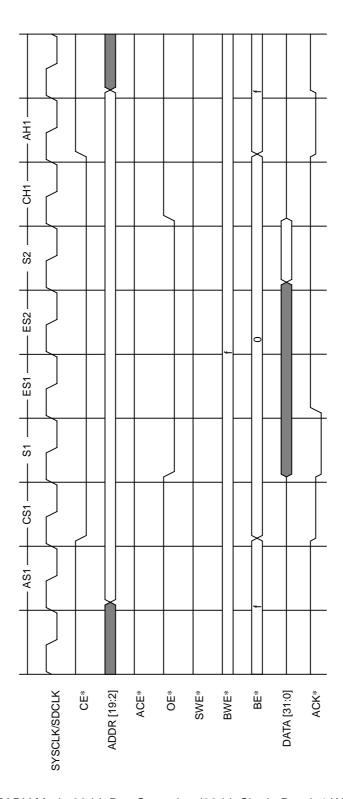

| 9. | 9.1 Feat 9.2 Bloc 9.3 Reg 9.3.1 9.3.2  9.4 Ope 9.4.1 9.4.2 9.4.3 9.4.4 9.4.5 9.4.6 9.4.7 9.4.8 9.4.9 9.4.10 9.4.11 9.4.12  9.5 Tim 9.5.1 9.5.2 9.5.3 9.5.4 9.5.5 | ures                                                                                                                                                                                                                                                                                                                                                                                                                      | 9-19-29-39-49-69-69-79-79-89-109-119-129-139-139-159-169-209-24 |

| 9. | 9.1 Feat 9.2 Bloo 9.3 Reg 9.3.1 9.3.2  9.4 Ope 9.4.1 9.4.2 9.4.3 9.4.4 9.4.5 9.4.6 9.4.7 9.4.8 9.4.9 9.4.10 9.4.11 9.4.12  9.5 Tim 9.5.1 9.5.2 9.5.3 9.5.4       | ures                                                                                                                                                                                                                                                                                                                                                                                                                      | 9-19-29-39-39-69-69-79-79-89-109-119-129-139-139-159-169-209-24 |

| 9.5.8<br>9.5.9 | ı                                                                                                                              |       |

|----------------|--------------------------------------------------------------------------------------------------------------------------------|-------|

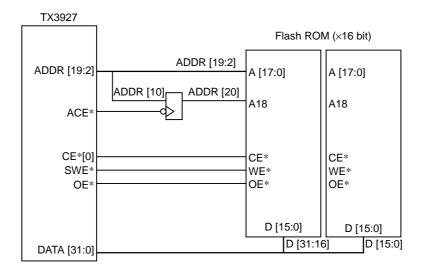

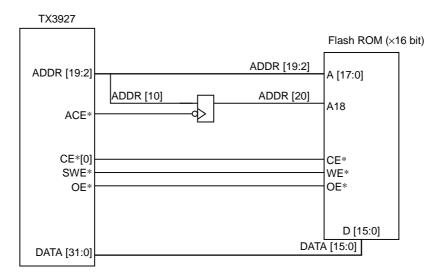

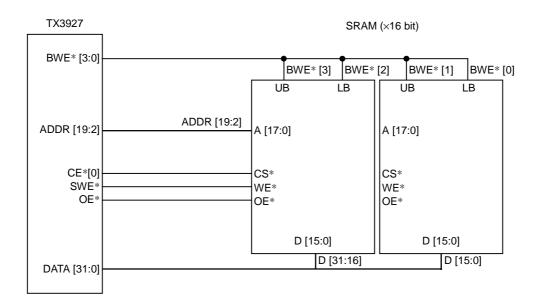

|                | Examples of Using Flash ROM and SRAM                                                                                           |       |

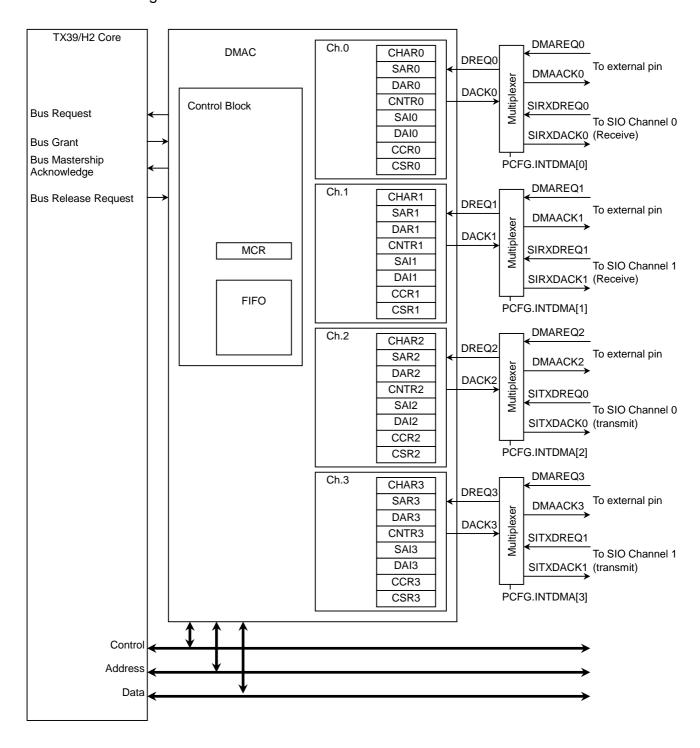

|                | Controller                                                                                                                     |       |

|                | Features                                                                                                                       |       |

|                | Block Diagram                                                                                                                  |       |

|                | Registers                                                                                                                      |       |

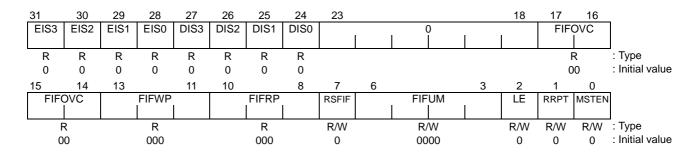

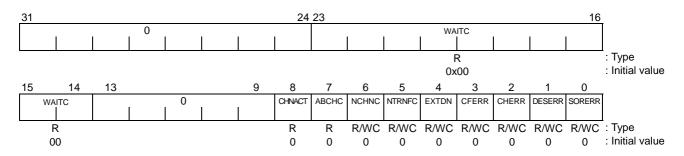

| 10.3 F         |                                                                                                                                |       |

| 10.3.          |                                                                                                                                |       |

| 10.3.          |                                                                                                                                |       |

| 10.3.          |                                                                                                                                |       |

| 10.3.          |                                                                                                                                | 10-9  |

| 10.5.          | 0xFFFE_B044 (ch. 2), 0xFFFE_B064 (ch. 3)                                                                                       | 10-11 |

| 10.3.          |                                                                                                                                |       |

|                | 0xFFFE_B048 (ch. 2), 0xFFFE_B068 (ch. 3)                                                                                       | 10-12 |

| 10.3.          | = ( - )                                                                                                                        |       |

| 40.0           | 0xFFFE_B040 (ch. 2), 0xFFFE_B060 (ch. 3)                                                                                       | 10-13 |

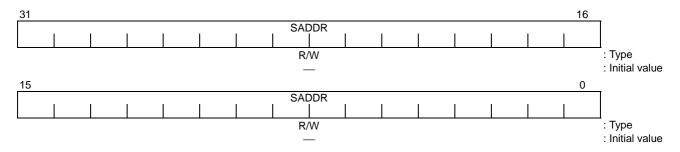

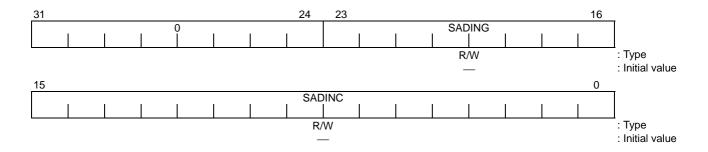

| 10.3.          | 8 Source Address Increment Registers (SAIn) 0xFFFE_B010 (ch. 0), 0xFFFE_B030 (ch. 1), 0xFFFE_B050 (ch. 2), 0xFFFE_B070 (ch. 3) | 10 14 |

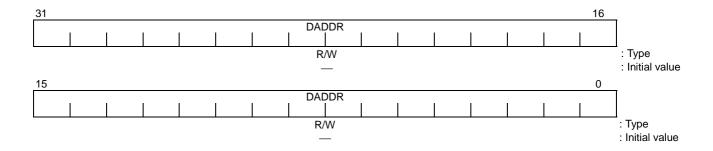

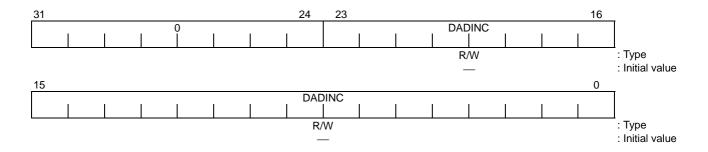

| 10.3.          | 9 Destination Address Increment Registers (DAIn) 0xFFFE_B014 (ch. 0), 0xFFFE_B034 (ch. 1)                                      | ,     |

| 10.3.          | 0xFFFE_B054 (ch. 2), 0xFFFE_B074 (ch. 3)                                                                                       | 10-15 |

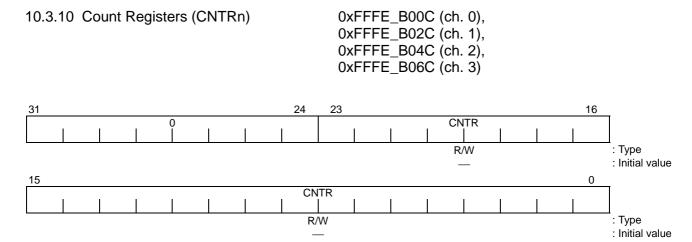

|                | 0xFFFE_B04C (ch. 2), 0xFFFE_B06C (ch. 3)                                                                                       | 10-16 |

| 10.4           | Operation                                                                                                                      |       |

| 10.4.          |                                                                                                                                |       |

| 10.4.          | 8 - 1                                                                                                                          |       |

| 10.4.          | e                                                                                                                              |       |

| 10.4.<br>10.4. | · · · · · · · · · · · · · · · · · · ·                                                                                          |       |

| 10.4.          |                                                                                                                                |       |

| 10.4.          |                                                                                                                                |       |

| 10.4.          |                                                                                                                                |       |

| 10.4.          |                                                                                                                                |       |

| 10.4.          | 10 Notes on Using the DMAC FIFO                                                                                                | 10-24 |

| 10.5           | Fiming Diagrams                                                                                                                | 10-26 |

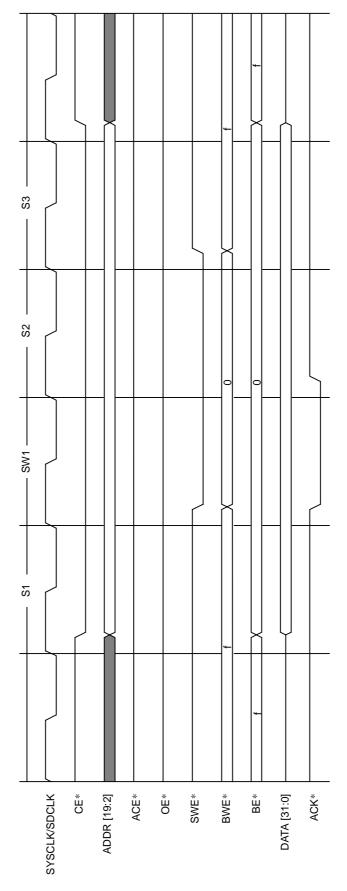

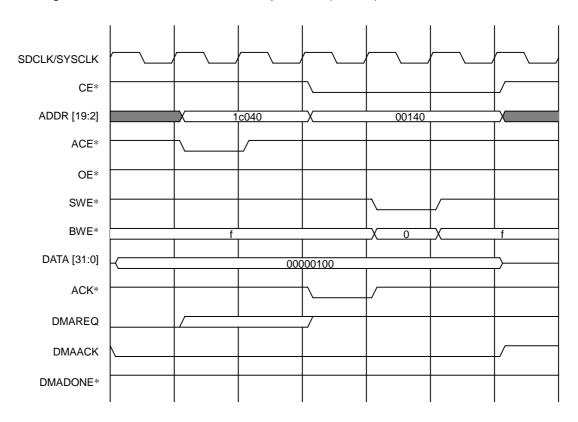

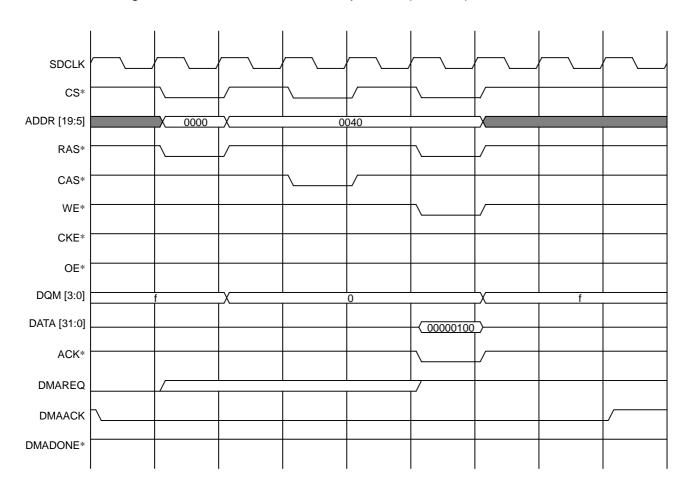

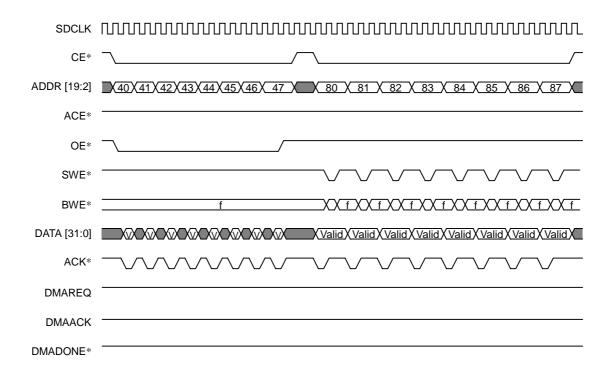

| 10.5.          | 1 Single-Address Mode, 32-bit Read Operation (ROM)                                                                             | 10-26 |

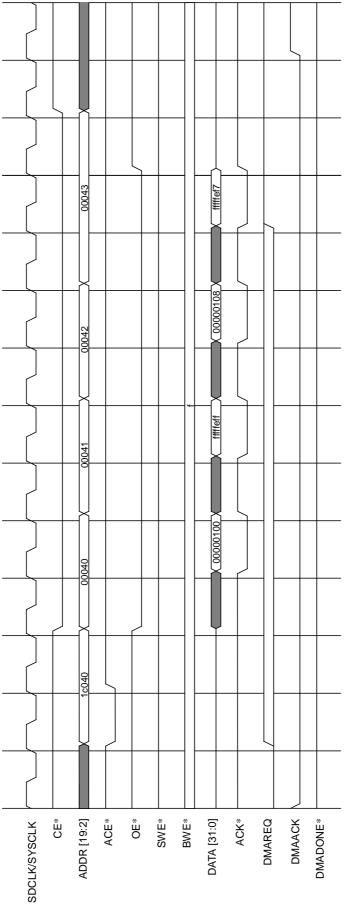

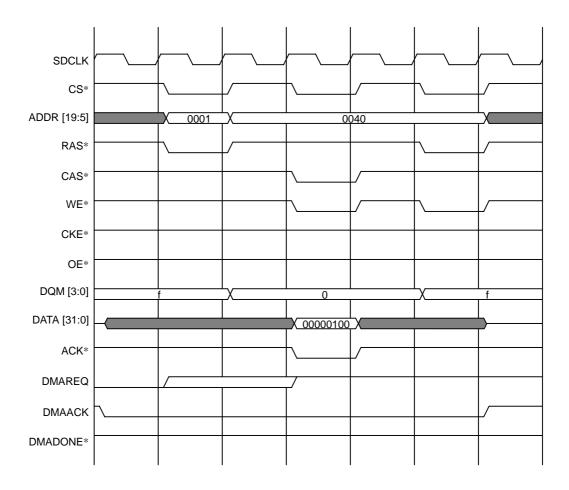

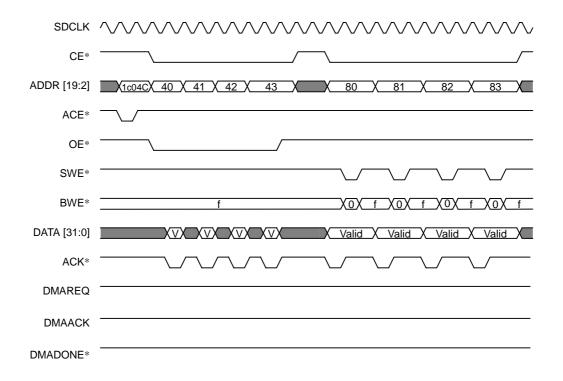

| 10.5.          | - B                                                                                                                            |       |

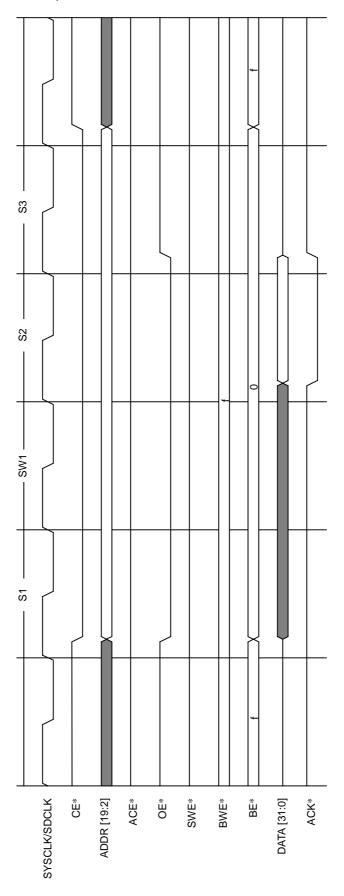

| 10.5.          |                                                                                                                                |       |

| 10.5.          |                                                                                                                                |       |

| 10.5.          |                                                                                                                                |       |

| 10.5.          |                                                                                                                                |       |

| 10.5.<br>10.5. |                                                                                                                                |       |

| 10.5.          |                                                                                                                                |       |

| 10.5.          |                                                                                                                                |       |

| 10.5.          |                                                                                                                                |       |

| 10.5.          |                                                                                                                                |       |

| 10.5.          | 13 Single-Address Mode, 32-bit Burst-Write Operation (SDRAM)                                                                   | 10-40 |

| 10.5.          |                                                                                                                                |       |

| 10.5.          | 1                                                                                                                              |       |

| 10.5.          | 1 ,                                                                                                                            |       |

| 10.5.          | 1                                                                                                                              |       |

| 10.5.          | · · · · · · · · · · · · · · · · · · ·                                                                                          |       |

| 10.5.<br>10.5. | 1 ,                                                                                                                            |       |

|                | 21 Dual-Address Mode Burst Operation (SRAM to SRAM)                                                                            |       |

| 10.5.          | 21 Dan Haress more bust operation (steam to bbit in)                                                                           | +0    |

|              | Dual-Address Mode Burst Operation (SDRAM to SRAM)            |       |

|--------------|--------------------------------------------------------------|-------|

| 10.5.23      | Dual-Address Mode Burst Operation (SDRAM to SDRAM)           | 10-50 |

| 10.5.24      | Dual-Address Mode Non-burst Operation (SDRAM to ROMC Device) | 10-51 |

| 10.5.25      | Dual-Address Mode Non-burst Operation (ROMC Device to SDRAM) | 10-52 |

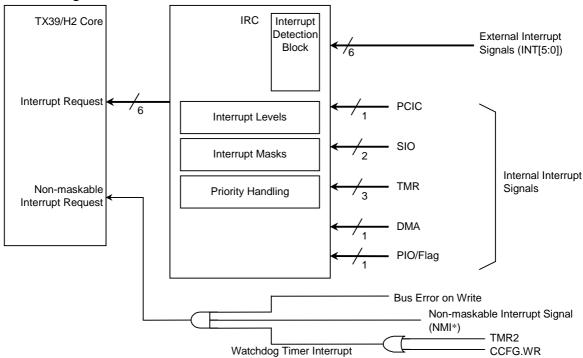

| 11 Interrupt | Controller (IRC)                                             | 11_1  |

| •            | ures                                                         |       |

|              |                                                              |       |

|              | k Diagram                                                    |       |

| _            | isters                                                       |       |

| 11.3.1       | Register Map                                                 |       |

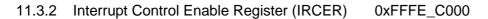

| 11.3.2       | Interrupt Control Enable Register (IRCER) 0xFFFE_C000        |       |

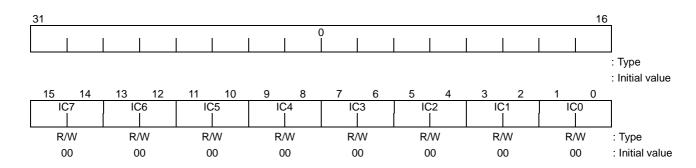

| 11.3.3       | Interrupt Control Mode Register 0 (IRCR0) 0xFFFE_C004        |       |

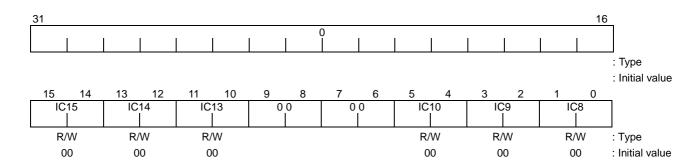

| 11.3.4       | Interrupt Control Mode Register 1 (IRCR1) 0xFFFE_C008        |       |

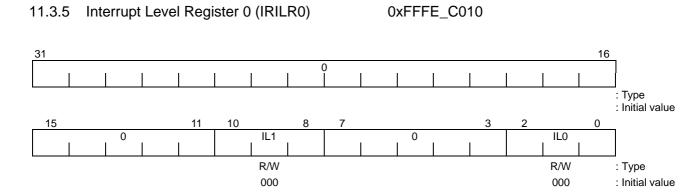

| 11.3.5       | Interrupt Level Register 0 (IRILR0) 0xFFFE_C010              |       |

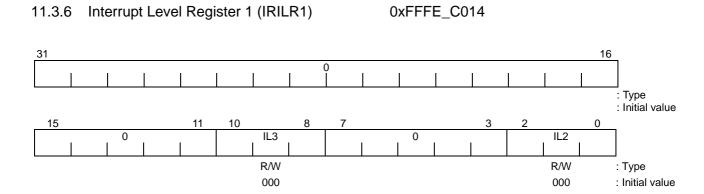

| 11.3.6       | Interrupt Level Register 1 (IRILR1) 0xFFFE_C014              |       |

| 11.3.7       | Interrupt Level Register 2 (IRILR2) 0xFFFE_C018              |       |

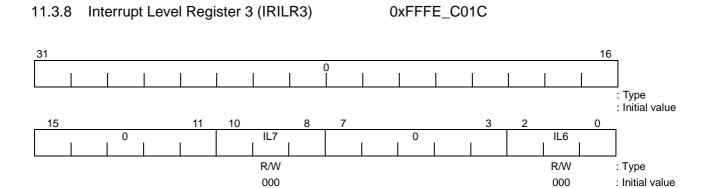

| 11.3.8       | Interrupt Level Register 3 (IRILR3) 0xFFFE_C01C              |       |

| 11.3.9       | Interrupt Level Register 4 (IRILR4) 0xFFFE_C020              |       |

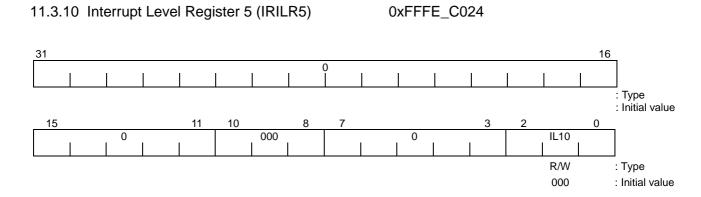

| 11.3.10      | Interrupt Level Register 5 (IRILR5) 0xFFFE_C024              | 11-12 |

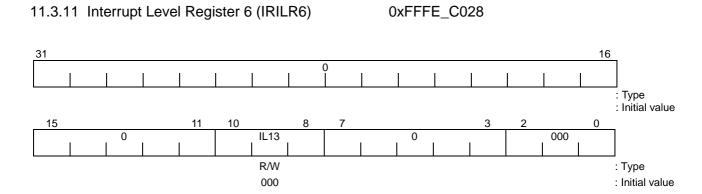

| 11.3.11      | Interrupt Level Register 6 (IRILR6) 0xFFFE_C028              |       |

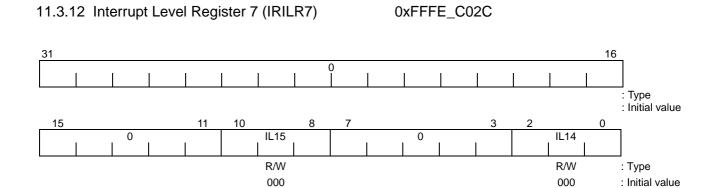

| 11.3.12      | Interrupt Level Register 7 (IRILR7) 0xFFFE_C02C              |       |

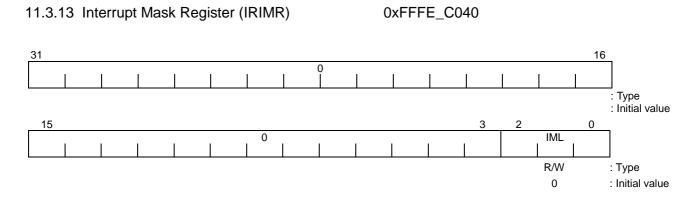

| 11.3.13      | Interrupt Mask Register (IRIMR) 0xFFFE_C040                  | 11-15 |

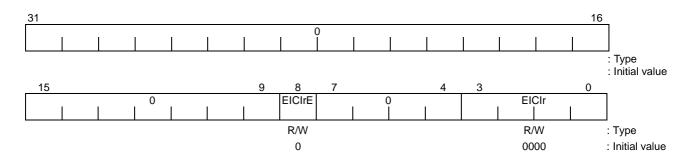

| 11.3.14      | Interrupt Status/Control Register (IRSCR) 0xFFFE_C060        | 11-16 |

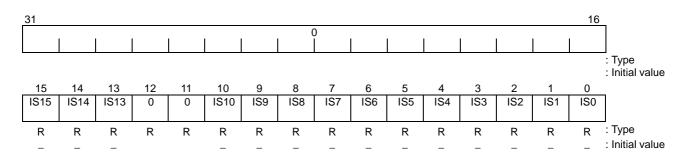

| 11.3.15      | Interrupt Source Status Register (IRSSR) 0xFFFE_C080         | 11-17 |

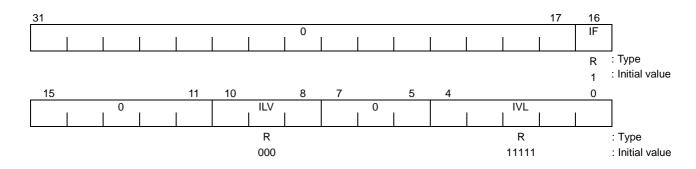

| 11.3.16      | Interrupt Current Status Register (IRCSR) 0xFFFE_C0A0        | 11-19 |

|              | ration                                                       |       |

| 11.4.1       | Interrupt Sources                                            |       |

| 11.4.2       | Interrupt Detection                                          |       |

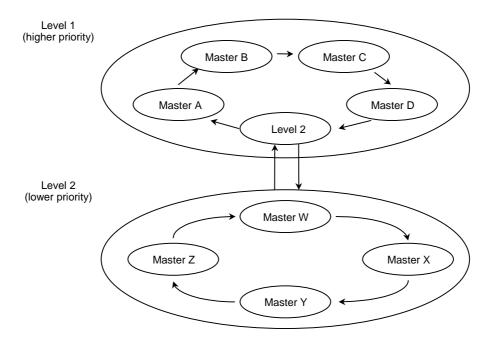

| 11.4.3       | Interrupt Priorities                                         |       |

|              | •                                                            |       |

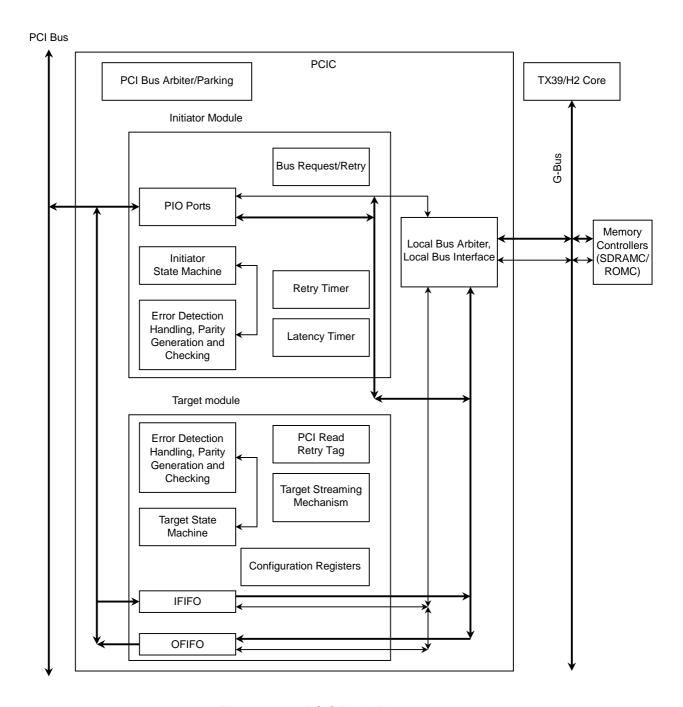

|              | roller (PCIC)                                                |       |

| 12.1 Feat    | ures                                                         | 12-1  |

| 12.1.1       | PCI Interface Features.                                      | 12-1  |

| 12.1.2       | PCI Initiator Features                                       | 12-2  |

| 12.1.3       | PCI Target Features                                          | 12-2  |

| 12.1.4       | PCI Arbiter and Bus Parking Features                         | 12-2  |

| 12.2 Bloc    | sk Diagram                                                   | 12-3  |

| 12.3 Reg     | isters                                                       | 12-4  |

| 12.3.1       | Register Map.                                                |       |

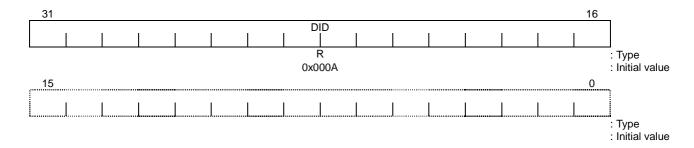

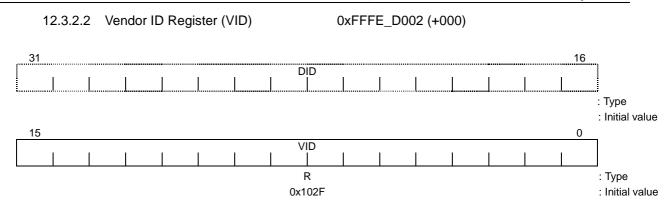

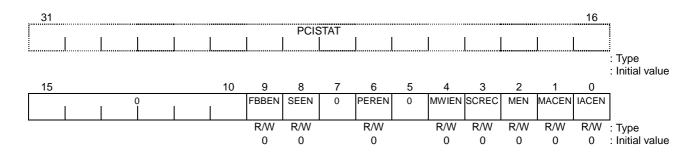

| 12.3.2       | PCI Configuration Header Space Registers                     |       |

| 12.3.3       | Initiator Configuration Space Registers                      |       |

| 12.3.4       | Target Configuration Space registers                         |       |

| 12.3.5       | PCI Bus Arbiter/Parked Master Registers                      |       |

| 12.3.6       | Local Bus Special Registers                                  |       |

|              |                                                              |       |

| -            | ration                                                       |       |

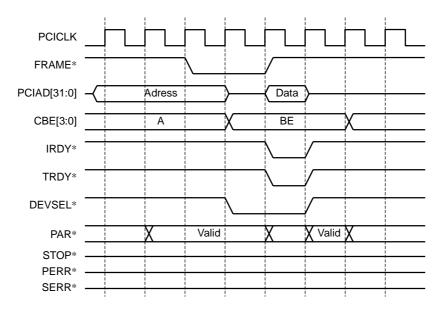

| 12.4.1       | Transfer Modes                                               |       |

| 12.4.2       | Configuration Cycles                                         |       |

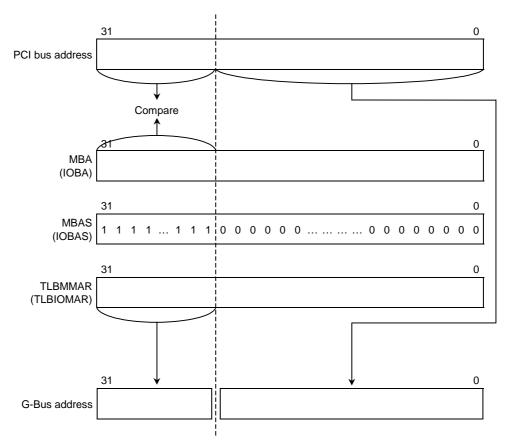

| 12.4.3       | Address Translation                                          |       |

| 12.4.4       | PCIC Clock                                                   |       |

| 12.4.5       | PCI Bus Arbitration                                          |       |

| 12.4.6       | FIFO Depth                                                   |       |

| 12.4.7       | Accessing the PCIC Target Module                             |       |

| 12.4.8       | PCIC Register Access                                         |       |

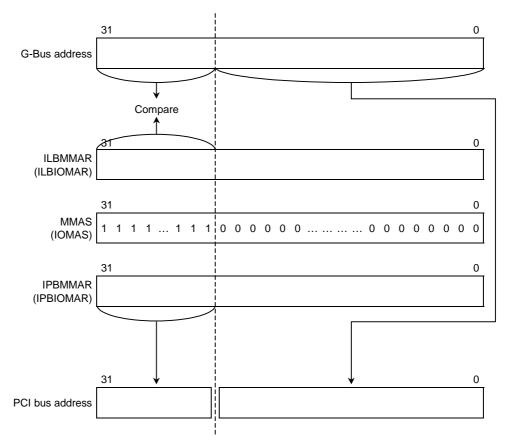

| 12.4.9       | Address Mapping Between the Local Bus and PCI Bus            |       |

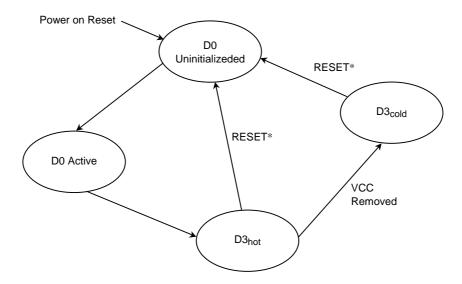

| 12.4.10      | ACPI Power Management                                        |       |

| 12.4.11      | Byte Swapping                                                |       |

| 12.4.12      | Disabling Access to a Part of the PCI Configuration Space    | 12-89 |

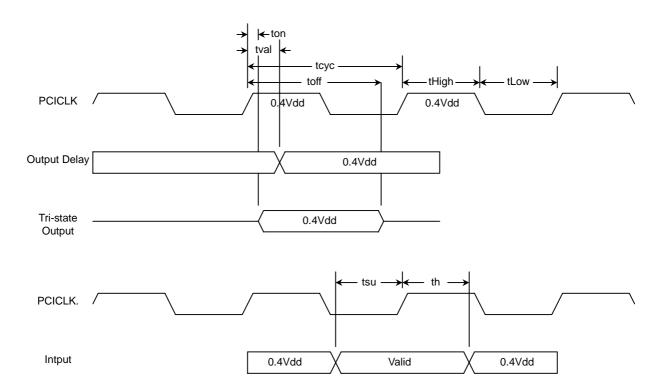

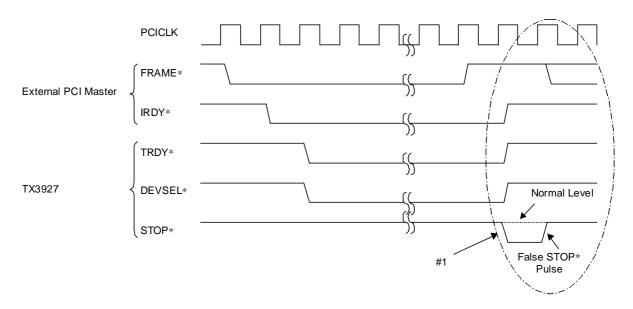

| 12.5 Tim     | ing Diagrams                                                 | 12-91 |

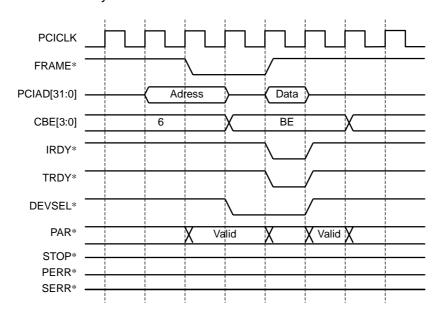

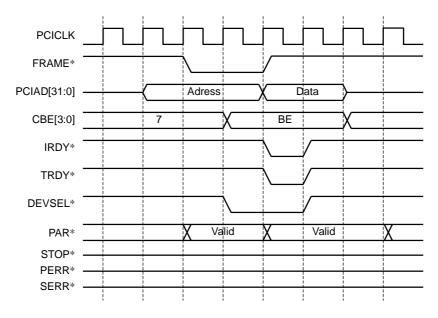

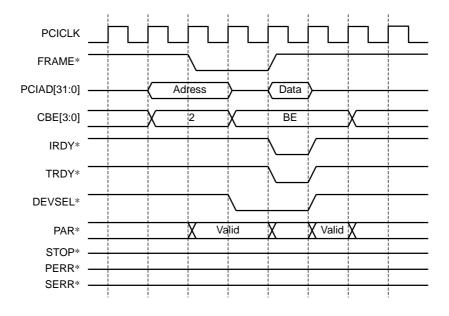

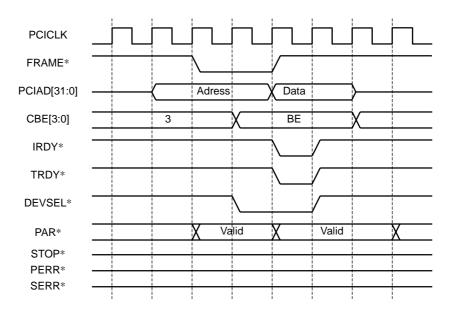

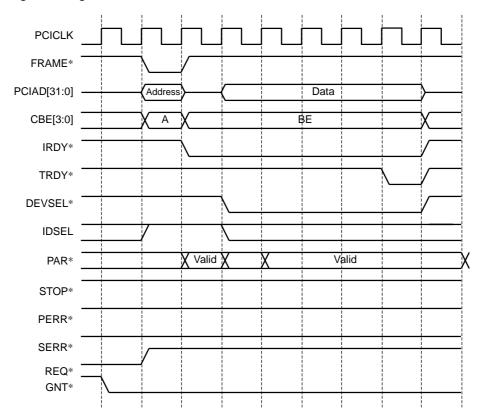

| 12.5.1       | Initiator Configuration Read                                 |       |

|              |                                                              |       |

| тозніі           | Table of Contents                                                                                      | RISC  |

|------------------|--------------------------------------------------------------------------------------------------------|-------|

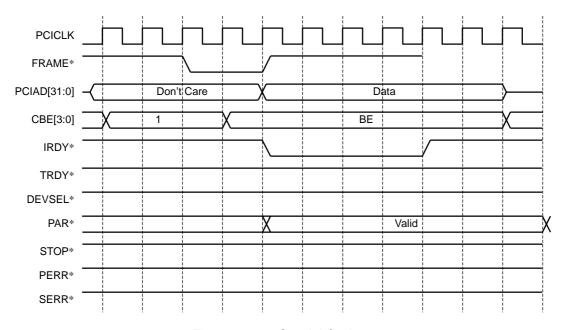

| 12.5.2           | Initiator Memory Read                                                                                  | 12-91 |

| 12.5.3           | ·                                                                                                      |       |

| 12.5.4           | · · · · · · · · · · · · · · · · · · ·                                                                  |       |

| 12.5.5           |                                                                                                        |       |

| 12.5.6           |                                                                                                        |       |

| 12.5.7           | ± •                                                                                                    |       |

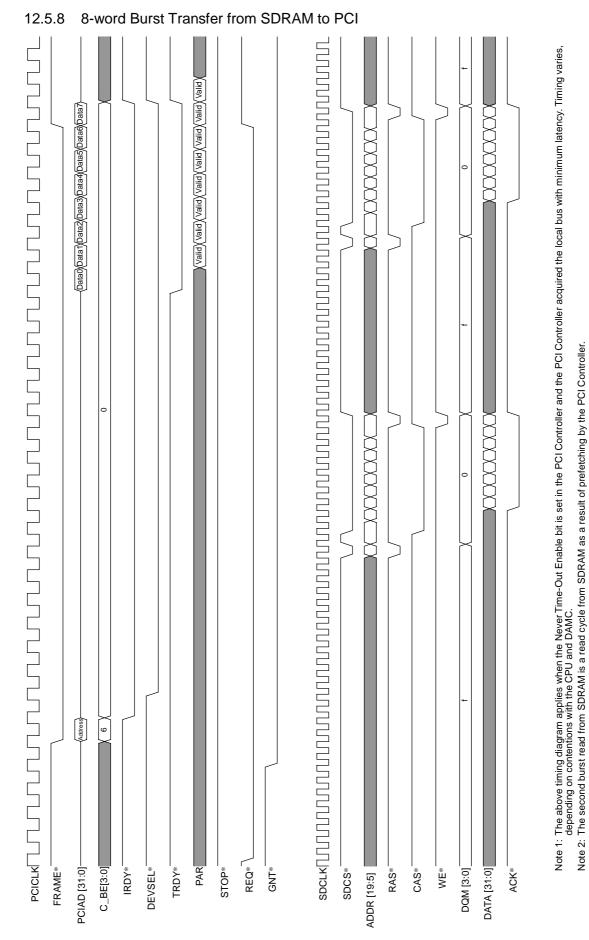

| 12.5.8           |                                                                                                        |       |

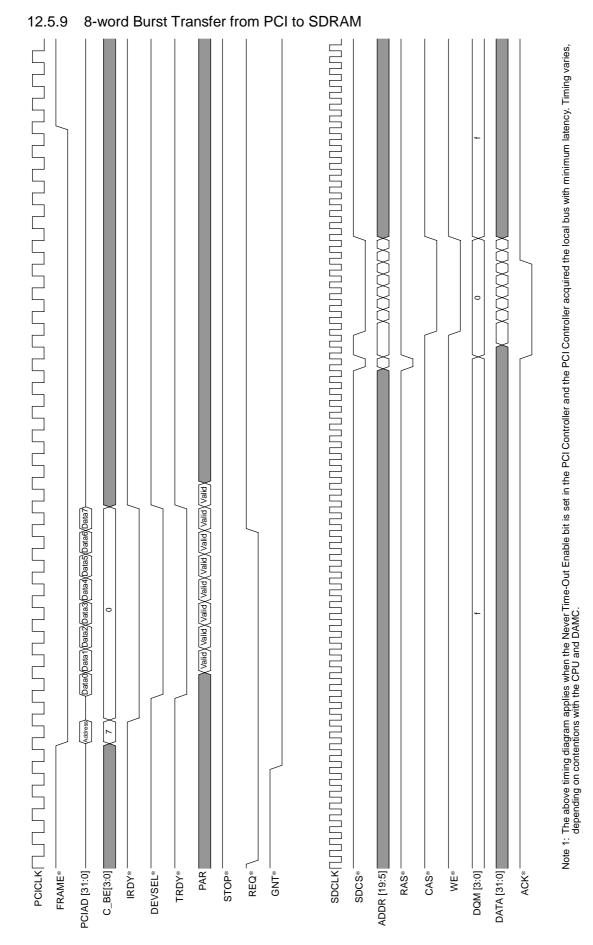

| 12.5.9           |                                                                                                        |       |

| 13. Serial I     | /O Ports (SIO)                                                                                         | 13-1  |

| 13.1 F           | eatures                                                                                                | 13-1  |

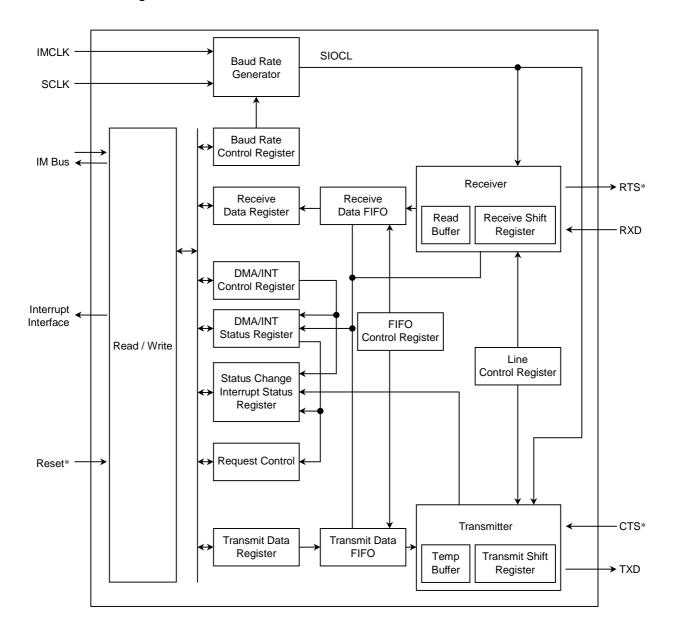

|                  | lock Diagram                                                                                           |       |

|                  |                                                                                                        |       |

|                  | egisters                                                                                               |       |

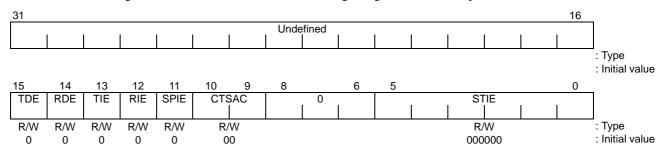

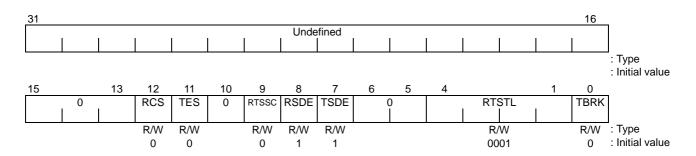

| 13.3.1           |                                                                                                        |       |

| 13.3.2           |                                                                                                        |       |

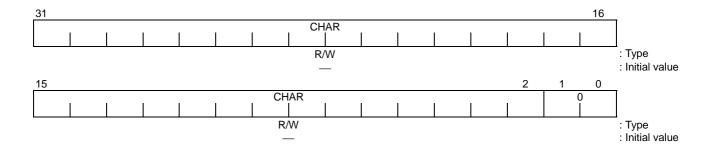

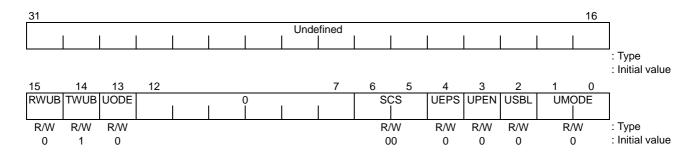

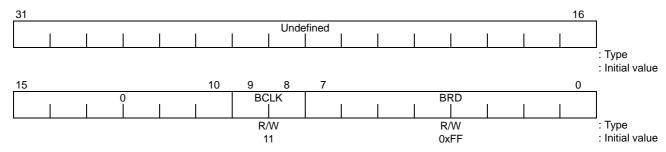

| 13.3.3<br>13.3.4 |                                                                                                        |       |

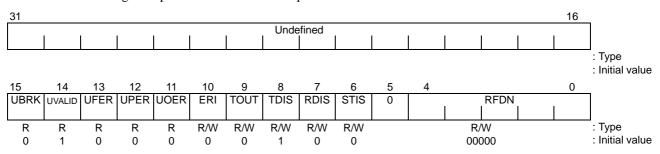

| 13.3.5           |                                                                                                        | 13-9  |

| 13.3             | 0xFFFE_F40C (Ch. 1)                                                                                    | 12 11 |

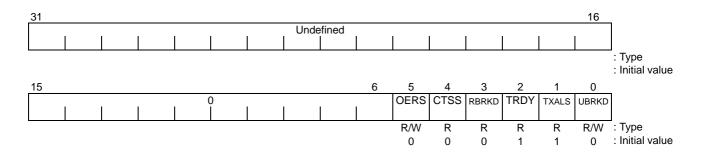

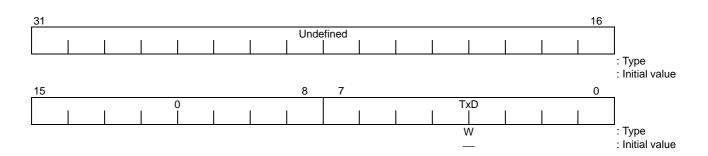

| 13.3.6           |                                                                                                        |       |

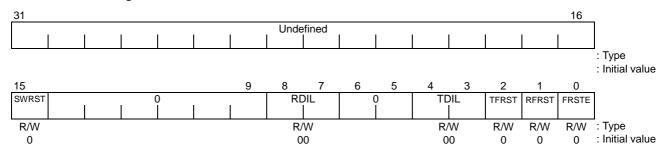

| 13.3.7           |                                                                                                        |       |

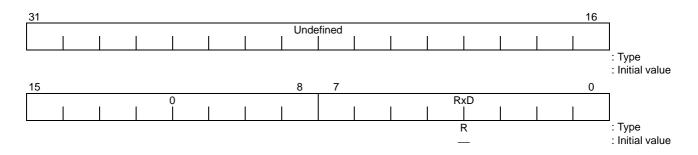

| 13.3.8           |                                                                                                        |       |

| 13.3.9           |                                                                                                        |       |

| 13.3.3           |                                                                                                        |       |

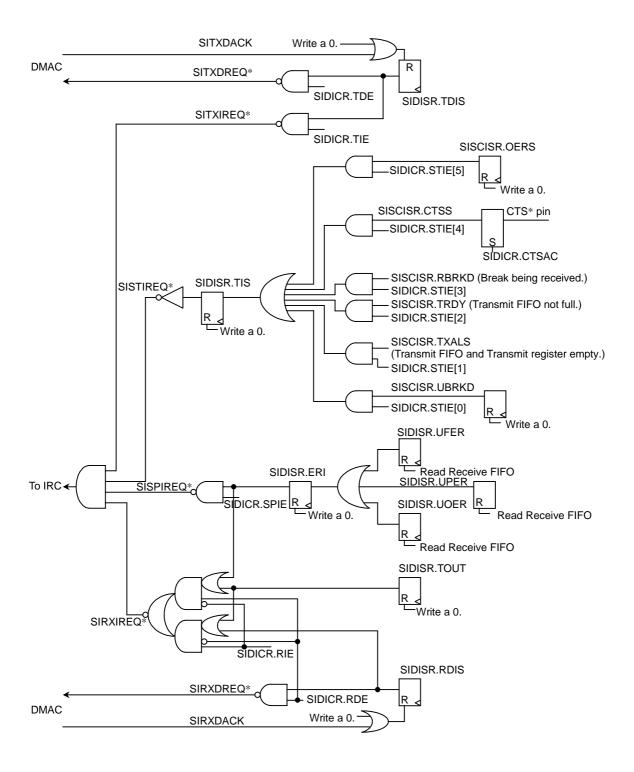

|                  |                                                                                                        |       |

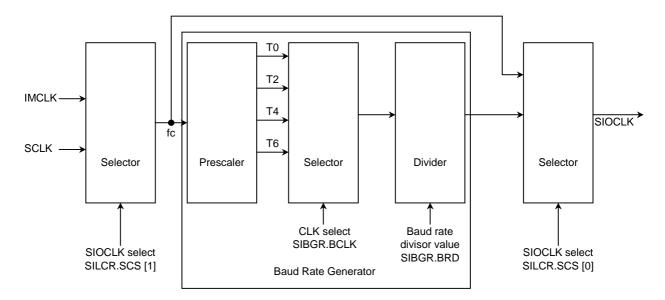

|                  | peration                                                                                               |       |

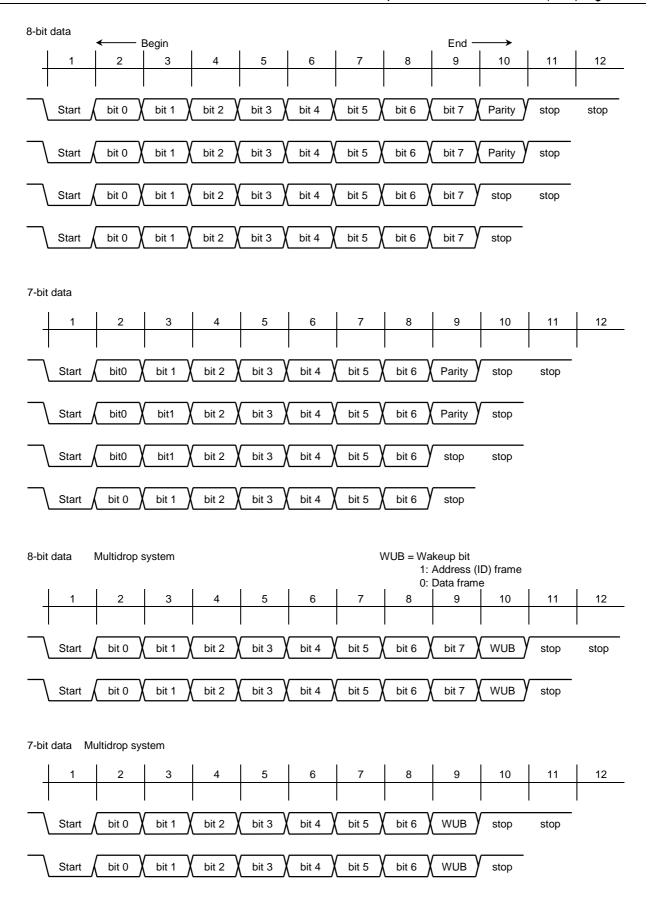

| 13.4.1           |                                                                                                        |       |

| 13.4.2           |                                                                                                        |       |

| 13.4.3           |                                                                                                        |       |

| 13.4.4           |                                                                                                        |       |

| 13.4.5           |                                                                                                        |       |

| 13.4.6           | e                                                                                                      |       |

| 13.4.7           |                                                                                                        |       |

| 13.4.8           |                                                                                                        |       |

| 13.4.9           |                                                                                                        |       |

|                  | 0 Host Interface                                                                                       |       |

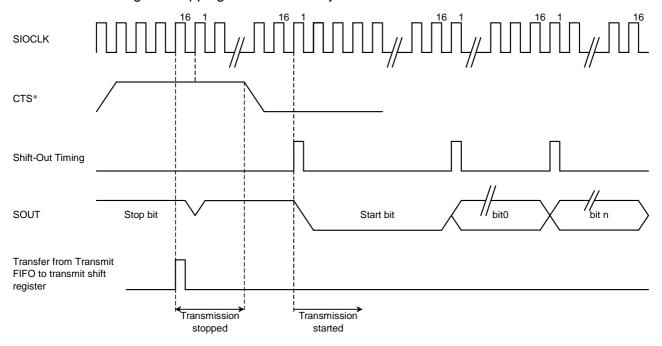

|                  | 1 Flow Controller                                                                                      |       |

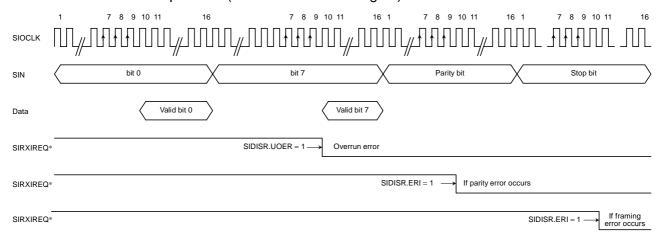

|                  | 2 Parity Controller                                                                                    |       |

|                  | 3 Error Flags                                                                                          |       |

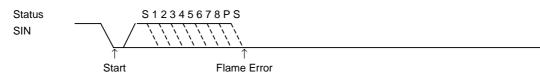

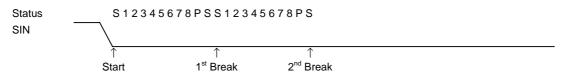

|                  | 4 Break Indication                                                                                     |       |

|                  | 5 Receive Timeout                                                                                      |       |

|                  | 6 Receive Data Transfer and the Handling of Receive FIFO Status Bits                                   |       |

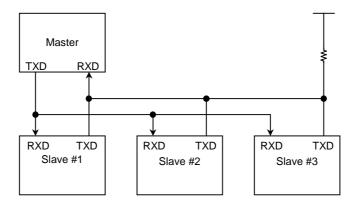

|                  | 7 Multidrop System                                                                                     |       |

|                  | 8 Software Reset                                                                                       |       |

| 13.4.1           | 9 DMA Transfer Mode                                                                                    | 13-25 |

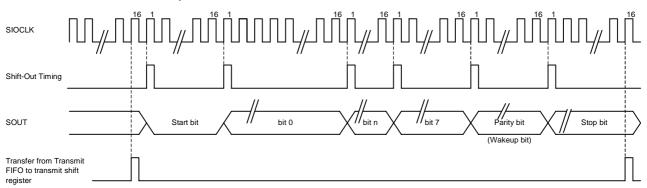

| 13.5 T           | ming Diagrams                                                                                          | 13-26 |

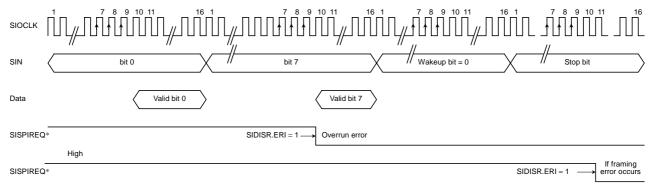

| 13.5.1           | Receiver Operation (7- and 8-bit Data Lengths)                                                         | 13-26 |

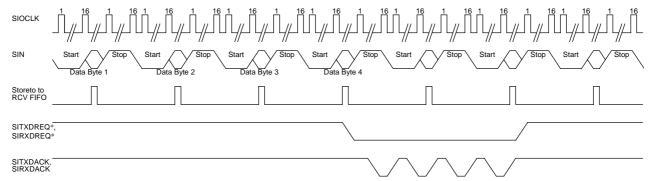

| 13.5.2           | SITXDREQ*/SITXDACK and SIRXDREQ/SIRXDACK Timing for DMA Interface                                      |       |

|                  | (DMA Level 4)                                                                                          | 13-26 |

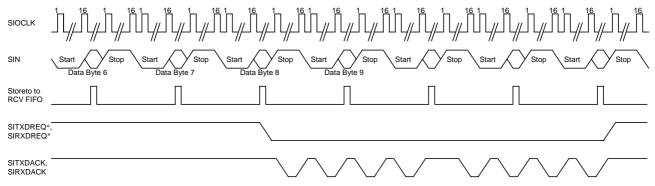

| 13.5.3           |                                                                                                        |       |

|                  | (DMA Level 8)                                                                                          | 13-26 |

| 13.5.4           |                                                                                                        |       |

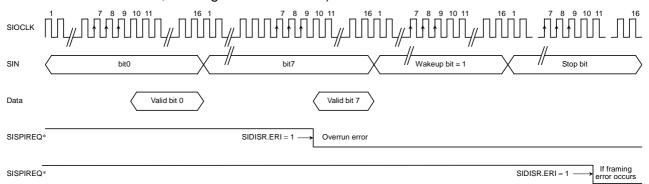

|                  | Waiting for an ID Frame)                                                                               | 13-27 |

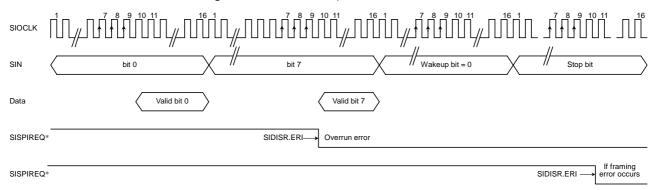

| 13.5.5           | Receiver Operation (7- and 8-bit Lengths in Multidrop System Mode, RWUB = 0, Waiting for a Data Frame) | 13-27 |

| 13.5.6           |                                                                                                        | 15 21 |

| 13.3.            | Skipping Data Read)                                                                                    | 13-27 |

| 13.5.7           |                                                                                                        |       |

| 13.5.8           |                                                                                                        |       |

|                  |                                                                                                        |       |

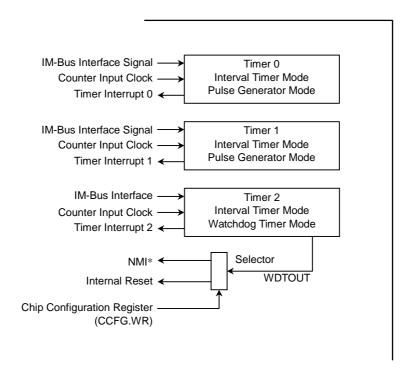

| 14. Timer/0      | Counter                                                                                                | 14-1  |

| 14.1       | Feat         | ures                                                                                              | 14-1        |

|------------|--------------|---------------------------------------------------------------------------------------------------|-------------|

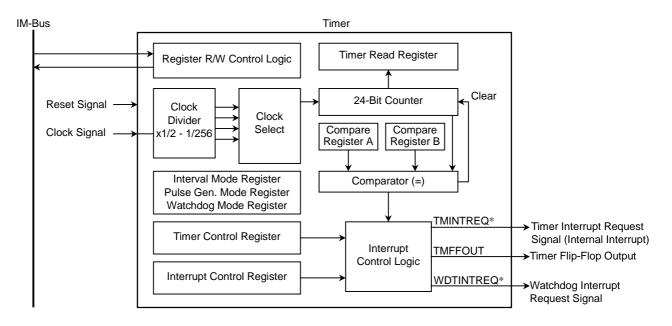

| 14.2       | Bloc         | k Diagram                                                                                         | 14-2        |

| 14.3       | Regi         | sters                                                                                             | 14-3        |

|            | .3.1         | Register Map                                                                                      |             |

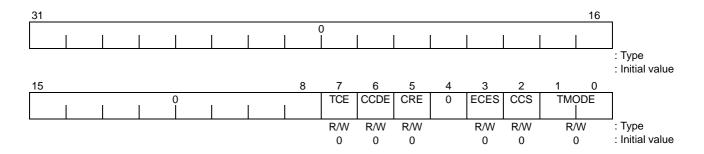

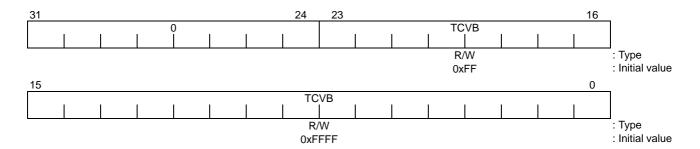

| 14         | .3.2         | Timer Control Registers (TMTCRn) 0xFFFE_F000 (Ch. 0) 0xFFFE_F100 (Ch. 1)                          |             |

|            |              | 0xFFFE_F200 (Ch. 2)                                                                               | 14-4        |

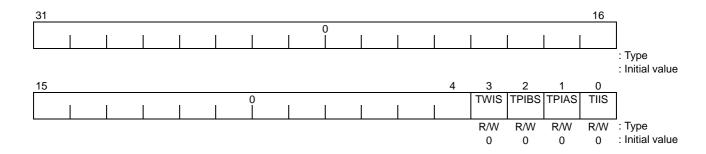

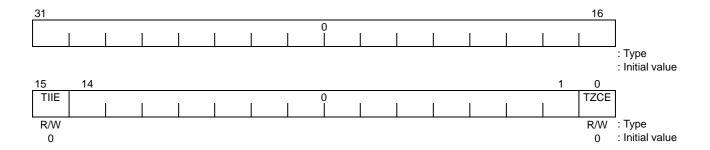

| 14         | .3.3         | Timer Interrupt Status Registers (TMTISRn) 0xFFFE_F004 (Ch. 0) 0xFFFE_F104 (Ch. 1)                |             |

| 1.4        | 2.4          | 0xFFFE_F204 (Ch. 2)                                                                               | 14-5        |

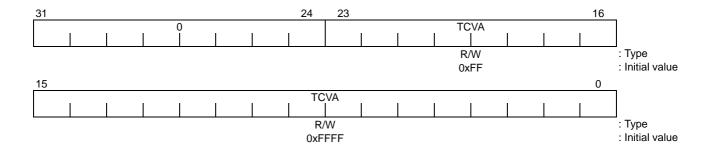

| 14         | .3.4         | Compare Registers A (TMCPRAn) 0xFFFE_F008 (Ch. 0) 0xFFFE_F108 (Ch. 1) 0xFFFE_F208 (Ch. 2)         | 147         |

| 14         | .3.5         | Compare Registers B (TMCPRBn) 0xFFFE F00C (Ch. 0) 0xFFFE F10C (Ch. 1)                             |             |

|            | .3.6         | Interval Timer Mode Registers (TMITMRn) 0xFFFE_F010 (Ch. 0) 0xFFFE_F110 (Ch. 1)                   |             |

|            |              | 0xFFFE_F210 (Ch. 2)                                                                               | 14-9        |

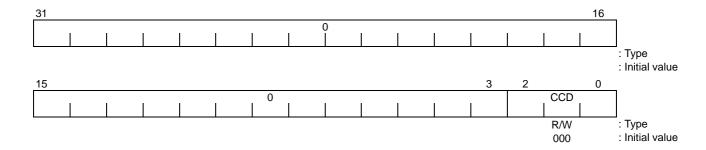

| 14         | .3.7         | Clock Divider Registers (TMCCDRn) 0xFFFE_F020 (Ch. 0) 0xFFFE_F120 (Ch. 1)                         |             |

|            |              | 0xFFFE_F220 (Ch. 2)                                                                               |             |

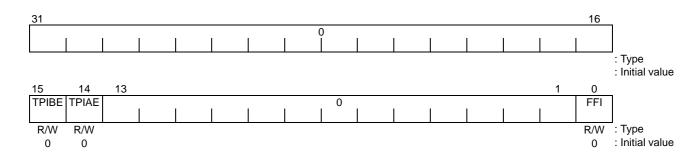

|            | .3.8         | $Pulse\ Generator\ Mode\ Registers\ (TMPGMRn)\ 0xFFFE\_F030\ (Ch.\ 0)  0xFFFE\_F130\ (Ch.\ 1)\ .$ | 14-11       |

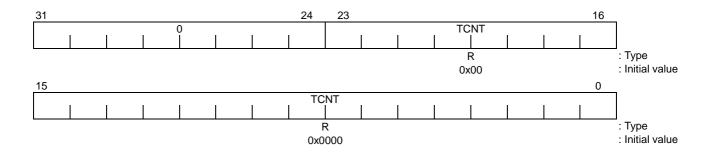

| 14         | .3.9         | Timer Read Registers (TMTRRn) 0xFFFE_F0F0 (Ch. 0) 0xFFFE_F1F0 (Ch. 1)                             | 4 4 4 4 4 4 |

| 1.4        | 2 10         | 0xFFFE_F2F0 (Ch. 2)                                                                               |             |

|            |              |                                                                                                   |             |

|            |              | ration                                                                                            |             |

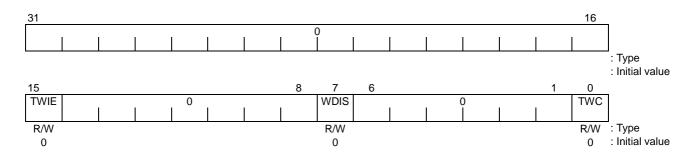

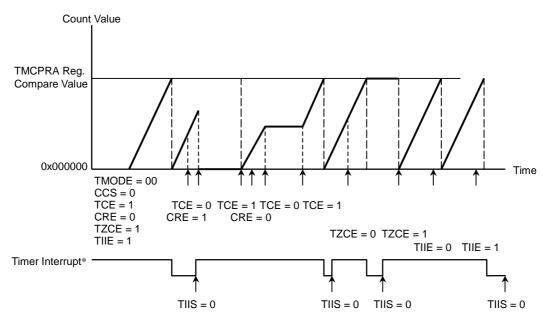

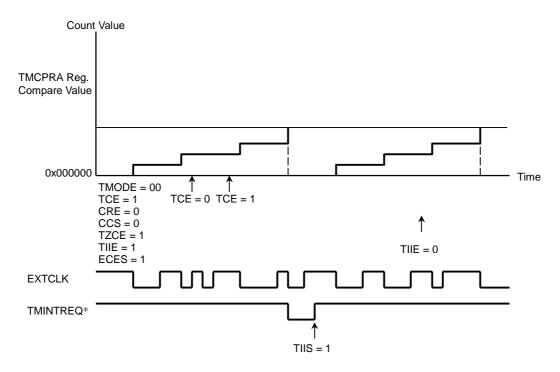

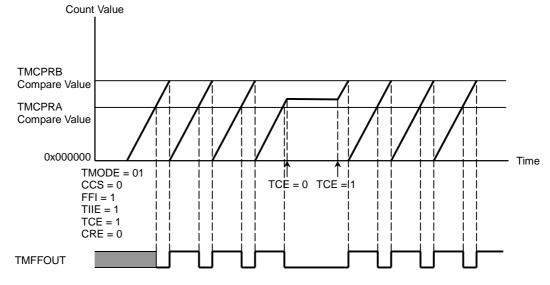

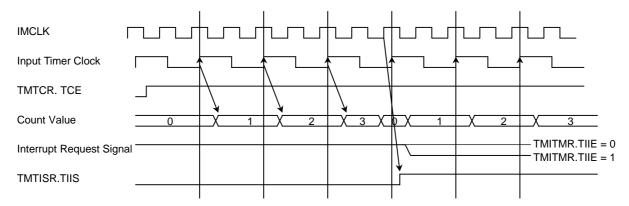

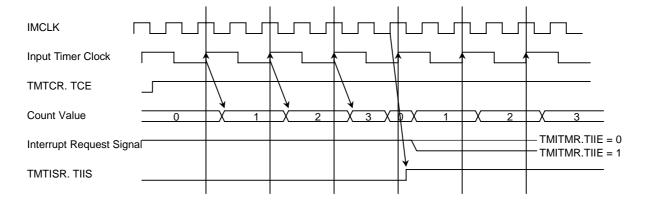

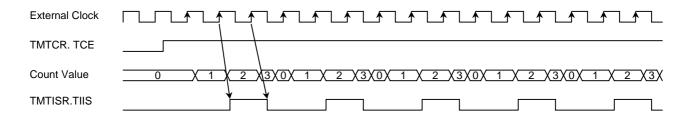

|            | .4.1<br>.4.2 | Interval Timer Mode                                                                               |             |

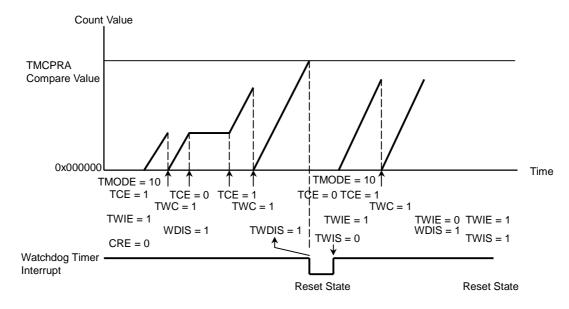

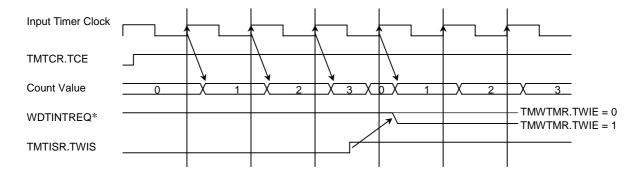

|            | .4.2<br>.4.3 | Watchdog Timer Mode                                                                               |             |

|            |              | -                                                                                                 |             |

|            | .5.1         | ng Diagrams                                                                                       |             |

|            | .5.2         | Output Flip-Flop Timing in Pulse Generator Mode                                                   |             |

|            | .5.3         | Interrupt Timing in Watchdog Timer Mode                                                           |             |

|            |              |                                                                                                   |             |

|            |              | O Port (PIO)                                                                                      |             |

| 15.1       |              | ures                                                                                              |             |

|            |              | sters                                                                                             |             |

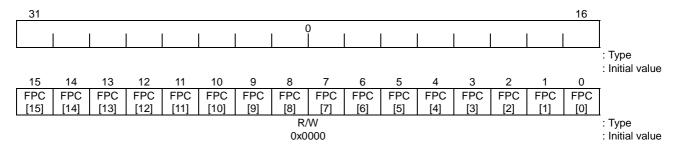

|            | .2.1         | Register Map                                                                                      |             |

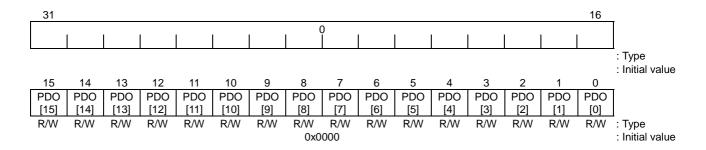

|            | .2.2         | PIO Data Output Register (XPIODO) 0xFFFE_F500                                                     |             |

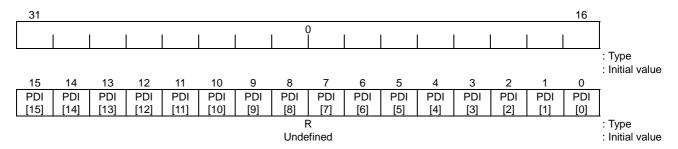

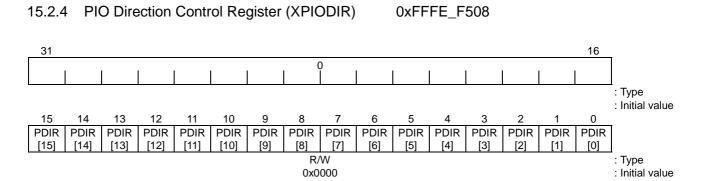

|            | .2.3<br>.2.4 | PIO Data Input Register (XPIODI) 0xFFFE_F504                                                      |             |

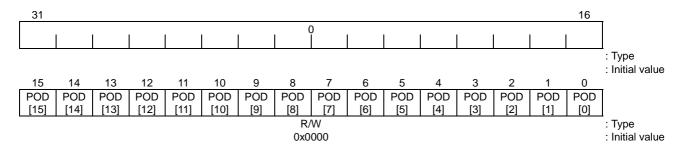

| _          | .2.4         | PIO Open-Drain Control Register (XPIOOD) 0xFFFE_E50C                                              |             |

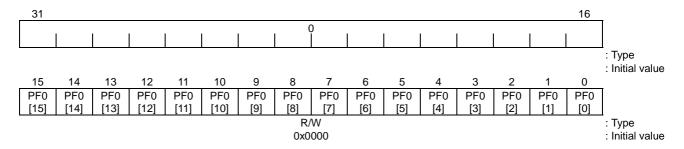

|            | .2.6         | PIO Flag Register 0 (XPIOFLAG0) 0xFFFE_F510                                                       |             |

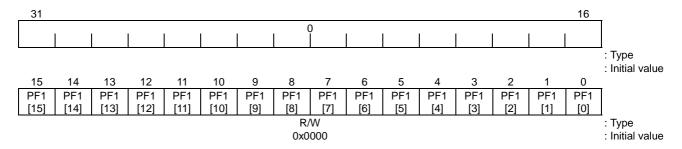

|            | .2.7         | PIO Flag Register 1 (XPIOFLAG1) 0xFFFE_F514                                                       |             |

|            | .2.8         | PIO Flag Polarity Control Register (XPIOPOL) 0xFFFE_F518                                          |             |

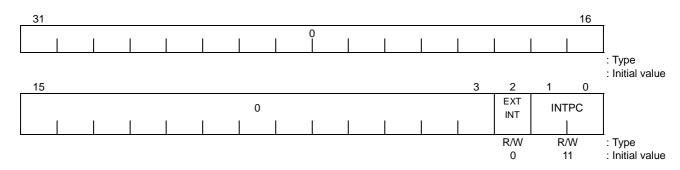

| 15         | .2.9         | PIO Interrupt Control Register (XPIOINT) 0xFFFE_F51C                                              |             |

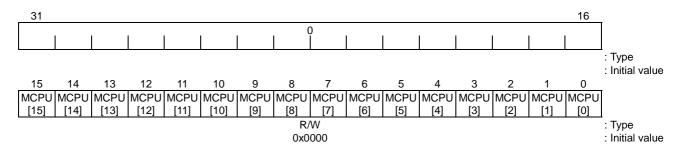

|            |              | CPU Interrupt Mask Register (XPIOMASKCPU) 0xFFFE_F520                                             |             |

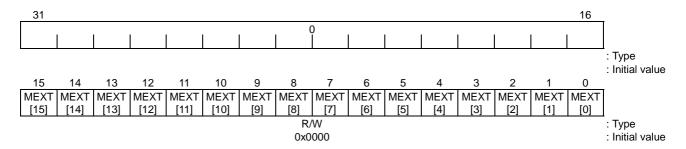

| 15         | .2.11        | External Interrupt Mask Register (XPIOMASKEXT) 0xFFFE_F524                                        | 15-11       |

| 15.3       | Oper         | ration                                                                                            |             |

|            | .3.1         | Assigning PIO Pin Functions                                                                       |             |

|            | .3.2         | General-Purpose Parallel Port                                                                     |             |

|            | .3.3         | Interrupt Requests                                                                                |             |

|            | .3.4         | Accessing PIO Pins                                                                                |             |

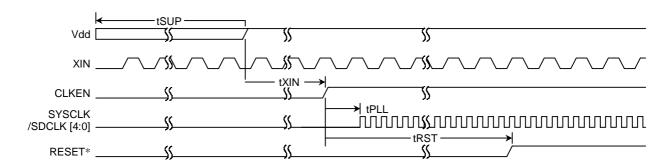

| 16. Pow    | er-On        | Sequence                                                                                          | 16-1        |

| 17. Elec   | trical       | Characteristics                                                                                   | 17-1        |

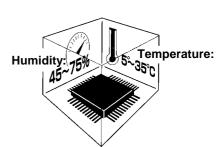

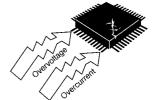

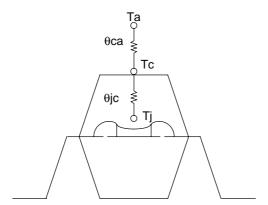

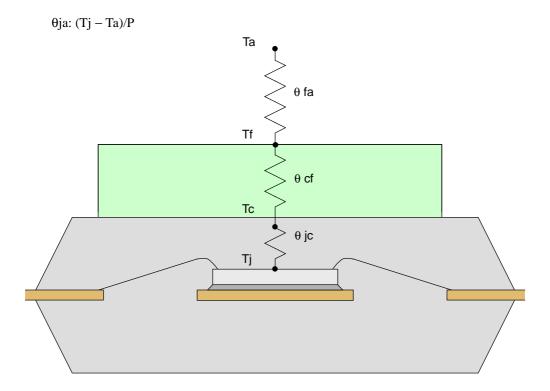

| 17.1       | Abso         | olute Maximum Ratings (*1)                                                                        | 17-1        |

| 17.2       |              | ommended Operating Conditions (*2)                                                                |             |

|            |              |                                                                                                   |             |

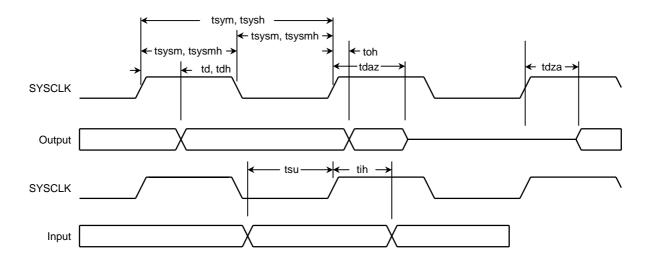

| 17.3<br>17 | .3.1         | Characteristics — Non-PCI Interface Pins                                                          |             |

|            | .3.1         | DC Characteristics – PCI Interface Pins                                                           |             |