#### TMP86FH46

## **CMOS 8-Bit Microcontroller** TMP86FH46NG

The TMP86FH46 is a high-speed, high-performance 8-bit microcomputer built around the TLCS-870/C Series core with built-in 16-Kbyte flash memory and it is pin compatible with its mask ROM version, the TMP86C846/H46. Writing programs in the built-in flash memory enables this microcomputer to perform the same operations as the TMP86C846/H46. The built-in flash memory can be rewritten on board (without removing it from the PCB) by a built-in boot program.

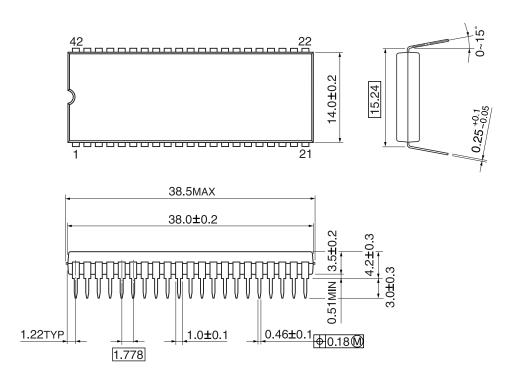

| Product No. | Flash Memory  | RAM                 | Package           |

|-------------|---------------|---------------------|-------------------|

| TMP86FH46NG | 16384 × 8 bit | $512 \times 8$ bits | P-SDIP42-600-1.78 |

## Feautures

- 8-bit single chip microcomputer TLCS-870/C series

- Instruction execution time: 0.25 µs (at 16 MHz) 122 µs (at 32.768 kHz)

- 132 types and 731 basic instructions

- 18 interrupt sources (External: 6, Internal: 12)

- Input/output ports (33 pins)

- 16-bit timer counter: 1 ch

- Timer, event counter, pulse width measurment, programmable pulse generator (PPG), external-triggered timer, window modes

- 8-bit timer counter: 2 ch

- Timer, PWM, PPG, PDO, Event counter modes

- Time base timer

- Divider output function

070122EBP

- The information contained herein is subject to change without notice. 021023 D

- TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property.

- In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc. 021023 A

- The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer's own risk. 021023 B

- The products described in this document shall not be used or embedded to any downstream products of which manufacture, use and/or sale are prohibited under any applicable laws and regulations. 060106\_Q

- The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any patents or other rights of TOSHIBA or the third parties. 070122\_C

- the products described in this document are subject to foreign exchange and foreign trade control laws. 060925\_E For a discussion of how the reliability of microcontrollers can be predicted, please refer to Section 1.3 of the chapter entitled Quality and Reliability Assurance/Handling Precautions. 030619 S

- Watchdog timer

- Interrupt sources/reset output (Programmable)

- Serial interface

- 8-bit SIO: 1 ch

- 8-bit UART: 1 ch

- 10-bit successive approximation type AD converter

- Analog input: 8 ch

- ♦ Key-on wakeup: 4 ch

- Dual clock operation

- Single/dual-clock mode

- Nine power saving operating modes

- STOP mode: Oscillation stops. Battery/capacitor backup. Port output hold/high-impedance.

- SLOW 1, 2 mode: Low power consumption operation using low-frequency clock (32.768 kHz)

- IDLE 0 mode: CPU stops, and peripherals operate using high-frequency clock of timebase-timer. Release by INTTBT interrupt.

- IDLE 1 mode: CPU stops, and peripherals operate using high-frequency clock. Release by interrupts.

- IDLE 2 mode: CPU stops, and peripherals operate using high and low frequency clock. Release by interrupts.

- SLEEP 0 mode: CPU stops, and peripherals operate using low-frequency clock of timebase-timer. Release by INTTBT interrupt.

- SLEEP 1 mode: CPU stops, and peripherals operate using low-frequency clock. Release by interrupts.

- SLEEP 2 mode: CPU stops, and peripherals operate using high and low frequency clock. Release by interrupts.

- ♦ Wide operating voltage: 4.5 to 5.5 V at 16 MHz/32.768 kHz 2.7 to 5.5 V at 8 MHz/32.768 kHz

- Note: The operating voltage, the operating temperature and the operating current are different between TMP86FH46 and TMP86C846/H46. About details, please refer to electrical characteristics of each products.

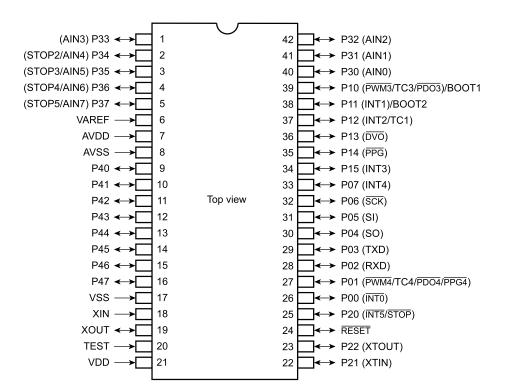

## Pin Assignments (Top view)

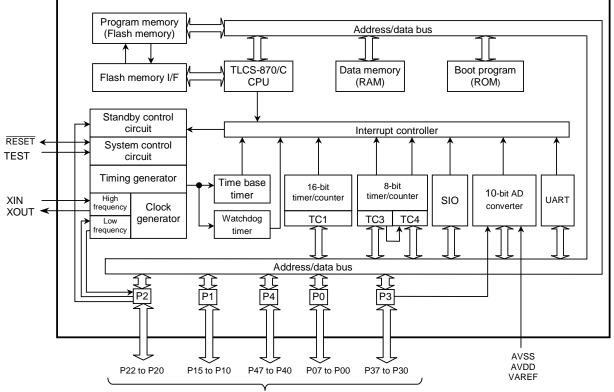

## **Block Diagram**

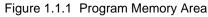

The TMP86FH46 has MCU mode and serial PROM mode.

(1) MCU mode

In the MCU mode, the TMP86FH46 is a pin compatible with the TMP86C846/H46 (Make sure to fix the TEST pin to low level).

(2) Serial PROM mode

The serial PROM mode is set by fixing TEST pin, P10 and P11 at "high" respectively when  $\overline{\text{RESET}}$  pin is fixed "low".

After release of reset, the built-in BOOT ROM program is activated and the built-in flash memory is rewritten by serial I/F (UART).

| Pin Name<br>(Serial PROM mode)                                | Input/<br>Output | Functions                                                                          | Pin Name<br>(MCU mode) |  |  |

|---------------------------------------------------------------|------------------|------------------------------------------------------------------------------------|------------------------|--|--|

| BOOT1/RXD                                                     | Input/Input      | Fix "High" during reset. This pin is used as RXD pin after releasing reset.        | P10                    |  |  |

| BOOT2/TXD                                                     | Input/Output     | Fix "High" during reset. This pin is used as P11<br>TXD pin after releasing reset. |                        |  |  |

| TEST                                                          | Input            | Fix to "High".                                                                     |                        |  |  |

| RESET                                                         | I/O              | Reset signal input or an internal error reset output.                              |                        |  |  |

| VDD, AVDD                                                     |                  | 5 V                                                                                |                        |  |  |

| VSS, AVSS                                                     | Power supply     | 0 V                                                                                |                        |  |  |

| VAREF                                                         |                  | Leave open or apply reference voltage.                                             |                        |  |  |

| P07 to P00, P15 to P12, P22 to P20,<br>P37 to P30, P47 to P40 |                  | Fix to "Low" or "High".                                                            |                        |  |  |

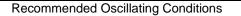

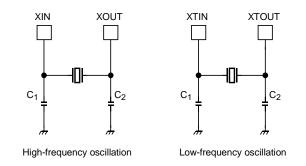

| XIN                                                           | Input            | Solf assillation with reconstor (2 MHz, 4 MHz, 9 MHz, 16 MHz)                      |                        |  |  |

| XOUT                                                          | Output           | Self oscillation with resonator (2 MHz, 4 MHz, 8 MHz, 16 MHz)                      |                        |  |  |

## Operation

This section describes the functions and basic operational blocks of TMP86FH46.

The TMP86FH46 has flash memory in place of the mask ROM which is included in the TMP86C846/H46. The configuration and function are the same as the TMP86C846/H46.

## 1. Operating Mode

The TMP86FH46 has MCU mode and serial PROM mode.

### 1.1 MCU Mode

The MCU mode is set by fixing the TEST pin to the low level. In the MCU mode, the operation is the same as the TMP86C846/H46.

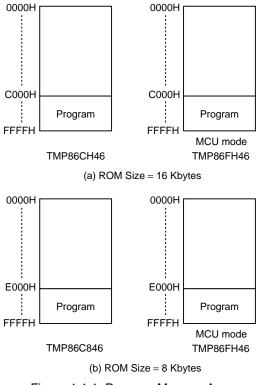

### 1.1.1 Program memory

The TMP86FH46 has a 16-Kbyte built-in flash memory (addresses C000H to FFFFH in the MCU mode).

When using TMP86FH46 for evaluation of TMP86C846/H46, the program is written by the serial PROM mode.

Note: The area that is not in use should be set data to FFH.

### 1.1.2 Data Memory

TMP86FH46 has a built-in 512-byte data memory (Static RAM).

### 1.1.3 Input/Output Circuitry

(1) Control pins

The control pins of the TMP86FH46 are the same as those of the TMP86C846/H46.

(2) I/O ports

The I/O circuitries of TMP86FH46 I/O ports are the same as the those of TMP86C846/H46.

### 2. Serial PROM Mode

#### 2.1 Outline

The TMP86FH46 has a 2-Kbyte BOOT ROM for programming to flash memory. This BOOT ROM is a mask ROM that contains a program to write the flash memory on-board. The BOOT ROM is available in a serial PROM mode and it is controlled by TEST pin and RESET pin and 2 I/O pins, and is communicated with UART. There are four operation modes in a serial PROM mode: flash memory writing mode, RAM loader mode, flash memory SUM output mode and product discrimination code output mode. Operating area of serial PROM mode differs from that of MCU mode. The operating area of serial PROM mode shows in Table 2.1.1.

| Parameter         | Symbol          | Min         | Max | Unit |

|-------------------|-----------------|-------------|-----|------|

| Operating voltage | V <sub>DD</sub> | 4.5         | 5.5 | V    |

| High frequency    | fc              | 2, 4, 8, 16 |     | MHz  |

| Temperature       | Topr            | 25          | °C  |      |

Table 2.1.1 Operating Area of Serial PROM Mode

### 2.2 Memory Mapping

The BOOT ROM is mapped in address F800H to FFFFH. The BOOT ROM can't be accessed in MCU mode. The Figure 2.2.1 shows a memory mapping.

Figure 2.2.1 Memory Address Maps

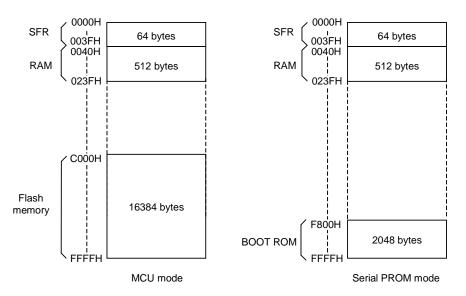

### 2.3 Serial PROM Mode Setting

#### 2.3.1 Serial PROM Mode Control Pins

To execute on-board programming, start the TMP86FH46 in serial PROM mode. Setting of a serial PROM mode is shown in Table 2.3.1.

| Pin                | Setting |

|--------------------|---------|

| TEST pin           | High    |

| BOOT1 (RXD) (Note) | High    |

| BOOT2 (TXD) (Note) | High    |

| RESET pin          |         |

Table 2.3.1 Serial PROM Mode Setting

Note: BOOT1 is RXD pin and BOOT2 is TXD pin during a serial PROM mode.

#### 2.3.2 Pin Function

In the serial PROM mode, TXD (P11) and RXD (P10) pins are used as a serial interface pin. Therefore, if the programming is executed on-board after mounting, these pins should be released from the other devices for communication in serial PROM mode.

| Pin Name<br>(Serial PROM mode)                                | Input/<br>Output | Functions Pin Nan<br>(MCU mo                                                |     |  |  |

|---------------------------------------------------------------|------------------|-----------------------------------------------------------------------------|-----|--|--|

| BOOT1/RXD                                                     | Input/Input      | Fix "High" during reset. This pin is used as RXD pin after releasing reset. | P10 |  |  |

| BOOT2/TXD                                                     | Input/Output     | Fix "High" during reset. This pin is used as TXD pin after releasing reset. | P11 |  |  |

| TEST                                                          | Input            | Fix to "High".                                                              |     |  |  |

| RESET                                                         | I/O              | Reset signal input or an internal error reset output.                       |     |  |  |

| VDD, AVDD                                                     |                  | 5 V                                                                         |     |  |  |

| VSS, AVSS                                                     | Power supply     | 0 V                                                                         |     |  |  |

| VAREF                                                         |                  | Leave open or apply reference voltage.                                      |     |  |  |

| P07 to P00, P15 to P12, P22 to P20,<br>P37 to P30, P47 to P40 |                  | Fix to "low" or "high".                                                     |     |  |  |

| XIN                                                           | Input            |                                                                             |     |  |  |

| XOUT                                                          | Output           | Self oscillation with resonator (2 MHz, 4 MHz, 8 MHz, 16 MHz)               |     |  |  |

Note: When the device is used as on-board writing and other parts are already mounted in place, be careful not to affect these communication control pins.

To set a serial PROM mode, connect device pins as shown in Figure 2.3.1.

Figure 2.3.1 Serial PROM Mode Port Setting

#### 2.3.3 Activating Serial PROM Mode

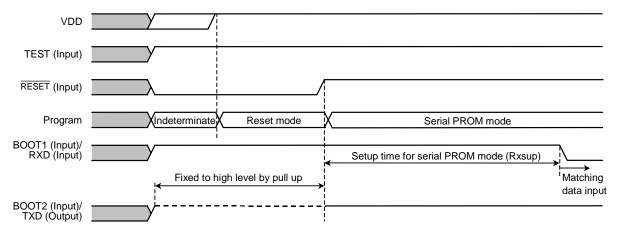

The following is a procedure of setting of serial PROM mode. Figure 2.3.2 shows a serial PROM mode timing.

- (1) Turn on the power to the VDD pin.

- (2) Set the  $\overline{\text{RESET}}$  to low level.

- (3) Set the TEST, BOOT1 and BOOT2 pin to high level.

- (4) Wait until the power supply and clock sufficiently stabilize.

- (5) Release the  $\overline{\text{RESET}}$  (Set to high level).

- (6) Input a matching data (5AH) to BOOT1/RXD pin after waiting for setup sequence. For details of the setup timing, refer to 2.14 "UART Timing".

Figure 2.3.2 Serial PROM Mode Timing

### 2.4 Interface Specifications for UART

The following shows the UART communication format used in serial PROM mode. Before on-board programming can be executed, the communication format on the external controller side must also be setup in the same way as for this product.

Note that although the default baud rate is 9,600 bps, it can be changed to other values as shown in Table 2.4.1. The Table 2.4.2 shows an operating frequency and baud rate in serial PROM mode. Except frequency which is not described in Table 2.4.2 can not use in serial PROM mode.

Baud rate (Default): 9,600 bps Data length: 8 bits Parity addition: None Stop bit length: 1 bit

| Baud rate modification data | 04H   | 05H   | 07H   | 0AH   | 18H   | 28H  |

|-----------------------------|-------|-------|-------|-------|-------|------|

| Baud rate (bps)             | 76800 | 62500 | 38400 | 31250 | 19200 | 9600 |

| Table 2.4.1 Baud Rate Modification | ı Data |

|------------------------------------|--------|

|------------------------------------|--------|

| Table 2.4.2 Operating Frequence | / and Baud Rate in Serial PROM Mode |

|---------------------------------|-------------------------------------|

|---------------------------------|-------------------------------------|

| Reference Baud<br>Rate (Baud)   | 768   | 300   | 625   | 500  | 384   | 400   | 312   | 250  | 192   | 200   | 96    | 00    |

|---------------------------------|-------|-------|-------|------|-------|-------|-------|------|-------|-------|-------|-------|

| Baud Rate<br>Modification Data  | 04    | 1H    | 05    | iΗ   | 07    | Ή     | 0A    | λH   | 18    | BH    | 28    | 3H    |

| Reference<br>Frequency<br>(MHz) | (bps) | (%)   | (bps) | (%)  | (bps) | (%)   | (bps) | (%)  | (bps) | (%)   | (bps) | (%)   |

| 2                               | -     | -     | -     | _    | -     | -     | -     | -    | -     | _     | 9615  | +0.16 |

| 4                               | _     | _     | -     | _    | -     | _     | 31250 | 0.00 | 19231 | +0.16 | 9615  | +0.16 |

| 8                               | _     | _     | 62500 | 0.00 | 38462 | +0.16 | 31250 | 0.00 | 19231 | +0.16 | 9615  | +0.16 |

| 16                              | 76923 | +0.16 | 62500 | 0.00 | 38462 | +0.16 | 31250 | 0.00 | 19231 | +0.16 | 9615  | +0.16 |

Note: "Reference Frequency" shows the high-frequency area supported in serial PROM mode. Except the above frequency can not be supported in serial PROM mode.

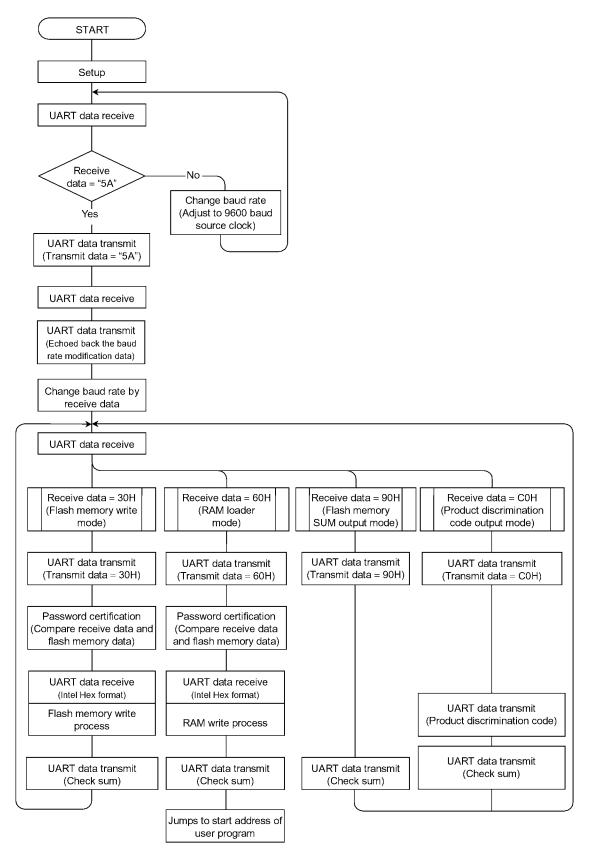

### 2.5 Command

There are five commands in serial PROM mode. After reset release, the TMP86FH46 waits a matching data (5AH).

| Command Data | Operation Mode                     | Remarks                                                                                                                 |

|--------------|------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| 5AH          | Setup                              | Matching data. Always start with this command after reset release.                                                      |

| 30H          | Flash memory writing               | Writing to area from C000H to FFFFH is enable.                                                                          |

| 60H          | RAM loader                         | Writing to area from 0050H to 0230H is enable.                                                                          |

| 90H          | Flash memory SUM output            | The checksum of entire flash memory area (from C000H to FFFFH) is output in order of the upper byte and the lower byte. |

| СОН          | Product discrimination code output | Product discrimination code, that is expressed by 13 bytes data, is output.                                             |

Table 2.5.1 Command in Serial PROM Mode

#### 2.6 Operation Mode

There are four operating modes in serial PROM mode: Flash memory writing mode, RAM loader mode, flash memory SUM output mode and product discrimination code output mode. For details about these modes, refer to (1) Flash memory writing mode through (4) Product discrimination code output mode.

#### (1) Flash memory writing mode

The data are written to the specified flash memory addresses. The controller should send the write data in the Intel Hex format (Binary). For details of writing data format, refer to 2.7 "Flash Memory Writing Data Format".

If no errors are encountered till the end record, the SUM of 16 Kbytes of flash memory is calculated and the result is returned to the controller.

To execute the flash memory writing mode, the TMP86FH46 checks the passwords except a blank product. If the passwords did not match, the program is not executed.

#### (2) RAM loader mode

The RAM loader transfers the data into the internal RAM that has been sent from the controller in Intel Hex format. When the transfer has terminated normally, the RAM loader calculates the SUM and sends the result to the controller before it starts executing the user program. After sending of SUM, the program jumps to the start address of RAM in which the first transferred data has been written. This RAM loader function provides the user's own way to control on-board programming.

To execute the RAM loader mode, the TMP86FH46 checks the passwords except a blank product. If the passwords did not match, the program is not executed.

#### (3) Flash memory SUM output mode

The SUM of 16 Kbytes of flash memory is calculated and the result is returned to the controller.

The BOOT ROM does not support the reading function of the flash memory. Instead, it has this SUM command to use. By reading the SUM, it is possible to manage Revisions of application programs.

#### (4) Product discrimination code output mode

The product discrimination code is output as a 13-byte data, that includes the start address and the end address of ROM. (In case of TMP86FH46, the start address is C000H and the end address is FFFFH.) Therefore, the controller can recognize the device information by using this function.

#### 2.6.1 Flash Memory Writing Mode (Operation command: 30H)

Table 2.6.1 shows flash memory writing mode process.

|      | Number of     | Transfer Data from                                     |                       | Transfer Data from                                    |

|------|---------------|--------------------------------------------------------|-----------------------|-------------------------------------------------------|

|      | Bytes         | External Controller to                                 | Baud Rate             | TMP86FH46 to External                                 |

|      | Transferred   | TMP86FH46                                              |                       | Controller                                            |

|      | 1st byte      | Matching data (5AH)                                    | 9600 bps              | <ul> <li>– (Baud rate auto set)</li> </ul>            |

|      | 2nd byte      | -                                                      | 9600 bps              | OK: Echo back data (5AH)                              |

|      |               |                                                        |                       | Error: Nothing transmitted                            |

|      | 3rd byte      | Baud rate modification data                            | 9600 bps              | -                                                     |

|      |               | (See Table 2.4.1)                                      |                       |                                                       |

|      | 4th byte      | -                                                      | 9600 bps              | OK: Echo back data                                    |

|      |               |                                                        |                       | Error: A1H $\times$ 3, A3H $\times$ 3, 62H $\times$ 3 |

|      | 5th byte      | Operation command data (30H)                           | Changed new baud rate | (Note 1)                                              |

|      | 6th byte      |                                                        | Changed new baud rate | OK: Echo back data (30H)                              |

|      | our byte      |                                                        | Changed new badd rate | Error: A1H $\times$ 3, A3H $\times$ 3, 63H $\times$ 3 |

|      |               |                                                        |                       | (Note 1)                                              |

|      | 7th byte      | Address 15 to 08 in which to                           | Changed new baud rate | -                                                     |

|      | 8th byte      | store Password count (Note 4)                          | Changed new baud rate | OK: Nothing transmitted                               |

|      |               |                                                        |                       | Error: Nothing transmitted                            |

|      | 9th byte      | Address 07 to 00 in which to                           | Changed new baud rate | -                                                     |

|      | 10th byte     | store Password count (Note 4)                          | Changed new baud rate | OK: Nothing transmitted                               |

| воот |               |                                                        |                       | Error: Nothing transmitted                            |

| ROM  | 11th byte     | Address 15 to 08 in which to start Password comparison | Changed new baud rate |                                                       |

|      | 12th byte     | (Note 4)                                               | Changed new baud rate | OK: Nothing transmitted                               |

|      | 13th byte     | Address 07 to 00 in which to                           | Changed new baud rate | Error: Nothing transmitted                            |

|      | 14th byte     | start Password comparison                              | Changed new baud rate | OK: Nothing transmitted                               |

|      | i illi byto   | (Note 4)                                               | Changed new Sada rate | Error: Nothing transmitted                            |

|      | 15th byte     | Password string (Note 5)                               | Changed new baud rate |                                                       |

|      | :             |                                                        | C C                   |                                                       |

|      | m'th byte     | -                                                      | Changed new baud rate | OK: Nothing transmitted                               |

|      |               |                                                        |                       | Error: Nothing transmitted                            |

|      | m'th + 1 byte | Extended Intel format (binary)                         | Changed new baud rate | -                                                     |

|      | :             | (Note 2, 6)                                            |                       |                                                       |

|      | n'th – 2 byte |                                                        |                       |                                                       |

|      | n'th – 1 byte | -                                                      | Changed new baud rate | OK: SUM (High) (Note 3)                               |

|      | n'th byte     | _                                                      | Changed new baud rate | Error: Nothing transmitted<br>OK: SUM (Low) (Note 3)  |

|      | ii iii byte   | _                                                      |                       | Error: Nothing transmitted                            |

|      | n'th + 1 byte | (Wait for the next operation)                          | Changed new baud rate |                                                       |

|      | in an in byto | (Command data)                                         | changed new badd late |                                                       |

|      | I             | (communic dutu)                                        |                       |                                                       |

Note 1: "xxH  $\times$  3" denotes that operation stops after sending 3 bytes of xxH. For details, refer to 2.8 "Error Code".

Note 2: Refer to 2.10 "Intel Hex Format (Binary)".

Note 3: Refer to 2.9 "Checksum (SUM)".

Note 4: Refer to 2.11 "Passwords".

Note 5: If all data of vector area are "00H" or "FFH", the passwords comparison is not executed because the device is considered as blank product. However, it is necessary to specify the password count storage addresses and the password comparison start address even though it is a blank product. If a password error occurs, the UART function of TMP86FH46 stops without returning error code to the controller. Therefore, when a password error occurs, the TMP86FH46 should be reset by RESET pin input.

Note 6: The time between data records needs over 1 ms.

Description of flash memory writing mode

- 1. The receive data in the 1st byte is the matching data. When the boot program starts in serial PROM mode, TMP86FH46 (Mentioned as "device" hereafter) waits for the matching data (5AH) to receive. Upon receiving the matching data, it automatically adjusts the UART's initial baud rate to 9,600bps.

- 2. When the device has received the matching data, the device transmits the data "5AH" as an echo back to the controller. If the device can not receive the matching data, the device does not transmit the echo back data and waits for the matching data again with changing baud rate. Therefore, the controller should send the matching data continuously until the device transmits the echo back data.

- 3. The receive data in the 3rd byte is the baud rate modification data. The six kinds of baud rate modification data shown in Table 2.4.1 are available. Even if baud rate changing is no need, be sure to send the initial baud rate data (28H: 9,600 bps). The changing of baud rate is executed after transmitting the echo back data.

- 4. When the 3rd byte data is one of the baud rate modification data corresponding to the device's operating frequency, the device sends the echo back data which is the same as received baud rate modification data. Then the baud rate is changed. If the 3rd byte data does not correspond to the baud rate modification data, the device stops UART function after sending 3 bytes of baud rate modification error code: (62H).

- 5. The receive data in the 5th byte is the command data (30H) to write the flash memory.

- 6. When the 5th byte is one of the operation command data shown in Table 2.5.1, the device sends the echo back data which is the same as received operation command data (in this case, 30H). If the 5th byte data does not correspond to the operation command data, the device stops UART function after sending 3 bytes of operation command error code: (63H).

- 7. The 7th byte is used as an upper bit (Bit15 to bit8) of the password count storage address. When the receiving is executed correctly (No error), the device does not send any data. If the receiving error or password error occur, the device does not send any data and stops UART function.

- 8. The 9th byte is used as a lower bit (Bit7 to bit0) of the password count storage address. When the receiving is executed correctly (No error), the device does not send any data. If the receiving error or password error occur, the device does not send any data and stops UART function.

- 9. The 11th byte is used as an upper bit (Bit15 to bit8) of the password comparison start address. When the receiving is executed correctly (No error), the device does not send any data. If the receiving error or password error occur, the device does not send any data and stops UART function.

- 10. The 13th byte is used as a lower bit (Bit7 to bit0) of the password comparison start address. When the receiving is executed correctly (No error), the device does not send any data. If the receiving error or password error occur, the device does not send any data and stops UART function.

- 11. The 15th through the m'th bytes are the password data. The number of passwords is the data (N) indicated by the password count storage address. The password data are compared for N entries beginning with the password comparison start address. The controller should send N bytes of password data to the device. If the passwords do not match, the device stops UART function without returning error code to the controller. If the data of vector addresses (FFE0H to FFFFH) are all "FFH", the comparison of passwords is not executed because the device is considered as a blank product.

- 12. The receive data in the m'th + 1 through n'th 2 byte are received as binary data in Intel Hex format. No received data are echoed back to the controller. The data which is not the start mark (3AH for ":") in Intel Hex format is ignored and does not send an error code to the controller until the device receives the start mark. After receiving the start mark, the device receives the data record, that consists of length of data, address, record type, writing data and checksum. After receiving the checksum of data record, the device waits the start mark data (3AH) again. The data of data record is temporarily stored to RAM and then, is written to specified flash memory by page (32 bytes) writing. For details of an organization of flash memory, refer to 2. "Serial PROM Mode". Since after receiving an end record, the device starts to calculate the SUM, the controller should wait the SUM after sending the end record. If receive error or Intel Hex format error occurs, the device stops UART function without returning error code to the controller.

- 13. The n'th 1 and the n'th bytes are the SUM value that is sent to the controller in order of the upper byte and the lower byte. For details on how to calculate the SUM, refer to 2.9 "Checksum (SUM)". The SUM calculation is performed after detecting the end record, but the calculation is not executed when receive error or Intel Hex format error has occurred. The time required to calculate the SUM of the 16 Kbytes of Flash memory area is approximately 100 ms at fc = 16 MHz. After the SUM calculation, the device sends the SUM data to the controller. After sending the end record, the controller can judge that the transmission has been terminated correctly by receiving the checksum.

- 14. After sending the SUM, the device waits for the next operation command data.

#### 2.6.2 RAM Loader Mode (Operation command: 60H)

Table 2.6.2 shows RAM loader mode process.

|      | Number of                      | Transfer Data from                                        |                                                | Transfer Data from                                                   |

|------|--------------------------------|-----------------------------------------------------------|------------------------------------------------|----------------------------------------------------------------------|

|      | Bytes                          | External Controller to                                    | Baud Rate                                      | TMP86FH46 to External                                                |

|      | Transferred                    | TMP86FH46                                                 |                                                | Controller                                                           |

|      | 1st byte                       | Matching data (5AH)                                       | 9600 bps                                       | <ul> <li>– (Baud rate auto set)</li> </ul>                           |

|      | 2nd byte                       | -                                                         | 9600 bps                                       | OK: Echo back data (5AH)                                             |

|      |                                |                                                           |                                                | Error: Nothing transmitted                                           |

|      | 3rd byte                       | Baud rate modification data                               | 9600 bps                                       | -                                                                    |

|      |                                | (See Table 2.4.1)                                         |                                                |                                                                      |

|      | 4th byte                       | -                                                         | 9600 bps                                       | OK: Echo back data                                                   |

|      |                                |                                                           |                                                | Error:A1H $\times$ 3, A3H $\times$ 3, 62H $\times$ 3                 |

|      |                                |                                                           |                                                | (Note 1)                                                             |

|      | 5th byte                       | Operation command data (60H)                              | Changed new baud rate                          | -                                                                    |

|      | 6th byte                       | -                                                         | Changed new baud rate                          | OK: Echo back data (60H)                                             |

|      |                                |                                                           |                                                | Error: A1H $\times$ 3, A3H $\times$ 3, 63H $\times$ 3                |

|      |                                |                                                           |                                                | (Note 1)                                                             |

|      | 7th byte                       | Address 15 to 08 in which to                              | Changed new baud rate                          | -                                                                    |

|      | 8th byte                       | store Password count (Note 4)                             | Changed new baud rate                          | OK: Nothing transmitted                                              |

|      |                                |                                                           |                                                | Error: Nothing transmitted                                           |

|      | 9th byte                       | Address 07 to 00 in which to                              | Changed new baud rate                          | -                                                                    |

| воот | 10th byte                      | store Password count (Note 4)                             | Changed new baud rate                          | OK: Nothing transmitted                                              |

| ROM  |                                |                                                           |                                                | Error: Nothing transmitted                                           |

|      | 11th byte                      | Address 15 to 08 in which to                              | Changed new baud rate                          | -                                                                    |

|      | 12th byte                      | start Password comparison<br>(Note 4)                     | Changed new baud rate                          | OK: Nothing transmitted                                              |

|      |                                | · · · /                                                   |                                                | Error: Nothing transmitted                                           |

|      | 13th byte                      | Address 07 to 00 in which to<br>start Password comparison | Changed new baud rate<br>Changed new baud rate | -                                                                    |

|      | 14th byte                      | (Note 4)                                                  | Changed new badd rate                          | OK: Nothing transmitted                                              |

|      |                                | · · · ·                                                   |                                                | Error: Nothing transmitted                                           |

|      | 15th byte                      | Password string (Note 5)                                  | Changed new baud rate                          | -                                                                    |

|      | :                              |                                                           | Changed new baud rate                          |                                                                      |

|      | m'th byte                      | -                                                         |                                                | OK: Nothing transmitted                                              |

|      |                                |                                                           |                                                | Error: Nothing transmitted                                           |

|      | m'th + 1 byte                  | Extended Intel format (Binary)                            | Changed new baud rate                          | -                                                                    |

|      | :                              | (Note 2)                                                  |                                                |                                                                      |

|      | n'th – 2 byte<br>n'th – 1 byte | -                                                         | Changed new boud rate                          | OK: SUM (Lligh) (Note 2)                                             |

|      | n in – T byte                  | -                                                         | Changed new baud rate                          | OK: SUM (High) (Note 3)                                              |

|      | n'th byte                      | _                                                         | Changed new baud rate                          | Error: Nothing transmitted<br>OK: SUM (Low) (Note 3)                 |

|      | i i i byte                     |                                                           | Changed hew badd late                          |                                                                      |

| RAM  | _                              | The program jumps to the start ac                         | dress of RAM in which the fi                   | Error: Nothing transmitted<br>rst transferred data has been written. |

| Table 2.6.2 | RAM Loader | Mode Process |

|-------------|------------|--------------|

|-------------|------------|--------------|

Note 1: "xxH  $\times$  3" denotes that operation stops after sending 3 bytes of xxH. For details, refer to 2.8 "Error Code".

Note 2: Refer to 2.10 "Intel Hex Format (Binary)".

Note 3: Refer to 2.9 "Checksum (SUM)".

Note 4: Refer to 2.11 "Passwords".

- Note 5: If all data of vector area are "00H" or "FFH", the passwords comparison is not executed because the device is considered as blank product. However, it is necessary to specify the password count storage addresses and the password comparison start address even though it is a blank product. If a password error occurs, the UART function of TMP86FH46 stops without returning error code to the controller. Therefore, when a password error occurs, the TMP86FH46 should be reset by RESET pin input.

- Note 6: Do not send only end record after transferring of password string. If the TMP86FH46 receives the end record only after reception of password string, it does not operate correctly.

Description of RAM loader mode

- 1. The process of the 1st byte through the 4th byte are the same as flash memory writing mode.

- 2. The receive data in the 5th byte is the RAM loader command data (60H) to write the user's program to RAM.

- 3. When the 5th byte is one of the operation command data shown in Table 2.5.1, the device sends the echo back data which is the same as received operation command data (in this case, 60H). If the 5th byte data does not correspond to the operation command data, the device stops UART function after sending 3 bytes of operation command error code: (63H).

- 4. The process of the 7th byte through the m'th byte are the same as flash memory writing mode.

- 5. The receive data in the m'th + 1 through n'th 2byte are received as binary data in Intel Hex format. No received data are echoed back to the controller. The data which is not the start mark (3AH for ":") in Intel Hex format is ignored and does not send an error code to the controller until the device receives the start mark. After receiving the start mark, the device receives the data record, that consists of length of data, address, record type, writing data and checksum. After receiving the checksum of data record, the device waits the start mark data (3AH) again. The data of data record is written to specified RAM by the receiving data. Since after receiving an end record, the device starts to calculate the SUM, the controller should wait the SUM after sending the end record. If receive error or Intel Hex format error occurs, the UART function of TMP86FH46 stops without returning error code to the controller.

- 6. The n'th 1 and the n'th bytes are the SUM value that is sent to the controller in order of the upper byte and the lower byte. For details on how to calculate the SUM, refer to 2.9 "Checksum (SUM)". The SUM calculation is performed after detecting the end record, but the calculation is not executed when receive error or Intel Hex format error has occurred. The SUM is calculated by the data written to RAM, but the length of data, address, record type and checksum in Intel Hex format are not included in SUM.

- 7. The boot program jumps to the first address that is received as data in Intel Hex format after sending the SUM to the controller.

#### 2.6.3 Flash Memory Memory SUM Output Mode (Operation command: 90H)

Table 2.6.3 shows flash memory SUM output mode process.

| Table 2.6.3 | Flash Memory | Memory | SUM C | Dutput Process |

|-------------|--------------|--------|-------|----------------|

|-------------|--------------|--------|-------|----------------|

|      | Number of   | Transfer Data from            |                       | Transfer Data from                                    |

|------|-------------|-------------------------------|-----------------------|-------------------------------------------------------|

|      | Bytes       | External Controller to        | Baud Rate             | TMP86FH46 to External                                 |

|      | Transferred | TMP86FH46                     |                       | Controller                                            |

|      | 1st byte    | Matching data (5AH)           | 9600 bps              | <ul> <li>– (Baud rate auto set)</li> </ul>            |

|      | 2nd byte    | -                             | 9600 bps              | OK: Echo back data (5AH)                              |

|      |             |                               |                       | Error: Nothing transmitted                            |

|      | 3rd byte    | Baud rate modification data   | 9600 bps              | _                                                     |

|      |             | (See Table 2.4.1)             |                       |                                                       |

|      | 4th byte    | -                             | 9600 bps              | OK: Echo back data                                    |

|      |             |                               |                       | Error: A1H $\times$ 3, A3H $\times$ 3, 62H $\times$ 3 |

|      |             |                               |                       | (Note 1)                                              |

| BOOT | 5th byte    | Operation command data        | Changed new baud rate | -                                                     |

| ROM  | 6th byte    | (90H)                         | Changed new baud rate | OK: Echo back data (90H)                              |

|      |             | -                             |                       | Error: A1H $\times$ 3, A3H $\times$ 3, 63H $\times$ 3 |

|      |             |                               |                       | (Note 1)                                              |

|      | 7th byte    | -                             | Changed new baud rate | OK: SUM (High) (Note 2)                               |

|      |             |                               |                       | Error: Nothing transmitted                            |

|      | 8th byte    | -                             | Changed new baud rate | OK: SUM (Low) (Note 2)                                |

|      |             |                               |                       | Error: Nothing transmitted                            |

|      | 9th byte    | (Wait for the next operation) | Changed new baud rate | -                                                     |

|      |             | (Command data)                |                       |                                                       |

Note 1: "xxH  $\times$  3" denotes that operation stops after sending 3 bytes of xxH. For details, refer to 2.8 "Error Code".

Note 2: Refer to 2.9 "Checksum (SUM)"

Description of flash memory SUM output mode

- 1. The process of the 1st byte through the 4th byte are the same as flash memory writing mode.

- 2. The receive data in the 5th byte is the flash memory SUM command data (90H) to calculate the entire flash memory.

- 3. When the 5th byte is one of the operation command data shown in Table 2.5.1, the device sends the echo back data which is the same as received operation command data (in this case, 90H). If the 5th byte data does not correspond to the operation command data, the device stops UART function after sending 3 bytes of operation command error code: (63H).

- 4. The 7th and the 8th bytes are the SUM value that is sent to the controller in order of the upper byte and the lower byte. For details on how to calculate the SUM, refer to 2.9 "Checksum (SUM)".

- 5. After sending the SUM, the device waits for the next operation command data.

#### 2.6.4 Product Discrimination Code Output Mode (Operation command: C0H)

Table 2.6.4 shows product discrimination code output mode process.

|      | Number of   | Transfer Data from                              |                                          |        | Transfer Data from                             |

|------|-------------|-------------------------------------------------|------------------------------------------|--------|------------------------------------------------|

|      |             |                                                 |                                          |        |                                                |

|      | Bytes       | External Controller to                          | Baud Rate                                | IIV    | IP86FH46 to External                           |

|      | Transferred | TMP86FH46                                       |                                          |        | Controller                                     |

|      | 1st byte    | Matching data (5AH)                             | 9600 bps                                 | – (Bau | ud rate auto set)                              |

|      | 2nd byte    | _                                               | 9600 bps                                 | OK: E  | cho back data (5AH)                            |

|      | -           |                                                 | -                                        | Error: | Nothing transmitted                            |

|      | 3rd byte    | Baud rate modification data                     | 9600 bps                                 | -      |                                                |

|      |             | (See Table 2.4.1)                               | -                                        |        |                                                |

|      | 4th byte    |                                                 | 9600 bps                                 | OK: E  | cho back data                                  |

|      | ,           |                                                 |                                          | Error: | A1H $\times$ 3, A3H $\times$ 3, 62H $\times$ 3 |

|      |             |                                                 |                                          | (Note  |                                                |

|      | 5th byte    | Operation command data                          | Changed new baud rate                    | -      |                                                |

|      | 6th byte    | (C0H)                                           | Changed new baud rate                    | OK: E  | cho back data (C0H)                            |

|      | 0112910     | _                                               | enangea nen baaa rate                    |        | A1H $\times$ 3, A3H $\times$ 3, 63H $\times$ 3 |

|      |             |                                                 |                                          | (Note  |                                                |

|      | 7th byte    |                                                 | Changed new baud rate                    | 3AH    | Start mark                                     |

|      | 8th byte    |                                                 | Changed new baud rate                    | 0AH    | The number of transfer                         |

|      |             |                                                 |                                          | -      | data (from 9th to 18th byte)                   |

|      | 9th byte    |                                                 | Changed new baud rate                    | 02H    | Length of address (2 bytes)                    |

| BOOT | 10th byte   |                                                 | Changed new baud rate                    | 03H    | Reserved data                                  |

| ROM  | 11th byte   |                                                 | Changed new baud rate                    | 00H    | Reserved data                                  |

|      | 12th byte   |                                                 | Changed new baud rate                    | 00H    | Reserved data                                  |

|      | 13th byte   |                                                 | Changed new baud rate                    | 00H    | Reserved data                                  |

|      | 14th byte   |                                                 | Changed new baud rate                    | 01H    | The number of ROM block                        |

|      |             |                                                 |                                          |        | (1 block)                                      |

|      | 15th byte   |                                                 | Changed new baud rate                    | COH    | First address of ROM                           |

|      |             |                                                 |                                          |        | (Upper 8 bits)                                 |

|      | 16th byte   |                                                 | Changed new baud rate                    | 00H    | First address of ROM                           |

|      |             |                                                 |                                          |        | (Lower 8 bits)                                 |

|      | 17th byte   |                                                 | Changed new baud rate                    | FFH    | End address of ROM                             |

|      | 1011        |                                                 |                                          |        | (Upper 8 bits)                                 |

|      | 18th byte   |                                                 | Changed new baud rate                    | FFH    | End address of ROM                             |

|      | 10th histo  |                                                 | Observation and the second second second | 2011   | (Lower 8 bits)                                 |

|      | 19th byte   |                                                 | Changed new baud rate                    | 3CH    | Checksum of transferred                        |

|      | 20th byte   | (Moit for the poyt operation)                   | Changed new baud rate                    |        | data (from 9th to 18th byte)                   |

|      | ∠utn byte   | (Wait for the next operation)<br>(Command data) | Changed new baud rate                    | -      |                                                |

|      |             |                                                 |                                          |        |                                                |

| Table 2.6.4 | Product | Discrimination | Code | Output Process |

|-------------|---------|----------------|------|----------------|

|-------------|---------|----------------|------|----------------|

Note: "xxH  $\times$  3" denotes that operation stops after sending 3 bytes of xxH. For details, refer to 2.8 "Error Code".

Description of product discrimination code output mode

- 1. The process of the 1st byte through the 4th byte are the same as flash memory writing mode.

- 2. The receive data in the 5th byte is the product discrimination code output command data (C0H).

- 3. When the 5th byte is one of the operation command data shown in Table 2.5.1, the device sends the echo back data which is the same as received operation command data (in this case, C0H). If the 5th byte data does not correspond to the operation command data, the device stops UART function after sending 3 bytes of operation command error code: (63H).

- 4. The 9th and the 19th bytes are the product discrimination code. For details, refer to 2.12 "Product Discrimination Code".

- 5. After sending the SUM, the device waits for the next operation command data.

### 2.7 Flash Memory Writing Data Format

Flash memory area of TMP86FH46 consists of 512 pages and one page size is 32 bytes. Writing to flash memory is executed by page writing. Therefore, it is necessary to send 32 bytes data (for one page) even though only a few bytes data are written. Figure 2.7.1 shows an organization of flash memory area. When the controller sends the writing data to the device, be sure to keep the format described below.

- 1. The address of data after receiving the flash memory writing command should be the first address of page. For example, in case of page 2, the first address should be C040H.

- 2. If the last data's address of data record is not end address of page, the address of the next data record should be the address + 1 and the last data's address must point to the last address of this page. For example, if the last data's address is COOFH (Page0), the address of the next data record should be CO10H (Page0) and the address of the last data should be CO1FH (Page0).

- 3. The last data's address of data record immediately before sending the end record should be the last address of page. For example, in case of page 1, the last data's address of data record should be C03FH.

| Address    | 0 | 1 | 2 | 3           | 4 | 5 | 6 | 7    | 8    | 9          | А | В | С                  | D | Е           | F        |

|------------|---|---|---|-------------|---|---|---|------|------|------------|---|---|--------------------|---|-------------|----------|

| C000H      | F |   |   | ,<br>,<br>, |   |   |   | Do(  | 100  | <br> <br>  |   |   | ,<br>,<br><b>,</b> |   | ,<br>,<br>, |          |

| C010H      |   |   |   | l<br>l      |   |   |   | Paç  | jeu  | 1          |   |   | 1                  |   | 1           | Е        |

| C020H      | F |   |   |             |   |   |   | Dea  |      |            |   |   |                    |   |             |          |

| C030H      |   |   |   | 1           |   |   |   | Paç  | jen  | 1          |   |   | i<br>I             |   | <br>        | Е        |

| C040H      | F |   |   | ;<br>;<br>+ |   |   |   | Pag  | 201  |            |   |   | ,<br>,<br>+        |   | ¦<br>+      |          |

| C050H      |   |   |   | !           |   |   |   | Γαί  | jez  |            |   |   | <br>               |   | <br>        | Е        |

| C060H      | F |   |   |             |   |   |   | Pag  | ne3  |            |   |   | ;<br>+             |   |             |          |

| C070H      |   |   |   | !           |   |   |   | 1 4  | ,00  |            |   |   | <br>               |   |             | E        |

| C080H      | F |   |   |             |   |   |   | Pag  | ne4  |            |   |   | ;<br>              |   | ¦           |          |

| C090H      |   |   |   | !           |   |   |   |      | ,- · | !          |   |   | !                  |   | !<br>       | E        |

| C0A0H      | F |   |   |             |   |   |   | Pag  | ae5  |            |   |   | <br>               |   |             |          |

| C0B0H      |   |   |   | i<br>       |   |   |   |      |      |            |   |   | i<br>              |   |             | E        |

| C0C0H      | F |   |   | <br>        |   |   |   |      |      | ¦<br>      |   |   | <br>               |   | <br>        |          |

| :          |   |   |   |             |   |   |   |      |      |            |   |   |                    |   |             | <b>I</b> |

| :<br>FF70H |   |   |   |             |   |   |   |      |      | +          |   |   | <br>               |   | <br> <br>   | Е        |

| FF80H      | F |   |   | l           |   |   |   |      |      | i          |   |   | i                  |   | 1           |          |

| FF90H      | · |   |   |             |   |   |   | Page | e508 |            |   |   | +<br>+             |   | +           | E        |

| FFA0H      | F |   |   | I           |   |   |   |      |      | !          |   |   | I                  |   |             |          |

| FFB0H      |   |   |   | +<br>1      |   |   |   | Page | e509 |            |   |   | +<br>1             |   | +           | Е        |

| FFC0H      | F |   |   | !           |   |   |   |      |      | l          |   |   | !                  |   |             |          |

| FFD0H      | · |   |   | +<br>,      |   |   |   | Page | e510 | L<br> <br> |   |   | L                  |   | ¦           | Е        |

| FFE0H      | F |   |   | !           |   |   |   | _    |      | !          |   |   | 1                  |   |             |          |

| FFF0H      |   |   |   | <br>1<br>1  |   |   |   | Page | e511 | <br> <br>  |   |   | <br>1<br>1         |   | <br> <br>   | Е        |

Note: Do not write only the vector area (FFF0H to FFFFH) when all data of flash memory are the same data. If the vector area is only written, the next operation can not be executed because of password error.

Note: "F" shows the first address of each page and "E" shows the last address of each page.

Figure 2.7.1 Organization of Flash Memory Area

### 2.8 Error Code

When the device detects an error, the error codes are sent to the controller.

| Table 2.8.1 Error Code |

|------------------------|

|                        |

| Transmi  | t Data     | Meaning of Transmit Data                 |

|----------|------------|------------------------------------------|

| 62H, 62H | I, 62H E   | Baud rate modification error occurred.   |

| 63H, 63H | I, 63H (   | Operating command error occurred.        |

| A1H, A1F | I, A1H F   | Framing error in received data occurred. |

| A3H, A3H | I, A3H 🛛 🔾 | Overrun error in received data occurred. |

### 2.9 Checksum (SUM)

#### (1) Calculation method

SUM consists of byte + byte.... + byte, the checksum of which is returned in word as the result.

Namely, data is read out in byte and checksum of which is calculated, with the result returned in word.

Example:

|     | If the data to be calcul | ated consists of the four bytes shown to the |

|-----|--------------------------|----------------------------------------------|

| A1H | left, SUM of the data is |                                              |

| B2H | A1H + B2H + C3H +        | -D4H = 02EAH                                 |

| C3H | SUM (HIGH)               | = 02H                                        |

| D4H | SUM (LOW)                | = EAH                                        |

|     |                          |                                              |

The SUM returned when executing the flash memory write command, RAM loader command, or flash memory SUM command is calculated in the manner shown above.

#### (2) Calculation data

The data from which SUM is calculated are listed in Table 2.9.1 below.

| Operating Mode                               | Calculation Data                                     | Remarks                                                                                                              |

|----------------------------------------------|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| Flash memory writing mode                    | Data in the entire area (16 Kbytes) of flash         | Even when written to part of the flash memory area, data in the entire memory area (16 Kbytes) is                    |

| Flash memory Checksum output mode            | ( ) )                                                | calculated.<br>The length of data, address, record type and<br>checksum in Intel Hex format are not included in SUM. |

| RAM loader mode                              | Data written to RAM                                  | The length of data, address, record type and checksum in Intel Hex format are not included in SUM.                   |

| Product discrimination code out-<br>put mode | Checksum of transferred data (from 9th to 18th byte) | For details, refer to "2.6.4 Product Discrimination Code Output Mode".                                               |

| Table 2.9.1 | Checksum  | Calculation | Data |

|-------------|-----------|-------------|------|

| 10010 21011 | Onoonoann | ouroundion  | Duia |

#### 2.10 Intel Hex Format (Binary)

- 1. After receiving the SUM of a record, the device waits for the start mark data (3AH for ":") of the next record. Therefore, the device ignores the data, which does not match the start mark data after receiving the SUM of a record.

- 2. Make sure that once the controller program has finished sending the SUM of the end record, it does not send anything and waits for two bytes of data to be received (Upper and lower bytes of SUM). This is because after receiving the SUM of the end record, the boot program calculates the SUM and returns the calculated SUM in two bytes to the controller.

- 3. If a receive error or Intel Hex format error occurs, the UART function of TMP86FH46 stops without returning error code to the controller. In the following cases, an Intel Hex format error occurs:

- When the record type is not 00H, 01H, or 02H

- When a SUM error occurred

- When the data length of an extended record (Type = 02H) is not 02H

- When the address of an extended record (Type = 02H) is larger than 1000H and after that, receives the data record

- When the data length of the end record (Type = 01H) is not 00H

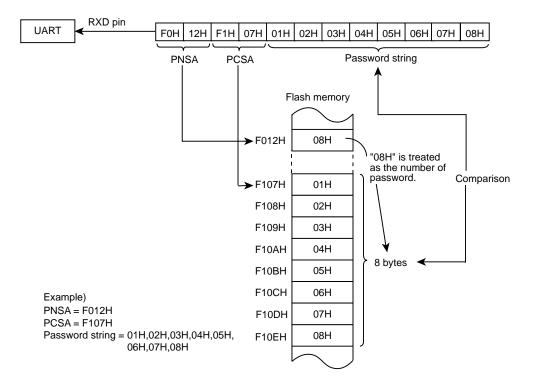

#### 2.11 Passwords

The area in which passwords can be specified is located at addresses C000H to FF9FH. The vector area (from FFA0H to FFFFH) can not be specified as passwords area. The device compares the stored passwords with the passwords, which are received from the controller. If all data of vector area are "00H" or "FFH", the passwords comparison is not executed because the device is considered as blank product. It is necessary to specify the password count storage addresses and the password comparison start address even though it is a blank product.

| Password                                    | Blank Product(Note 1)                             | Non Blank Product           |

|---------------------------------------------|---------------------------------------------------|-----------------------------|

| PNSA<br>(Password count storage addresses)  | $C000H \le PNSA \le FF9FH$                        | $C000H \le PNSA \le FF9FH$  |

| PCSA<br>(Password comparison start address) | $\text{C000H} \leq \text{PCSA} \leq \text{FF9FH}$ | $C000H \le PCSA \le FFA0-N$ |

| N<br>(Password count)                       | *                                                 | $8 \le N$                   |

| Setting of password                         | No need                                           | Need (Note 2)               |

Table 2.11.1 Password Setting in the Blank Product and Non Blank Product

Note 1: When all data of addresses from FFE0H to FFFFH area are "00H" or "FFH", the device is judged as blank product.

Note 2: The same three or more bytes consecutive data can not be used as password.

- When the password includes the same consecutive data (three or more bytes), the password error occurs. If the password error occured, the UART function of device stops without returning error code.

- Note 3: \*: Don't care.

- Note 4: When the password doesn't match the above condition, the password error occurs. If the password error occured, the UART function of device stops without returning error code.

- Note 5: In case of the blank product, the device receives Intel Hex Format immediately after receiving PCSA without receiving password strings. In this time, because the device ignores the data

except the start mark data (3AH for ":") as Intel Hex Format data, even if external controller transmitted dummy password strings, process operates correctly. However, if the dummy password strings contain data "3AH", the device detects it as start mark data mistakenly, and device stops process without returning error doce. Therefore, if these process becomes issue, the external controller should not transmit the dummy password strings.

Figure 2.11.1 Password Comparison Example

#### 3. Password string

A password string sent from the controller is compared with the specified data in the flash memory. If the password string does not match the specified data in the flash memory, a password error occurs and the TMP86FH46 stops operating.

4. Handling of password error

If a password error occurs, the UART function of TMP86FH46 stops without returning error code to the controller. Therefore, when a password error occurs, the TMP86FH46 should be reset by **RESET** pin input.

### 2.12 Product Discrimination Code

The product discrimination code is a 13-byte data, that includes the start address and the end address of ROM. Table 2.12.1 shows the product discrimination code format.

| Data | The Meaning of Data                                  | In Case of TMP86FH46         |

|------|------------------------------------------------------|------------------------------|

| Data |                                                      |                              |

| 1st  | Start mark (3AH)                                     | 3AH                          |

| 2nd  | The number of transfer data (from 3rd to 13th byte)  | 0AH                          |

| 3rd  | Length of address                                    | 02H                          |

| 4th  | Reserved data                                        | 03H                          |

| 5th  | Reserved data                                        | 00H                          |

| 6th  | Reserved data                                        | 00H                          |

| 7th  | Reserved data                                        | 00H                          |

| 8th  | The number of ROM block                              | 01H                          |

| 9th  | The upper byte of the first address of ROM           | C0H (Depends on the product) |

| 10th | The lower byte of the first address of ROM           | 00H (Depends on the product) |

| 11th | The upper byte of the end address of ROM             | FFH (Depends on the product) |

| 12th | The lower byte of the end address of ROM             | FFH (Depends on the product) |

| 13th | Checksum of transferred data (from 3rd to 12th byte) | 3CH (Depends on the product) |

Table 2.12.1 Product Discrimination Code Format

### 2.13 Flowchart

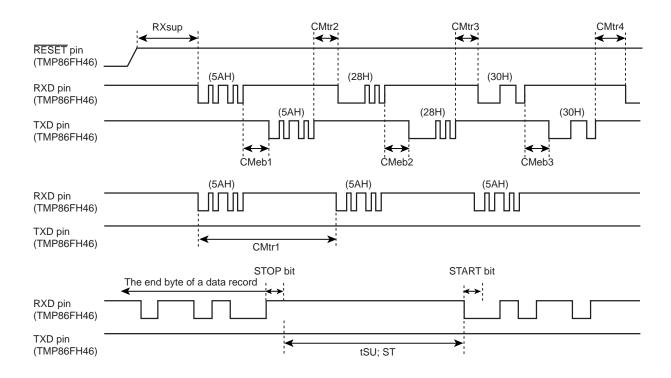

### 2.14 UART Timing

Table 2.14.1 UART Timing-1 (VDD = 4.5 V to 5.5 V, fc = 2 MHz, 4 MHz, 8 MHz, 16 MHz, Topr = 20 to 30°C)

|                                                                                           |        | The Number of      | Required Minimum Time |                   |  |

|-------------------------------------------------------------------------------------------|--------|--------------------|-----------------------|-------------------|--|

| Parameter                                                                                 | Symbol | Clock (fc)         | At fc = 2 MHz         | At fc = 16<br>MHz |  |

| Time from the reception of a matching data until the output of an echo back               | CMeb1  | Approx. 600        | 300 μs                | 37.5 μs           |  |

| Time from the reception of a baud rate modification data until the output of an echo back | CMeb2  | Approx. 500        | 250 μs                | 31.3 μs           |  |

| Time from the reception of an operation command until the output of an echo back          | CMeb3  | Approx. 500        | 250 μs                | 31.3 μs           |  |

| Calculation time of checksum                                                              | CKsm   | Approx.<br>1573000 | 786.5 ms              | 98.3 ms           |  |

#### Table 2.14.2 UART Timing-2 (VDD = 4.5 V to 5.5 V, fc = 2 MHz, 4 MHz, 8 MHz, 16 MHz, Topr = 20 to 30°C)

|                                                                  |          | The        | Required Minimum Time |              |  |

|------------------------------------------------------------------|----------|------------|-----------------------|--------------|--|

| Parameter                                                        | Symbol   | Number of  | At fc = 2 MHz         | At $fc = 16$ |  |

|                                                                  |          | Clock (fc) |                       | MHz          |  |

| Time from reset release until acceptance of start bit of RXD pin | RXsup    | 25000      | 12.5 ms               | 1.56 ms      |  |

| Time between a matching data and the next matching data          | CMtr1    | 28500      | 14.3 ms               | 1.8 ms       |  |

| Time from the echo back of matching data until the acceptance    | CMtr2    | 400        | 200 μs                | 25 μs        |  |

| of baud rate modification data                                   | OMITZ    | 400        | 200 μ3                | 25 μ5        |  |

| Time from the output of echo back of baud rate modification      | CMtr3    | 500        | 250 μs                | 31.3 μs      |  |

| data until the acceptance of an operation command                | OMUS     | 500        | 200 μ3                | 51.5 μ3      |  |

| Time from the output of echo back of operation command until     | CMtr4    | 2600       | 1.3 ms                | 163 μs       |  |

| the acceptance of Password count storage addresses               | Civili 4 | 2000       | 1.0 110               | 100 μο       |  |

#### Table 2.14.3 UART Timing-3 (VDD = 4.5 V to 5.5 V, fc = 2 MHz, 4 MHz, 8 MHz, 16 MHz, Topr = 20 to 30°C)

| Parameter                                                                               | Symbol  | Min. | Max. | Unit |

|-----------------------------------------------------------------------------------------|---------|------|------|------|

| Time from the stop bit of the previous data record to start bit of the next data record | tSU; ST | 1    | -    | ms   |

## **Electrical Characteristics**

| Absolute Maximum Ratings | $(V_{SS} = 0 V)$ |

|--------------------------|------------------|

|--------------------------|------------------|

| Parameter                       | Symbol                            | Pins             | Rating                        | Unit |

|---------------------------------|-----------------------------------|------------------|-------------------------------|------|

| Supply voltage                  | V <sub>DD</sub>                   |                  | -0.3 to 5.5                   |      |

| Input voltage                   | V <sub>IN</sub>                   |                  | -0.3 to V <sub>DD</sub> + 0.3 | V    |

| Output voltage                  | V <sub>OUT</sub>                  |                  | -0.3 to V <sub>DD</sub> + 0.3 |      |

|                                 | I <sub>OUT1</sub> I <sub>OH</sub> | P1, P3, P4 ports | -1.8                          |      |

| Output current (Per 1 pin)      | I <sub>OUT2</sub> I <sub>OL</sub> | P1, P3 ports     | 3.2                           | l    |