## Preface

Thank you very much for making use of Toshiba microcomputer LSIs. Before use this LSI, refer the section, "Points of Note and Restrictions". Especially, take care below cautions.

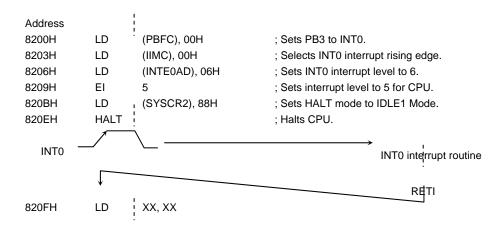

## \*\*CAUTION\*\* How to release the HALT mode

Usually, interrupts can release all halts status. However, the interrupts = (INT0 to INT3, INTRTC, INTALM0 to INTALM4, INTKEY), which can release the HALT mode may not be able to do so if they are input during the period CPU is shifting to the HALT mode (for about 5 clocks of  $f_{FPH}$ ) with IDLE1 or STOP mode (IDLE2 is not applicable to this case). (In this case, an interrupt request is kept on hold internally.)

If another interrupt is generated after it has shifted to HALT mode completely, halt status can be released without difficultly. The priority of this interrupt is compare with that of the interrupt kept on hold internally, and the interrupt with higher priority is handled first followed by the other interrupt.

# CMOS 16-Bit Microcontrollers TMP91C025FG/JTMP91C025-S

## 1. Outline and Features

TMP91C025 is a high-speed 16-bit microcontroller designed for the control of various mid- to large-scale equipment.

TMP91C025FG comes in a 100-pin flat package. JTMP91C025-S comes in a 100-pad chip.

Listed below are the features.

- (1) High-speed 16-bit CPU (900/L1 CPU)

- Instruction mnemonics are upward-compatible with TLCS-90

- 16 Mbytes of linear address space

- General-purpose registers and register banks

- 16-bit multiplication and division instructions; bit transfer and arithmetic instructions

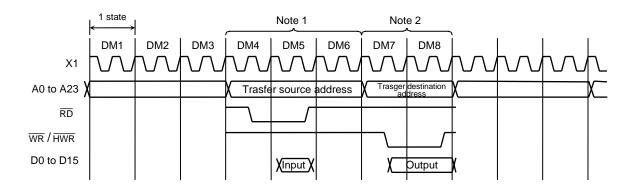

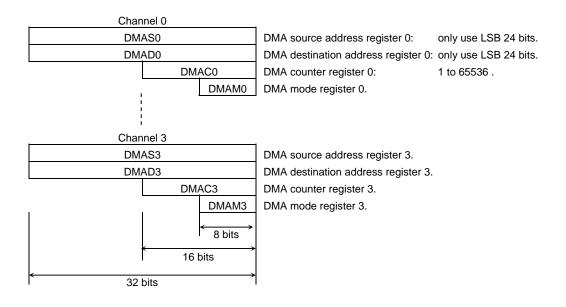

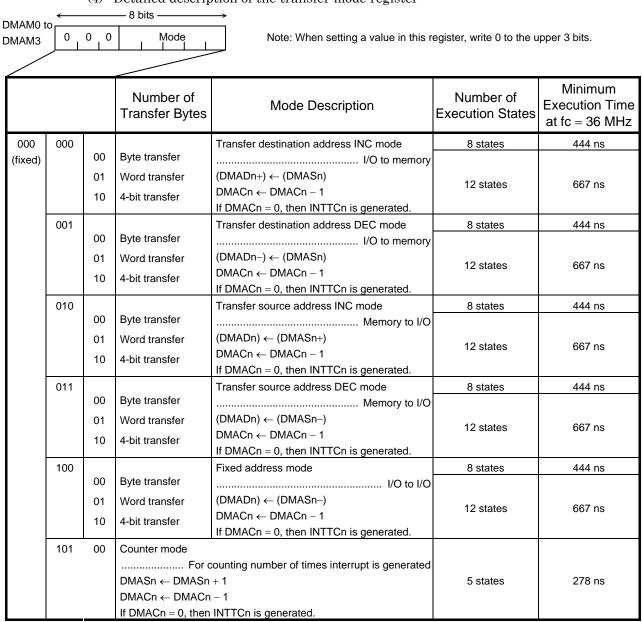

- Micro DMA: 4 channels (444 ns/ 2 bytes at 36 MHz)

- (2) Minimum instruction execution time: 111 ns (at 36 MHz)

#### **RESTRICTIONS ON PRODUCT USE**

070208EBP

- The information contained herein is subject to change without notice. 021023\_D

- TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor

devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical

stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety

in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such

TOSHIBA products could cause loss of human life, bodily injury or damage to property.

In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc. 021023\_A

- The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer's own risk. 021023\_B

- The products described in this document shall not be used or embedded to any downstream products of which manufacture, use and/or sale are prohibited under any applicable laws and regulations. 060106\_Q

- The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any patents or other rights of TOSHIBA or the third parties. 021023\_C

- The products described in this document are subject to foreign exchange and foreign trade control laws. 060925\_E

- For a discussion of how the reliability of microcontrollers can be predicted, please refer to Section 1.3 of the chapter entitled Quality and Reliability Assurance/Handling Precautions. 030619\_S

- (3) Built-in RAM: None Built-in ROM: None

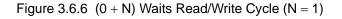

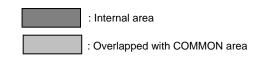

- (4) External memory expansion

- Expandable up to 104 Mbytes (Shared program/data area)

- Can simultaneously support 8-/16-bit width external data bus ... Dynamic data bus sizing

- Separate bus system

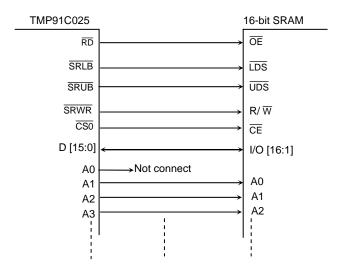

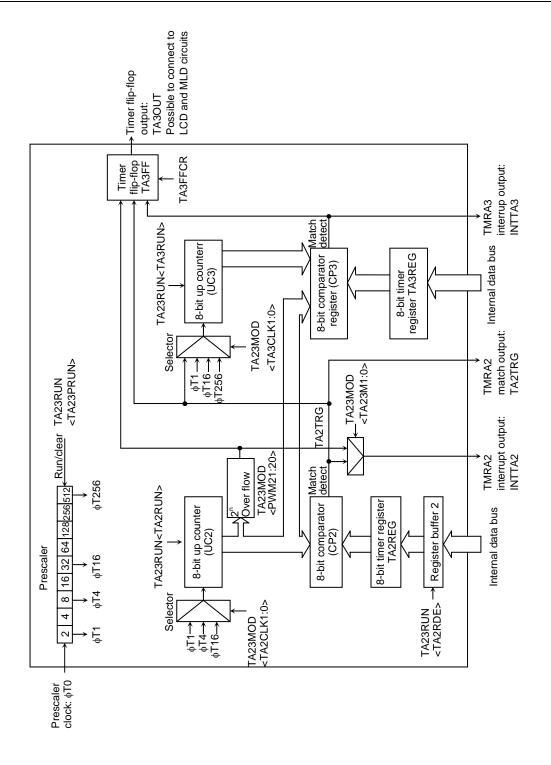

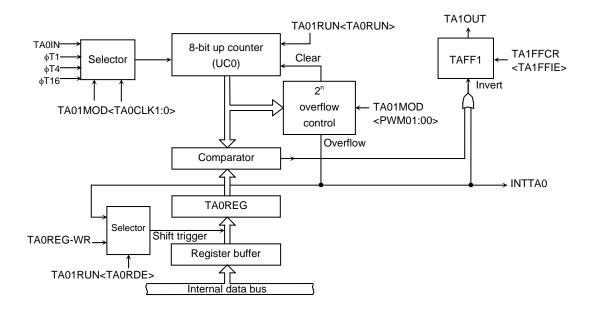

- (5) 8-bit timers: 4 channels

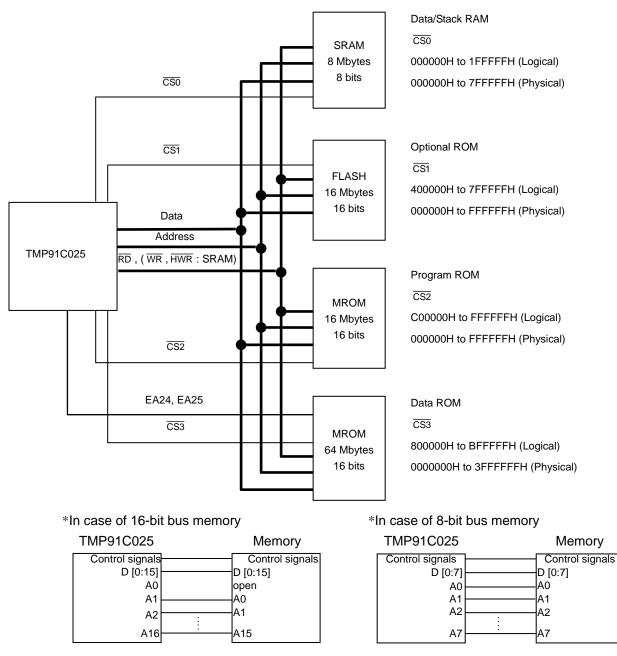

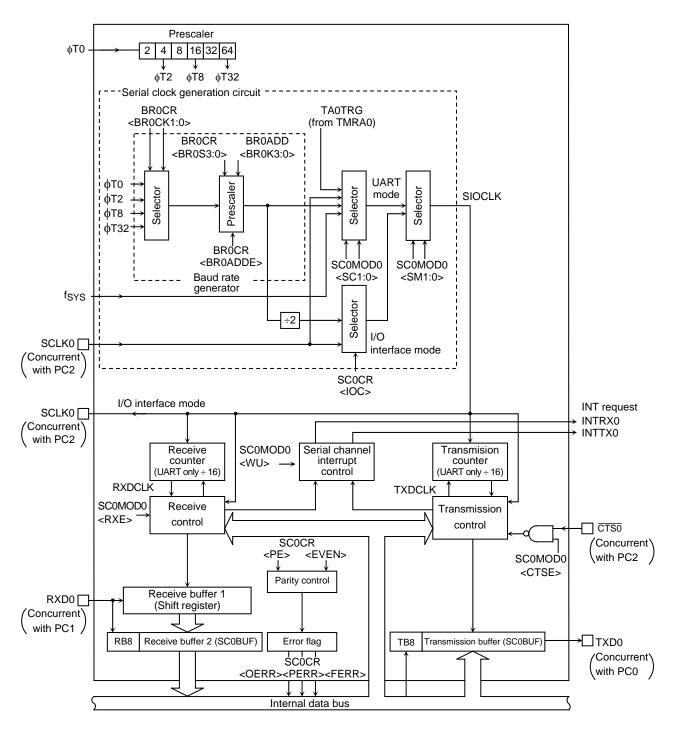

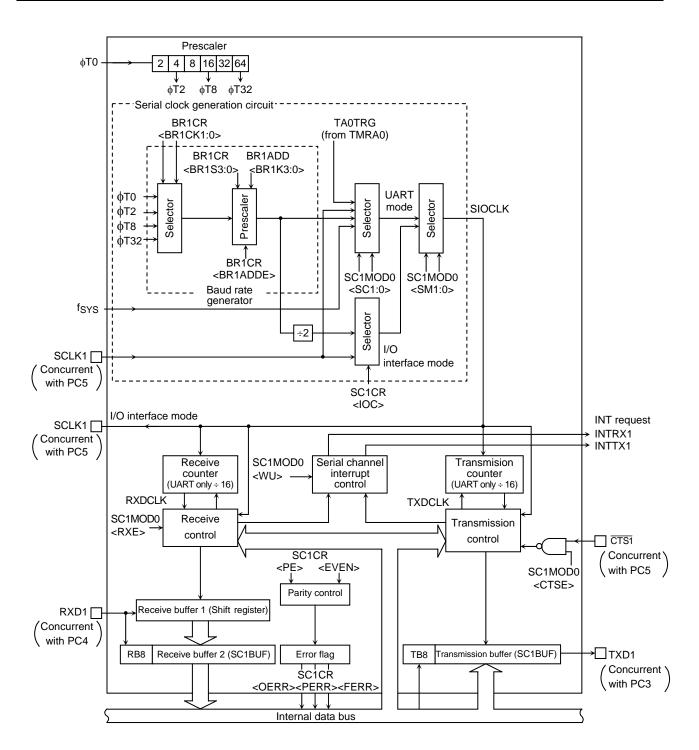

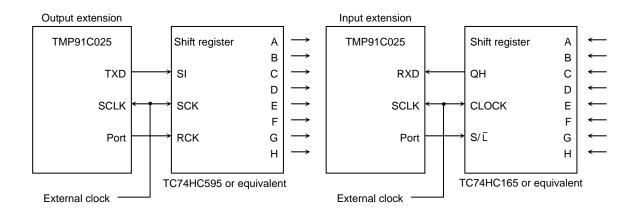

- (6) General-purpose serial interface: 2 channels

- UART/Synchronous mode: 2 channels

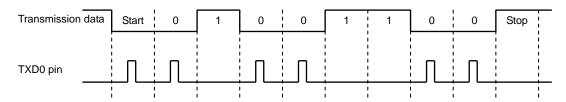

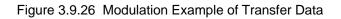

- IrDA Ver.1.0 (115.2 kbps) mode selectable: 1 channel

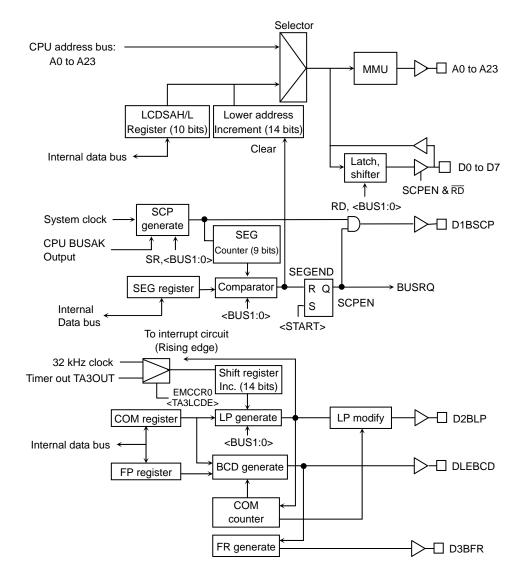

- (7) LCD controller

- Adapt to both shift register type and built-in RAM type LCD driver

- (8) Timer for real-time clock (RTC)

- Based on TC8521A

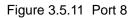

- (9) Key-on wakeup (Interrupt key input)

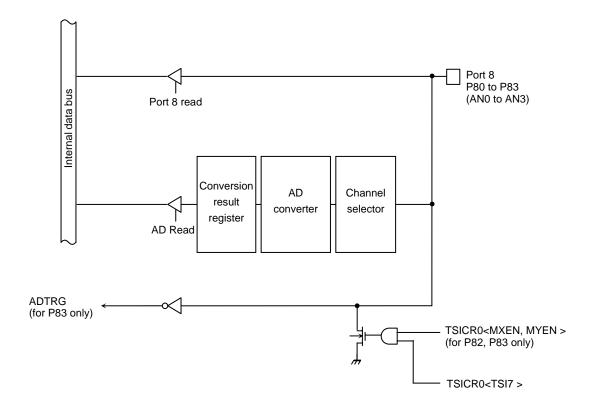

- (10) 10-bit AD converter: 4 channels

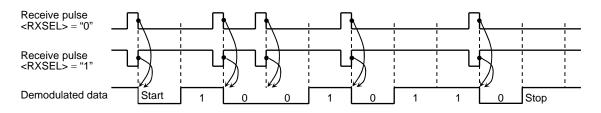

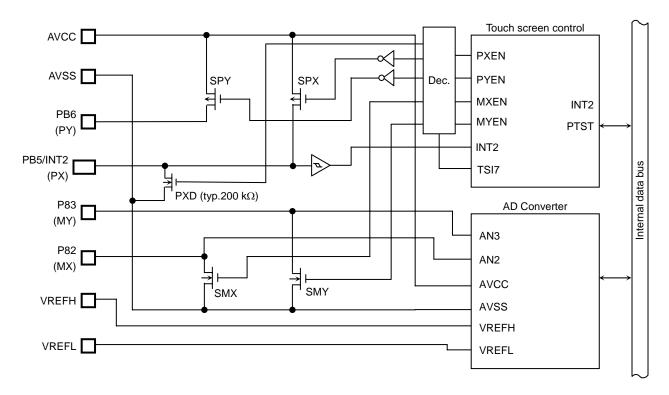

- (11) Touch screen interface

- Available to reduce external components

- (12) Watchdog timer

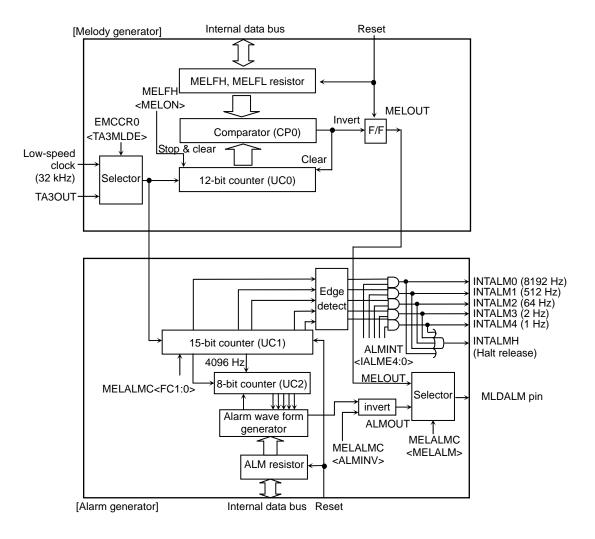

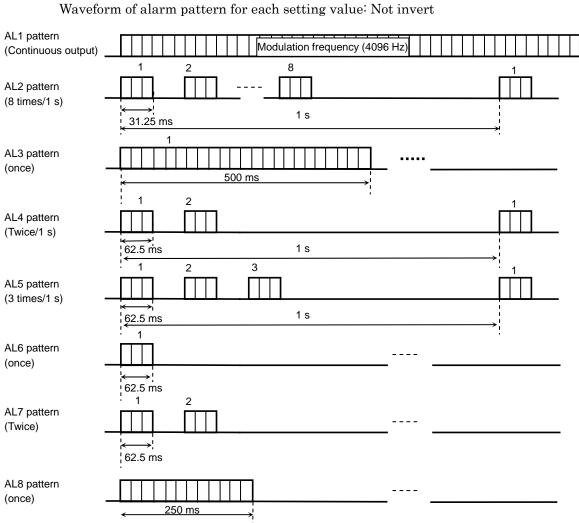

- (13) Melody/alarm generator

- Melody: Output of clock 4 to 5461 Hz

- Alarm: Output of the 8 kinds of alarm pattern

- Output of the 5 kinds of interval interrupt

(14) Chip select/wait controller: 4 channels

(15) MMU

• Expandable up to 104 Mbytes

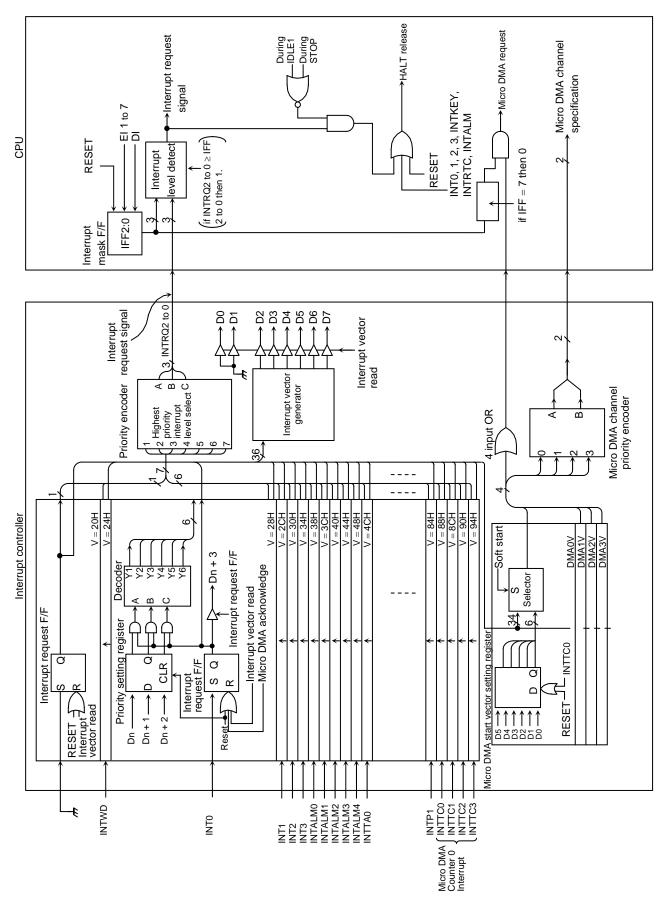

(16) Interrupts: 37 interrupt

- 9 CPU interrupts: Software interrupt instruction and illegal instruction

- 23 internal interrupts: 7 priority levels are selectable

- 5 external interrupts: 7 priority levels are selectable (among 4 interrupts are selectable edge mode)

(17) Input/output ports: 49 pins (Except Data bus (8bit), Address bus (24bit) and RD pin)

(18) Standby function

Three HALT modes: IDLE2 (Programmable), IDLE1 and STOP

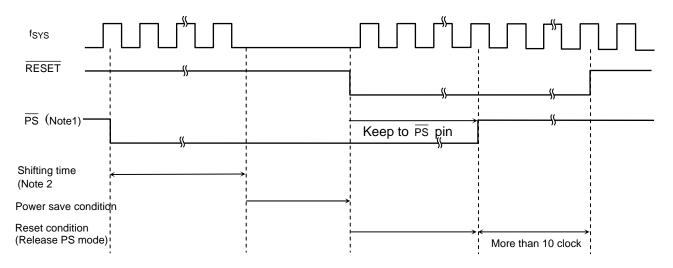

(19) Hardware standby function (Power save function)

(20) Triple-clock controller

- Clock doubler (DFM) circuit is inside

- Clock gear function: Select a high-frequency clock fc/1 to fc/16

- SLOW mode (fs = 32.768 kHz)

(21) Operating voltage

- V<sub>CC</sub> = 3.0 V to 3.6 V (fc max = 36 MHz)

- $V_{CC} = 2.7 \text{ V to } 3.6 \text{ V (fc max} = 27 \text{ MHz})$

- V<sub>CC</sub> = 2.4 V to 3.6 V (fc max = 16 MHz)

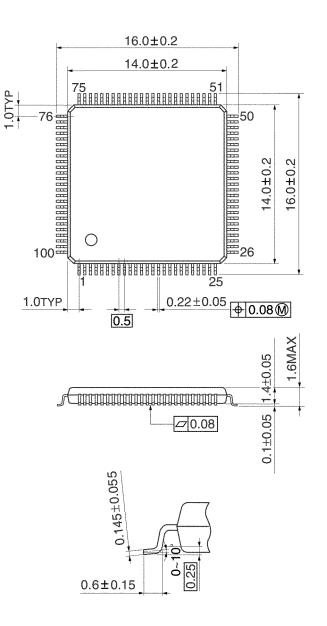

(22) Package

• 100-pin QFP: P-LQFP100-1414-0.50F, chip form supply also available. For details, contact your local Toshiba sales representative.

## TOSHIBA

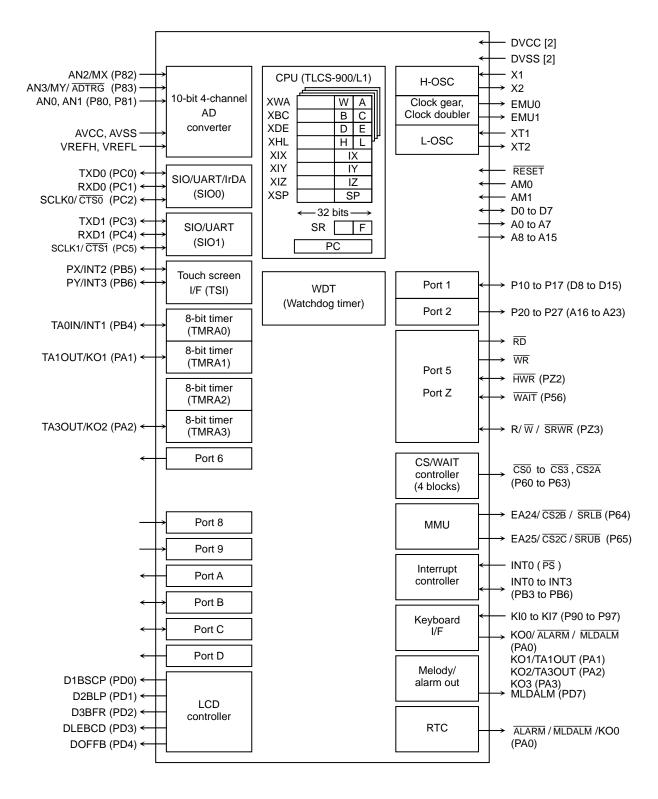

( ): Initial function after reset

Figure 1.1 TMP91C025 Block Diagram

## TOSHIBA

## 2. Pin Assignment and Pin Functions

The assignment of input/output pins for the TMP91C025, their names and functions are as follows:

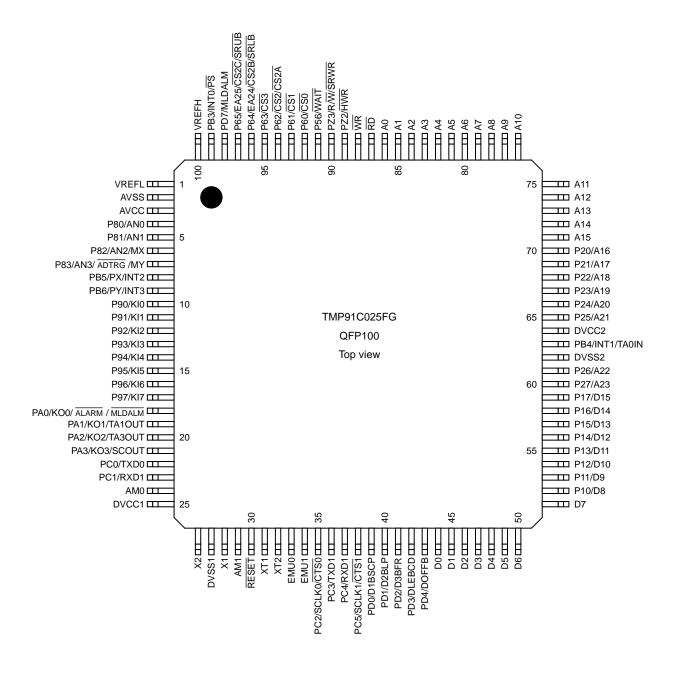

## 2.1 Pin Assignment Diagram

Figure 2.1.1 shows the pin assignment of the TMP91C025FG.

Figure 2.1.1 Pin Assignment Diagram (100-pin QFP)

| 2.2        | PAD La      | yout       |                |            |          |             |              |            |       |            |              |

|------------|-------------|------------|----------------|------------|----------|-------------|--------------|------------|-------|------------|--------------|

|            | (Chip size  | e 4.58 m   | m 	imes 4.6    | 3 mm)      |          |             |              |            |       |            | Unit (µm)    |

| Pin<br>No. | Name        | X<br>Point | Y<br>Point     | Pin<br>No. | Name     | X<br>Point  | Y<br>Point   | Pin<br>No. | Name  | X<br>Point | Y<br>Point   |

| 1          | VREFL       | -2151      | 1627           | 44         | D0       | 852         | -2175        | 87         | RD    | 210        | 2175         |

| 2          | AVSS        | -2151      | 1502           | 45         | D1       | 977         | -2175        | 88         | WR    | 83         | 2175         |

| 3          | AVCC        | -2151      | 1376           | 46         | D2       | 1103        | -2175        | 89         | PZ2   | -42        | 2175         |

| 4          | P80         | -2151      | 1251           | 47         | D3       | 1228        | -2175        | 90         | PZ3   | -169       | 2175         |

| 5          | P81         | -2151      | 1126           | 48         | D4       | 1353        | -2175        | 91         | P56   | -296       | 2175         |

| 6          | P82         | -2151      | 1001           | 49         | D5       | 1478        | -2175        | 92         | P60   | -421       | 2175         |

| 7          | P83         | -2151      | 876            | 50         | D6       | 1603        | -2175        | 93         | P61   | -548       | 2175         |

| 8          | PB5         | -2151      | 751            | 51         | D7       | 2151        | -1636        | 94         | P62   | -674       | 2175         |

| 9          | PB6         | -2151      | 625            | 52         | P10      | 2151        | -1490        | 95         | P63   | -801       | 2175         |

| 10         | P90         | -2151      | 336            | 53         | P11      | 2151        | -1359        | 96         | P64   | -926       | 2175         |

| 11         | P91         | -2151      | 211            | 54         | P12      | 2151        | -1228        | 97         | P65   | -1051      | 2175         |

| 12         | P92         | -2151      | 86             | 55         | P13      | 2151        | -1096        | 98         | PD7   | -1177      | 2175         |

| 13         | P93         | -2151      | -38            | 56         | P14      | 2151        | -965         | 99         | PB3   | -1302      | 2175         |

| 14         | P94         | -2151      | -163           | 57         | P15      | 2151        | -834         | 100        | VREFH | -1606      | 2175         |

| 15         | P95         | -2151      | -289           | 58         | P16      | 2151        | -703         |            |       |            |              |

| 16         | P96         | -2151      | -414           | 59         | P17      | 2151        | -571         |            |       |            |              |

| 17         | P97         | -2151      | -539           | 60         | P27      | 2151        | -440         |            |       |            |              |

| 18         | PA0         | -2151      | -664           | 61         | P26      | 2151        | -309         |            |       |            |              |

| 19         | PA1         | -2151      | -789           | 62         | DVSS2    | 2151        | -153         |            |       |            |              |

| 20         | PA2         | -2151      | -914           | 63         | PB4      | 2151        | 2            |            |       |            |              |

| 21         | PA3         | -2151      | -1040          | 64         | DVCC2    | 2151        | 158          |            |       |            |              |

| 22         | PC0         | -2151      | -1165          | 65         | P25      | 2151        | 315          |            |       |            |              |

| 23         | PC1         | -2151      | -1290          | 66         | P24      | 2151        | 446          |            |       |            |              |

| 24         | AM0         | -2151      | -1415          | 67         | P23      | 2151        | 577          |            |       |            |              |

| 25         | DVCC1       | -2151      | -1636          | 68         | P22      | 2151        | 708          |            |       |            |              |

| 26         | X2          | -1603      | -2175          | 69         | P21      | 2151        | 839          |            |       |            |              |

| 27         | DVSS1       | -1438      | -2175          | 70         | P20      | 2151        | 971          |            |       |            |              |

| 28         | X1          | -1273      | -2175          | 71         | A15      | 2151        | 1102         |            |       |            |              |

| 29         | AM1         | -1147      | -2175          | 72         | A14      | 2151        | 1233         |            |       |            | <b>└──</b> ┃ |

| 30         | RESET       | -1022      | -2175          | 73         | A13      | 2151        | 1364         |            |       |            | <u> </u>     |

| 31         | XT1         | -897       | -2175          | 74         | A12      | 2151        | 1495         |            |       |            |              |

| 32         | XT2         | -649       | -2175          | 75         | A11      | 2151        | 1627         |            |       |            | <u> </u>     |

| 33         | EMU0        | -524       | -2175          | 76         | A10      | 1603        | 2175         |            |       |            |              |

| 34         | EMU1<br>PC2 | -398       | -2175<br>2175  | 77         | A9       | 1477        | 2175         |            |       |            | <u> </u>     |

| 35         |             | -273       | -2175<br>2175  | 78         | A8       | 1350        | 2175         |            |       |            |              |

| 36<br>37   | PC3<br>PC4  | -148       | -2175<br>2175  | 79<br>80   | A7       | 1224        | 2175         |            |       |            | ├            |

| 37         | PC4<br>PC5  | -23<br>101 | -2175<br>-2175 | 80<br>81   | A6<br>A5 | 1097<br>970 | 2175<br>2175 |            |       |            |              |

| 30         | PC5<br>PD0  | 226        | -2175          | 82         | A5<br>A4 | 970<br>844  | 2175         |            |       |            | <u> </u>     |

| 40         | PD0<br>PD1  | 352        | -2175          | 83         | A4<br>A3 | 044<br>717  | 2175         |            |       |            | <u> </u>     |

| 40         | PD1<br>PD2  | 477        | -2175          | 84         | A3<br>A2 | 590         | 2175         |            |       |            |              |

| 41         | PD2<br>PD3  | 602        | -2175          | 85         | A2<br>A1 | 590<br>464  | 2175         |            |       |            |              |

| 42         | PD3<br>PD4  | 727        | -2175          | 86         | A1<br>A0 | 464<br>337  | 2175         |            |       |            |              |

| 43         | FU4         | 121        | -21/3          | 00         | AU       | <i>აა</i> / | 2113         |            |       |            |              |

## 2.3 Pin Names and Functions

The names of the input/output pins and their functions are described below.

| Pin Name   | Number<br>of Pins | I/O    | Functions                                                                  |

|------------|-------------------|--------|----------------------------------------------------------------------------|

| D0 to D7   | 8                 | I/O    | Data (lower): bits 0 to 7 of data bus                                      |

| P10 to P17 | 8                 | I/O    | Port 1: I/O port that allows I/O to be selected at the bit level           |

|            |                   |        | (When used to the external 8bit bus)                                       |

| D8 to D15  |                   | I/O    | Data (upper): Bits 8 to15 of data bus                                      |

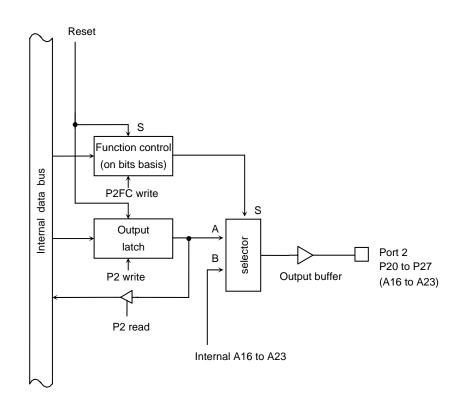

| P20 to P27 | 8                 | Output | Port 2: Output port                                                        |

| A16 to A23 |                   | Output | Address: Bits 16 to 23 of address bus                                      |

| A8 to A15  | 8                 | Output | Address: Bits 8 to 15 of address bus                                       |

| A0 to A7   | 8                 | Output | Address: Bits 0 to 7 of address bus                                        |

| RD         | 1                 | Output | Read: Strobe signal for reading external memory                            |

| WR         | 1                 | Output | Write: Strobe signal for writing data to pins D0 to D7                     |

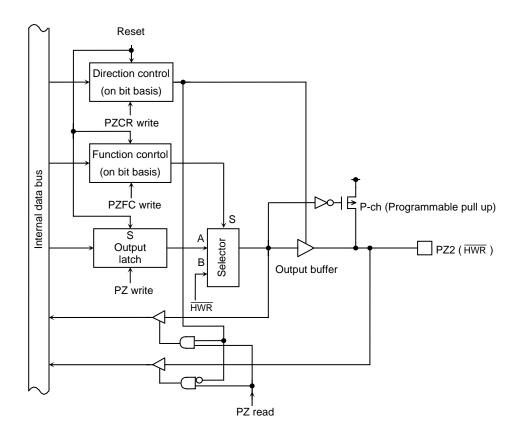

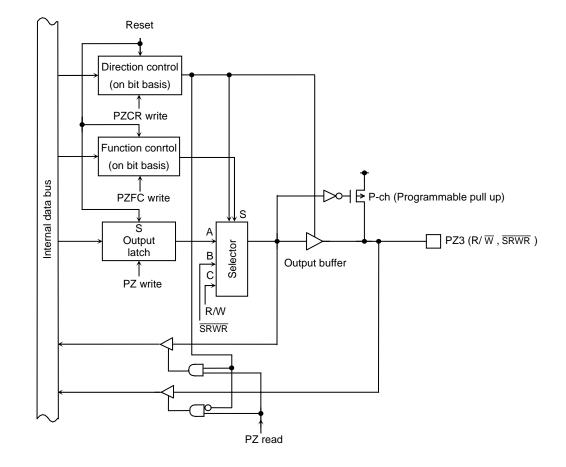

| PZ2        | 1                 | I/O    | Port Z2: I/O port (with pull-up resistor)                                  |

| HWR        |                   | Output | High Write: Strobe signal for writing data to pins D8 to D15               |

| PZ3        | 1                 | I/O    | Port Z3: I/O port (with pull-up resistor)                                  |

| R/ W       |                   | Output | Read/Write: 1 represents read or dummy cycle; 0 represents write cycle.    |

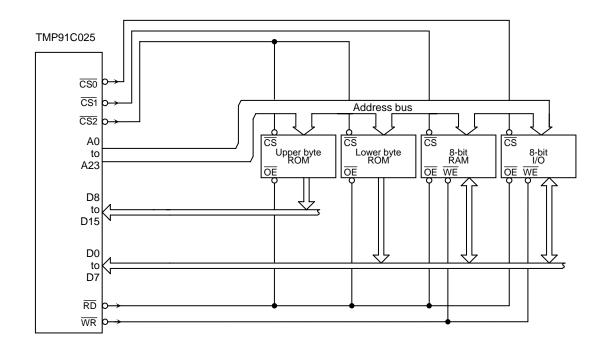

| SRWR       |                   | Output | Write: Strobe signal for writing data to pins D0 to D15 for SRAM           |

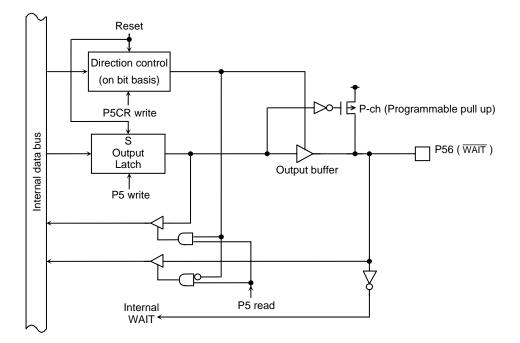

| P56        | 1                 | I/O    | Port 56: I/O port (with pull-up resistor)                                  |

| WAIT       |                   | Input  | Wait: Pin used to request CPU bus wait                                     |

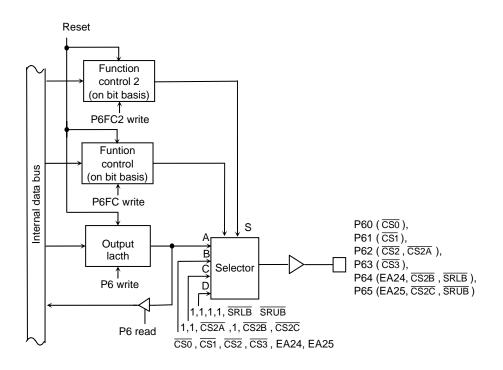

| P60        | 1                 | Output | Port 60:Output port                                                        |

| CS0        |                   | Output | Chip select 0: Outputs 0 when address is within specified address area.    |

| P61        | 1                 | Output | Port 61:Output port                                                        |

| CS1        |                   | Output | Chip select 1: Outputs 0 when address is within specified address area     |

| P62        | 1                 | Output | Port 62: Output port                                                       |

| CS2        |                   | Output | Chip select 2: Outputs 0 when address is within specified address area     |

| CS2A       |                   | Output | Expand chip select: 2A: Outputs 0 when address is within specified address |

|            |                   |        | area                                                                       |

| P63        | 1                 | Output | Port 63:Output port                                                        |

| CS3        |                   | Output | Chip select 3: Outputs 0 when address is within specified address area     |

| P64        | 1                 | Output | Port 64: Output port                                                       |

| EA24       |                   | Output | Chip select 24: Outputs 0 when address is within specified address area    |

| CS2B       |                   | Output | Expand chip select: 2B: Outputs 0 when address is within specified address |

|            |                   | _      | area                                                                       |

| SRLB       |                   | Output | Low byte enable for SRAM                                                   |

| P65        | 1                 | Output | Port 65: Output port                                                       |

| EA25       |                   | Output | Chip select 25: Outputs 0 when address is within specified address area    |

| CS2C       |                   | Output | Expand chip select: 2C: Outputs 0 when address is within specified address |

|            |                   |        | area                                                                       |

| SRUB       |                   | Output | High byte enable for SRAM                                                  |

Table 2.3.1 Pin Names and Functions (1/3)

| Pin Name   | Number<br>of Pins | I/O    | Functions                                                                       |

|------------|-------------------|--------|---------------------------------------------------------------------------------|

| P80 to P81 | 2                 | Input  | Port 80 to 81 port: Pin used to input ports                                     |

| AN0 to AN1 |                   | Input  | Analog input 0 to 1: Pin used to input to AD converter                          |

| P82        | 1                 | Input  | Port 82 port: Pin used to input ports                                           |

| AN2        |                   | Input  | Analog input 2: Pin used to input to AD converter                               |

| MX         |                   | Input  | X-Minus: Pin connected to X- for touch screen panel                             |

| P83        | 1                 | Input  | Port 83 port: Pin used to input ports                                           |

| AN3        |                   | Input  | Analog input 3: Pin used to input to AD converter                               |

| ADTRG      |                   | Input  | AD trigger: Signal used to request AD start                                     |

| MY         |                   | Input  | Y-Minus: Pin connected to Y- for touch screen panel                             |

| P90 to P97 | 8                 | Input  | Port: 90 to 97 port: Pin used to input ports                                    |

| KI0 to KI7 | -                 | Input  | Key input 0 to 7: Pin used of key-on wakeup 0 to 7                              |

|            |                   | ·      | (Schmitt input, with pull-up resistor)                                          |

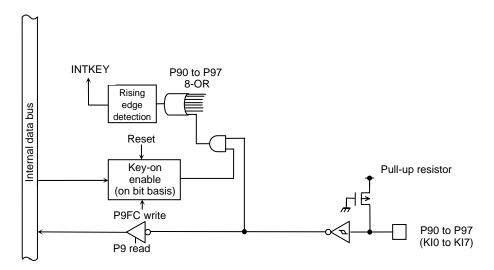

| PA0        | 1                 | Output | Port: A0 port: Pin used to output ports                                         |

| KO0        |                   | Output | Key output 0: Pin used of key-scan strobe 0                                     |

| ALARM      |                   | Output | RTC alarm output pin                                                            |

| MLDALM     |                   | Output | Melody/alarm output pin (Inverted)                                              |

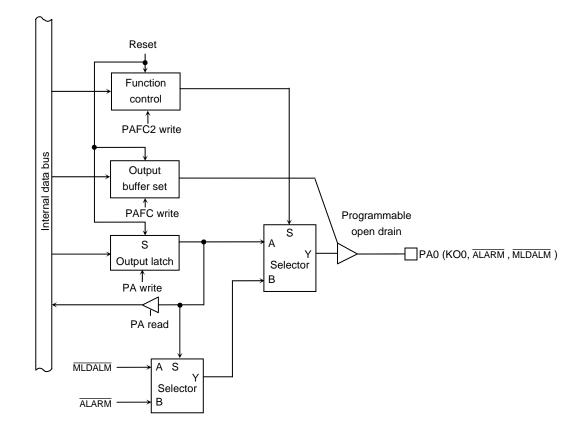

| PA1        | 1                 | Output | Port: A1 port: Pin used to output ports                                         |

| KO1        |                   | Output | Key output 1: Pin used of key-scan strobe 1                                     |

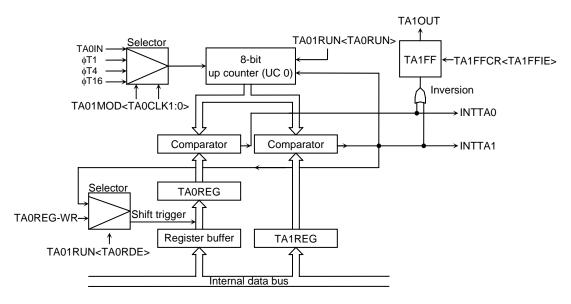

| TA1OUT     |                   | Output | 8-bit timer 1 output: Timer 0 input or timer 1 output                           |

| PA2        | 1                 | Output | Port: A2 port: Pin used to output ports                                         |

| KO2        |                   | Output | Key output 2: Pin used of key-scan strobe 2                                     |

| TA3OUT     |                   | Output | 8-bit timer 3 output: Timer 2 input or timer 3 output                           |

| PA3        | 1                 | Output | Port: A3 port: Pin used to output ports                                         |

| КОЗ        |                   | Output | Key output 3: Pin used of key-scan strobe 3                                     |

| SCOUT      |                   | Output | System clock output: Output f <sub>FPH</sub> clock                              |

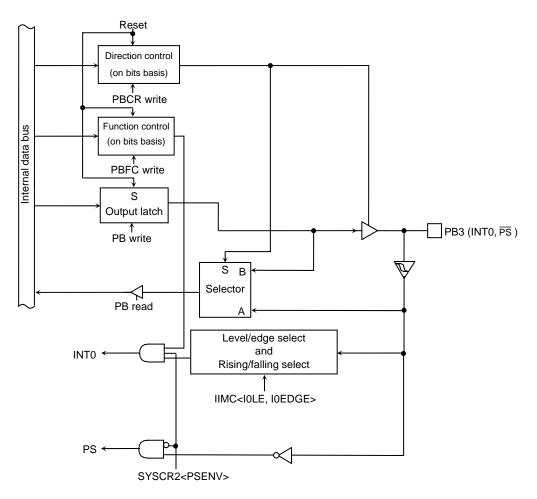

| PB3        | 1                 | I/O    | Port B3: I/O port                                                               |

| INT0       |                   | Input  | Interrupt request pin0: Interrupt request with programmable level/rising edge   |

| PS         |                   | Input  | Power save: Pin used as input pin for H/W standby mode                          |

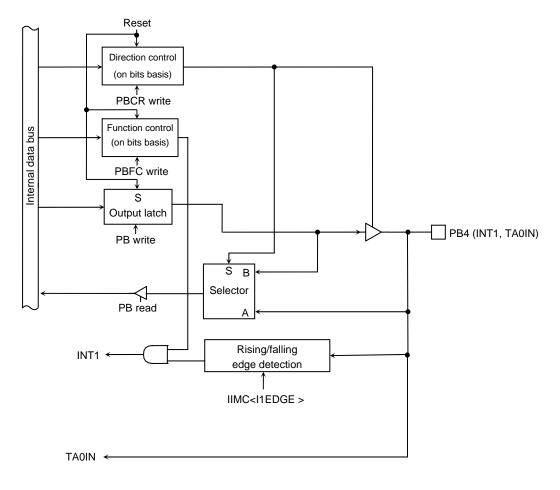

| PB4        | 1                 | I/O    | Port B4: I/O port                                                               |

| INT1       |                   | Input  | Interrupt request pin1: Interrupt request with programmable rising/falling edge |

| TAOIN      |                   | Input  | 8-bit timer 0 input: Timer 0 input                                              |

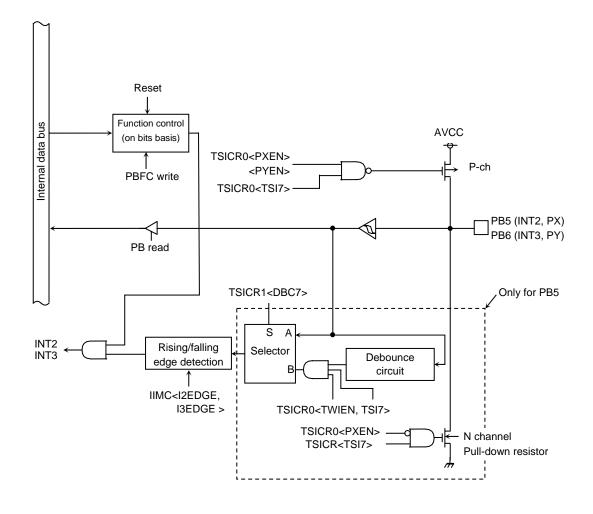

| PB5        | 1                 | Input  | Port B5: Input port                                                             |

| INT2       |                   | Input  | Interrupt request pin2: Interrupt request with programmable rising/falling edge |

| PX         |                   | Output | X-Plus: Pin connected to X+ for touch screen panel                              |

| PB6        | 1                 | Input  | Port B6: Input port                                                             |

| INT3       |                   | Input  | Interrupt request pin3: Interrupt request with programmable rising/falling edge |

| PY         |                   | Output | Y-Plus: Pin connected to Y+ for touch screen panel                              |

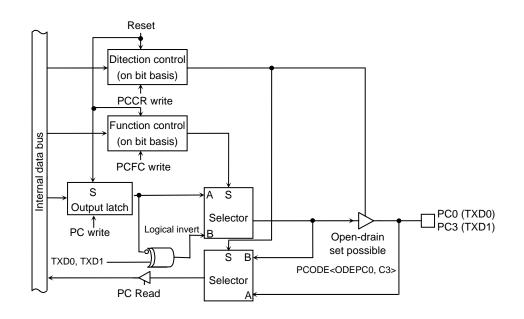

| PC0        | 1                 | I/O    | Port C0: I/O port                                                               |

| TXD0       |                   | Output | Serial 0 send data: Open-drain output pin by programmable                       |

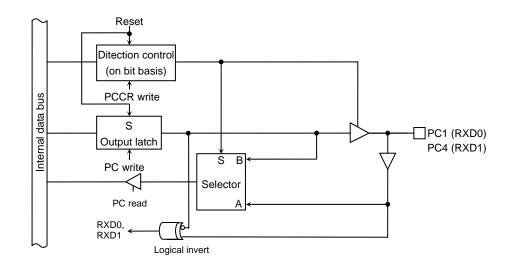

| PC1        | 1                 | I/O    | Port C1: I/O port                                                               |

| RXD0       |                   | Output | Serial 0 receive data                                                           |

Table 2.3.2 Pin Names and Functions (2/3)

Note: After reset, input "1" to PB3 (INT0, PS)-pin, because it is worked as PS input pin.

| Pin Name   | Number<br>of Pins | I/O    | Functions                                                                  |

|------------|-------------------|--------|----------------------------------------------------------------------------|

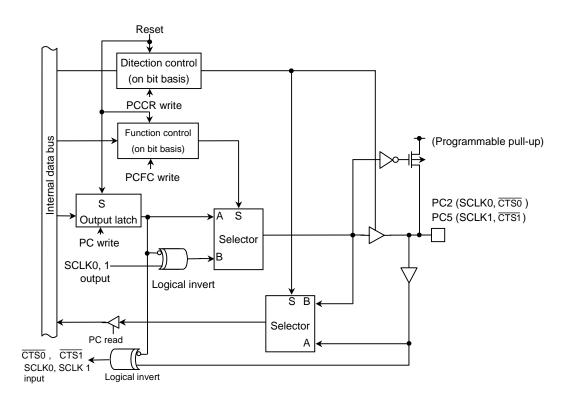

| PC2        | 1                 | I/O    | Port C2: I/O port (with pull-up resistor)                                  |

| SCLK0      |                   | I/O    | Serial clock I/O 0                                                         |

| CTS0       |                   | Input  | Serial data send enable 0 (Clear to send)                                  |

| PC3        | 1                 | I/O    | Port C3: I/O port                                                          |

| TXD1       |                   | Output | Serial send data 1                                                         |

|            |                   | -      | Open-drain output pin by programmable                                      |

| PC4        | 1                 | I/O    | Port C4: I/O port                                                          |

| RXD1       |                   | Input  | Serial receive data 1                                                      |

| PC5        | 1                 | I/O    | Port C5: I/O port (with pull-up resistor)                                  |

| SCLK1      |                   | I/O    | Serial clock I/O 1                                                         |

| CTS1       |                   | Input  | Serial data send enable 1 (Clear to send)                                  |

| XT1        | 1                 | Input  | Low-frequency oscillator connecting pin                                    |

| XT2        | 1                 | Output | Low-frequency oscillator connecting pin                                    |

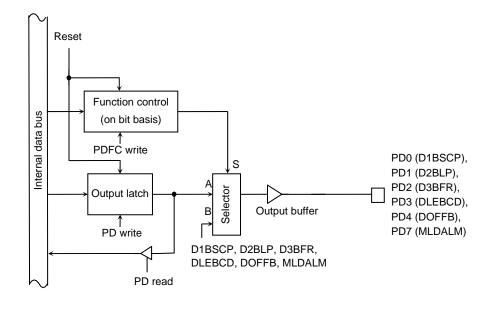

| PD0        | 1                 | Output | Port D0: Output port                                                       |

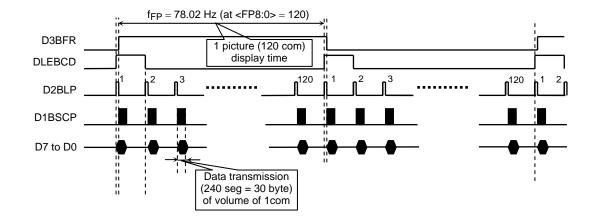

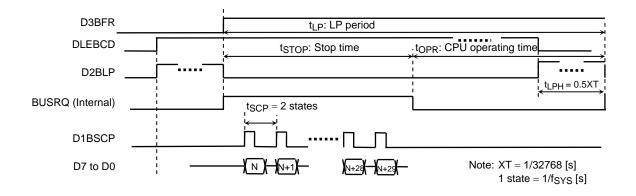

| D1BSCP     |                   | Output | LCD controller output pin                                                  |

| PD1        | 1                 | Output | Port D1: Output port                                                       |

| D2BLP      |                   | Output | LCD controller output pin                                                  |

| PD2        | 1                 | Output | Port D2: Output port                                                       |

| D3BFR      |                   | Output | LCD controller output pin                                                  |

| PD3        | 1                 | Output | Port D3: Output port                                                       |

| DLEBCD     |                   | Output | LCD controller output pin                                                  |

| PD4        | 1                 | Output | Port D4: Output port                                                       |

| DOFFB      |                   | Output | LCD controller output pin                                                  |

| PD7        | 1                 | Output | Port D7: Output port                                                       |

| MLDALM     |                   | Output | Melody/alarm output pin                                                    |

| AM0 to AM1 | 2                 | Input  | Operation mode:                                                            |

|            |                   |        | Fixed to AM1 = 0, AM0 = 1 16-bit external bus or 8-/16-bit dynamic sizing. |

|            |                   |        | Fixed to AM1 = 0, AM0 = 0 8-bit external bus fixed.                        |

| EMU0       | 1                 | Output | Open pin                                                                   |

| EMU1       | 1                 | Output | Open pin                                                                   |

| RESET      | 1                 | Input  | Reset: initializes TMP91C025. (with pull-up resistor)                      |

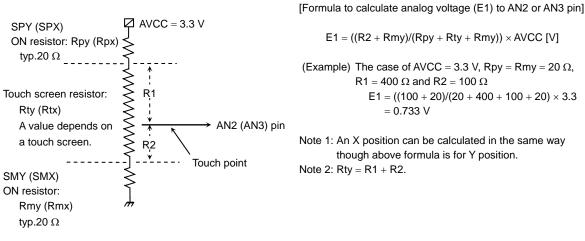

| VREFH      | 1                 | Input  | Pin for reference voltage input to AD converter (H)                        |

| VREFL      | 1                 | Input  | Pin for reference voltage input to AD converter (L)                        |

| AVCC       | 1                 |        | Power supply pin for AD converter                                          |

| AVSS       | 1                 |        | GND pin for AD converter (0 V)                                             |

| X1, X2     | 2                 | I/O    | High-frequency oscillator connection pins                                  |

| DVCC       | 2                 |        | Power supply pins                                                          |

|            | _                 |        | (All VCC pins should be connected with the power supply pin.)              |

| DVSS       | 2                 |        | GND pins (0 V) (All pins should be connected with GND (0 V).)              |

Table 2.3.3 Pin Names and Functions. (3/3)

## 3. Operation

This following describes block by block the functions and operation of the TMP91C025.

Notes and restrictions for eatch book are outlined in 6, precautions and restrictions at the end of this manual.

#### 3.1 CPU

The TMP91C025 incorporates a high-performance 16-bit CPU (the 900/L1-CPU). For CPU operation, see the TLCS-900/L1 CPU.

The following describe the unique function of the CPU used in the TMP91C025; these functions are not covered in the TLCS-900/L1 CPU section.

#### 3.1.1 Reset

When resetting the TMP91C025 microcontroller, ensure that the power supply voltage is within the operating voltage range, and that the internal high-frequency oscillator has stabilized. Then hold the  $\overline{\text{RESET}}$  input to low level at least for 10 system clocks (9 µs at 36 MHz).

Thus, when turn on the switch, be set to the power supply voltage is within the operating voltage range, and that the internal high-frequency oscillator has stabilized. Then hold the  $\overline{\text{RESET}}$  input to low level at least for 10 system clocks.

Clock gear is initialized 1/16 mode by reset operation. It means that the system clock mode fsys is set to  $fc/32 (= fc/16 \times 1/2)$ .

When the reset is accept, the CPU:

• Sets as follows the program counter (PC) in accordance with the reset vector stored at address FFFF00H to FFFF02H:

PC<0:7>  $\leftarrow$  Value at FFFF00H address

PC<15:8>  $\leftarrow$  Value at FFFF01H address

PC<23:16>  $\leftarrow$  Value at FFFF02H address

- Sets the stack pointer (XSP) to 100H.

- Sets bits <IFF2:0> of the status register (SR) to 111 (Sets the interrupt level mask register to level 7).

- Sets the <MAX> bit of the status register (SR) to 1 (MAX mode).

Note: As this product does not support MIN mode, do not write a 0 to the <MAX>

- Clears bits <RFP2:0> of the status register(SR) to 000 (Sets the register bank to 0).

When reset is released, the CPU starts executing instructions in accordance with the program counter settings. CPU internal registers not mentioned above do not change when the reset is released.

When the reset is accepted, the CPU sets internal I/O, ports, and other pins as follows.

- Initializes the internal I/O registers.

- Sets the port pins, including the pins that also act as internal I/O, to general-purpose input or output port mode.

Note: The CPU internal register (Except to PC, SR, XSP) do not change by resetting.

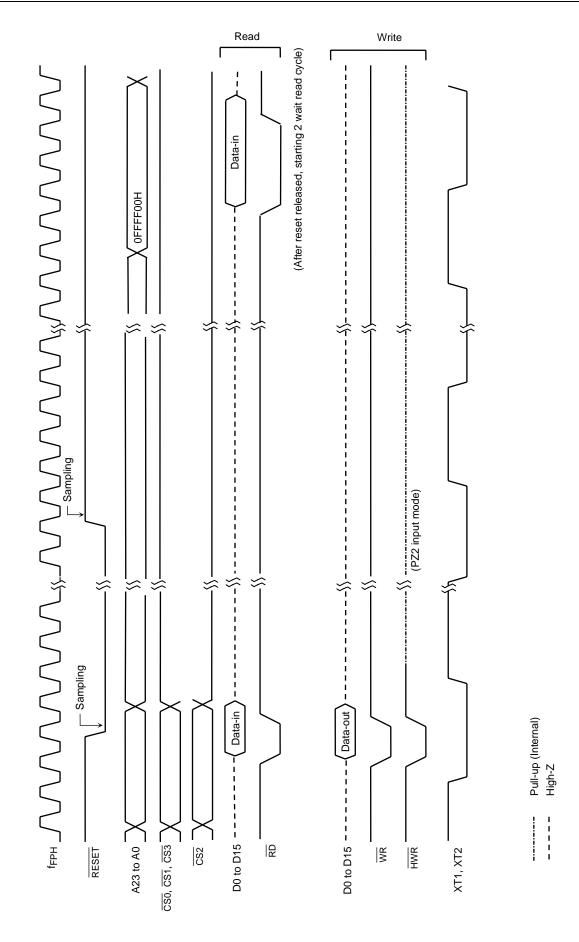

Figure 3.1.1 is a reset timing chart of the TMP91C025.

Figure 3.1.1 Reset Timing Chart

## 3.2 Memory Map

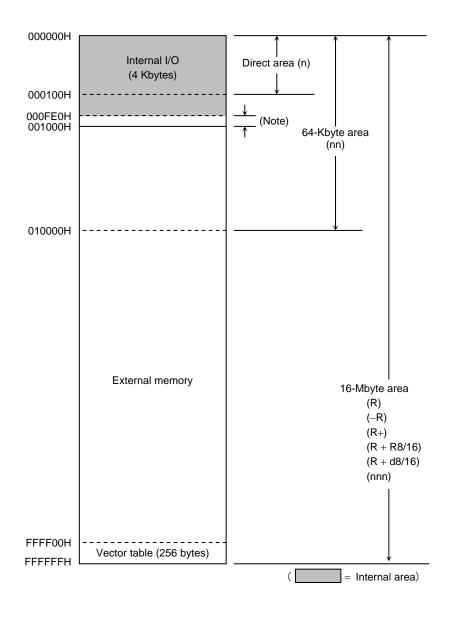

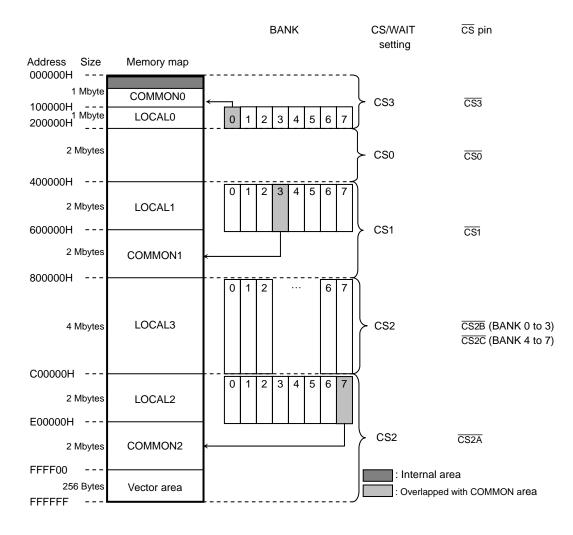

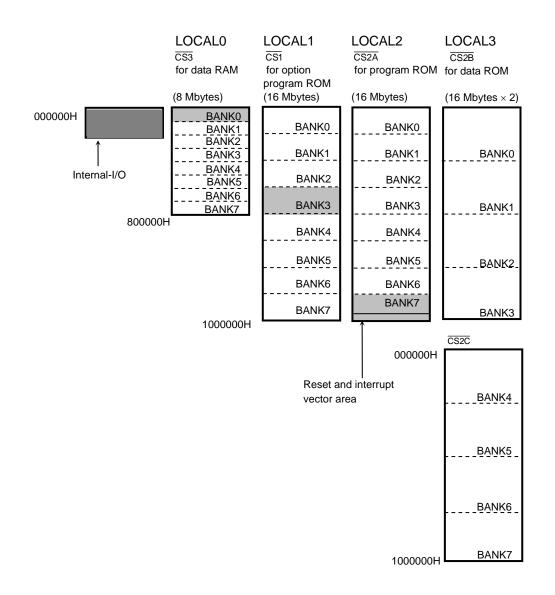

Figure 3.2.1 is a memory map of the TMP91C025.

Figure 3.2.1 Memory Map

Note: Address 000FE0H to 000FEFH is assigned for the external memory area of built-in RAM type LCD driver.

Address 000FF0H to 000FFFH is assingned for the external memory area as reserved.

## 3.3 Triple Clock Function and Standby Function

TMP91C025 contains a clock gear, clock doubler (DFM), standby controller and noise-reduction circuit. It is used for low-power and low-noise systems.

This chapter is organized as follows:

- 3.3.1 Block Diagram of System Clock

- 3.3.2 SFRs

- 3.3.3 System Clock Controller

- 3.3.4 Prescaler Clock Controller

- 3.3.5 Clock Doubler (DFM)

- 3.3.6 Noise reducing Circuit

- 3.3.7 Standby Controller

## TOSHIBA

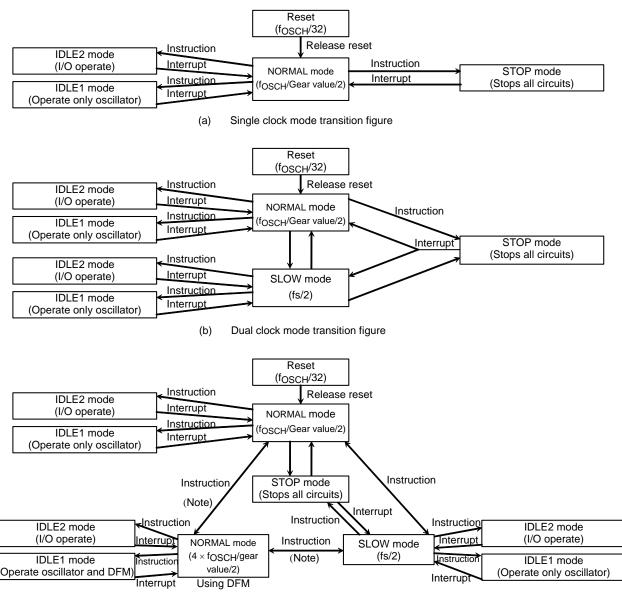

The clock operating modes are as follows: (a) Single clock mode (X1, X2 pins only), (b) Dual clock mode (X1, X2, XT1 and XT2 pins) and (c) Triple clock mode (the X1, X2, XT1 and XT2 pins and DFM).

Figure 3.3.1 shows a transition figure.

(c) Triple clock mode trasision figure

Note 1: It's prohibited to control DFM in SLOW mode when shifting from SLOW mode to NORMAL mode with use of DFM. (DFM start up/stop/change write to DFMCR0<ACT1:0> register)

Note 2: If you shift from NORMAL mode with use of DFM to NORMAL mode, the instruction should be separated into two procedures as below. Change CPU clock → Stop DFM circuit

Note 3: It's prohibited to shift from NORMAL mode with use of DFM to STOP mode directly. You should set NORMAL mode once, and then shift to STOP mode.(You should stop high frequency oscillator after you stop DFM.)

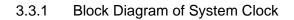

#### Figure 3.3.1 System Clock Block Diagram

The clock frequency input from the X1 and X2 pins is called fc and the clock frequency input from the XT1 and XT2 pins is called fs. The clock frequency selected by SYSCR1<SYSCK> is called the system clock fFPH. The system clock fSYS is defined as the divided clock of fFPH, and one cycle of fSYS is defined to as one state.

Figure 3.3.2 Block Diagram of System Clock

## TOSHIBA

#### 3.3.2 SFRs

|         |             | 7               | 6               | 5                           | 4               | 3              | 2                           | 1                    | 0            |

|---------|-------------|-----------------|-----------------|-----------------------------|-----------------|----------------|-----------------------------|----------------------|--------------|

| SYSCR0  | Bit symbol  | XEN             | XTEN            | RXEN                        | RXTEN           | RSYSCK         | WUEF                        | PRCK1                | PRCK0        |

| (00E0H) | Read/Write  |                 |                 |                             | R/              | W              |                             |                      |              |

|         | After reset | 1               | 1               | 1                           | 0               | 0              | 0                           | 0                    | 0            |

|         | Function    | High-           | Low-            | High-                       | Low-            | Selects        | Warm-up                     | Select presca        | aler clock   |

|         |             | frequency       | frequency       | frequency                   | frequency       | clock after    | timer                       | 00: f <sub>FPH</sub> |              |

|         |             | oscillator (fc) | oscillator (fs) | oscillator (fc)             | oscillator (fs) | release of     | 0: Write                    | 01: Reserved         |              |

|         |             | 0: Stop         | 0: Stop         | after release               | after release   | STOP mode      | Don't care                  | 10: fc/16            |              |

|         |             | 1: Oscillation  | 1: Oscillation  | of STOP                     | of STOP         | 0: fc          | 1: Write                    | 11: Reserved         |              |

|         |             |                 | (Note 1)        | mode                        | mode            | 1: fs          | start timer                 |                      |              |

|         |             |                 |                 | 0: Stop                     | 0: Stop         |                | 0: Read                     |                      |              |

|         |             |                 |                 | 1: Oscillation              | 1: Oscillation  |                | end                         |                      |              |

|         |             |                 |                 |                             |                 |                | warm-up                     |                      |              |

|         |             |                 |                 |                             |                 |                | 1:Read                      |                      |              |

|         |             |                 |                 |                             |                 |                | do not end                  |                      |              |

|         |             | 7               | 6               | 5                           | 4               | 3              | warm-up<br>2                | 1                    | 0            |

| SYSCR1  |             |                 | <u> </u>        | <u> </u>                    | - T             |                |                             |                      |              |

| (00E1H) | Bit symbol  | $\backslash$    | $\backslash$    | $\backslash$                |                 | SYSCK          | GEAR2                       | GEAR1                | GEAR0        |

| · · ·   | Read/Write  | /               |                 |                             |                 | R/W            |                             |                      |              |

|         | After reset |                 |                 |                             |                 | 0              | 1                           | 0                    | 0            |

|         | Function    |                 |                 |                             |                 | Select         | _                           | alue of high-fre     | equency (fc) |

|         |             |                 |                 |                             |                 | system         | 000: fc                     |                      |              |

|         |             |                 |                 |                             |                 | clock<br>0: fc | 001: fc/2<br>010: fc/4      |                      |              |

|         |             |                 |                 |                             |                 | 0.1C<br>1: fs  | 010. lc/4<br>011: fc/8      |                      |              |

|         |             |                 |                 |                             |                 | 1.15           | 100: fc/16                  |                      |              |

|         |             |                 |                 |                             |                 |                | 100: 10/10<br>101: (Reserve | ed)                  |              |

|         |             |                 |                 |                             |                 |                | 110: (Reserv                | -                    |              |

|         |             |                 |                 |                             |                 |                | 111: (Reserve               | -                    |              |

|         |             | 7               | 6               | 5                           | 4               | 3              | 2                           | 1                    | 0            |

| SYSCR2  | Bit symbol  | PSENV           | /               | WUPTM1                      | WUPTM0          | HALTM1         | HALTM0                      | SELDRV               | DRVE         |

| (00E2H) | Read/Write  | R/W             |                 | R/W                         | R/W             | R/W            | R/W                         | R/W                  | R/W          |

|         | After reset | 0               |                 | 1                           | 0               | 1              | 1                           | 0                    | 0            |

|         | Function    | 0: Power        |                 | Warm-up time                | ər              | HALT mode      |                             | <drve></drve>        | Pin state    |

|         |             | save            |                 | 00: Reserved                |                 | 00: Reserved   | l                           | mode                 | control in   |

|         |             | mode            |                 | 01: 2 <sup>8</sup> /inputte | d frequency     | 01: STOP mo    | ode                         | select               | STOP/IDLE1   |

|         |             | enable          |                 | 10: 2 <sup>14</sup>         |                 | 10: IDLE1 mo   | ode                         | 0: IDLE1             | mode         |

|         |             | 1: Disable      |                 | 11: 2 <sup>16</sup>         |                 | 11: IDLE2 mc   | ode                         | 1: STOP              | 0: I/O off   |

|         |             | (Note 2)        |                 |                             |                 |                |                             | (Note 3)             | 1: Remains   |

|         |             |                 |                 |                             |                 |                |                             |                      | the state    |

|         |             |                 |                 |                             |                 |                |                             |                      | before       |

|         |             |                 |                 |                             |                 |                |                             |                      | halt         |

Note 1: By reset, low-frequency oscillator is enabled.

Note 2: When hard ware standby mode is entered, the meaning of SYSCR2<HALTM1:0> = 11 shows IDLE1 mode.

Note 3: "0" means IDLE1 and "1" means STOP. Please be carefull because this setting is sometimes different from others.

Figure 3.3.3 SFRs for System Clock

| Symbol  | Name                             | Address  | 7                                                                         | 6                          | 5                                   | 4                                                                                      | 3               | 2             | 1   | 0   |

|---------|----------------------------------|----------|---------------------------------------------------------------------------|----------------------------|-------------------------------------|----------------------------------------------------------------------------------------|-----------------|---------------|-----|-----|

|         |                                  |          | ACT1                                                                      | ACT0                       | DLUPFG                              | DLUPTM                                                                                 |                 |               |     |     |

|         |                                  |          | R/W                                                                       | R/W                        | R                                   | R/W                                                                                    |                 |               |     |     |

|         | DEM                              |          | 0                                                                         | 0                          | 0                                   | 0                                                                                      |                 | /             |     |     |

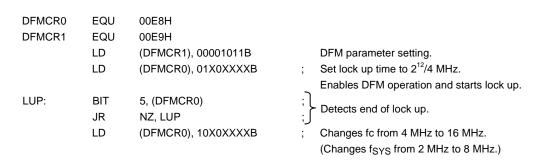

| DFMCR0  | DFM                              | EQU      | DFM L                                                                     | UP select f <sub>FPH</sub> | Lock up                             | Lock up                                                                                |                 |               |     |     |

| Drivero | R0 control<br>register 0         | E8H      | 00 STOP ST<br>01 RUN RI<br>10 RUN ST<br>11 RUN ST                         | JN fosch<br>OP fdfm        | status Flag<br>0: End<br>1: Not end | Time<br>0: 2 <sup>12</sup> /f <sub>OSCH</sub><br>1: 2 <sup>10</sup> /f <sub>OSCH</sub> |                 |               |     |     |

|         |                                  |          | D7                                                                        | D6                         | D5                                  | D4                                                                                     | D3              | D2            | D1  | D0  |

|         | DEM                              |          | R/W                                                                       | R/W                        | R/W                                 | R/W                                                                                    | R/W             | R/W           | R/W | R/W |

| DFMCR1  | CR1 DFM<br>control<br>register 1 | E9H<br>1 | 0                                                                         | 0                          | 0                                   | 1                                                                                      | 0               | 0             | 1   | 1   |

|         |                                  |          | DFM revision<br>Input frequency 4 to 9 MHz (at 3.0 V to 3.6 V): write 0BH |                            |                                     |                                                                                        |                 |               |     |     |

|         |                                  |          |                                                                           | Inpu                       | ut frequency 4                      | to 6.75 MHz (a                                                                         | at 2.7 V to 3.6 | V): write 0BH |     |     |

Figure 3.3.4 SFRs for DFM

Limitation point on the use of DFM

- 1. It's prohibited to execute DFM enable/disable control in the SLOW mode (fs) (write to DFMCR0<ACT1:0> = "10"). You should control DFM in the NORMAL mode.

- 2. If you stop DFM operation during using DFM(DFMCR0<ACT1:0> = "10"), you shouldn't execute that change the clock fDFM to fOSCH and stop the DFM at the same time. Therefore the above execution should be separated into two procedures as showing below.

- (DFMCR0), C0H LD Change the clock fDFM to fOSCH : LD

- (DFMCR0), 00H DFM stop ;

- 3. If you stop high-frequency oscillator during using DFM (DFMCR0<ACT1:0> = "10"), you should stop DFM before you stop high-frequency oscillator.

Please refer to 3.3.5 Clock Doubler (DFM) for the Details.

|         |             | 7                                                       | 6                                                                                                                                | 5            | 4              | 3        | 2              | 1              | 0              |  |  |  |  |

|---------|-------------|---------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--------------|----------------|----------|----------------|----------------|----------------|--|--|--|--|

| EMCCR0  | Bit symbol  | PROTECT                                                 | <b>TA3LCDE</b>                                                                                                                   | AHOLD        | <b>TA3MLDE</b> | -        | EXTIN          | DRVOSCH        | DRVOSCL        |  |  |  |  |

| (00E3H) | Read/Write  | R                                                       | R/W                                                                                                                              | R/W          | R/W            | R/W      | R/W            | R/W            | R/W            |  |  |  |  |

|         | After reset | 0                                                       | 0                                                                                                                                | 0            | 0              | 0        | 0              | 1              | 1              |  |  |  |  |

|         | Function    | Protect flag                                            | LCDC source                                                                                                                      | Address hold | Melody/alarm   | Always   | 1: External    | fc oscillator  | fs oscillator  |  |  |  |  |

|         |             | 0: Off                                                  | CLK                                                                                                                              | 0: Disable   | source clock   | write 0. | clock          | driver ability | driver ability |  |  |  |  |

|         |             | 1: On                                                   | 0: 32 kHz                                                                                                                        | 1: Enable    | 0: 32 kHz      |          |                | 1: Normal      | 1: Normal      |  |  |  |  |

|         |             |                                                         | 1: TA3OUT                                                                                                                        | (Note)       | 1: TA3OUT      |          |                | 0: Weak        | 0: Weak        |  |  |  |  |

| EMCCR1  | Bit symbol  |                                                         |                                                                                                                                  |              |                |          |                |                |                |  |  |  |  |

| (00E4H) | Read/Write  |                                                         |                                                                                                                                  |              |                |          |                |                |                |  |  |  |  |

|         | After reset | Switching th                                            | Switching the protect ON/OFF by write to following 1st-KEY, 2nd-KEY<br>1st-KEY: EMCCR1 = 5AH, EMCCR2 = $A5H$ in succession write |              |                |          |                |                |                |  |  |  |  |

|         | Function    | 0                                                       |                                                                                                                                  |              |                |          |                |                |                |  |  |  |  |

| EMCCR2  | Bit symbol  | 2nd-KEY: EMCCR1 = A5H, EMCCR2 = 5AH in succession write |                                                                                                                                  |              |                |          |                |                |                |  |  |  |  |

| (00E5H) | Read/Write  |                                                         |                                                                                                                                  |              |                |          |                |                |                |  |  |  |  |

|         | After reset |                                                         |                                                                                                                                  |              |                |          |                |                |                |  |  |  |  |

|         | Function    |                                                         |                                                                                                                                  |              |                |          |                |                |                |  |  |  |  |

| EMCCR3  | Bit symbol  |                                                         | ENFROM                                                                                                                           | ENDROM       | ENPROM         |          | FFLAG          | DFLAG          | PFLAG          |  |  |  |  |

| (00E6H) | Read/Write  | /                                                       | R/W                                                                                                                              | R/W          | R/W            | /        | R/W            | R/W            | R/W            |  |  |  |  |

|         | After reset |                                                         | 0                                                                                                                                | 0            | 0              |          | 0              | 0              | 0              |  |  |  |  |

|         | Function    |                                                         | CS1A area                                                                                                                        | CS2B-2C      | CS2A area      |          | CS1A write     | CS2B-2C write  | CS2A write     |  |  |  |  |

|         |             |                                                         | detect control                                                                                                                   | area detect  | detect control |          | operation flag | operation      | operation      |  |  |  |  |

|         |             |                                                         | 0: Disable                                                                                                                       | control      | 0: Disable     |          |                | flag           | flag           |  |  |  |  |

|         |             |                                                         | 1: Enable                                                                                                                        | 0: Disable   | 1: Enable      |          | When reading   | W              | /hen writing   |  |  |  |  |

|         |             |                                                         |                                                                                                                                  | 1: Enable    |                |          | 0: Not written | 0              | : Clear flag   |  |  |  |  |

|         |             |                                                         |                                                                                                                                  |              |                |          | 1: Written     |                |                |  |  |  |  |

Note1: When getting access to the logic address 000000H to 000FDFH, A0 to A23 holds the previous address of external access.

Note2: In case restarting the oscillator in the stop oscillation state (e.g. Restart the oscillator in STOP mode), set EMCCR0<DRVOSCH>, <DRVOSCL>="1".

Figure 3.3.5 SFRs for Noise Reduction

### 3.3.3 System Clock Controller

The system clock controller generates the system clock signal (f<sub>SYS</sub>) for the CPU core and internal I/O. It contains two oscillation circuits and a clock gear circuit for high-frequency (fc) operation. The register SYSCR1<SYSCK> changes the system clock to either fc or fs, SYSCR0<XEN> and SYSCR0<XTEN> control enabling and disabling of each oscillator, and SYSCR1<GEAR0:2> sets the high-frequency clock gear to either 1, 2, 4, 8 or 16 (fc, fc/2, fc/4, fc/8 or fc/16). These functions can reduce the power consumption of the equipment in which the device is installed.

The combination of settings  $\langle XEN \rangle = 1$ ,  $\langle XTEN \rangle = 0$ ,  $\langle SYSCK \rangle = 0$  and  $\langle GEAR0:2 \rangle = 100$  will cause the system clock (f<sub>SYS</sub>) to be set to fc/32 (fc/16 × 1/2) after a reset.

For example, fSYS is set to 1.1 MHz when the 36 MHz oscillator is connected to the X1 and X2 pins.

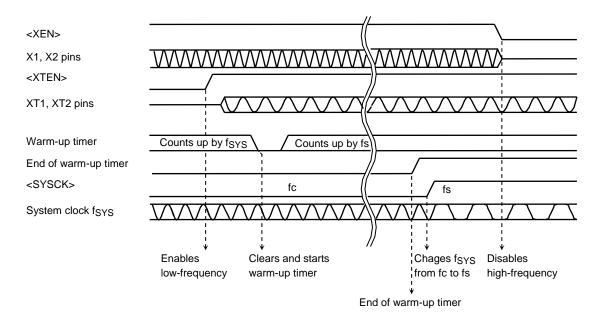

(1) Switching from NORMAL mode to SLOW mode

When the resonator is connected to the X1 and X2 pins, or to the XT1 and XT2 pins, the warm-up timer can be used to change the operation frequency after stable oscillation has been attained.

The warm-up time can be selected using SYSCR2<WUPTM0:1>.

This warm-up timer can be programmed to start and stop as shown in the following examples 1 and 2.

Table 3.3.1 shows the warm-up time.

- Note 1: When using an oscillator (other than a resonator) with stable oscillation, a warm-up timer is not needed.

- Note 2: The warm-up timer is operated by an oscillation clock. Hence, there may be some variation in warm-up time.

| Warm-up Time<br>SYSCR2<br><wuptm1:0></wuptm1:0> | Change to<br>NORMAL Mode | Change to<br>SLOW Mode | at f <sub>OSCH</sub> = 36 MHz, |

|-------------------------------------------------|--------------------------|------------------------|--------------------------------|

| 01 (2 <sup>8</sup> /frequency)                  | 7.1 (μs)                 | 7.8 (ms)               | fs = 32.768 kHz                |

| 10 (2 <sup>14</sup> /frequency)                 | 0.455 (ms)               | 500 (ms)               |                                |

| 11 (2 <sup>16</sup> /frequency)                 | 1.820 (ms)               | 2000 (ms)              |                                |

Table 3.3.1 Warm-up Times

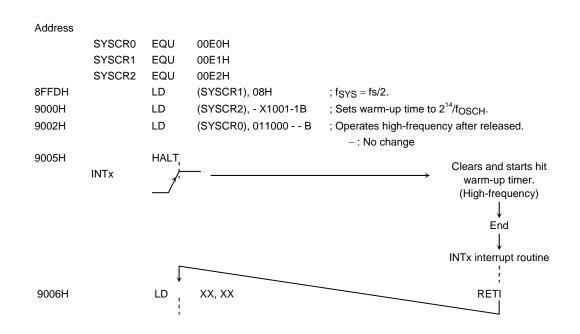

#### (Example 1: Setting the clock)

Changing from high-frequency (fc) to low-frequency (fs).

| SYSCR0 | EQU       | 00E0H                  |          |                                           |

|--------|-----------|------------------------|----------|-------------------------------------------|

| SYSCR1 | EQU       | 00E1H                  |          |                                           |

| SYSCR2 | EQU       | 00E2H                  |          |                                           |

|        | LD        | (SYSCR2), - X11 B      | ;        | Sets warm-up time to 2 <sup>16</sup> /fs. |

|        | SET       | 6, (SYSCR0)            | ;        | Enables low-frequency oscillation.        |

|        | SET       | 2, (SYSCR0)            | ;        | Clears and starts warm-up timer.          |

| WUP:   | BIT       | 2, (SYSCR0)            | ; ]      | Detects stopping of worm up timor         |

|        | JR        | NZ, WUP                | ; J      | Detects stopping of warm-up timer.        |

|        | SET       | 3, (SYSCR1)            | ;        | Changes fSYS from fc to fs.               |

|        | RES       | 7, (SYSCR0)            | ;        | Disables high-frequency oscillation.      |

| WOF.   | JR<br>SET | NZ, WUP<br>3, (SYSCR1) | ; J<br>; | 0 010                                     |

#### x: Don't care

-: No change

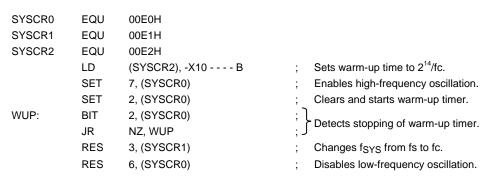

#### (Example 2: Setting the clock)

Changing from low-frequency (fs) to high-frequency (fc).

#### x: Don't care

-: No change

#### (2) Clock gear controller

When the high-frequency clock fc is selected by setting SYSCR1<SYSCK> = 0, fFPH is set according to the contents of the clock gear select register SYSCR1<GEAR2:0> to either fc, fc/2, fc/4, fc/8 or fc/16. Using the clock gear to select a lower value of fFPH reduces power consumption.

(Example 3)

Changing to a high-frequency gear

| SYSCR1 | EQU | 00E1H               |   |                                   |

|--------|-----|---------------------|---|-----------------------------------|

|        | LD  | (SYSCR1), XXXX0000B | ; | Changes f <sub>SYS</sub> to fc/2. |

X: Don't care

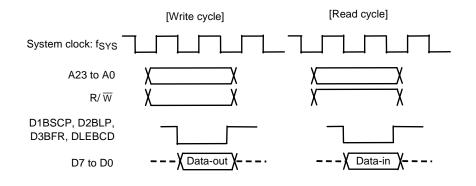

#### (High-speed clock gear changing)

To change the clock gear, write the register value to the SYSCR1<GEAR2:0> register. It is necessary the warm-up time until changing after writing the register value.

There is the possibility that the instruction next to the clock gear changing instruction is executed by the clock gear before changing. To execute the instruction next to the clock gear switching instruction by the clock gear after changing, input the dummy instruction as follows (Instruction to execute the write cycle).

#### (Example)

| SYSCR1 | EQU<br>LD  | 00E1H<br>(SYSCR1), XXXX0001B      |         | Changes fsys to fc/4. |

|--------|------------|-----------------------------------|---------|-----------------------|

|        | LD         | (DUMMY), 00H                      | ;       | Dummy instruction     |

|        | Instructio | on to be executed after clock gea | r has c | changed               |

#### (3) Internal clock output pin

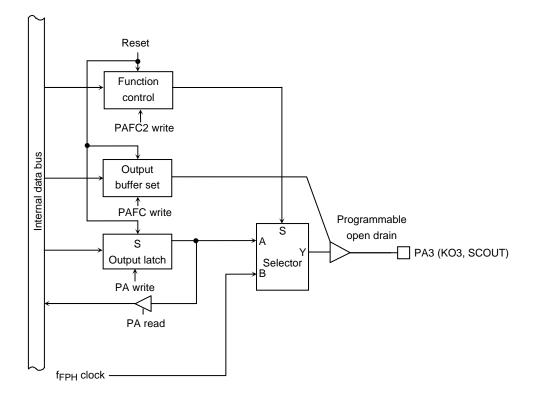

An internal clock fFPH can be output to the PA3/SCOUT pin. By setting "1" to the PAFC2<PA3F2> register, the PA3 pin functions as the SCOUT pin.

## TOSHIBA

#### 3.3.4 Prescaler Clock Controller

For the internal I/O (TMRA01 to TMRA23, SIO0 to SIO1) there is a prescaler which can divide the clock.

The  $\phi$ TO clock input to the prescaler is either the clock fFPH divided by 4 or the clock fc/16 divided by 4. The setting of the SYSCR0<PRCK0:1> register determines which clock signal is input.

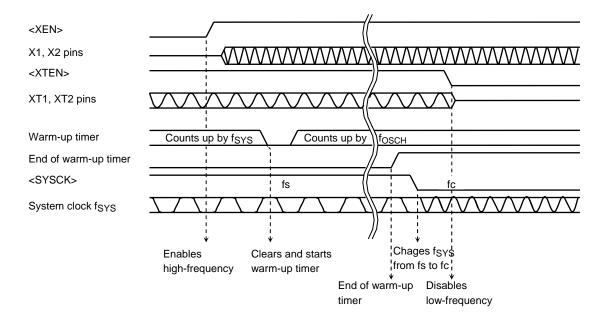

#### 3.3.5 Clock Doubler (DFM)

DFM outputs the  $f_{DFM}$  clock signal, which is four times as fast as  $f_{OSCH}$ . It can use the low-frequency oscillator, even though the internal clock is high frequency.

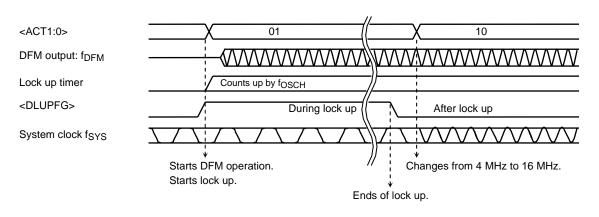

A reset initializes DFM to stop status, setting to DFMCR0-register is needed before use. Like an oscillator, this circuit requires time to stabilize. This is called the lock up time. The following example shows how DFM is used.

#### X: Don't care

Note: Input frequency limitation and correction for DFM

Recommend to use Input frequency (High-speed oscillation) for DFM in the following condition.

- f<sub>OSCH</sub> = 4 to 9 MHz (Vcc = 3.0 to 3.6 V): Write 0BH to DFMCR1

- $f_{OSCH} = 4$  to 6.75 MHz (Vcc = 2.7 to 3.6 V): Write 0BH to DFMCR1

Limitation point on the use of DFM

1. It's prohibited to execute DFM enable/disable control in the SLOW mode (fs)

(write to DFMCR0<ACT1:0> = "10"). You should control DFM in the NORMAL mode.

- 2. If you stop DFM operation during using DFM (DFMCR0<ACT1:0> = "10"), you shouldn't execute the commands that change the clock fDFM to fOSCH and stop the DFM at the same time. Therefore the above executions should be separated into two procedures as showing below.

- LD(DFMCR0), C0H;Change the clock f<sub>DFM</sub> to f<sub>OSCH</sub>.LD(DFMCR0), 00H;DFM stop.

- 3. If you stop high-frequency oscillator during using DFM (DFMCR0<ACT1:0> = "10"), you should stop DFM before you stop high-frequency oscillator.

Examples of settings are below.

(1) Start up/change control

(OK) Low-frequency oscillator operation mode (fs) (High-frequency oscillator STOP)  $\rightarrow$ High-frequency oscillator start up  $\rightarrow$  High-frequency oscillator operation mode (fosch)  $\rightarrow$ DFM start up  $\rightarrow$  DFM use mode (fDFM)

|      | LD  | (SYSCR0), 11 1 B   | ; High-frequency oscillator start up/warm-up start. |

|------|-----|--------------------|-----------------------------------------------------|

| WUP: | BIT | 2, (SYSCR0)        | ; } Check for the flag of warm-up end.              |

|      | JR  | NZ, WUP            | ; Check for the hag of warn-up end.                 |

|      | LD  | (SYSCR1), 0 B      | ; Change the system clock fs to f <sub>OSCH</sub> . |

|      | LD  | (DFMCR0), 01 - 0 B | ; DFM start up/lock up start.                       |

| LUP: | BIT | 5, (DFMCR0)        | ; } Check for the flag of lock up end.              |

|      | JR  | NZ, LUP            |                                                     |

|      | LD  | (DFMCR0), 10 - 0 B | ; Change the system clock fOSCH to fDFM.            |

(OK) Low-frequency oscillator operation mode (fs) (High-frequency oscillator operate)  $\rightarrow$  High-frequency oscillator operation mode (fosch)  $\rightarrow$  DFM start up  $\rightarrow$  DFM use mode (f<sub>DFM</sub>)

|      | LD  | (SYSCR1), 0 B      | ; Change the system clock fs to f <sub>OSCH</sub> . |

|------|-----|--------------------|-----------------------------------------------------|

|      | LD  | (DFMCR0), 01 - 0 B | ; DFM start up/lock up start.                       |

| LUP: | BIT | 5, (DFMCR0)        | ; } Check for the flag of lock up end.              |

|      | JR  | NZ, LUP            |                                                     |

|      | LD  | (DFMCR0), 10 - 0 B | ; Change the system clock fOSCH to fDFM.            |

(Error) Low-frequency oscillator operation mode (fs) (High-frequency oscillator STOP)  $\rightarrow$  High-frequency oscillator start up  $\rightarrow$  DFM start up  $\rightarrow$  DFM use mode (f<sub>DFM</sub>)

| 8 1  |     |                    |                                                    |

|------|-----|--------------------|----------------------------------------------------|

|      | LD  | (SYSCR0), 11 1 B   | ; High-frequency oscillator starts up/warm-up      |

|      |     |                    | start.                                             |

| WUP: | BIT | 2, (SYSCR0)        | ; Check for the flag of warm-up end.               |

|      | JR  | NZ, WUP            | ; J                                                |

|      | LD  | (DFMCR0), 01 - 0 B | ; DFM start up/lock up start.                      |

| LUP: | BIT | 5, (DFMCR0)        | ; } Check for the flag of lock up end.             |

|      | JR  | NZ, LUP            |                                                    |

|      | LD  | (DFMCR0), 10 - 0 B | ; Change the internal clock fOSCH to fDFM.         |

|      | LD  | (SYSCR1),0B        | ; Change the system clock fs to f <sub>DFM</sub> . |

|      |     |                    |                                                    |

(2) Change/stop control

| (OK) DFM use mode ( $f_{DFM}$ ) $\rightarrow$ High-frequency oscillator operation mode ( $f_{OSCH}$ ) $\rightarrow$ DFM                                                                                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\operatorname{stop} \to \operatorname{Low-frequency} \operatorname{oscillator} \operatorname{operation} \operatorname{mode} (\operatorname{fs}) \to \operatorname{High-frequency} \operatorname{oscillator} \operatorname{stop}$ |

| LD | (DFMCR0), 11 B | ; | Change the system clock fDFM to fOSCH. |

|----|----------------|---|----------------------------------------|

| LD | (DFMCR0), 00 B | ; | DFM stop.                              |

| LD | (SYSCR1), 1 B  | ; | Change the system clock fOSCH to fs.   |

| LD | (SYSCR0), 0 B  | ; | High-frequency oscillator stop.        |

|    |                |   |                                        |

(Error) DFM use mode (fDFM)  $\rightarrow$  Low-frequency oscillator operation mode (fs)  $\rightarrow$  DFM stop  $\rightarrow$  High-frequency oscillator stop

| LD | (SYSCR1), 1 B  | ; | Change the system clock fDFM to fs.           |

|----|----------------|---|-----------------------------------------------|

| LD | (DFMCR0), 11 B | ; | Change the internal clock (fc) fDFM to fOSCH. |

| LD | (DFMCR0), 00 B | ; | DFM stop.                                     |

| LD | (SYSCR0), 0 B  | ; | High-frequency oscillator stop.               |

(OK) DFM use mode ( $f_{DFM}$ )  $\rightarrow$  Set the STOP mode

$\begin{array}{cccc} \rightarrow & \mbox{High-frequency oscillator operation mode} & (f_{OSCH}) \rightarrow & \mbox{DFM stop} \rightarrow & \mbox{HALT} \\ (\mbox{High-frequency oscillator stop}) & & \mbox{LD} & (\mbox{SYSCR2}), --- & \mbox{O1--B} & ; & \mbox{Set the STOP mode.} \\ & & (\mbox{This command can execute before use of} & \mbox{O1--B} & \mbox{Chis} & \m$

|      |                |   | DFM.)                                  |

|------|----------------|---|----------------------------------------|

| LD   | (DFMCR0), 11 B | ; | Change the system clock fDFM to fOSCH. |

| LD   | (DFMCR0), 00 B | ; | DFM stop.                              |

| HALT |                | ; | Shift to STOP mode.                    |

(Error) DFM use mode (fDFM)  $\rightarrow$  Set the STOP mode  $\rightarrow$  HALT (High-frequency oscillator stop)

| LD   | (SYSCR2), 01 B | ; | Set the STOP mode.                      |

|------|----------------|---|-----------------------------------------|

|      |                |   | (This command can execute before use of |

|      |                |   | DFM.)                                   |

| HALT |                | ; | Shift to STOP mode.                     |

#### 3.3.6 Noise Reduction Circuits

Noise reduction circuits are built in, allowing implementation of the following features.

- (1) Reduced drivability for high-frequency oscillator

- (2) Reduced drivability for low-frequency oscillator

- (3) Single drive for high-frequency oscillator

- (4) SFR protection of register contents

- (5) ROM protection of register contents

The above functions are performed by making the appropriate settings in the EMCCR0 to EMCCR3 registers.

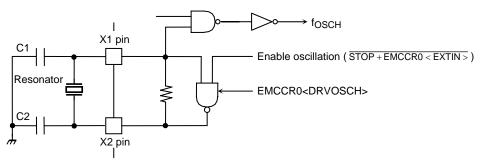

(1) Reduced drivability for high-frequency oscillator

#### (Purpose)

Reduces noise and power for oscillator when a resonator is used.

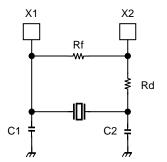

(Block diagram)

(Setting method)

The drivability of the oscillator is reduced by writing 0 to EMCCR0<DRVOSCH> register. By reset, <DRVOSCH> is initialized to 1 and the oscillator starts oscillation by normal-drivability when the power-supply is on.

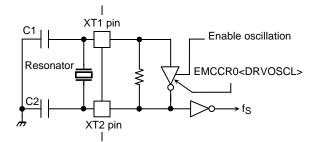

(2) Reduced drivability for low-frequency oscillator

#### (Purpose)

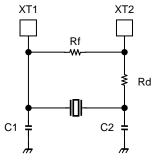

Reduces noise and power for oscillator when a resonator is used.

(Block diagram)

#### (Setting method)

The drivability of the oscillator is reduced by writing 0 to the EMCCR0<DRVOSCL> register. By reset, <DRVOSCL> is initialized to 1.

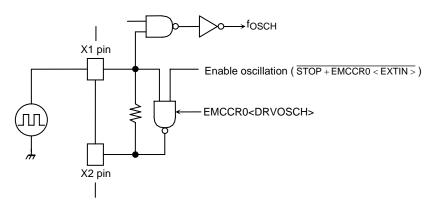

(3) Single drive for high-frequency oscillator

#### (Purpose)

Not need twin-drive and protect mistake operation by inputted noise to X2 pin when the external-oscillator is used.

(Block diagram)

(Setting method)

The oscillator is disabled and starts operation as buffer by writing 1 to EMCCR0<EXTIN> register. X2-pin is always outputted 1.

By reset, <EXTIN> is initialized to 0.

Note: Do not write EMCCR0<EXTIN> = "1" when using external resonator.

(4) Runaway provision with SFR protection register

#### (Purpose)

Provision in runaway of program by noise mixing.

Write operation to specified SFR is prohibited so that provision program in runaway prevents that it is it in the state which is fetch impossibility by stopping of clock, memory control register (CS/WAIT controller, MMU) is changed.

And error handling in runaway becomes easy by INTP0 interruption.

Specified SFR list

| 1. CS/WAIT controller                  |

|----------------------------------------|

| B0CS, B1CS, B2CS, B3CS, BEXCS,         |

| MSAR0, MSAR1, MSAR2, MSAR3,            |

| MAMR0, MAMR1, MAMR2, MAMR3             |

| 2. MMU                                 |

| LOCAL0/1/2/3                           |

| 3. Clock gear                          |

| SYSCR0, SYSCR1, SYSCR2, EMCCR0, EMCCR3 |

| 4. DFM                                 |

| DFMCR0, DFMCR1                         |

(Operation explanation)

Execute and release of protection (write operation to specified SFR) becomes possible by setting up a double key to EMCCR1 and EMCCR2 register.

(Double key)

1st-KEY: Succession writes in 5AH at EMCCR1 and A5H at EMCCR2 2nd-KEY: Succession writes in A5H at EMCCR1 and 5AH at EMCCR2

A state of protection can be confirmed by reading EMCCR0<PROTECT>.

By reset, protection becomes OFF.

And INTPO interruption occurs when write operation to specified SFR was executed with protection ON state.

(5) Runaway provision with ROM protection register

#### (Purpose)

Provision in runaway of program by noise mixing.

#### (Operation explanation)

When write operation was executed for external three kinds of ROM by runaway of program, INTP1 is occurred and detects runaway function.

Three kinds of ROM is fixed as for Flash ROM (Option program ROM), Data ROM, Program ROM are as follows on the logical address memory map.

| 1. Flash ROM:   | Address 400000H to 7FFFFFH |

|-----------------|----------------------------|

| 2. Data ROM:    | Address 800000H to BFFFFFH |

| 3. Program ROM: | Address C00000H to FFFFFFH |

For these address, admission/prohibition of detection of write operation sets it up with EMCCR3<ENFROM, ENDROM, ENPROM>. And INTP1 interruption occurred within which ROM area in the case that occurred can confirm each with EMCCR3<FFLAG, DFLAG, PFLAG>. This flag is cleared when write in 0.

#### 3.3.7 Standby Controller

(1) HALT modes

When the HALT instruction is executed, the operating mode switches to IDLE2, IDLE1 or STOP mode, depending on the contents of the SYSCR2<HALTM1:0> register.

The subsequent actions performed in each mode are as follows:

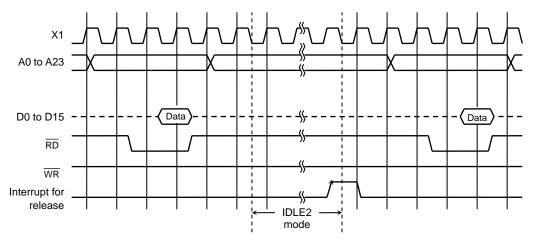

a. IDLE2: Only the CPU halts.

The internal I/O is available to select operation during IDLE2 mode. By setting the following register.

Table 3.3.2 Shows the registers of setting operation during IDLE2 mode.

| Internal I/O | SFR                       |

|--------------|---------------------------|

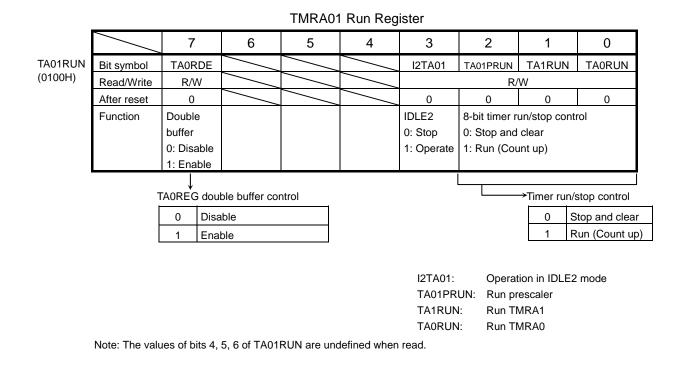

| TMRA01       | TA01RUN <i2ta01></i2ta01> |

| TMRA23       | TA23RUN <i2ta23></i2ta23> |

| SIO0         | SC0MOD1 <i2s0></i2s0>     |

| SIO1         | SC1MOD1 <i2s1></i2s1>     |

| AD converter | ADMOD1 <i2ad></i2ad>      |

| WDT          | WDMOD <i2wdt></i2wdt>     |

Table 3.3.2 SFR Setting Operation during IDLE2 Mode

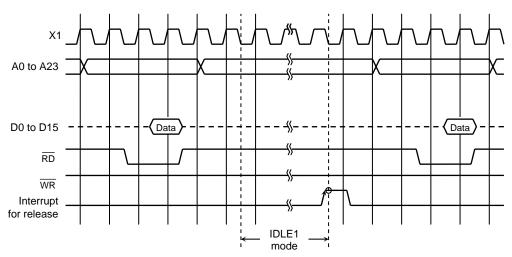

- b. IDLE1: Only the oscillator and the RTC (Real-time clock) and MLD continue to operate.

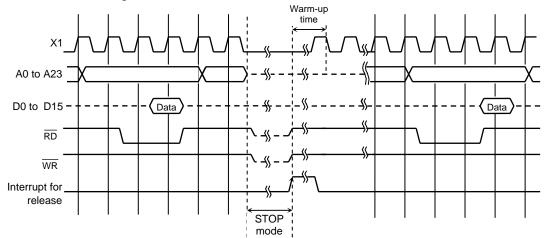

- c. STOP: All internal circuits stop operating.

The operation of each of the different HALT modes is described in Table 3.3.3.

| HALT Mode                    |                      | IDLE2                                                  | IDLE1               | STOP       |

|------------------------------|----------------------|--------------------------------------------------------|---------------------|------------|

| SYSCR2 <haltm1:0></haltm1:0> |                      | 11                                                     | 10                  | 01         |

|                              | CPU                  | Stop                                                   |                     |            |

|                              | I/O ports            | Keep the state when the HALT instruction was executed. | See Table 3.3.6, T  | able 3.3.7 |

|                              | TMRA                 |                                                        |                     |            |

| Block                        | SIO                  | Available to select                                    |                     |            |

| AD converter                 |                      | operation block                                        | Stop                |            |

|                              | WDT                  |                                                        | Зюр                 |            |

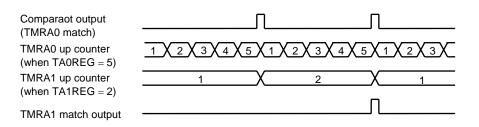

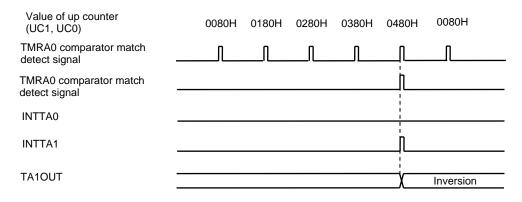

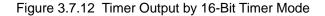

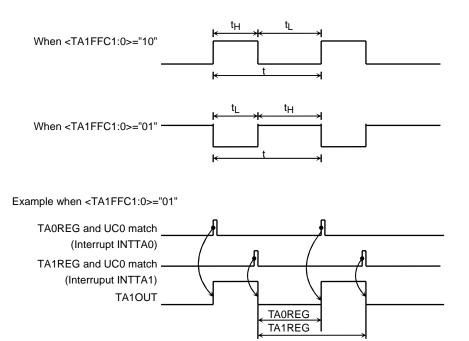

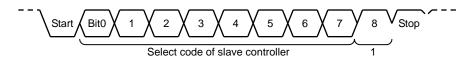

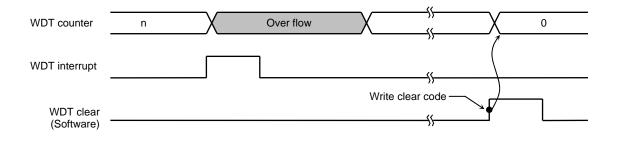

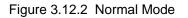

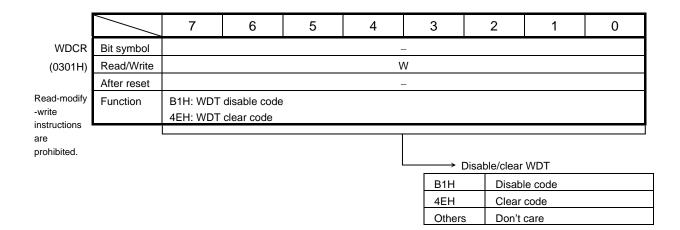

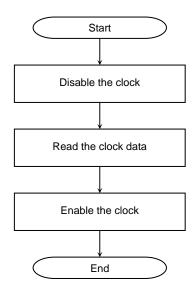

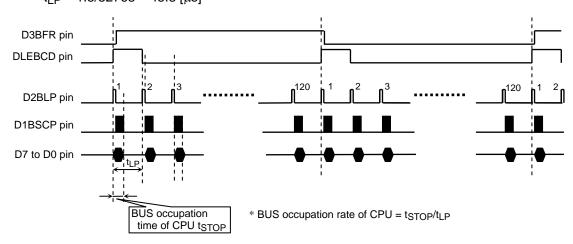

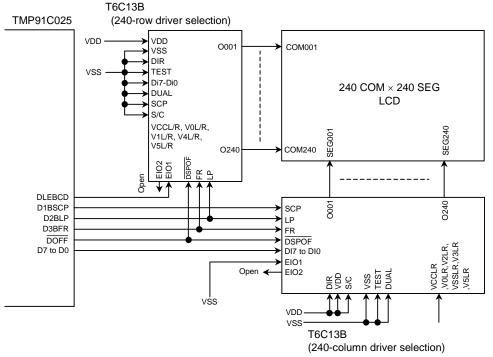

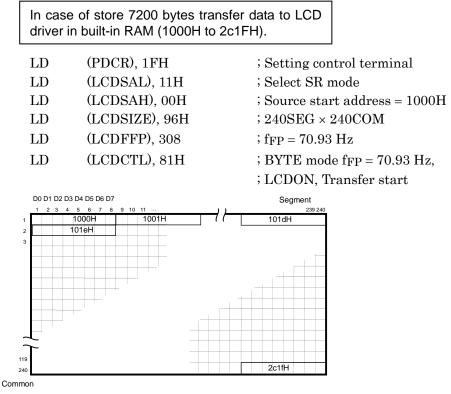

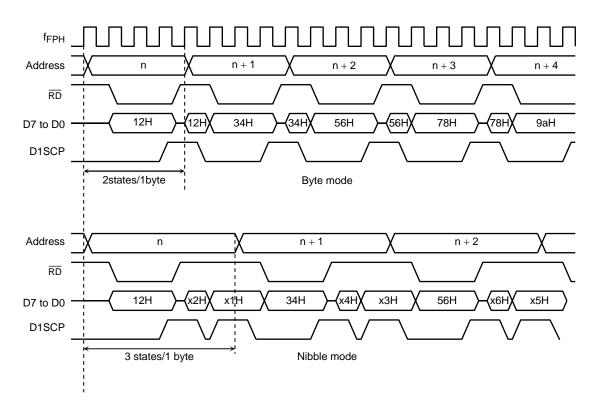

|                              | LCDC,                |                                                        |                     |            |