**TPA3124D2**

www.ti.com SLOS578-MAY 2008

## 15-W STEREO CLASS-D AUDIO POWER AMPLIFIER

#### **FEATURES**

- 10-W/Ch Into an 8-Ω Load From a 24-V Supply

- 15-W/Ch into a 4-Ω Load from a 22-V Supply

- 30-W/Ch into a 8-Ω Load from a 22-V Supply

- Operates From 10 V to 26 V

- Can Run From +24 V LCD Backlight Supply

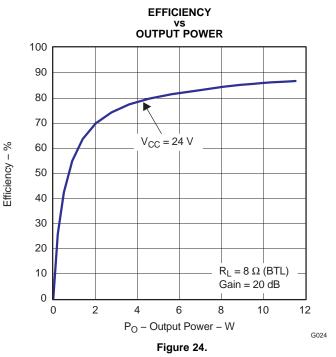

- Efficient Class-D Operation Eliminates Need for Heat Sinks

- Four Selectable, Fixed-Gain Settings

- Internal Oscillator (No External Components Required)

- Single-Ended Analog Inputs

- Thermal and Short-Circuit Protection With Auto Recovery

- Space-Saving Surface Mount 24-Pin TSSOP Package

- Advanced Power-Off Pop Reduction

#### APPLICATIONS

- Flat Panel Televisions

- DLP® TVs

- CRT TVs

- Powered Speakers

#### DESCRIPTION

The TPA3124D2 is a 15-W (per channel), efficient, class-D audio power amplifier for driving stereo speakers in a single-ended configuration; or, a mono speaker in a bridge-tied-load configuration. The TPA3124D2 can drive stereo speakers as low as 4  $\Omega$ . The efficiency of the TPA3124D2 eliminates the need for an external heat sink when playing music.

The gain of the amplifier is controlled by two gain select pins. The gain selections are 20, 26, 32, and 36 dB.

The patented start-up and shutdown sequences minimize pop noise in the speakers without additional circuitry.

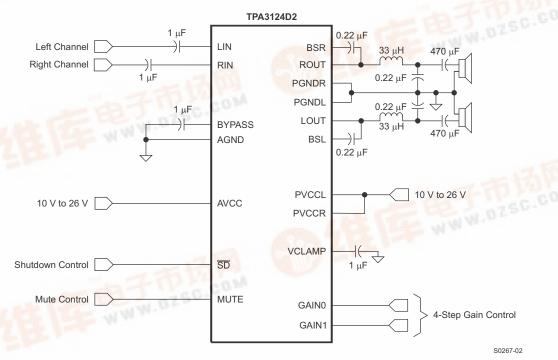

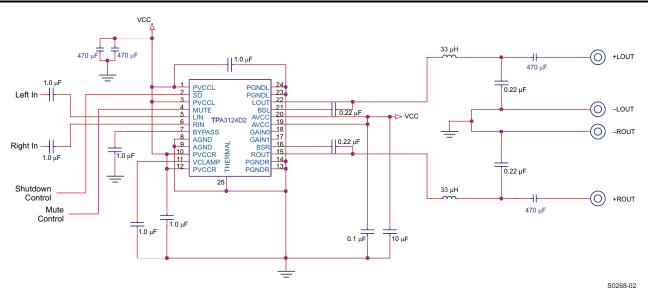

#### SIMPLIFIED APPLICATION CIRCUIT

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

Pis a registered trademark of Texas Instruments.

System Two, Audio Precision are trademarks of Audio Precision, Inc. All other trademarks are the property of their respective owners.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

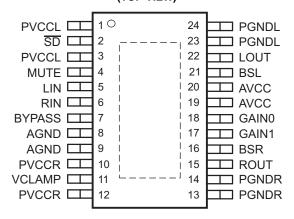

# PWP (TSSOP) PACKAGE (TOP VIEW)

**Table 1. TERMINAL FUNCTIONS**

| TERMINAL    |                 |       |                                                                                                                                                            |  |  |  |  |

|-------------|-----------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| NAME        | 24-PIN<br>(PWP) | I/O/P | DESCRIPTION                                                                                                                                                |  |  |  |  |

| SD          | 2               | I     | Shutdown signal for IC (low = disabled, high = operational). TTL logic levels with compliance to AVCC                                                      |  |  |  |  |

| RIN         | 6               | I     | Audio input for right channel                                                                                                                              |  |  |  |  |

| LIN         | 5               | I     | Audio input for left channel                                                                                                                               |  |  |  |  |

| GAIN0       | 18              | I     | Gain select least-significant bit. TTL logic levels with compliance to AVCC                                                                                |  |  |  |  |

| GAIN1       | 17              | I     | Gain select most-significant bit. TTL logic levels with compliance to AVCC                                                                                 |  |  |  |  |

| MUTE        | 4               | ı     | Mute signal for quick disable/enable of outputs (high = outputs switch at 50% duty cycle, low = outputs enabled). TTL logic levels with compliance to AVCC |  |  |  |  |

| BSL         | 21              | I/O   | Bootstrap I/O for left channel                                                                                                                             |  |  |  |  |

| PVCCL       | 1, 3            | Р     | Power supply for left-channel H-bridge, not internally connected to PVCCR or AVCC                                                                          |  |  |  |  |

| LOUT        | 22              | 0     | Class-D -H-bridge positive output for left channel                                                                                                         |  |  |  |  |

| PGNDL       | 23, 24          | Р     | Power ground for left-channel H-bridge                                                                                                                     |  |  |  |  |

| VCLAMP      | 11              | Р     | Internally generated voltage supply for bootstrap capacitors                                                                                               |  |  |  |  |

| BSR         | 16              | I/O   | Bootstrap I/O for right channel                                                                                                                            |  |  |  |  |

| ROUT        | 15              | 0     | Class-D -H-bridge negative output for right channel                                                                                                        |  |  |  |  |

| PGNDR       | 13, 14          | Р     | Power ground for right-channel H-bridge.                                                                                                                   |  |  |  |  |

| PVCCR       | 10, 12          | Р     | Power supply for right-channel H-bridge, not connected to PVCCL or AVCC                                                                                    |  |  |  |  |

| AGND        | 9               | Р     | Analog ground for digital/analog cells in core                                                                                                             |  |  |  |  |

| AGND        | 8               | Р     | Analog ground for analog cells in core                                                                                                                     |  |  |  |  |

| BYPASS      | 7               | 0     | Reference for preamplifier inputs. Nominally equal to AVCC/8. Also controls start-up time via external capacitor sizing.                                   |  |  |  |  |

| AVCC        | 19, 20          | Р     | High-voltage analog power supply. Not internally connected to PVCCR or PVCCL                                                                               |  |  |  |  |

| Thermal pad | Die pad         | Р     | Connect to ground. Thermal pad should be soldered down on all applications to secure the device properly to the printed wiring board.                      |  |  |  |  |

2

#### **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted) (1)

|                  |                                      |                                 | VALUE                        | UNIT |

|------------------|--------------------------------------|---------------------------------|------------------------------|------|

| V <sub>CC</sub>  | Supply voltage                       | AVCC, PVCC                      | -0.3 to 30                   | V    |

| $V_{I}$          | Logic input voltage                  | SD, MUTE, GAINO, GAIN1          | $-0.3$ to $V_{CC} + 0.3$     | V    |

| $V_{IN}$         | Analog input voltage                 | RIN, LIN                        | -0.3 to 7                    | V    |

|                  | Continuous total power dissipation   |                                 | See Dissipation Rating Table |      |

| T <sub>A</sub>   | Operating free-air temperature range |                                 | -40 to 85                    | °C   |

| TJ               | Operating junction temperature range |                                 | -40 to 150                   | °C   |

| T <sub>stg</sub> | Storage temperature range            |                                 | -65 to 150                   | °C   |

| D                | Load resistance (minimum value)      | SE Output Configuration         | 3.2                          | Ω    |

| $R_L$            | Load resistance (minimum value)      | BTL Output Configuration        | 6.4                          | 12   |

|                  |                                      | Human body model (all pins)     | ±2                           | kV   |

| ESD              | Electrostatic Discharge              | Charged-device model (all pins) | ±500                         | V    |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### **DISSIPATION RATINGS**

| PACKAGE <sup>(1)(2)</sup> | T <sub>A</sub> ≤ 25°C | DERATING FACTOR | T <sub>A</sub> = 70°C | T <sub>A</sub> = 85°C |

|---------------------------|-----------------------|-----------------|-----------------------|-----------------------|

| 24-pin TSSOP              | 4.16 W                | 33.3 mW/°C      | 2.67 W                | 2.16 W                |

<sup>(1)</sup> For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI website at www.ti.com.

#### RECOMMENDED OPERATING CONDITIONS

|                 |                                |                                                            | MIN | MAX | UNIT |

|-----------------|--------------------------------|------------------------------------------------------------|-----|-----|------|

| V <sub>CC</sub> | Supply voltage                 | PVCC, AVCC                                                 | 10  | 26  | V    |

| V <sub>IH</sub> | High-level input voltage       | SD, MUTE, GAIN0, GAIN1                                     | 2   |     | V    |

| V <sub>IL</sub> | Low-level input voltage        | SD, MUTE, GAINO, GAIN1                                     |     | 0.8 | V    |

|                 |                                | $\overline{SD}$ , $V_1 = V_{CC}$ , $V_{CC} = 30 \text{ V}$ |     | 125 |      |

| I <sub>IH</sub> | High-level input current       | MUTE, $V_I = V_{CC}$ , $V_{CC} = 30 \text{ V}$             |     | 125 | μΑ   |

|                 |                                | GAIN0, GAIN1, $V_I = V_{CC}$ , $V_{CC} = 24 \text{ V}$     |     | 125 |      |

|                 |                                | $\overline{SD}$ , $V_I = 0$ , $V_{CC} = 30 \text{ V}$      |     | 1   |      |

| I <sub>IL</sub> | Low-level input current        | MUTE, $V_I = 0 \text{ V}$ , $V_{CC} = 30 \text{ V}$        |     | 1   | μΑ   |

|                 |                                | GAIN0, GAIN1, V <sub>I</sub> = 0 V, V <sub>CC</sub> = 24 V |     | 1   |      |

| T <sub>A</sub>  | Operating free-air temperature |                                                            | -40 | 85  | °C   |

<sup>(2)</sup> This data was taken using 1 oz trace and copper pad that is soldered directly to a JEDEC standard high-k PCB. The thermal pad must be soldered to a thermal land on the printed-circuit board. See the *PowerPAD Thermally Enhanced Package* application note (SLMA002).

#### **DC CHARACTERISTICS**

$T_{A}$  = 25°C,  $V_{CC}$  = 24 V,  $R_{L}$  =8 $\Omega$  (unless otherwise noted)

|                       | PARAMETER                                                                                       | TEST CON                                         | DITIONS       | MIN | TYP    | MAX | UNIT |

|-----------------------|-------------------------------------------------------------------------------------------------|--------------------------------------------------|---------------|-----|--------|-----|------|

| Vos                   | Class-D output offset voltage<br>(measured differentially in BTL<br>mode as shown in Figure 36) | $V_I = 0 \text{ V}, \text{ A}_V = 36 \text{ dB}$ |               |     | 7.5    | 50  | mV   |

| V <sub>(BYPASS)</sub> | Bypass output voltage                                                                           | No load                                          |               |     | AVCC/8 |     | V    |

| I <sub>CC(q)</sub>    | Quiescent supply current                                                                        | <u>SD</u> = 2 V, MUTE = 0 V                      | , no load     |     | 16     | 30  | mA   |

| I <sub>CC(q)</sub>    | Quiescent supply current in mute mode                                                           | MUTE = 0.8 V, no load                            |               | 16  |        | mA  |      |

| I <sub>CC(q)</sub>    | Quiescent supply current in shutdown mode                                                       | SD = 0.8 V, no load                              |               |     | 0.39   | 1   | mA   |

| r <sub>DS(on)</sub>   | Drain-source on-state resistance                                                                |                                                  |               |     | 210    | 450 | mΩ   |

|                       |                                                                                                 | CAINA OOV                                        | GAIN0 = 0.8 V | 18  | 20     | 22  |      |

| 0                     | On-i                                                                                            | GAIN1 = 0.8 V                                    | GAIN0 = 2 V   | 24  | 26     | 28  | ٦D   |

| G                     | Gain                                                                                            | CAIN OV                                          | GAIN0 = 0.8 V | 30  | 32     | 34  | dB   |

|                       |                                                                                                 | GAIN = 2 V<br>GAIN0 = 2 V                        |               | 34  | 36     | 38  |      |

|                       | Mute attenuation                                                                                | V <sub>I</sub> = 1 Vrms                          |               | -80 |        | dB  |      |

#### **AC CHARACTERISTICS**

$T_{A}$  = 25°C,  $V_{CC}$  = 24 V,  $R_{L}$  =  $8\Omega$  (unless otherwise noted)

|                | PARAMETER                         | TEST CONDITION                                     | S          | MIN | TYP   | MAX | UNIT |

|----------------|-----------------------------------|----------------------------------------------------|------------|-----|-------|-----|------|

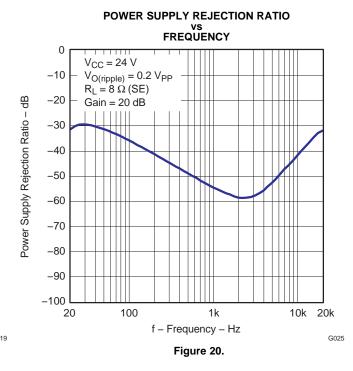

| l. a. m        | Complete visual and a settle se   | $V_{CC} = 24$ , $V_{ripple} = 200 \text{ mV}_{PP}$ | 100 Hz     |     | -48   |     | J.   |

| ksvr           | Supply ripple rejection           | Gain = 20 dB                                       | 1 kHz      |     | -52   |     | dB   |

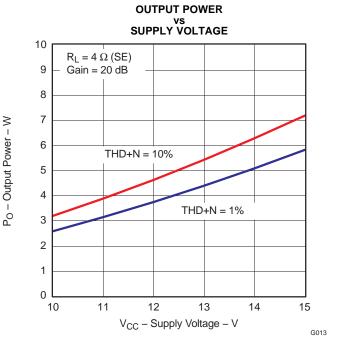

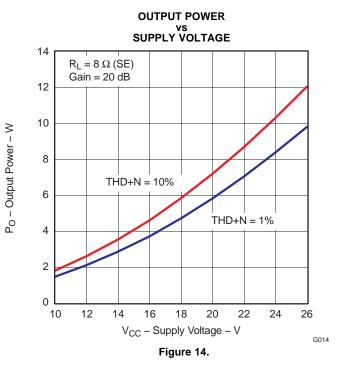

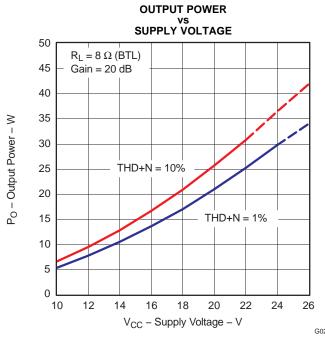

| Б              | Output power at 1% THD+N          | V <sub>CC</sub> = 24 V, f = 1 kHz                  |            |     | 8     |     |      |

| Po             | Output power at 10% THD+N         | V <sub>CC</sub> = 24 V, f = 1 kHz                  |            |     | 10    |     | W    |

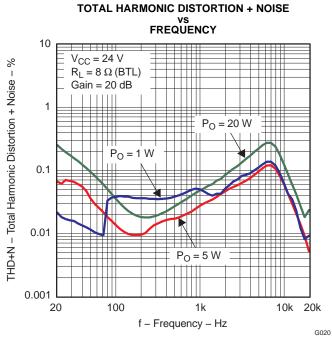

| THD+N          | Total harmonic distortion + noise | f = 1 kHz, P <sub>O</sub> = 5 W                    |            |     | 0.04% |     |      |

| V              | Output integrated paigs floor     | 20 Hz to 22 kHz, A-weighted fi                     | Iter,      |     | 125   |     | μV   |

| V <sub>n</sub> | Output integrated noise floor     | Gain = 20 dB                                       |            |     | -78   |     | dBV  |

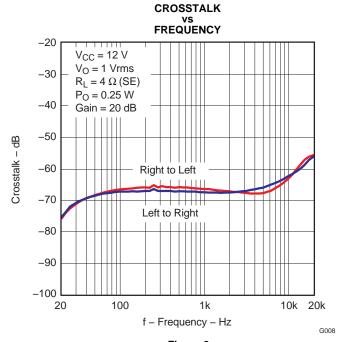

|                | Crosstalk                         | P <sub>O</sub> = 1 W, f = 1 kHz; gain = 20         | dB         |     | -70   |     | dB   |

| SNR            | Signal-to-noise ratio             | Max output at THD+N < 1%, f gain = 20 dB           | = 1 kHz,   |     | -92   |     | dB   |

|                | Thermal trip point                |                                                    |            |     | 150   |     | O°   |

|                | Thermal hysteresis                |                                                    |            |     | 30    |     | °C   |

| fosc           | Oscillator frequency              |                                                    |            | 250 | 300   | 350 | kHz  |

| Δt mute        | Mute delay                        | Time from mute input switches outputs muted        | high until |     | 30    |     | μsec |

| Δt unmute      | Unmute delay                      | Time from mute input switches outputs unmuted      | low until  |     | 120   |     | msec |

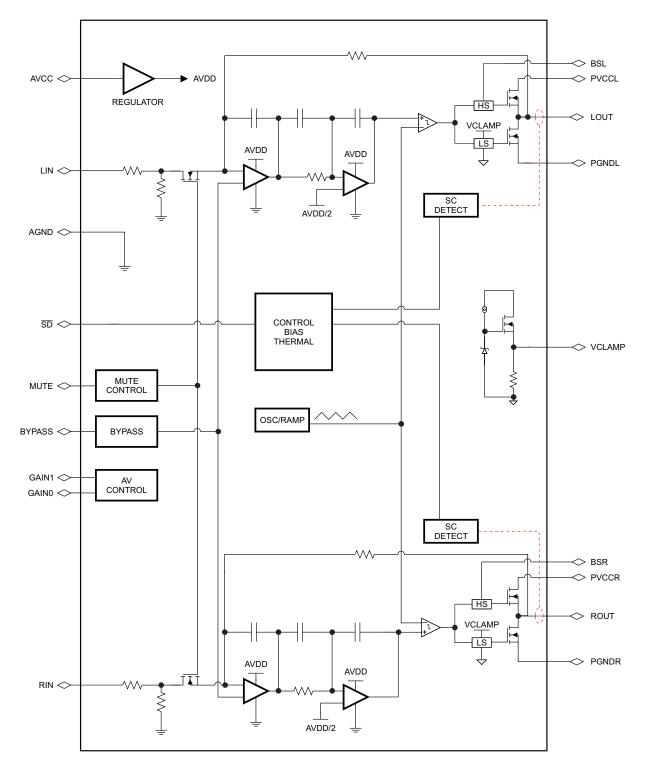

#### **FUNCTIONAL BLOCK DIAGRAM**

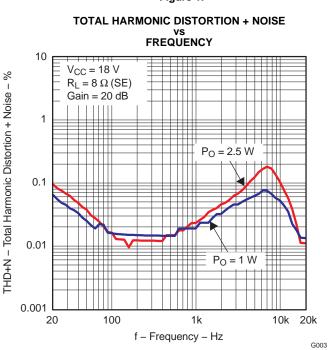

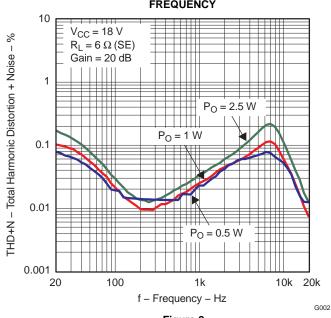

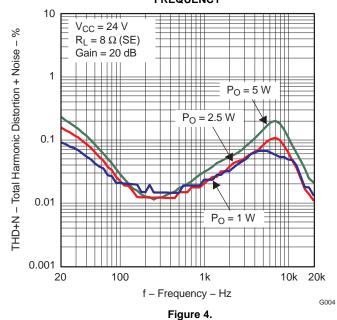

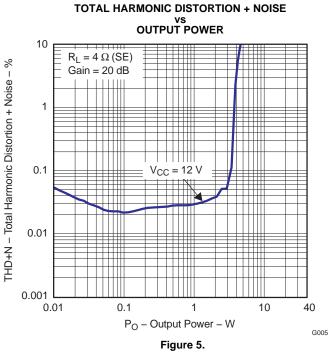

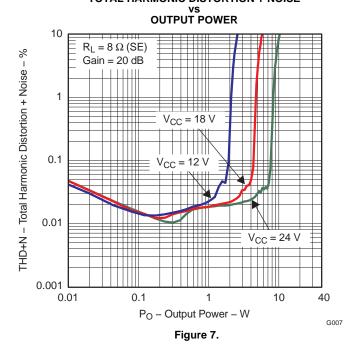

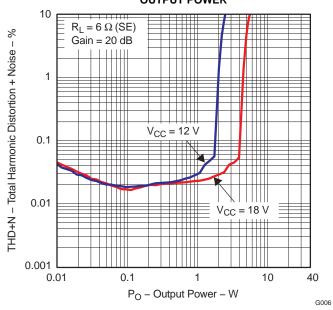

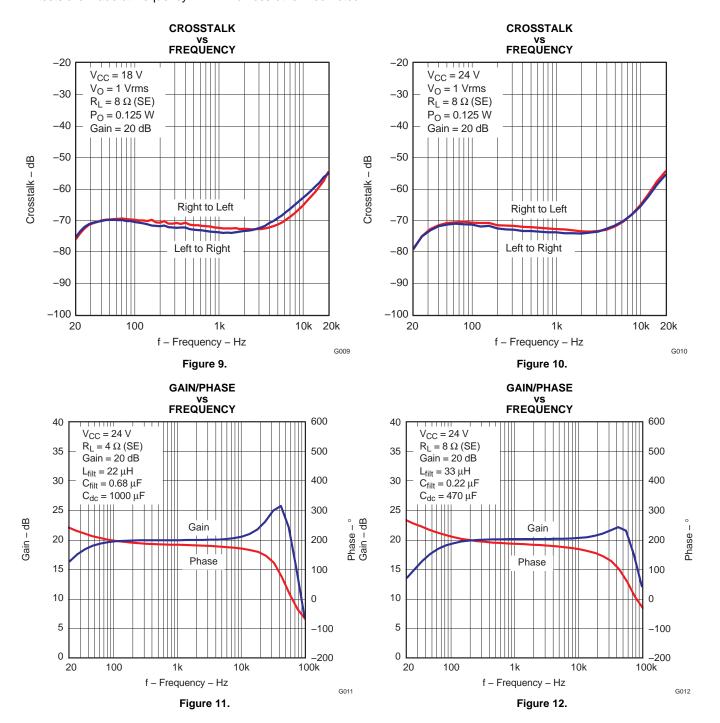

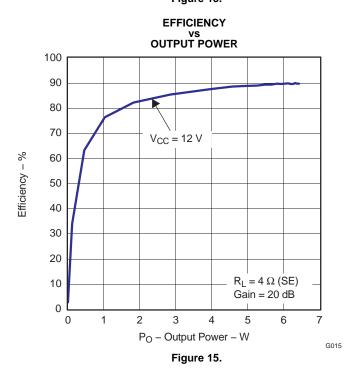

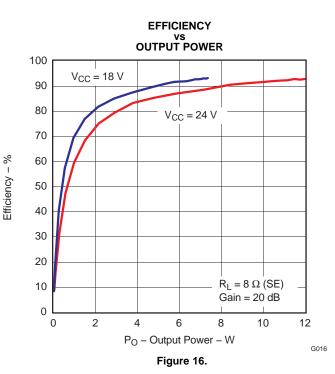

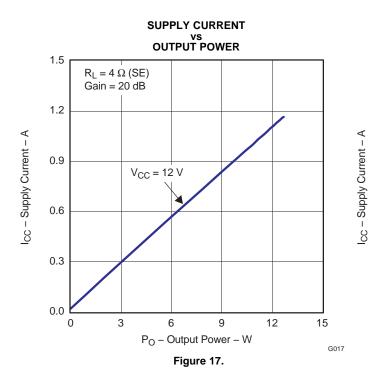

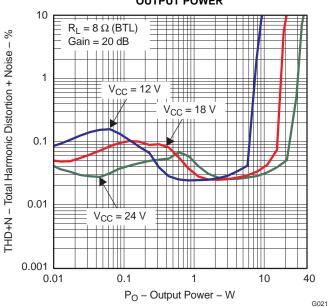

#### TYPICAL CHARACTERISTICS

All tests are made at frequency = 1 kHz unless otherwise noted.

### **TOTAL HARMONIC DISTORTION + NOISE** vs FREQUENCY 10 $V_{CC} = 12 V$ THD+N - Total Harmonic Distortion + Noise - % $R_L = 4 \Omega (SE)$ Gain = 20 dB $P_0 = 2.5 \text{ W}$ $P_0 = 1 W$ 0.1 0.01 $P_0 = 0.5 \text{ W}$ 0.001 20 100 1k 10k 20k f - Frequency - Hz G001

Figure 1.

Figure 3.

### **TOTAL HARMONIC DISTORTION + NOISE** vs FREQUENCY

Figure 2.

## **TOTAL HARMONIC DISTORTION + NOISE** vs FREQUENCY

#### **TYPICAL CHARACTERISTICS (continued)**

All tests are made at frequency = 1 kHz unless otherwise noted.

TOTAL HARMONIC DISTORTION + NOISE

# TOTAL HARMONIC DISTORTION + NOISE

Figure 6.

Figure 8.

#### **TYPICAL CHARACTERISTICS (continued)**

All tests are made at frequency = 1 kHz unless otherwise noted.

#### **TYPICAL CHARACTERISTICS (continued)**

All tests are made at frequency = 1 kHz unless otherwise noted.

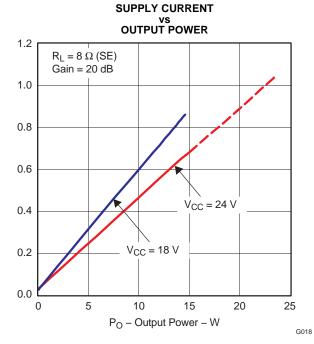

Dashed line represents thermally limited region.

Figure 13.

#### **TYPICAL CHARACTERISTICS (continued)**

All tests are made at frequency = 1 kHz unless otherwise noted.

Dashed line represents thermally limited region.

Figure 18.

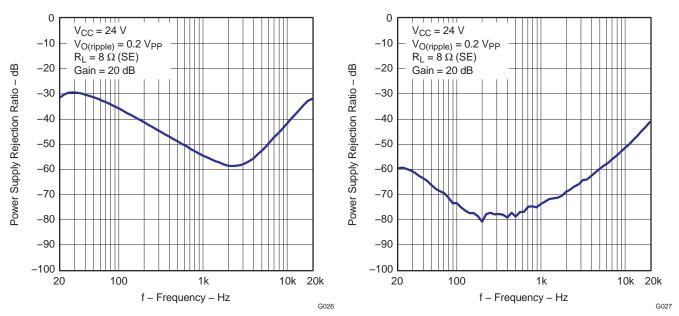

#### **POWER SUPPLY REJECTION RATIO** vs FREQUENCY 0 V<sub>CC</sub> = 24 V $V_{O(ripple)} = 0.2 V_{PP}$ $R_L = 4 \Omega (SE)$ -10Power Supply Rejection Ratio - dB -20 Gain = 20 dB -30-40 -50 -60 -70 -80 -90 -100 100 1k 10k 20k 20 f - Frequency - Hz G019 Figure 19.

#### **TYPICAL CHARACTERISTICS (continued)**

All tests are made at frequency = 1 kHz unless otherwise noted.

Figure 21.

A. Dashed line represents thermally limited region.

Figure 23.

# TOTAL HARMONIC DISTORTION + NOISE vs OUTPUT POWER

Figure 22.

#### **APPLICATION INFORMATION**

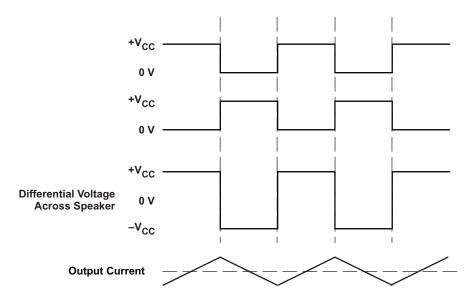

#### **CLASS-D OPERATION**

This section focuses on the class-D operation of the TPA3124D2.

#### **Traditional Class-D Modulation Scheme**

The TPA3124D2 operates in AD mode. There are two main configurations that may be used. For stereo operation, the TPA3124D2 should be configured in a single-ended (SE) half-bridge amplifier. For mono applications, TPA3124D2 may be used as a bridge-tied-load (BTL) amplifier. The traditional class-D modulation scheme, which is used in the TPA3124D2 BTL configuration, has a differential output where each output is 180 degrees out of phase and changes from ground to the supply voltage,  $V_{CC}$ . Therefore, the differential prefiltered output varies between positive and negative  $V_{CC}$ , where filtered 50% duty cycle yields 0 V across the load. The class-D modulation scheme with voltage and current waveforms is shown in Figure 25 and Figure 26.

Figure 25. Class-D Modulation for TPA3124D2 SE Configuration

Figure 26. Class-D Modulation for TPA3124D2 BTL Configuration

#### Supply Pumping

One issue encountered in single-ended (SE) class-D amplifier designs is supply pumping. Power-supply pumping is a rise in the local supply voltage due to energy being driven back to the supply by operation of the class-D amplifier. This phenomenon is most evident at low audio frequencies and when both channels are operating at the same frequency and phase. At low levels, power-supply pumping results in distortion in the audio output due to fluctuations in supply voltage. At higher levels, pumping can cause the overvoltage protection to operate, which temporarily shuts down the audio output.

Texas

Instruments

Several things can be done to relieve power-supply pumping. The lowest impact is to operate the two inputs out of phase 180° and reverse the speaker connections. Because most audio is highly correlated, this causes the supply pumping to be out of phase and not as severe. If this is not enough, the amount of bulk capacitance on the supply must be increased. Also, improvement is realized by hooking other supplies to this node, thereby, sinking some of the excess current. Power-supply pumping should be tested by operating the amplifier at low frequencies and high output levels.

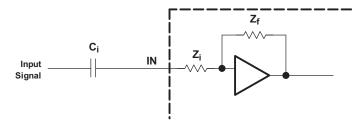

#### Gain Setting via GAIN0 and GAIN1 Inputs

The gain of the TPA3124D2 is set by two input terminals, GAIN0 and GAIN1.

The gains listed in Table 2 are realized by changing the taps on the input resistors and feedback resistors inside the amplifier. This causes the input impedance  $(Z_I)$  to be dependent on the gain setting. The actual gain settings are controlled by ratios of resistors, so the gain variation from part-to-part is small. However, the input impedance from part-to-part at the same gain may shift by  $\pm 20\%$  due to shifts in the actual resistance of the input resistors.

For design purposes, the input network (discussed in the next section) should be designed assuming an input impedance of 8 k $\Omega$ , which is the absolute minimum input impedance of the TPA3124D2. At the higher gain settings, the input impedance could increase as high as 72 k $\Omega$ .

|       |       | J                               |                                  |

|-------|-------|---------------------------------|----------------------------------|

| GAIN1 | GAIN0 | AMPLIFIER GAIN (dB),<br>TYPICAL | INPUT IMPEDANCE (kΩ),<br>TYPICAL |

| 0     | 0     | 20                              | 60                               |

| 0     | 1     | 26                              | 30                               |

| 1     | 0     | 32                              | 15                               |

| 1     | 1     | 36                              | 9                                |

Table 2. Gain Setting

#### **INPUT RESISTANCE**

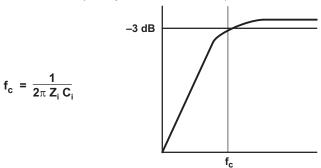

Changing the gain setting can vary the input resistance of the amplifier from its smallest value, 10 k $\Omega$  ±20%, to the largest value, 60 k $\Omega$  ±20%. As a result, if a single capacitor is used in the input high-pass filter, the -3-dB cutoff frequency may change when changing gain steps.

The -3-dB frequency can be calculated using Equation 1. Use the  $Z_I$  values given in Table 2.

$$f = \frac{1}{2\pi Z_i C_i} \tag{1}$$

(2)

SLOS578-MAY 2008 www.ti.com

#### INPUT CAPACITOR, C,

In the typical application, input capacitor  $C_l$  is required to allow the amplifier to bias the input signal to the proper dc level for optimum operation. In this case  $C_l$  and the input impedance of the amplifier  $(Z_l)$  form a high-pass filter with the corner frequency determined in Equation 2.

The value of  $C_l$  is important, as it directly affects the bass (low-frequency) performance of the circuit. Consider the example where  $Z_l$  is 20 k $\Omega$  and the specification calls for a flat bass response down to 20 Hz. Equation 2 is reconfigured as Equation 3.

$$C_i = \frac{1}{2\pi Z_i f_c} \tag{3}$$

In this example,  $C_l$  is  $0.4~\mu F$ ; so, one would likely choose a value of  $0.47~\mu F$  as this value is commonly used. If the gain is known and is constant, use  $Z_l$  from Table 2 to calculate  $C_l$ . A further consideration for this capacitor is the leakage path from the input source through the input network,  $C_l$ , and the feedback network to the load. This leakage current creates a dc offset voltage at the input to the amplifier that reduces useful headroom, especially in high-gain applications. For this reason, a low-leakage tantalum or ceramic capacitor is the best choice. When polarized capacitors are used, the positive side of the capacitor should face the amplifier input in most applications as the dc level there is held at 2 V, which is likely higher than the source dc level. Note that it is important to confirm the capacitor polarity in the application. Additionally, lead-free solder can create dc offset voltages, and it is important to ensure that boards are cleaned properly.

#### Single-Ended Output Capacitor, Co

In single-ended (SE) applications, the dc blocking capacitor forms a high-pass filter with the speaker impedance. The frequency response rolls off with decreasing frequency at a rate of 20 dB/decade. The cutoff frequency is determined by

$$f_c = \pi C_O Z_L$$

Table 3 shows some common component values and the associated cutoff frequencies:

C<sub>SE</sub> - DC Blocking Capacitor (μF)

$f_c = 60 \text{ Hz } (-3 \text{ dB})$   $f_c = 40 \text{ Hz } (-3 \text{ dB})$   $f_c = 20 \text{ Hz } (-3 \text{ dB})$

4

680

1000

2200

6

470

680

1500

8

330

470

1000

Table 3. Common Filter Responses

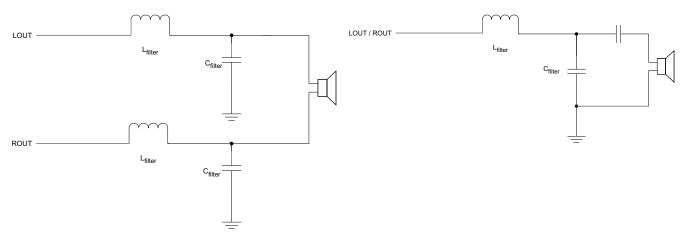

#### **Output Filter and Frequency Response**

For the best frequency response, a flat-passband output filter (second-order Butterworth) may be used. The output filter components consist of the series inductor and capacitor to ground at the LOUT and ROUT pins. There are several possible configurations, depending on the speaker impedance and whether the output configuration is single-ended (SE) or bridge-tied load (BTL). Table 4 lists the recommended values for the filter components. It is important to use a high-quality capacitor in this application. A rating of at least X7R is required.

#### **Table 4. Recommended Filter Output Components**

| Output Configuration   | Speaker Impedance (Ω) | Filter Inductor (μH) | Filter Capacitor (nF) |

|------------------------|-----------------------|----------------------|-----------------------|

| Cingle Ended (CE)      | 4                     | 22                   | 680                   |

| Single Ended (SE)      | 8                     | 33                   | 220                   |

| Bridge Tied Load (BTL) | 8                     | 22                   | 680                   |

Figure 27. BTL Filter Configuration

Figure 28. SE Filter Configuration

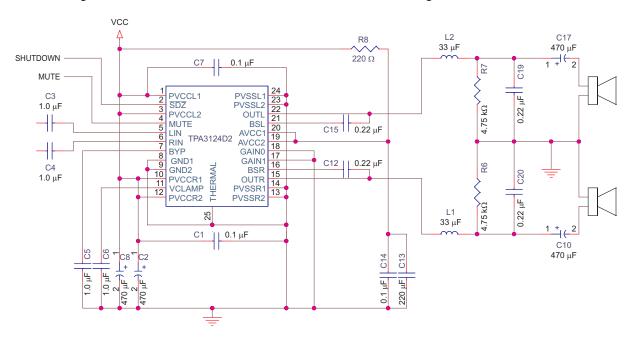

#### Power-Supply Decoupling, C<sub>S</sub>

The TPA3124D2 is a high-performance CMOS audio amplifier that requires adequate power-supply decoupling to ensure that the output total harmonic distortion (THD) is as low as possible. Power-supply decoupling also prevents oscillations for long lead lengths between the amplifier and the speaker. The optimum decoupling is achieved by using two capacitors of different types that target different types of noise on the power-supply leads. For higher-frequency transients, spikes, or digital hash on the line, a good low equivalent-series-resistance (ESR) ceramic capacitor, typically 0.1  $\mu F$  to 1  $\mu F$ , placed as close as possible to the device  $V_{CC}$  lead works best. For filtering lower frequency noise signals, a larger aluminum electrolytic capacitor of 470  $\mu F$  or greater placed near the audio power amplifier is recommended. The 470- $\mu F$  capacitor also serves as local storage capacitor for supplying current during large signal transients on the amplifier outputs. The PVCC terminals provide the power to the output transistors, so a 470- $\mu F$  or larger capacitor should be placed on each PVCC terminal. A 10- $\mu F$  capacitor on the AVCC terminal is adequate. These capacitors must be properly derated for voltage and ripple-current rating to ensure reliability.

Figure 29. PSRR Without AVCC Filter

Figure 30. PSRR With AVCC Filter

Figure 31. Application Schematic with 220- $\Omega$ /220- $\mu$ F AVCC Filter

#### **BSN** and **BSP** Capacitors

The half H-bridge output stages use only NMOS transistors. Therefore, they require bootstrap capacitors for the high side of each output to turn on correctly. A 220-nF ceramic capacitor, rated for at least 25 V, must be connected from each output to its corresponding bootstrap input. Specifically, one 220-nF capacitor must be connected from LOUT to BSL, and one 220-nF capacitor must be connected from ROUT to BSR.

The bootstrap capacitors connected between the BSx pins and their corresponding outputs function as a floating power supply for the high-side N-channel power MOSFET gate-drive circuitry. During each high-side switching cycle, the bootstrap capacitors hold the gate-to-source voltage high enough to keep the high-side MOSFETs turned on.

#### **VCLAMP** Capacitor

To ensure that the maximum gate-to-source voltage for the NMOS output transistors is not exceeded, one internal regulator clamps the gate voltage. One 1- $\mu$ F capacitor must be connected from VCLAMP (pin 11) to ground and must be rated for at least 16 V. The voltages at the VCLAMP terminal may vary with V<sub>CC</sub> and may not be used for powering any other circuitry.

#### **VBYP Capacitor Selection**

The scaled supply reference (VBYP) nominally provides an AVCC/8 internal bias for the preamplifier stages. The external capacitor for this reference,  $C_{BYP}$ , is a critical component and serves several important functions. During start-up or recovery from shutdown mode,  $C_{BYP}$  determines the rate at which the amplifier starts. The start up time is proportional to 0.5 s per microfarad. Thus, the recommended 1- $\mu$ F capacitor results in a start-up time of approximately 500 ms. The second function is to reduce noise produced by the power supply caused by coupling with the output drive signal. This noise could result in degraded power-supply rejection and THD+N.

The circuit is designed for a  $C_{BYP}$  value of 1  $\mu F$  for best pop performance. The input capacitors should have the same value. A ceramic or tantalum low-ESR capacitor is recommended.

#### SHUTDOWN OPERATION

The TPA3124D2 employs a shutdown mode of operation designed to reduce supply current (I<sub>CC</sub>) to the absolute minimum level during periods of nonuse for power conservation. The SHUTDOWN input terminal should be held high (see specification table for trip point) during normal operation when the amplifier is in use. Pulling SHUTDOWN low causes the outputs to mute and the amplifier to enter a low-current state. Never leave SHUTDOWN unconnected, because amplifier operation would be unpredictable.

For the best power-up *pop* performance, place the amplifier in the shutdown or mute mode prior to applying the power-supply voltage.

#### **MUTE Operation**

The MUTE pin is an input for controlling the output state of the TPA3124D2. A logic high on this terminal causes the outputs to run at a constant 50% duty cycle. A logic low on this pin enables the outputs. This terminal may be used as a quick disable/enable of outputs when changing channels on a television or transitioning between different audio sources.

The MUTE terminal should never be left floating. For power conservation, the SHUTDOWN terminal should be used to reduce the guiescent current to the absolute minimum level.

#### **USING LOW-ESR CAPACITORS**

Low-ESR capacitors are recommended throughout this application section. A real (as opposed to ideal) capacitor can be modeled simply as a resistor in series with an ideal capacitor. The voltage drop across this resistor minimizes the beneficial effects of the capacitor in the circuit. The lower the equivalent value of this resistance, the more the real capacitor behaves like an ideal capacitor.

#### **SHORT-CIRCUIT PROTECTION**

The TPA3124D2 has short-circuit protection circuitry on the outputs that prevents damage to the device during output-to-output shorts and output-to-GND shorts after the filter and output capacitor (at the speaker terminal.) Directly at the device terminals, the protection circuitry prevents damage to device during output-to-output, output-to-ground, and output-to-supply. When a short circuit is detected on the outputs, the part immediately disables the output drive. This is an unlatched fault. Normal operation is restored when the fault is removed.

#### THERMAL PROTECTION

Thermal protection on the TPA3124D2 prevents damage to the device when the internal die temperature exceeds  $150^{\circ}$ C. There is a  $\pm 15^{\circ}$ C tolerance on this trip point from device to device. Once the die temperature exceeds the thermal set point, the device enters into the shutdown state and the outputs are disabled. This is not a latched fault. The thermal fault is cleared once the temperature of the die is reduced by  $30^{\circ}$ C. The device begins normal operation at this point with no external system interaction.

#### PRINTED-CIRCUIT BOARD (PCB) LAYOUT

Because the TPA3124D2 is a class-D amplifier that switches at a high frequency, the layout of the printed-circuit board (PCB) should be optimized according to the following guidelines for the best possible performance.

- Decoupling capacitors—The high-frequency 0.1-μF decoupling capacitors should be placed as close to the PVCC (pins 1, 3, 10, and 12) and AVCC (pins 19 and 20) terminals as possible. The VBYP (pin 7) capacitor and VCLAMP (pin 11) capacitor should also be placed as close to the device as possible. Large (220-μF or greater) bulk power-supply decoupling capacitors should be placed near the TPA3124D2 on the PVCCL and PVCCR terminals.

- Grounding—The AVCC (pins 19 and 20) decoupling capacitor and VBYP (pin 7) capacitor should each be

grounded to analog ground (AGND, pins 8 and 9). The PVCCx decoupling capacitors and VCLAMP

capacitors should each be grounded to power ground (PGND, pins 13, 14, 23, and 24). Analog ground and

power ground should be connected at the thermal pad, which should be used as a central ground connection

or star ground for the TPA3124D2.

- Output filter—The reconstruction filter (L1, L2, C9, and C16) should be placed as close to the output terminals as possible for the best EMI performance. The capacitors should be grounded to power ground.

- Thermal pad—The thermal pad must be soldered to the PCB for proper thermal performance and optimal reliability. The dimensions of the thermal pad and thermal land are described in the mechanical section at the back of the data sheet. See TI Technical Briefs SLMA002 and SLOA120 for more information about using the thermal pad. For recommended PCB footprints, see figures at the end of this data sheet.

For an example layout, see the TPA3124D2 Evaluation Module (TPA3124D2EVM) User Manual, (SLOU189). Both the EVM user manual and the thermal pad application note are available on the TI Web site at http://www.ti.com.

Figure 32. Schematic for Single-Ended (SE) Configuration (8-Ω Speaker)

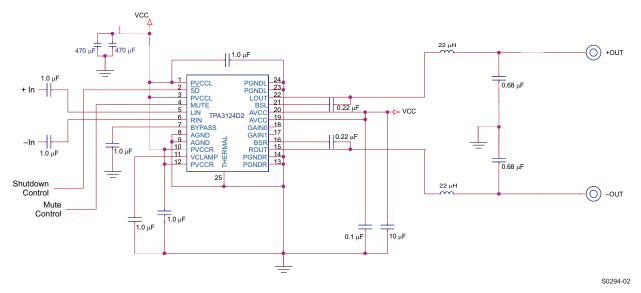

Figure 33. Schematic for Bridge-Tied-Load (BTL) Configuration (8-Ω Speaker)

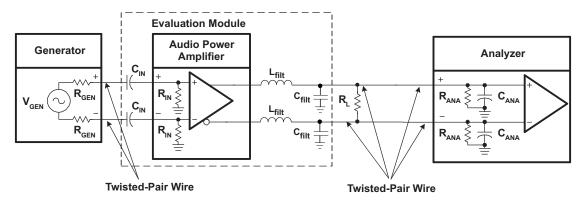

#### **BASIC MEASUREMENT SYSTEM**

This section focuses on methods that use the basic equipment listed below:

- Audio analyzer or spectrum analyzer

- Digital multi meter (DMM)

- Oscilloscope

- Twisted-pair wires

- Signal generator

- Power resistor(s)

- Linear regulated power supply

- Filter components

- EVM or other complete audio circuit

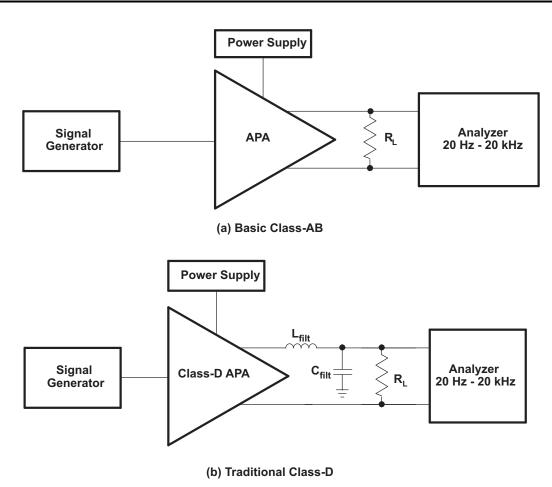

Figure 34 shows the block diagrams of basic measurement systems for class-AB and class-D amplifiers. A sine wave is normally used as the input signal because it consists of the fundamental frequency only (no other harmonics are present). An analyzer is then connected to the audio power amplifier (APA) output to measure the voltage output. The analyzer must be capable of measuring the entire audio bandwidth. A regulated dc power supply is used to reduce the noise and distortion injected into the APA through the power pins. A System Two™ audio measurement system (AP-II) by Audio Precision™ includes the signal generator and analyzer in one package.

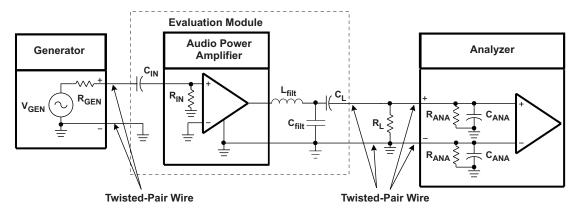

The generator output and amplifier input must be ac-coupled. However, the EVMs already have the ac-coupling capacitors  $C_{IN}$ , so no additional coupling is required. The generator output impedance should be low to avoid attenuating the test signal, and is important because the input resistance of APAs is not high. Conversely, the analyzer input impedance should be high. The output resistance,  $R_{OUT}$ , of the APA is normally in the hundreds of milliohms and can be ignored for all but the power-related calculations.

Figure 34(a) shows a class-AB amplifier system. It takes an analog signal input and produces an analog signal output. This amplifier circuit can be directly connected to the AP-II or other analyzer input.

This is not true of the class-D amplifier system shown in Figure 34(b), which requires low-pass filters in most cases in order to measure the audio output waveforms. This is because it takes an analog input signal and converts it into a pulse-width modulated (PWM) output signal that is not accurately processed by some analyzers.

Figure 34. Audio Measurement Systems

#### SE Input and SE Output (TPA3124D2 Stereo Configuration)

The SE input and output configuration is used with class-AB amplifiers. A block diagram of a fully SE measurement circuit is shown in Figure 35. SE inputs normally have one input pin per channel. In some cases, two pins are present; one is the signal and the other is ground. SE outputs have one pin driving a load through an output ac-coupling capacitor and the other end of the load is tied to ground. SE inputs and outputs are considered to be unbalanced, meaning one end is tied to ground and the other to an amplifier input/output.

The generator should have unbalanced outputs, and the signal should be referenced to the generator ground for best results. Unbalanced or balanced outputs can be used when floating, but they may create a ground loop that affects the measurement accuracy. The analyzer should have balanced inputs to cancel out any common-mode noise in the measurement.

Figure 35. SE Input—SE Output Measurement Circuit

The following general rules should be followed when connecting to APAs with SE inputs and outputs:

- Use an unbalanced source to supply the input signal.

- Use an analyzer with balanced inputs.

- Use twisted-pair wire for all connections.

- Use shielding when the system environment is noisy.

- Ensure the cables from the power supply to the APA, and from the APA to the load, can handle the large currents (see Table 5).

#### **DIFFERENTIAL INPUT AND BTL OUTPUT (TPA3124D2 Mono Configuration)**

Many of the class-D APAs and many class-AB APAs have differential inputs and bridge-tied-load (BTL) outputs. Differential inputs have two input pins per channel and amplify the difference in voltage between the pins. Differential inputs reduce the common-mode noise and distortion of the input circuit. BTL is a term commonly used in audio to describe differential outputs. BTL outputs have two output pins providing voltages that are 180° out of phase. The load is connected between these pins. This has the added benefits of quadrupling the output power to the load and eliminating a dc-blocking capacitor.

A block diagram of the measurement circuit is shown in Figure 36. The differential input is a balanced input, meaning the positive (+) and negative (-) pins have the same impedance to ground. Similarly, the SE output equates to a balanced output.

Figure 36. Differential Input, BTL Output Measurement Circuit

The generator should have balanced outputs, and the signal should be balanced for best results. An unbalanced output can be used, but it may create a ground loop that affects the measurement accuracy. The analyzer must also have balanced inputs for the system to be fully balanced, thereby cancelling out any common-mode noise in the circuit and providing the most accurate measurement.

The following general rules should be followed when connecting to APAs with differential inputs and BTL outputs:

- Use a balanced source to supply the input signal.

- Use an analyzer with balanced inputs.

- · Use twisted-pair wire for all connections.

- Use shielding when the system environment is noisy.

- Ensure that the cables from the power supply to the APA, and from the APA to the load, can handle the large currents (see Table 5).

Table 5 shows the recommended wire size for the power supply and load cables of the APA system. The real concern is the dc or ac power loss that occurs as the current flows through the cable. These recommendations are based on 12-inch (30.5-cm)-long wire with a 20-kHz sine-wave signal at 25°C.

| P <sub>OUT</sub> (W) | $R_L(\Omega)$ | AWG Size |    | DC POWER LOSS<br>(mW) |     |     | ER LOSS<br>W) |

|----------------------|---------------|----------|----|-----------------------|-----|-----|---------------|

| 10                   | 4             | 18       | 22 | 16                    | 40  | 18  | 42            |

| 2                    | 4             | 18       | 22 | 3.2                   | 8   | 3.7 | 8.5           |

| 1                    | 8             | 22       | 28 | 2                     | 8   | 2.1 | 8.1           |

| < 0.75               | 8             | 22       | 28 | 1.5                   | 6.1 | 1.6 | 6.2           |

**Table 5. Recommended Minimum Wire Size for Power Cables**

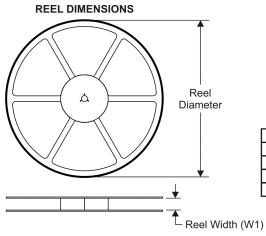

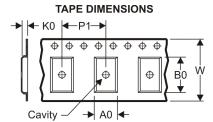

## **PACKAGE MATERIALS INFORMATION**

7-Jun-2008

#### TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

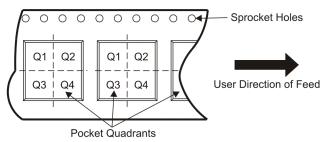

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device        | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|---------------|-----------------|--------------------|----|------|--------------------------|--------------------------|---------|---------|---------|------------|-----------|------------------|

| TPA3124D2PWPR | HTSSOP          | PWP                | 24 | 2000 | 330.0                    | 16.4                     | 6.95    | 8.3     | 1.6     | 8.0        | 16.0      | Q1               |

7-Jun-2008

#### \*All dimensions are nominal

| Device        | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |  |

|---------------|--------------|-----------------|------|------|-------------|------------|-------------|--|

| TPA3124D2PWPR | HTSSOP       | PWP             | 24   | 2000 | 346.0       | 346.0      | 33.0        |  |

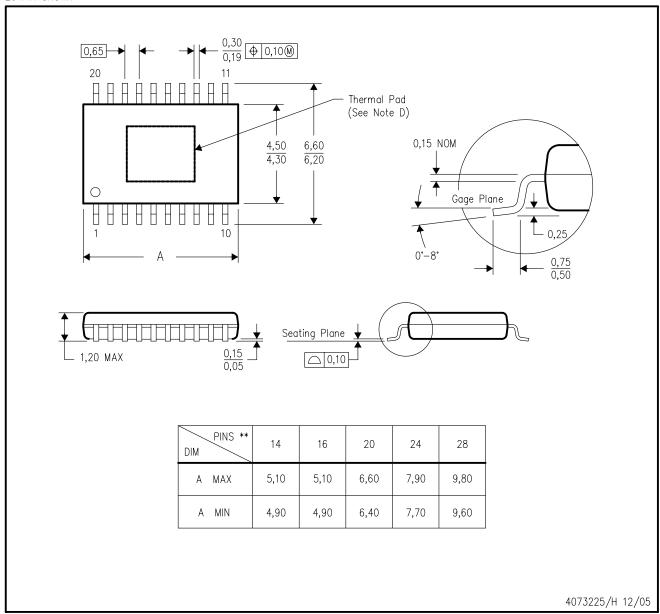

# PWP (R-PDSO-G\*\*)

# PowerPAD™ PLASTIC SMALL-OUTLINE PACKAGE

20 PIN SHOWN

NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusions. Mold flash and protrusion shall not exceed 0.15 per side.

- D. This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 for information regarding recommended board layout. This document is available at www.ti.com <a href="https://www.ti.com">www.ti.com</a>.

- E. Falls within JEDEC MO-153

PowerPAD is a trademark of Texas Instruments.

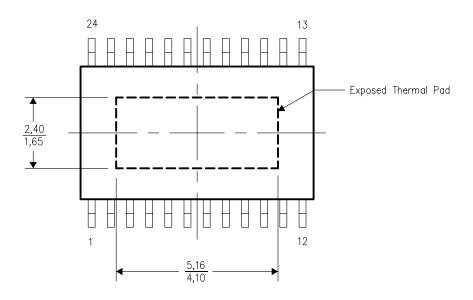

# THERMAL PAD MECHANICAL DATA PWP (R-PDS0-G24)

#### THERMAL INFORMATION

This PowerPAD  $^{\mathbf{M}}$  package incorporates an exposed thermal pad that is designed to be attached directly to an external heatsink. The thermal pad must be soldered directly to the printed circuit board (PCB). After soldering, the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For additional information on the PowerPAD package and how to take advantage of its heat dissipating abilities, refer to Technical Brief, PowerPAD Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 and Application Brief, PowerPAD Made Easy, Texas Instruments Literature No. SLMA004. Both documents are available at www.ti.com.

The exposed thermal pad dimensions for this package are shown in the following illustration.

Top View

NOTE: All linear dimensions are in millimeters

Exposed Thermal Pad Dimensions

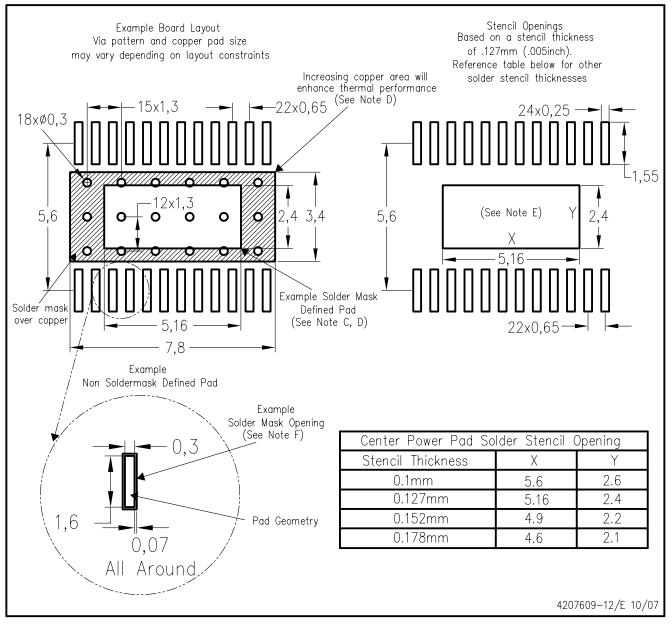

# PWP (R-PDSO-G24) PowerPAD™

NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Customers should place a note on the circuit board fabrication drawing not to alter the center solder mask defined pad.

- D. This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad Thermally Enhanced Package, Texas Instruments Literature No. SLMA002, SLMA004, and also the Product Data Sheets for specific thermal information, via requirements, and recommended board layout. These documents are available at www.ti.com <a href="http://www.ti.com">http://www.ti.com</a>. Publication IPC-7351 is recommended for alternate designs.

- E. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Example stencil design based on a 50% volumetric metal load solder paste. Refer to IPC-7525 for other stencil recommendations.

- F. Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

PowerPAD is a trademark of Texas Instruments.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products                    |                        |

|-----------------------------|------------------------|

| Amplifiers                  | amplifier.ti.com       |

| Data Converters             | dataconverter.ti.com   |

| DSP                         | dsp.ti.com             |

| Clocks and Timers           | www.ti.com/clocks      |

| Interface                   | interface.ti.com       |

| Logic                       | logic.ti.com           |

| Power Mgmt                  | power.ti.com           |

| Microcontrollers            | microcontroller.ti.com |

| RFID                        | www.ti-rfid.com        |

| RF/IF and ZigBee® Solutions | www.ti.com/lprf        |

| www.ti.com/audio          |

|---------------------------|

| www.ti.com/automotive     |

| www.ti.com/broadband      |

| www.ti.com/digitalcontrol |

| www.ti.com/medical        |

| www.ti.com/military       |

| www.ti.com/opticalnetwork |

| www.ti.com/security       |

| www.ti.com/telephony      |

| www.ti.com/video          |

| www.ti.com/wireless       |

|                           |