## SINGLE-CHIP HDMI TRANSMITTER PORT PROTECTION AND INTERFACE DEVICE

SLVS639-OCTOBER 2007

### **FEATURES**

- Single-Chip ESD Solution for High-Definition Multimedia Interface (HDMI) Driver

- 0.9 pF Capacitance for High-Speed Transition Minimized Differential Signaling (TMDS) Lines

- 0.05-pF Matching Capacitance Between the **Differential Signal Pair**

- Integrated Level Shifting for the Control Lines

- ±8-kV Contact ESD Protection on **External Lines**

- 38-Pin Thin Shrink Small-Outline Package (TSSOP) Provides Seamless Layout Option With HDMI Connector

- **Backdrive Protection**

- **Lead-Free Package**

- On-Chip Current Regulator With 55-mA **Current Output**

### **APPLICATIONS**

- **PCs**

- **Consumer Electronics**

- **Set-Top Boxes**

- **DVDRW Players**

| (TOP VIEW)     |                                                                   |                                                                                                                                                                                                                    |  |  |  |  |  |

|----------------|-------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 5V_SUPPLY      | DBI PACKAGE<br>(TOP VIEW)  1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 | 38 5V_OUT 37 ESD_BYP 36 GND 35 TMDS_D2+ 34 TMDS_CND 33 TMDS_D1+ 31 TMDS_D1+ 31 TMDS_D1- 29 TMDS_D1- 29 TMDS_D0+ 28 TMDS_CND 27 TMDS_CND 27 TMDS_CND 27 TMDS_CND 26 TMDS_CK+ 25 TMDS_CND 24 TMDS_CK- 25 CREMOTE OUT |  |  |  |  |  |

| DDC_CLK_IN     | 17<br>18                                                          | 22 DDC_CLK_OUT                                                                                                                                                                                                     |  |  |  |  |  |

| DDC_CLK_IN === | 17                                                                | 22 DDC_CLK_OUT                                                                                                                                                                                                     |  |  |  |  |  |

| HOTPLUG_DET_IN | 19                                                                | 20 HOTPLUG_DET_OUT                                                                                                                                                                                                 |  |  |  |  |  |

### DESCRIPTION/ORDERING INFORMATION

The TPD12S521 is a single-chip ESD solution for the high-definition multimedia interface (HDMI) transmitter port. In many cases, the core ICs, such as the scalar chipset, may not have robust ESD cells to sustain system-level ESD strikes. In these cases, the TPD12S521 provides the desired system level ESD protection, such as the the IEC61000-4-2 (Level 4) ESD, by absorbing the energy associated with the ESD strike.

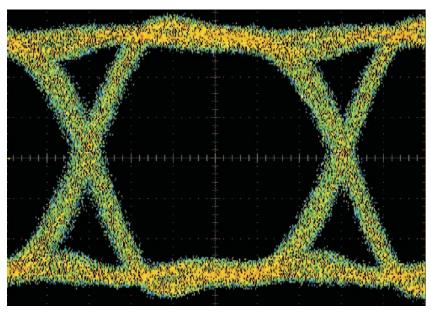

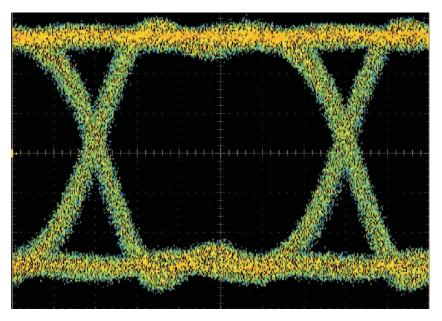

While providing the ESD protection, the TPD12S521 adds little or no additional glitch in the high-speed differential signals (see Figure 3 and Figure 4). The high-speed transition minimized differential signaling (TMDS) lines add only 0.9 pF capacitance to the lines. In addition, the monolithic integrated circuit technology ensures that there is excellent matching between the two-signal pair of the differential line. This is a direct advantage over discrete ESD clamp solutions where variations between two different ESD clamps may significantly degrade the differential signal quality.

The low-speed control lines offer voltage-level shifting to eliminate the need for an external voltage level-shifter IC. The control line ESD clamps add 3.5 pF capacitance to the control lines. The 38-pin DBT package offers seamless layout routing option to eliminate the routing glitch for the differential signal pair.

The TPD12S521 provides an on-chip regulator with current output ratings of 55 mA at pin 38. Maximum overcurrent protection output drop at 55 mA on 5V\_OUT is 100 mV. This current enables the HDMI receiver detection even when the receiver device is powered-off. DBT package pitch (0.5 mm) matches with HDMI connector pitch. In addition, pin mapping follows the same order as the HDMI connector pin mapping. This HDMI receiver port protection and interface device is specifically designed for next-generation HDMI transmitter protection.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

## SINGLE-CHIP HDMI TRANSMITTER PORT PROTECTION AND INTERFACE DEVICE

SLVS639-OCTOBER 2007

### ORDERING INFORMATION

|                |                           | STANDARD FINISH                         |                     | LEAD-FREE FINISH                        |                     |

|----------------|---------------------------|-----------------------------------------|---------------------|-----------------------------------------|---------------------|

| T <sub>A</sub> | PACKAGE <sup>(1)(2)</sup> | ORDERABLE<br>PART NUMBER <sup>(3)</sup> | TOP-SIDE<br>MARKING | ORDERABLE<br>PART NUMBER <sup>(3)</sup> | TOP-SIDE<br>MARKING |

| –40°C to 85°C  | TSSOP-38                  | TPD12S521DBTR                           | PREVIEW             | TPD12S521DBTR                           | PREVIEW             |

- (1) Package drawings, thermal data, and symbolization are available at www.ti.com/packaging.

- (2) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI website at www.ti.com.

- (3) Parts are shipped in tape-and-reel form, unless otherwise specified.

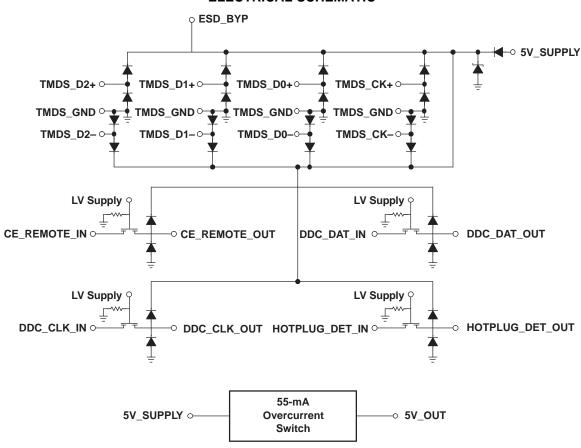

### **ELECTRICAL SCHEMATIC**

External bypass capacitors and resistor components not included

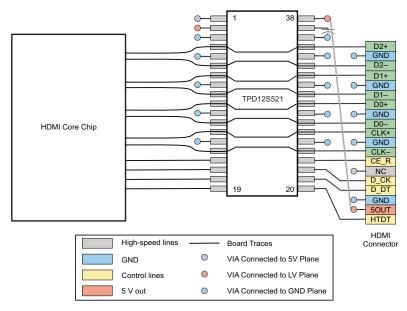

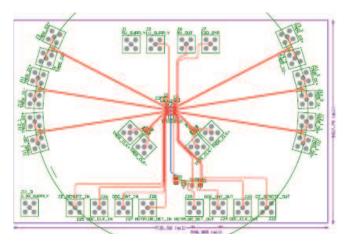

Figure 1. Board Layout for HDMI Transmitter Using TPD12S521DBTR

### **PIN DESCRIPTION**

| PIN NO.                                | NAME            | DESCRIPTION                                                                                                   |

|----------------------------------------|-----------------|---------------------------------------------------------------------------------------------------------------|

| 4, 35                                  | TMDS_D2+        | TMDS 0.9-pF ESD protection <sup>(1)</sup>                                                                     |

| 6, 33                                  | TMDS_D2-        | TMDS 0.9-pF ESD protection <sup>(1)</sup>                                                                     |

| 7, 32                                  | TMDS_D1+        | TMDS 0.9-pF ESD protection <sup>(1)</sup>                                                                     |

| 9, 30                                  | TMDS_D1-        | TMDS 0.9-pF ESD protection (2)                                                                                |

| 10, 29                                 | TMDS_D0+        | TMDS 0.9-pF ESD protection <sup>(2)</sup>                                                                     |

| 12, 27                                 | TMDS_D0-        | TMDS 0.9-pF ESD protection <sup>(2)</sup>                                                                     |

| 13, 26                                 | TMDS_CK+        | TMDS 0.9-pF ESD protection <sup>(2)</sup>                                                                     |

| 15, 24                                 | TMDS_CK-        | TMDS 0.9-pF ESD protection <sup>(2)</sup>                                                                     |

| 16                                     | CE_REMOTE_IN    | LV_SUPPLY referenced logic level in                                                                           |

| 23                                     | CE_REMOTE_OUT   | 5V_SUPPLY referenced logic level out, plus 3.5-pF ESD                                                         |

| 17                                     | DDC_CLK_IN      | LV_SUPPLY referenced logic level in                                                                           |

| 22                                     | DDC_CLK_OUT     | 5V_SUPPLY referenced logic level out, plus 3.5-pF ESD                                                         |

| 18                                     | DDC_DAT_IN      | LV_SUPPLY referenced logic level in                                                                           |

| 21                                     | DDC_DAT_OUT     | 5V_SUPPLY referenced logic level out, plus 3.5-pF ESD                                                         |

| 19                                     | HOTPLUG_DET_IN  | LV_SUPPLY referenced logic level in                                                                           |

| 20                                     | HOTPLUG_DET_OUT | 5V_SUPPLY referenced logic level out, plus 3.5-pF ESD                                                         |

| 2                                      | LV_SUPPLY       | Bias for CE/DDC/HOTPLUG level shifters                                                                        |

| 1                                      | 5V_SUPPLY       | Current source for 5V_OUT                                                                                     |

| 38                                     | 5V_OUT          | 55-mA minimum overcurrent protected 5-V output. This output must be bypassed with a 0.1-μF ceramic capacitor. |

| 37                                     | ESD_BYP         | ESD bypass. This pin must be connected to a 0.1-µF ceramic capacitor.                                         |

| 3, 5, 8, 11, 14,<br>25, 28, 31, 34, 36 | GND/TMDS_GND    | GND reference                                                                                                 |

These two pins must be connected together inline on the PCB.

These two pins must be connected together inline on the PCB.

## SINGLE-CHIP HDMI TRANSMITTER PORT PROTECTION AND INTERFACE DEVICE

SLVS639-OCTOBER 2007

## **Absolute Maximum Ratings**

over operating free-air temperature range (unless otherwise noted)

|                                      |                                 | MIN         | MAX            | UNIT |

|--------------------------------------|---------------------------------|-------------|----------------|------|

| V <sub>CC5</sub><br>V <sub>CC3</sub> |                                 |             | 6              | V    |

|                                      | DC voltage at any channel input | GND - 0.5   | $V_{CC} + 0.5$ | V    |

| T <sub>stg</sub>                     | Storage temperature range       | <b>–</b> 65 | 150            | °C   |

# **Recommended Operating Conditions**

|                             |           | MIN | NOM | MAX | UNIT |

|-----------------------------|-----------|-----|-----|-----|------|

| Operating supply voltage    | 5V_SUPPLY |     | 5   | 5.5 | V    |

| Bias supply voltage         | LV_SUPPLY | 1   | 3.3 | 5.5 | V    |

| Operating temperature range | ·         | -40 |     | 85  | °C   |

# TPD12S521 SINGLE-CHIP HDMI TRANSMITTER PORT PROTECTION AND INTERFACE DEVICE

SLVS639-OCTOBER 2007

### **Electrical Characteristics**

over operating free-air temperature range (unless otherwise noted)

|                            | PARAMETER                                                              | TEST                                                                                         | CONDITIONS          |     | MIN  | TYP  | MAX  | UNIT |

|----------------------------|------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|---------------------|-----|------|------|------|------|

| I <sub>CC5</sub>           | Operating supply current                                               | 5V_SUPPLY = 5 V                                                                              |                     |     |      | 110  | 130  | μΑ   |

| I <sub>CC3</sub>           | Bias supply current                                                    | LV_SUPPLY = 3.3 V                                                                            | LV_SUPPLY = 3.3 V   |     |      | 1    | 5    | μΑ   |

| V <sub>DROP</sub>          | 5V_OUT overcurrent output drop                                         | 5V_SUPPLY = 5 V, I <sub>OUT</sub>                                                            | = 55 mA             |     |      | 65   | 100  | mV   |

| I <sub>SC</sub>            | 5V_OUT short-circuit current limit                                     | 5V_SUPPLY= 5 V, 5V_C                                                                         | DUT = GND           |     | 90   | 135  | 175  | mA   |

| I <sub>OFF</sub>           | OFF-state leakage current, level-shifting NFET                         | LV_SUPPLY = 0 V                                                                              |                     |     |      | 0.1  | 5    | μA   |

| I <sub>BACKDRIVE</sub>     | Current conducted from output pins to V_SUPPLY rails when powered down | TMDS_D[2:0]+/-, TMDS_CK+/-, CE_REMOTE_OUT, DDC_DAT_OUT, DDC_CLK_OUT, HOTPLUG_DET_OUT, 5V_OUT |                     |     | 0.1  | 5    | μΑ   |      |

| V <sub>ON</sub>            | Voltage drop across level-shifting NFET when ON                        | LV_SUPPLY = 2.5 V, V <sub>S</sub> = GND, I <sub>DS</sub> = 3 mA                              |                     | 75  | 95   | 140  | mV   |      |

| .,                         | Diada famusad valtana                                                  | $I_F = 8 \text{ mA},$                                                                        | Top diode           |     | 0.6  | 0.85 | 0.95 | V    |

| V <sub>F</sub>             | Diode forward voltage                                                  | $T_A = 25^{\circ}C^{(1)}$ Bottom diode                                                       |                     |     | 0.6  | 0.85 | 0.95 | V    |

| V                          | CCD withstand valtage                                                  | Pins 4, 7, 10, 13, 20–24, 27, 30, 33 <sup>(1)(2)</sup> IEC                                   |                     | ±8  |      |      | kV   |      |

| V <sub>ESD</sub>           | ESD withstand voltage                                                  | Pins 1, 2, 16–19, 37, 38 <sup>(1)(3)</sup> HBM                                               |                     | ±2  |      |      | ĸv   |      |

| M                          | Channel clamp voltage                                                  | $T_A = 25^{\circ}C^{(1)(3)}$                                                                 | Positive transients |     |      | 9    |      | V    |

| $V_{CL}$                   | at 8-kV HBM ESD                                                        | 1A = 25 C · · · ·                                                                            | Negative transients |     | -9   |      |      | 7 V  |

| D                          | Dynamia registance                                                     | I = 1 A, T <sub>A</sub> = 25°C <sup>(4)</sup>                                                | Positive transients |     |      | 3    |      | Ω    |

| $R_{DYN}$                  | Dynamic resistance                                                     | T = T A, T <sub>A</sub> = 25 C · γ                                                           | Negative transients |     |      | 1.5  |      | 12   |

| I <sub>LEAK</sub>          | TMDS channel leakage current                                           | $T_A = 25^{\circ}C^{(1)}$                                                                    |                     |     |      | 0.01 | 1    | μΑ   |

| C <sub>IN</sub> ,<br>TMDS  | TMDS channel input capacitance                                         | 5V_SUPPLY= 5 V, Measured at 1 MHz, $V_{BIAS} = 2.5 V^{(1)}$                                  |                     |     |      | 0.9  | 1.1  | pF   |

| ΔC <sub>IN</sub> ,<br>TMDS | TMDS channel input capacitance matching                                | 5V_SUPPLY= 5 V, Measured at 1 MHz, $V_{BIAS} = 2.5 V^{(1)(5)}$                               |                     |     |      | 0.05 |      | pF   |

| C <sub>MUTUAL</sub>        | Mutual capacitance between signal pin and adjacent signal pin          | 5V_SUPPLY= 0 V, Measured at 1 MHz, V <sub>BIAS</sub> = 2.5 V <sup>(1)</sup>                  |                     |     | 0.07 |      | pF   |      |

| C <sub>IN</sub>            | Level-shifting input capacitance, capacitance to GND                   | 5V_SUPPLY= 0 V, Measured at 100 KHz, VBIAS = 2.5 V <sup>(1)</sup> DDC CEC HP                 |                     | DDC |      | 3.5  | 4    |      |

|                            |                                                                        |                                                                                              |                     | CEC |      | 3.5  | 4    | pF   |

|                            | capacitatioe to GND                                                    |                                                                                              |                     | HP  |      | 3.5  | 4    |      |

This parameter is specified by design and verified by device characterization.

<sup>(2)</sup> (3)

Standard IEC 61000-4-2,  $C_{DISCHARGE}$  = 150 pF,  $R_{DISCHARGE}$  = 330  $\Omega$ Human-Body Model (HBM) per MIL-STD-883, Method 3015,  $C_{DISCHARGE}$  = 100 pF,  $R_{DISCHARGE}$  = 1.5 k $\Omega$ These measurements performed with no external capacitor on ESD\_BYP.

Intrapair matching, each TMDS pair (i.e., D+, D-)

## **TYPICAL PERFORMANCE**

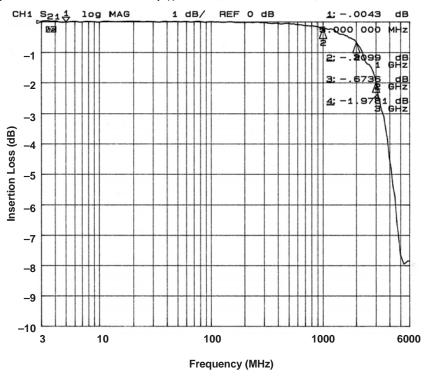

Typical Filter Performance ( $T_A = 25^{\circ}C$ , DC Bias = 0 V, 50- $\Omega$  Environment)

Figure 2. Insertion Loss vs Frequency (TMDS\_D1- to GND)

Figure 3. Eye Diagram With TPD12S521

PRODUCT PREVIEW

SLVS639-OCTOBER 2007

# **TYPICAL PERFORMANCE (continued)**

Figure 4. Eye Diagram Without TPD12S521

Figure 5. Test Board to Measure Eye Diagram for the TPD12S521 (Refer to Eye Diagram Plot)

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products              |                        | Applications       |                           |

|-----------------------|------------------------|--------------------|---------------------------|

| Amplifiers            | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters       | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP                   | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface             | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic                 | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt            | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers      | microcontroller.ti.com | Security           | www.ti.com/security       |

| RFID                  | www.ti-rfid.com        | Telephony          | www.ti.com/telephony      |

| Low Power<br>Wireless | www.ti.com/lpw         | Video & Imaging    | www.ti.com/video          |

|                       |                        | Wireless           | www.ti.com/wireless       |