# 捷多邦,专业PCB打样工厂,24小时加急出货 TPL9201 MICROCONTROLLER POWER SUPPLY AND MULTIPLE LOW-SIDE DRIVER

SLIS123A-JUNE 2006-REVISED JUNE 2006

#### **FEATURES**

- Eight Low-Side Drivers With Internal Clamp for Inductive Loads and Current Limiting for Self Protection

- Seven Outputs Rated at 150 mA and Controlled Through Serial Interface

- One Output Rated at 150 mA and Controlled Through Serial Interface and Dedicated Enable Pin

- 5-V ±5% Regulated Power Supply With 200-mA Load Capability at V<sub>IN</sub> Max of 18 V

- Internal Voltage Supervisory for Regulated Output

- Serial Communications for Control of Eight Low-Side Drivers

- Enable/Disable Input for OUT1

- 5-V or 3.3-V I/O Tolerant for Interface to Microcontroller

- Programmable Power-On Reset Delay Before RST Asserted High, Once 5 V Is Within Specified Range (6 ms Typ)

- Programmable Deglitch Timer Before RST Is

Asserted Low (40 μs Typ)

- Zero-Voltage Detection Signal With Built-In Filter of 20 μs

- Thermal Shutdown for Self Protection

## **APPLICATIONS**

- Electrical Appliances

- Air Conditioning Units

- Ranges

- Dishwashers

- Refrigerators

- Microwaves

- Washing Machines

- General-Purpose Interface Circuits, Allowing Microcontroller Interface to Relays, Electric Motors, LEDs, and Buzzers

# **DESCRIPTION/ORDERING INFORMATION**

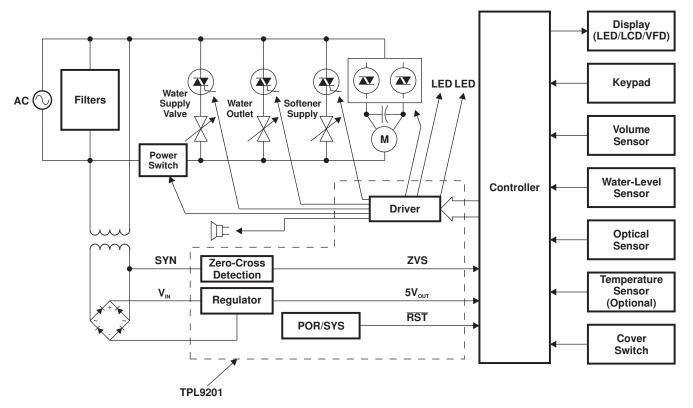

The power supply provides regulated 5-V output to power the system microcontroller and drive eight low-side switches. The AC zero-detect circuitry is monitoring the crossover voltage of the mains AC supply. The resultant signal is a low-frequency clock output on the ZVS terminal, based on the AC-line cycle. This information allows the microcontroller to reduce in-rush current by powering loads on the AC-line peak voltage.

A serial communications interface controls the eight low-side outputs; each output has an internal snubber circuit to absorb the energy in the inductor at turn OFF. Alternatively, the system can use a fly-back diode to  $V_{IN}$  to help recirculate the energy in an inductive load at turn OFF.

#### ORDERING INFORMATION

| T <sub>A</sub> | PAC             | CKAGE        | ORDERABLE PART NUMBER | TOP-SIDE MARKING |  |

|----------------|-----------------|--------------|-----------------------|------------------|--|

| –40°C to 125°C | PDIP – N        | Tube of 20   | TPL9201N              | TPL9201          |  |

|                | DawerDADTM DWD  | Reel of 2000 | TPL9201PWPR           | IC9201           |  |

|                | PowerPAD™ – PWP |              | Tube of 70 TPL9201PWP |                  |  |

PDPlease be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

SLIS123A-JUNE 2006-REVISED JUNE 2006

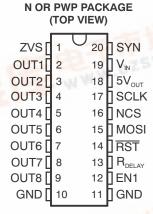

## **PINOUT CONFIGURATION**

| NO.               | NAME               | I/O | DESCRIPTION                                    |

|-------------------|--------------------|-----|------------------------------------------------|

| 1                 | ZVS                | 0   | Zero-voltage synchronization                   |

| 2                 | OUT1               | 0   | Low-side output 1                              |

| 3                 | OUT2               | 0   | Low-side output 2                              |

| 4                 | OUT3               | 0   | Low-side output 3                              |

| 5                 | OUT4               | 0   | Low-side output 4                              |

| 6                 | OUT5               | 0   | Low-side output 5                              |

| 7                 | OUT6               | 0   | Low-side output 6                              |

| 8                 | OUT7               | 0   | Low-side output 7                              |

| 9                 | OUT8               | 0   | Low-side output 8                              |

| 10 <sup>(1)</sup> | GND                | I   | Ground                                         |

| 11 <sup>(1)</sup> | GND                | I   | Ground                                         |

| 12                | EN1                | I   | Enable/disable for OUT1                        |

| 13                | R <sub>DELAY</sub> | 0   | Power-up reset delay                           |

| 14 <sup>(2)</sup> | RST                | I/O | Power-on reset output (open drain, active low) |

| 15                | MOSI               | I   | Serial data input                              |

| 16                | NCS                | I   | Chip select                                    |

| 17                | SCLK               | I   | Serial clock for data synchronization          |

| 18                | 5V <sub>OUT</sub>  | 0   | Regulated output                               |

| 19                | V <sub>IN</sub>    | I   | Unregulated input voltage source               |

| 20                | SYN                | I   | AC zero detect input                           |

<sup>(1)</sup> Terminals 10 and 11 are fused internally in the lead frame for the 20-pin PDIP package.

<sup>(2)</sup> Terminal 14 can be used as an input or an output.

SLIS123A-JUNE 2006-REVISED JUNE 2006

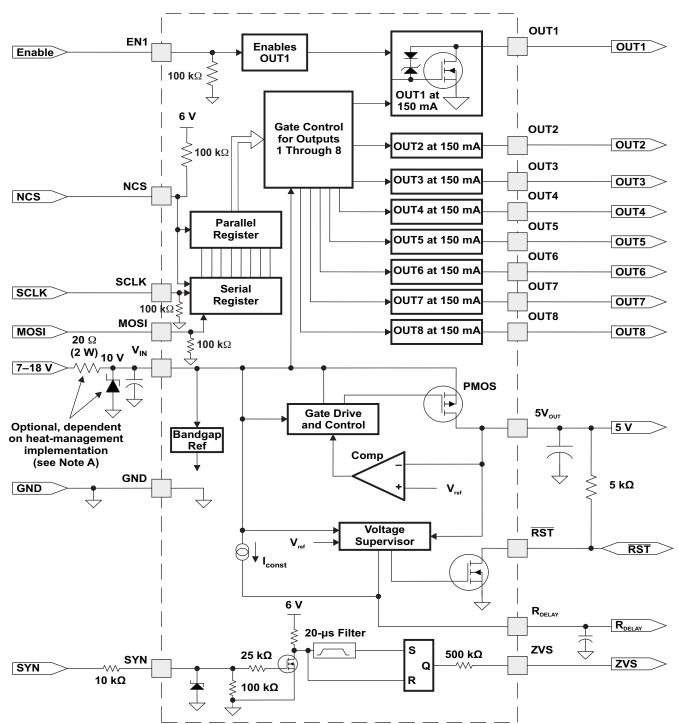

### **FUNCTIONAL BLOCK DIAGRAM**

A. The resistor and Zener diode are required if there is insufficient thermal-management allocation.

SLIS123A-JUNE 2006-REVISED JUNE 2006

#### DETAILED DESCRIPTION

The 5-V regulator is powered from  $V_{IN}$ , and the regulated output is within 5 V  $\pm$ 5% over the operating conditions. The open-drain power-on reset (RST) pin remains low until the regulator exceeds the set threshold, and the timer value set by the capacitor on the reset delay ( $R_{DELAY}$ ) pin expires. If both of these conditions are satisfied, RST is asserted high. This signifies to the microcontroller that serial communications can be initiated to the TPL9201.

The serial communications is an 8-bit format, with data transfer synchronized using a serial clock from the microcontroller. A single register controls all the outputs (one bit per output). The default value is zero (OFF). If an output requires pulse width modulation (PWM) function, the register must be updated at a rate faster than the desired PWM frequency. OUT1 can be controlled by serial input from the microcontroller or with the dedicated enable (EN1) pin. If EN1 is pulled low or left open, the serial input through the shift register controls OUT1. If EN1 is pulled high, OUT1 always is turned on, and the serial input for OUT1 is ignored.

The SYN input translates the image of the mains voltage through the secondary of the transformer. The SYN input has a resistor to protect from high currents into the IC. The zero-voltage synchronization output translates the AC-line cycle frequency into a low-frequency clock, which can be used for a timing reference and to help power loads on the AC-line peak voltage (to reduce in-rush currents).

If  $\overline{RST}$  is asserted, all outputs are turned OFF internally, and the input register is reset to all zeroes. The microcontroller must write to the register to turn the outputs ON again.

SLIS123A-JUNE 2006-REVISED JUNE 2006

# **Absolute Maximum Ratings**(1)

|                       |                                                           |                                                             | MIN | MAX  | UNIT  |

|-----------------------|-----------------------------------------------------------|-------------------------------------------------------------|-----|------|-------|

| \/                    | Liprogulated input valtage (2)(3)                         | V <sub>IN</sub>                                             |     | 24   | V     |

| V <sub>I(unreg)</sub> | Unregulated input voltage (2)(3)                          | SYN                                                         |     | 24   | V     |

| \/                    | Logic input voltage <sup>(2)(3)</sup>                     | EN1, MOSI, SCLK, and NCS                                    |     | 7    | V     |

| $V_{I(logic)}$        | Logic input voitage ( ) (                                 | RST and R <sub>DELAY</sub>                                  |     | 7    | V     |

| Vo                    | Low-side output voltage                                   | OUT1-OUT8                                                   |     | 16.5 | V     |

| I <sub>LIMIT</sub>    | Output current limit <sup>(4)</sup>                       | OUTn = ON and shorted to V <sub>IN</sub> with low impedance |     | 350  | mA    |

| 0                     | Thermal impedance, junction to ambient <sup>(5)</sup>     | N package                                                   |     | 69   | °C/W  |

| $\theta_{JA}$         |                                                           | PWP package                                                 |     | 33   | C/VV  |

| 0                     | Thermal impedance, junction to case <sup>(5)</sup>        | N package                                                   |     | 54   | °C/W  |

| $\theta_{JC}$         |                                                           | PWP package                                                 |     | 20   | -0/00 |

| $\theta_{\sf JP}$     | Thermal impedance, junction to thermal pad <sup>(5)</sup> | PWP package                                                 |     | 1.4  | °C/W  |

| _                     |                                                           | N package                                                   |     | 1.8  | W     |

| $P_D$                 | Continuous power dissipation (6)                          | PWP package                                                 |     | 3.7  | VV    |

| ESD                   | Electrostatic discharge <sup>(7)</sup>                    | ·                                                           |     | 2    | kV    |

| T <sub>A</sub>        | Operating ambient temperature range                       |                                                             | -40 | 125  | °C    |

| T <sub>stg</sub>      | Storage temperature range                                 |                                                             | -65 | 125  | °C    |

| T <sub>lead</sub>     | Lead temperature                                          | Soldering, 10 s                                             |     | 260  | °C    |

- (1) Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- 2) All voltage values are with respect to GND.

- (3) Absolute negative voltage on these pins must not go below -0.5 V.

- (4) Not more than one output should be shorted at a time, and duration of the short circuit should not exceed 1 ms.

- (5) The thermal data is based on using 1-oz copper trace with JEDEC 51-5 test board for PWP and JEDEC 51-7 test board for N.

- (6) The data is based on ambient temperature of 25°C max.

- (7) The Human-Body Model is a 100-pF capacitor discharged through a 1.5-k $\Omega$  resistor into each pin.

# **Dissipation Ratings**

| Ī | PACKAGE | T <sub>A</sub> ≤ 25°C<br>POWER RATING | DERATING FACTOR<br>ABOVE T <sub>A</sub> = 25°C | T <sub>A</sub> = 125°C<br>POWER RATING |

|---|---------|---------------------------------------|------------------------------------------------|----------------------------------------|

| Ī | N       | 1812 mW                               | 14.5 mW/°C                                     | 362 mW                                 |

| Ī | PWP     | 3787 mW                               | 30.3 mW/°C                                     | 757 mW                                 |

# **Recommended Operating Conditions**

|                       |                               |                                                   | MIN | MAX  | UNIT |

|-----------------------|-------------------------------|---------------------------------------------------|-----|------|------|

| V                     | Uprogulated input voltage     | V <sub>IN</sub>                                   | 7   | 18   | \/   |

| V <sub>I(unreg)</sub> | Unregulated input voltage     | SYN                                               | 0   | 18   | V    |

| V <sub>I(logic)</sub> | Logic input voltage           | EN1, MOSI, SCLK, NCS, RST, and R <sub>DELAY</sub> | 0   | 5.25 | V    |

| T <sub>A</sub>        | Operating ambient temperature |                                                   | -40 | 125  | °C   |

SLIS123A-JUNE 2006-REVISED JUNE 2006

# **Electrical Characteristics**

$\rm T_A = -40^{\circ}C$  to 125°C,  $\rm V_{IN} = 7~V$  to 18 V (unless otherwise stated)

|                                | PARAMETER                    | TEST CONDITIONS                                                                                          | MIN                   | TYP <sup>(1)</sup> | MAX  | UNIT |

|--------------------------------|------------------------------|----------------------------------------------------------------------------------------------------------|-----------------------|--------------------|------|------|

| Supply Vol                     | tage and Current             |                                                                                                          |                       |                    |      |      |

| V <sub>IN</sub> <sup>(2)</sup> | Input voltage                |                                                                                                          | 7                     |                    | 18   | V    |

|                                | lancet according accordant   | Enable = ON, OUT1-OUT8 = OFF                                                                             |                       |                    | 3    | A    |

| $I_{VIN}$                      | Input supply current         | Enable = ON, OUT1-OUT8 = ON                                                                              |                       |                    | 5    | mA   |

| Logic Input                    | s (MOSI, NCS, SCLK, and EN   | 1)                                                                                                       |                       |                    | •    |      |

| V <sub>IL</sub>                | Logic input low level        | I <sub>IL</sub> = 100 μA                                                                                 |                       |                    | 0.8  |      |

| V <sub>IH</sub>                | Logic input high level       | I <sub>IL</sub> = 100 μA                                                                                 | 2.4                   |                    |      | V    |

| Reset (RST                     | )                            |                                                                                                          |                       |                    | •    |      |

| V <sub>OL</sub>                | Logic level output           | I <sub>OL</sub> = 1.6 mA                                                                                 |                       |                    | 0.4  | V    |

| V <sub>OH</sub> <sup>(3)</sup> | Logic level output           | 5-k $\Omega$ pullup to V <sub>CC</sub>                                                                   | V <sub>CC</sub> - 0.8 |                    |      | V    |

| V <sub>H</sub>                 | Disabling reset threshold    | 5-V regulator ramps up                                                                                   |                       | 4.25               | 4.5  | V    |

| $V_L$                          | Enabling reset threshold     | 5-V regulator ramps down                                                                                 | 3.3                   | 3.75               |      | V    |

| V <sub>HYS</sub>               | Threshold hysteresis         |                                                                                                          | 0.12                  | 0.5                |      | V    |

| Reset Dela                     | y (R <sub>DELAY</sub> )      |                                                                                                          |                       |                    |      |      |

| I <sub>OUT</sub>               | Output current               |                                                                                                          | 18                    | 28                 | 48   | μΑ   |

| $T_DW$                         | Reset delay timer            | C = 47 nF                                                                                                | 3                     | 6                  |      | ms   |

| T <sub>UP</sub>                | Reset capacitor to low level | C = 47 nF                                                                                                |                       | 45                 |      | μs   |

| Output (OU                     | T1-OUT8)                     |                                                                                                          |                       |                    | •    |      |

| V <sub>OL</sub>                | Output ON                    | I <sub>OUTn</sub> = 150 mA                                                                               |                       | 0.4                | 0.7  | V    |

| I <sub>OH</sub>                | Output leakage               | V <sub>OH</sub> = Max of 16.5 V                                                                          |                       |                    | 2    | μΑ   |

| Regulator (                    | Output (5V <sub>OUT</sub> )  |                                                                                                          |                       |                    | •    |      |

| 5V <sub>OUT</sub>              | Output supply                | $I_{5\text{VOUT}}$ = 5 mA to 200 mA, $V_{\text{IN}}$ = 7 V to 18 V, $C_{5\text{VOUT}}$ = 1 $\mu\text{F}$ | 4.75                  | 5                  | 5.25 | V    |

| I <sub>5VOUT</sub> limit       | Output short-circuit current | 5V <sub>OUT</sub> = 0 V                                                                                  | 200                   |                    |      | mA   |

| Thermal Sh                     | utdown                       |                                                                                                          |                       |                    |      |      |

| T <sub>SD</sub>                | Thermal shutdown             |                                                                                                          |                       | 150                |      | °C   |

| T <sub>HYS</sub>               | Hysteresis                   |                                                                                                          |                       | 20                 |      | °C   |

|                                | ge Synchronization (ZVS)     |                                                                                                          | ·                     |                    |      | -    |

| V <sub>SYNTH</sub>             | Transition threshold         |                                                                                                          | 0.4                   | 0.75               | 1.1  | V    |

| I <sub>SYN</sub>               | Input activating current     | $R_{ZV} = 10 \text{ k}\Omega, V_{SYN} = 24 \text{ V}$                                                    |                       |                    | 2    | mA   |

| t <sub>D</sub>                 | Transition filtering time    | Rising and falling                                                                                       | 10                    | 30                 | 70   | μs   |

<sup>(1)</sup> All typical values are at  $T_A = 25^{\circ}C$ . (2) There are external high-frequency noise-suppression capacitors and filter capacitors on  $V_{IN}$ . (3)  $V_{CC}$  is the pullup resistor voltage.

SLIS123A-JUNE 2006-REVISED JUNE 2006

# **Output Control Register**

MSB LSB

| IN8 | IN7 | IN6 | IN5 | IN4 | IN3 | IN2 | IN1 |

|-----|-----|-----|-----|-----|-----|-----|-----|

| 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

INn = 0: Output OFF INn = 1: Output ON

To operate the output in PWM mode, the output control register must be updated at a rate twice the desired PWM frequency of the output. Maximum PWM frequency is 5 kHz. The register is updated every 100  $\mu$ s.

# **ENABLE TRUTH TABLE**

| EN1  | SERIAL INPUT<br>FOR OUT1 | OUT1 |

|------|--------------------------|------|

| Open | Н                        | On   |

| Open | L                        | Off  |

| L    | Н                        | On   |

| L    | L                        | Off  |

| Н    | Н                        | On   |

| Н    | L                        | On   |

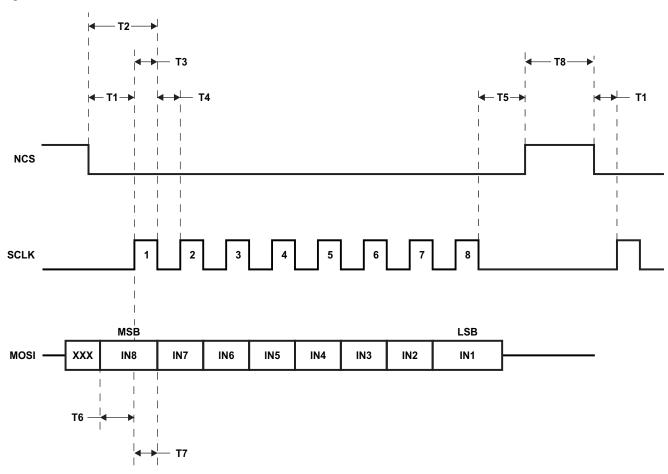

### **Serial Communications Interface**

The serial communications is an 8-bit format, with data transfer synchronized using a serial clock from the microcontroller (see Figure 1). A single register controls all the outputs. The signal gives the instruction to control the output of TPL9201.

The NCS signal enables the SCLK and MOSI data when it is low. After NCS is set low for  $T_1$ , synchronization clock and data begin to transmit and, after the 8-bit data has been transmitted, NCS is set high again to disable SCLK and MOSI and transfer the serial data to the control register. SCLK must be held low when NCS is in the high state.

Figure 1. Serial Communications

SLIS123A-JUNE 2006-REVISED JUNE 2006

## **Timing Requirements**

$T_A = -40$ °C to 125°C,  $V_{IN} = 7$  V to 18 V (unless otherwise stated)

|           | PARAMETER                                             | MIN | TYP | MAX | UNIT |

|-----------|-------------------------------------------------------|-----|-----|-----|------|

| $f_{SPI}$ | SPI frequency                                         |     | 4   |     | kHz  |

| T1        | Delay time, NCS falling edge to SCLK rising edge      | 10  |     |     | ns   |

| T2        | Delay time, NCS falling edge to SCLK falling edge     | 80  |     |     | ns   |

| T3        | Pulse duration, SCLK high                             | 60  |     |     | ns   |

| T4        | Pulse duration, SCLK low                              | 60  |     |     | ns   |

| T5        | Delay time, last SCLK falling edge to NCS rising edge | 80  |     |     | ns   |

| T6        | Setup time, MOSI valid before SCLK edge               | 10  |     |     | ns   |

| T7        | Hold time, MOSI valid after SCLK edge                 | 10  |     |     | ns   |

| T8        | Time between two words for transmitting               | 170 |     |     | ns   |

# Reset Delay (R<sub>DELAY</sub>)

The  $R_{DELAY}$  output provides a constant current source to charge an external capacitor to approximately 6.5 V. The external capacitor is selected to provide a delay time, based on the current equation for a capacitor,  $I = C(\Delta v/\Delta t)$  and a 28- $\mu$ A typical output current.

Therefore, the user should select a 47-nF capacitor to provide a 6-ms delay at 3.55 V.

$I = C(\Delta v / \Delta t)$

$28 \mu A = C \times (3.55 \text{ V/6 ms})$

C = 47 nF

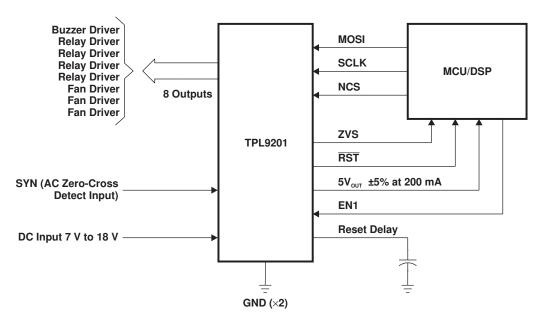

### **APPLICATION INFORMATION**

Figure 2. Typical Application

Figure 3. Washing-Machine Application

SLIS123A-JUNE 2006-REVISED JUNE 2006

## **APPLICATION INFORMATION (continued)**

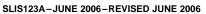

# **PCB Layout**

To maximize the efficiency of this package for application on a single-layer or multi-layer PCB, certain guidelines must be followed when laying out this part on the PCB.

The following information is to be used as a guideline only.

For further information, see the PowerPAD concept implementation document.

### **Application Using a Multilayer PCB**

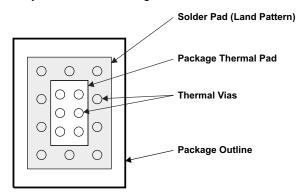

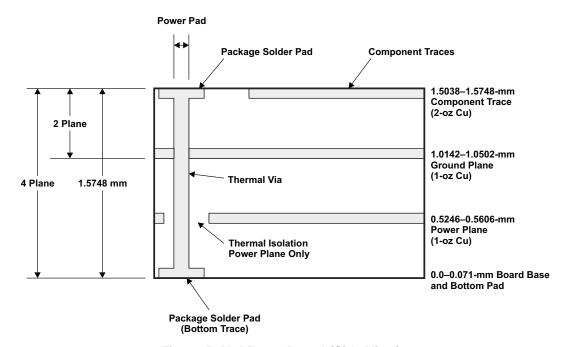

In a multilayer board application, the thermal vias are the primary method of heat transfer from the package thermal pad to the internal ground plane (see Figure 4 and Figure 5).

The efficiency of this method depends on several factors: die area, number of thermal vias, thickness of copper, etc. (see the *PowerPAD<sup>TM</sup> Thermally Enhanced Package Technical Brief*, literature number SLMA002).

Figure 4. Package and PCB Land Configuration for a Multilayer PCB

Figure 5. Multilayer Board (Side View)

SLIS123A-JUNE 2006-REVISED JUNE 2006

## **APPLICATION INFORMATION (continued)**

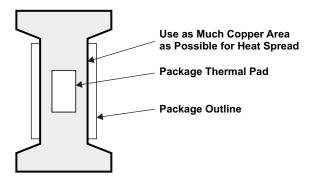

## **Application Using a Single-Layer PCB**

In a single-layer board application, the thermal pad is attached to a heat spreader (copper area) by using the low thermal-impedance attachment method (solder paste or thermal-conductive epoxy). With either method, it is advisable to use as much copper trace area as possible to dissipate the heat.

#### **CAUTION:**

If the attachment method is not implemented correctly, the functionality of the product cannot be assured. Power-dissipation capability is adversely affected if the device is incorrectly mounted onto the circuit board.

Figure 6. Layout Recommendations for a Single-Layer PCB

# **APPLICATION INFORMATION (continued)**

### **Recommended Board Layout**

Figure 7. Recommended Board Layout for PWP

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

|                        | Applications                                                                                      |                                                                                                                                                                                                                                             |

|------------------------|---------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| amplifier.ti.com       | Audio                                                                                             | www.ti.com/audio                                                                                                                                                                                                                            |

| dataconverter.ti.com   | Automotive                                                                                        | www.ti.com/automotive                                                                                                                                                                                                                       |

| dsp.ti.com             | Broadband                                                                                         | www.ti.com/broadband                                                                                                                                                                                                                        |

| interface.ti.com       | Digital Control                                                                                   | www.ti.com/digitalcontrol                                                                                                                                                                                                                   |

| logic.ti.com           | Military                                                                                          | www.ti.com/military                                                                                                                                                                                                                         |

| power.ti.com           | Optical Networking                                                                                | www.ti.com/opticalnetwork                                                                                                                                                                                                                   |

| microcontroller.ti.com | Security                                                                                          | www.ti.com/security                                                                                                                                                                                                                         |

| www.ti.com/lpw         | Telephony                                                                                         | www.ti.com/telephony                                                                                                                                                                                                                        |

|                        | Video & Imaging                                                                                   | www.ti.com/video                                                                                                                                                                                                                            |

|                        | Wireless                                                                                          | www.ti.com/wireless                                                                                                                                                                                                                         |

|                        | dataconverter.ti.com dsp.ti.com interface.ti.com logic.ti.com power.ti.com microcontroller.ti.com | amplifier.ti.com Audio dataconverter.ti.com Automotive dsp.ti.com Broadband interface.ti.com Digital Control logic.ti.com Military power.ti.com Optical Networking microcontroller.ti.com Security www.ti.com/lpw Telephony Video & Imaging |

Mailing Address: Texas Instruments

Post Office Box 655303 Dallas, Texas 75265