- Charge Pump Provides Negative Gate Bias for Depletion-Mode GaAs Power Amplifiers

- Buffered Clock Output to Drive Additional External Charge Pump

- 135-mΩ High-Side Switch Controls Supply Voltage to the GaAs Power Amplifier

- Power-Good Circuitry Prevents High-Side Switch Turn-on Until Negative Gate Bias is Present

- Charge Pump Can Be Driven From the Internal Oscillator or An External Clock

- 10-µA Maximum Standby Current

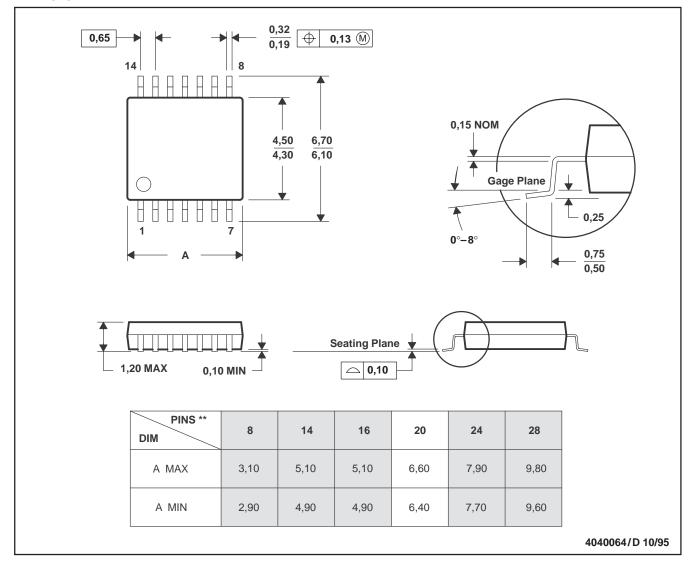

- Low-Profile (1.2-mm Max Height), 20-Pin TSSOP Package

#### **PW PACKAGE** (TOP VIEW) GATE\_BIAS □ 20 VDD V<sub>CC</sub> □ 2 19 CLK C1- 🗆 3 18 **BCLK** 17 C1+ 🗆 **GND** BATT IN 16 BATT OUT BATT IN 15 BATT\_OUT BATT\_IN 🗀 14 BATT\_OUT PGP □ 13 8 SW EN 12 PG □ OSC EN 9 GND □ 10 11

#### description

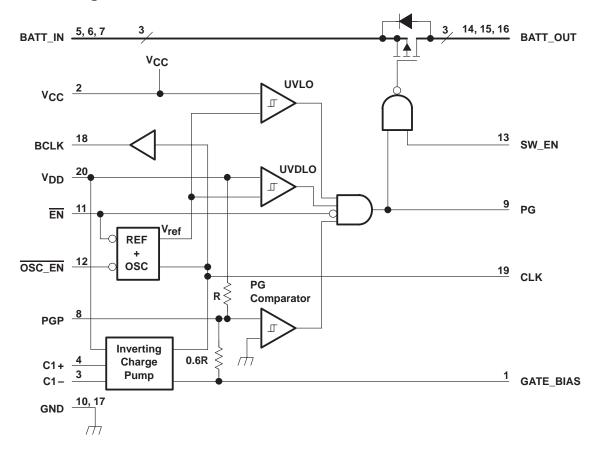

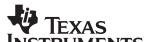

The TPS9103 is a highly integrated power supply for depletion-mode GaAs power amplifiers (PA) in cellular handsets and other wireless communications equipment. Functional integration and low-profile packaging combine to minimize circuit-board area and component height requirements. The device includes: a p-channel MOSFET configured as a high-side switch to control the application of power to the PA; a driver for the high-side switch with a logic-compatible input; a charge pump to provide negative gate-bias voltage; and logic to prevent turn-on of the high-side switch until gate bias is present. The high-side switch has a typical on-state resistance of 135 m $\Omega$ .

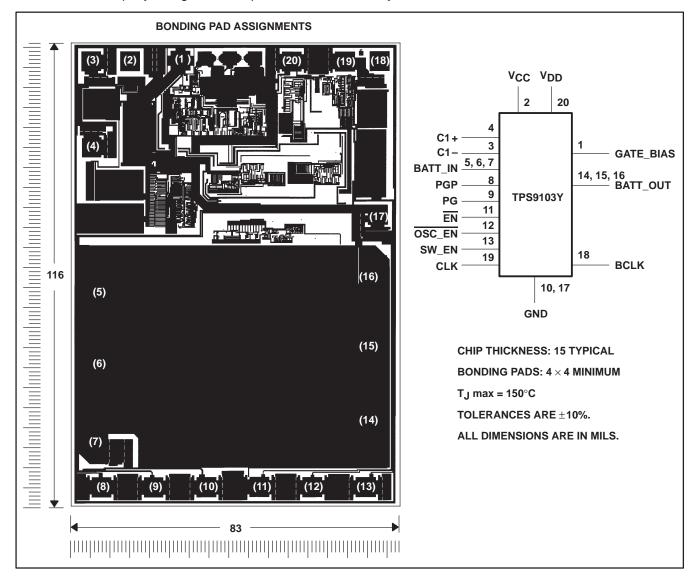

The TPS9103 is available in a 20-pin thin shrink small-outline package (TSSOP) or in chip form. Contact factory for die sales. The device operates over a junction temperature range of –25°C to 125°C.

#### **AVAILABLE OPTIONS**

| - 1           | PACKAGED DEVICE | CHIP FORM |

|---------------|-----------------|-----------|

| TA            | TSS0P<br>(PW)   | (Y)       |

| -25°C to 85°C | TPS9103PWLE     | TPS9103Y  |

The PW package is only available left-end taped and reeled (indicated by the LE suffix on the device type).

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

## TPS9103 POWER SUPPLY FOR GaAs POWER AMPLIFIERS

SLVS131A - OCTOBER 1995 - REVISED JULY 1996

## functional block diagram

## **TPS9103Y chip information**

This chip, when properly assembled, displays characteristics similar to the TPS9103. Thermal compression or ultrasonic bonding may be used on the doped-aluminum bonding pads. The chips may be mounted with conductive epoxy or a gold-silicon preform. Contact factory for die sales.

## TPS9103 POWER SUPPLY FOR GaAs POWER AMPLIFIERS

SLVS131A - OCTOBER 1995 - REVISED JULY 1996

## **Terminal Functions**

| TERMINAL        |     | DECODIFICAL                                           |

|-----------------|-----|-------------------------------------------------------|

| NAME            | NO. | DESCRIPTION                                           |

| GATE_BIAS       | 1   | Negative gate-bias output voltage                     |

| V <sub>CC</sub> | 2   | Logic supply voltage                                  |

| C1-             | 3   | External capacitor connection (inverting charge pump) |

| C1+             | 4   | External capacitor connection (inverting charge pump) |

| BATT_IN         | 5   | High-side switch input voltage                        |

| BATT_IN         | 6   | High-side switch input voltage                        |

| BATT_IN         | 7   | High-side switch input voltage                        |

| PGP             | 8   | Program input for power-good threshold                |

| PG              | 9   | Power-good output                                     |

| GND             | 10  | Ground                                                |

| EN              | 11  | Chip-enable input                                     |

| OSC_EN          | 12  | Oscillator-enable input                               |

| SW_EN           | 13  | High-side switch enable input                         |

| BATT_OUT        | 14  | High-side switch output voltage                       |

| BATT_OUT        | 15  | High-side switch output voltage                       |

| BATT_OUT        | 16  | High-side switch output voltage                       |

| GND             | 17  | Ground                                                |

| BCLK            | 18  | Buffered clock output                                 |

| CLK             | 19  | Clock (bidirectional)                                 |

| $V_{DD}$        | 20  | Charge-pump supply voltage                            |

### detailed description

#### high-side switch and driver (BATT\_IN, BATT\_OUT, SW\_EN)

The high-side switch is a p-channel MOSFET with a maximum on-state resistance of 180 m $\Omega$  ( $V_{I(BATT\_IN)}$ ) = 6 V and  $V_{CC}$  = 3.3 V). The driver pulls the gate of the high-side switch to GATE\_BIAS instead of ground to reduce the MOSFET on-state resistance. Gate breakdown considerations limit the voltage between BATT\_IN and GATE\_BIAS to 15 V. Extremely fast switching times are not required in this application, and the high-side switch/driver is designed to provide 2  $\mu$ s maximum switching times with minimum power consumption. The GaAs depletion-mode MOSFETs in the PA are protected from damage at power-up by internal logic that inhibits the driver until negative gate bias is available. The control input SW\_EN is compatible with 3-V and 5-V CMOS logic; a logic-high input turns the high-side switch on.

#### oscillator (OSC\_EN, CLK)

The internal oscillator drives the charge pump at 50 kHz with a nominal duty cycle of 50% when both the  $\overline{\text{EN}}$  and  $\overline{\text{OSC}_{EN}}$  inputs are logic lows. CLK outputs the internal oscillator signal (no buffer). A logic-high input to  $\overline{\text{OSC}_{EN}}$  disables the internal oscillator and allows the charge pump to operate from an external clock connected to CLK. When an external clock with negative overshoot is applied, a Schottky diode must be added to limit the amplitude of the overshoot.

#### charge pump (GATE\_BIAS, C1+, C1-)

The inverting charge pump generates the negative gate-bias voltage output at GATE\_BIAS.

#### chip enable (EN)

A logic high on  $\overline{EN}$  shuts down the internal functions of the TPS9103 and turns the bias system off, reducing the supply current to less than 10  $\mu$ A. A low input on  $\overline{EN}$  causes normal operation to resume.

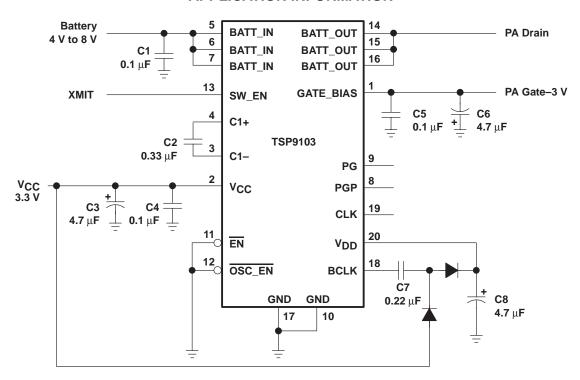

#### power good (PG, PGP)

PG output is logic high when GATE\_BIAS is in regulation. PG output is logic low when GATE\_BIAS is not in regulation. The high-side switch is disabled and PG is forced to logic low whenever the magnitude of GATE\_BIAS is less than  $0.6 \times V_{DD}$ . A modified threshold for the power-good function can be achieved by programming PGP with an external resistor.

#### undervoltage lockout for V<sub>CC</sub> and V<sub>DD</sub> (UVLO and UVDLO)

Undervoltage lockout prevents operation at supply voltages too low for proper operation. When UVLO or UVDLO is active, all power-switch drives are forced to the off state and bias is removed from unneeded functions. Hysteresis is provided to minimize cycling on and off because of source impedance loading when the supply voltage is close to the threshold.

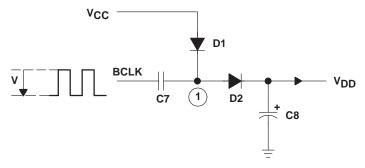

#### buffered clock output (BCLK)

The buffered clock output is a driver for an external charge pump. When the optional external charge pump is not needed, BCLK should be left unconnected. For more details, see the application section.

#### supply input for inverting charge pump (V<sub>DD</sub>)

$V_{DD}$  is the supply voltage for the inverting charge pump. In normal operation,  $V_{DD}$  is connected to  $V_{CC}$ . If the negative gate-bias needs to be larger than  $V_{CC}$  (i.e., more negative), then a higher voltage supply needs to be connected to  $V_{DD}$ . This can be supplied from an external charge pump driven from BCLK.

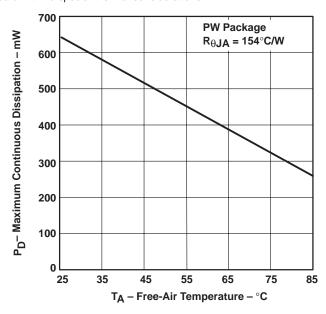

#### **DISSIPATION RATING TABLE**

| PACKAGE | $T_{\mbox{\scriptsize A}} \le 25^{\circ}\mbox{\scriptsize C}$ POWER RATING | DERATING FACTOR<br>ABOVE T <sub>A</sub> = 25°C | T <sub>A</sub> = 70°C<br>POWER RATING | T <sub>A</sub> = 85°C<br>POWER RATING |

|---------|----------------------------------------------------------------------------|------------------------------------------------|---------------------------------------|---------------------------------------|

| PW      | 645 mW                                                                     | 6.5 mW/°C                                      | 353 mW                                | 255 mW                                |

Maximum values are calculated using a derating factor based on  $R_{\theta JA}$  = 154°C/W for the package. These devices are mounted on an FR4 board with no special thermal considerations.

Figure 1. Dissipation vs Free-Air Temperature

## absolute maximum ratings over operating free-air temperature range (unless otherwise noted)†

| High-side switch input voltage range, BATT_IN (see Note 1) |                                            |

|------------------------------------------------------------|--------------------------------------------|

| Supply voltage range, V <sub>CC</sub> , V <sub>DD</sub>    | 0.3 V to 7 V                               |

| Differential voltage,  BATT_IN - GATE_BIAS                 | 15 V                                       |

| Input voltage range, SW_EN, EN, CLK, OSC_EN, PG            | $-0.3 \text{ V to V}_{CC} + 0.3 \text{ V}$ |

| GATE_BIAS                                                  | –5.5 V                                     |

| Output current, PG                                         | 5 mA                                       |

| Output current, BCLK                                       | 50 mA                                      |

| Output current, GATE_BIAS                                  |                                            |

| Output current, BATT_OUT                                   |                                            |

| Peak output current, BATT_OUT                              | 4 A                                        |

| Maximum external clock frequency, CLK                      | 100 kHz                                    |

| Continuous total power dissipation                         |                                            |

| Junction temperature range, T <sub>J</sub>                 | –25°C to 150°C                             |

| Storage temperature range, T <sub>stq</sub>                | 65°C to 150°C                              |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. All voltages are with respect to device GND.

<sup>2.</sup> Differential voltage calculated: |V<sub>I</sub>max| + |GATE\_BIAS|

## TPS9103 POWER SUPPLY FOR GaAs POWER AMPLIFIERS

SLVS131A - OCTOBER 1995 - REVISED JULY 1996

## recommended operating conditions

|                                                   |                        | MIN | NOM  | MAX        | UNIT |

|---------------------------------------------------|------------------------|-----|------|------------|------|

| Input voltage, BATT_IN                            |                        | 3   |      | 9          | V    |

| Supply voltage, V <sub>CC</sub> , V <sub>DD</sub> |                        | 2.7 |      | 5.5        | V    |

| Output voltage, GATE_BIAS, VO                     |                        | -2  |      | <b>–</b> 5 | V    |

| Continuous output current, GATE_BIAS              |                        | 0   |      | 10         | mA   |

| Continuous output current, BATT_OUT               |                        | 0   |      | 2          | Α    |

| Charge-pump capacitor value at C1+/C1-            |                        |     | 0.33 |            | μF   |

| External clock frequency, CLK                     |                        | 25  |      | 75         | kHz  |

| High-level input voltage, VIH                     |                        | 2   |      |            | V    |

| Low-level input voltage, V <sub>IL</sub>          | SW_EN, EN, OSC_EN, CLK |     |      | 0.8        | V    |

| Input current, I <sub>I</sub>                     |                        | -1  |      | 1          | μΑ   |

| Operating junction temperature, T <sub>J</sub>    |                        | -25 |      | 125        | °C   |

electrical characteristics over recommended operating junction temperature range, BATT\_IN = 6 V,  $V_{CC} = V_{DD} = 3.3$  V,  $I_{O(BATT\_OUT)} = 0.5$  A,  $I_{O(GATE\_BIAS)} = 2$  mA,  $\overline{EN} = \overline{OSC\_EN} = 0$  V, SW\_EN =  $V_{CC}$ , C1 = 0.33  $\mu F$  (unless otherwise noted)

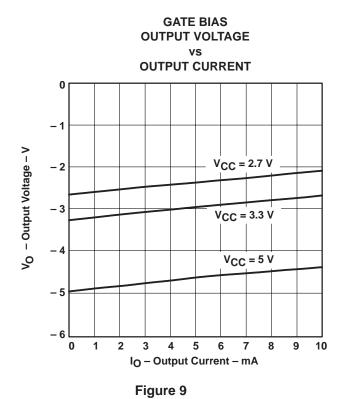

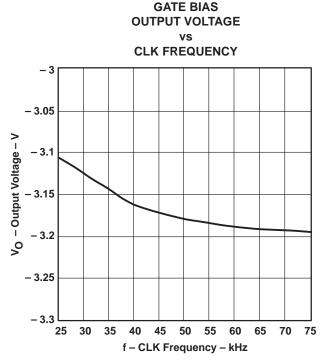

#### charge pump

| PARAMETER         | TEST CONDITIONS | MIN | TYP   | MAX  | UNIT |

|-------------------|-----------------|-----|-------|------|------|

| Output voltage    |                 | -3  | -3.10 | -3.3 | V    |

| Output resistance |                 |     | 95    |      | Ω    |

#### high-side switch

| PARAMETER                          | 1                                       | TEST CONDITIONS                       |             | MIN | TYP | MAX | UNIT |

|------------------------------------|-----------------------------------------|---------------------------------------|-------------|-----|-----|-----|------|

|                                    | T <sub>A</sub> = 25°C                   |                                       |             |     | 135 | 180 |      |

|                                    | $T_A = -25^{\circ}C$ to $85^{\circ}C$   | $T_A = -25^{\circ}C$ to $85^{\circ}C$ |             |     |     | 210 |      |

| Dran-to-source on-state resistance | T <sub>A</sub> = 25°C,                  | V <sub>I</sub> (BATT_IN) = 3 V        |             |     | 160 | 220 | mΩ   |

|                                    | $T_A = -25^{\circ}C$ to $85^{\circ}C$ , | BATT_IN = 3 V                         |             |     |     | 260 |      |

| Leakage current                    | T <sub>A</sub> = 25°C,                  | $V_{I(BATT_IN)} = 9 V$                | SW_EN = 0 V |     |     | 1   | ^    |

|                                    | T <sub>A</sub> = 85°C,                  | V <sub>I</sub> (BATT_IN) = 9 V,       | SW_EN = 0 V |     |     | 10  | μΑ   |

| Delay to high-level output         | SW_EN from 0 to V <sub>C</sub>          | SW_EN from 0 to V <sub>CC</sub>       |             |     | 0.2 | 2   | μs   |

| Delay to low-level output          | SW_EN from V <sub>CC</sub> to           | 0                                     |             |     | 0.9 | 2   | μs   |

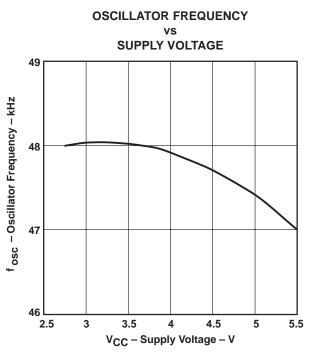

#### oscillator

| PARAMETER  | TEST CONDITIONS                  | MIN | TYP | MAX | UNIT |

|------------|----------------------------------|-----|-----|-----|------|

| Frequency  | V <sub>CC</sub> = 2.7 V to 5.5 V | 35  | 50  | 60  | kHz  |

| Duty cycle | V <sub>CC</sub> = 2.7 V to 5.5 V | 40% | 50% | 60% |      |

## buffered clock output (BCLK)

| PARAMETER                 | TEST CONDITIONS | MIN                   | TYP | MAX | UNIT |

|---------------------------|-----------------|-----------------------|-----|-----|------|

| Output resistance         |                 |                       |     | 10  | Ω    |

| High-level output voltage | I(BCLK) = 30 mA | V <sub>C</sub> C -0.3 |     |     | V    |

| Low-level output voltage  | I(BCLK) = 30 mA |                       |     | 0.3 | V    |

## TPS9103 POWER SUPPLY FOR GaAs POWER AMPLIFIERS

SLVS131A - OCTOBER 1995 - REVISED JULY 1996

## power good (PG)

| PARAMETER         | TEST CONDITIONS                                                         | MIN                  | TYP                  | MAX | UNIT |

|-------------------|-------------------------------------------------------------------------|----------------------|----------------------|-----|------|

| Threshold voltage | $V_{DD} = 2.7 \text{ V to } 5.5 \text{ V}$                              |                      | $0.60 \times V_{DD}$ |     | V    |

| On-state voltage  | $I_{O(PG)} = 500 \mu\text{A},  V_{CC} = 2.7 \text{V to } 5.5 \text{V}$  |                      |                      | 0.3 | V    |

| Off-state voltage | $I_{O(PG)} = -500 \mu\text{A},  V_{CC} = 2.7 \text{V to } 5.5 \text{V}$ | V <sub>CC</sub> −0.3 |                      |     | V    |

| Hysteresis        |                                                                         |                      | 130                  |     | mV   |

## power good (PGP)

| PARAMETER       | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|-----------------|-----------------|-----|-----|-----|------|

| Input impedance |                 | 85  |     |     | kΩ   |

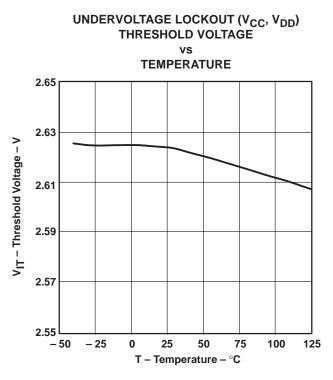

## undervoltage lockout (UVLO + UVDLO)

| PARAMETER               | TEST CONDITIONS            | MIN | TYP | MAX | UNIT |

|-------------------------|----------------------------|-----|-----|-----|------|

| Start threshold voltage | V <sub>CC</sub> increasing | 2.4 |     | 2.7 | V    |

| Hysteresis              |                            |     | 130 |     | mV   |

## supply current ( $I_{CC}$ and $I_{DD}$ )

| PARAMETER            | TEST CONDITIONS                           | MIN | TYP | MAX | UNIT |

|----------------------|-------------------------------------------|-----|-----|-----|------|

| Standby mode         | EN = V <sub>CC</sub>                      |     | 1   | 10  | μΑ   |

| Undervoltage lockout | V <sub>CC</sub> = V <sub>DD</sub> < 2.3 V |     | 35  | 50  | μΑ   |

| Operating mode       | No load                                   |     | 300 | 500 | μΑ   |

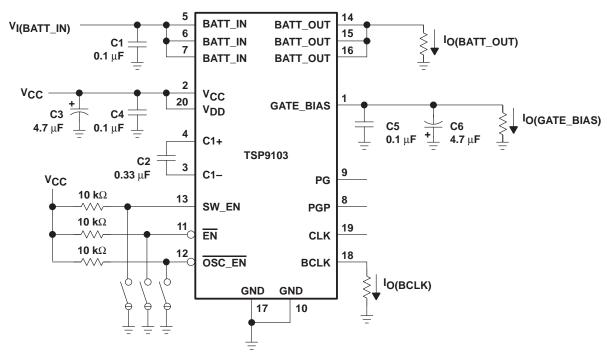

#### PARAMETER MEASUREMENT INFORMATION

Figure 2. Test Circuit

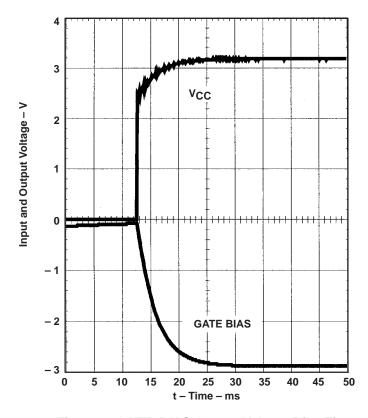

Figure 3. GATE\_BIAS Output Voltage Rise Time

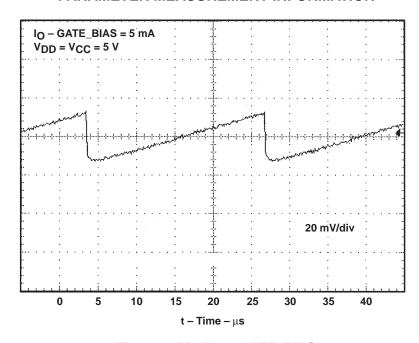

#### PARAMETER MEASUREMENT INFORMATION

Figure 4. Ripple on GATE\_BIAS

#### **TYPICAL CHARACTERISTICS**

#### **TABLE OF GRAPHS**

|                |                                                     |                            | FIGURE |

|----------------|-----------------------------------------------------|----------------------------|--------|

| rDS(on)        | Static drain-source on-state resistance             | vs Gate-source voltage, dc | 5      |

|                |                                                     | vs Temperature             | 6      |

| Fosc           | Oscillator frequency                                | vs Supply voltage          | 7      |

|                |                                                     | vs Temperature             | 8      |

| V <sub>O</sub> | Output voltage                                      | vs Output current          | 9      |

|                |                                                     | vs CLK frequency           | 10     |

| VIT            | Threshold voltage                                   | vs Temperature             | 11     |

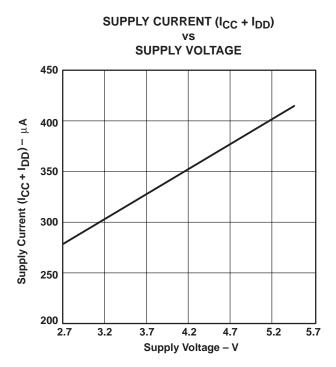

|                | Supply current (I <sub>CC</sub> + I <sub>DD</sub> ) | vs Supply voltage          | 12     |

|                |                                                     | vs Temperature             | 13     |

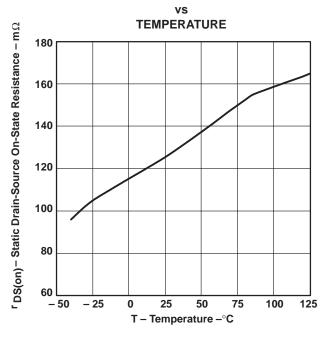

#### STATIC DRAIN-SOURCE ON-STATE RESISTANCE

## vs r DS(on) – Static Drain-Source On-State Resistance – m $\Omega$ 190 GATE-SOURCE VOLTAGE, 180 dc (V<sub>O(GATE\_BIAS)</sub> -V<sub>I(BATT\_IN)</sub>) 170 160 150 140 130 120 110 100 - 12 V<sub>GS</sub> – Gate-Source Voltage, dc (V<sub>O</sub>(GATE\_BIAS) –VI(BATT\_IN))

Figure 5

# HIGH-SIDE SWITCH STATIC DRAIN-SOURCE ON-STATE RESISTANCE

Figure 6

#### **TYPICAL CHARACTERISTICS**

**OSCILLATOR FREQUENCY TEMPERATURE** 49.5 f osc - Oscillator Frequency - kHz 49 3.3 V 48.5 2.7 V 48 47.5 - 50 - 25 25 50 75 100 125 T - Temperature - °C

Figure 7

Figure 10

#### **TYPICAL CHARACTERISTICS**

Figure 11 Figure 12

Figure 13

#### THERMAL INFORMATION

Implementation of integrated circuits in low-profile and fine-pitch packages requires special attention to power dissipation. Many system-dependent issues such as thermal coupling, airflow, added heat sinks and convection surfaces, and the presence of other heat-generating components affect the power-dissipation limits of a given component.

Three basic approaches for enhancing thermal performance are listed below:

- Improving the power-dissipation capability of the PWB design

- Improving the thermal coupling of the component to the PWB

- Introducing airflow in to the system

Using the given  $R_{\theta JA}$  for this IC, the maximum power dissipation can be calculated with the equation:

$$P_{D}max = \frac{T_{J}max - T_{A}}{R_{\theta, JA}}$$

For the TPS9103, the power dissipation is in the PMOSFET. To calculate the power, use:  $I^2 \times R$  where I is the current through the device and R is the internal resistance as shown in the electrical characteristics table.

For a  $V_I$  of 6 V, the resistance at 85°C is 0.210  $\Omega$ . At a current of 2 A, the peak power dissipation is:

$$P_D = 2^2 \times 0.210 = 0.84 \text{ W}$$

Assuming a duty cycle of 1/8 or 0.125, the average power is:

$$0.84 \text{ W} \times 0.125 = 0.105 \text{ W}$$

The change in temperature is:

$$\Delta T = 0.105 \text{ W} \times 154^{\circ}\text{C/W} = 16.2^{\circ}\text{C}$$

and the junction temperature is:

$$T_J = 85^{\circ}C + 16.2^{\circ}C = 101.2^{\circ}C$$

#### APPLICATION INFORMATION

#### introduction

Traditionally the RF power amplifier (PA) is powered directly from the battery, with a switching arrangement for powering down when not in use. GaAs FET PAs require a negative bias voltage that must be present before the supply is connected, or there is risk of destroying the FET. Logic must be provided to ensure the presence of the negative bias voltage.

A secondary charge pump is necessary for systems in which the supply voltage is insufficiently high – the negative bias produced from the charge pump is inadequate. In mobile telephony a second charge pump (regulated or unregulated) may also be needed, e.g. for varicap diodes/VCOs and some preamplifiers. The need for larger dynamic range or control-voltage range can become critical in certain applications.

#### the TPS9103 approach

The TPS9103 integrates a P-channel MOSFET high-side switch together with a selectable oscillator and charge pump for the GaAs FET power-amplifier gate bias, which is monitored.

Complete precautions are taken to ensure that the PA supply is not enabled unless the gate bias is present while  $V_{CC}$  and  $V_{DD}$  are also good. This protects the PA from inadvertent damage—without a major system size/cost increase.

The bias regulation monitor is flexible, accommodating both fixed and programmable approaches. The fixed resistors, provided internally, set the trip voltage to  $-0.6 \times V_{DD}$ . If  $V_{DD}$  is 5 V, then the trip voltage is -3 V. Should another value be preferred, it can be set by applying voltage divider to PGP. See the section "dimensioning the external voltage divider" for more details.

The charge pump clock is also flexible. The on-chip oscillator runs at a nominal 50 kHz, or alternatively an external oscillator can be connected to CLK. When an external clock is used, OSC\_EN should be taken high to disable the oscillator. When OSC\_EN is low and the on-chip oscillator is used, CLK provides an unbuffered clock output.

The circuit provides for a secondary charge pump driver. The buffered BCLK output can be used (with four external components) to provide a higher supply, both for those system functions that require it and for those GaAs PAs that need a more negative bias than is made possible by inverting the existing supply. This is facilitated by use of single-cell Li-ion batteries.

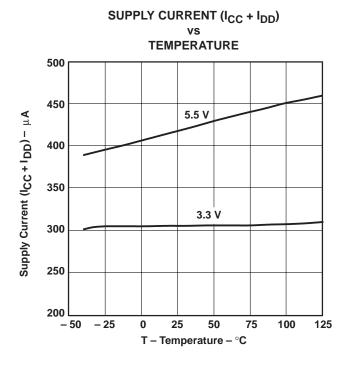

Figure 14 shows the TPS9103 in a typical application.

Figure 14. Typical Application

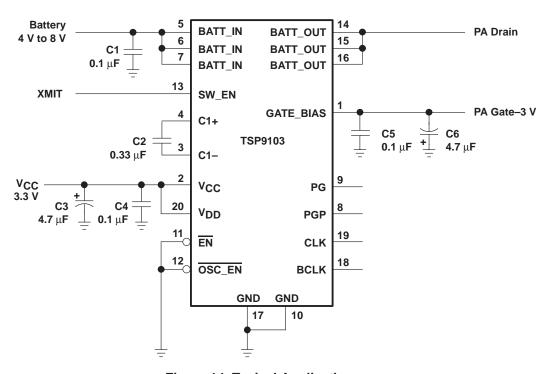

#### capacitors of the internal inverting charge pump (see Figure 15)

This charge pump inverts the voltage at V<sub>DD</sub> and provides a negative output voltage at GATE\_BIAS.

Figure 15. Internal Inverting Charge Pump

The output capacitor C6 limits the voltage ripple at GATE\_BIAS:

$$V_{Ripple} = \frac{I_{O(GATE\_BIAS)}}{C6 \times f}$$

With a capacitor C6 of 4.7 µF and an output current of 10 mA, the voltage ripple at GATE\_BIAS is 42 mV.

The capacitor C2 can be calculated using an equivalent resistance method:

$$R_{\text{equivalent}} = \frac{1}{C2 \times f}$$

Using 0.33 µF for C2, the equivalent resistance is:

$$R_{\text{equivalent}} = \frac{1}{0.33 \text{ } \mu\text{F} \times 50 \text{ kHz}} = 60.6 \text{ } \Omega$$

Add the internal resistance of the switches (35  $\Omega$ ) to get a total resistance seen by the current:

$$R_{TOTAL} = 60 + 35 = 95 \Omega$$

With a total resistance of 95  $\Omega$  and 10 mA flowing through it, a voltage drop of 0.95 V occurs. With 5 V on V<sub>DD</sub>, the output is -4.05 V with a 42 mV ripple.

The capacitors should have a low equivalent series resistance (ESR) to maintain low ripple and low noise. Careful layout is required. In most instances it is advisable to add a small decoupling capacitor C5 close to the GATE\_BIAS. An additional  $0.1-\mu F$  capacitor at other locations may be necessary if the power amplifier is located away from the TPS9103.

#### dimensioning of the external charge pump

For systems in which the bias voltage requirement is not met by inverting the power rail, the BCLK output can be used (with four passive components) to generate a higher V<sub>DD</sub>. The higher voltage is then inverted as before to produce the bias voltage. This voltage is also available for other parts of the main circuitry (see Figure 16).

With the TPS9103, an external charge pump could be used to increase the voltage at V<sub>DD</sub>, thereby deriving a higher negative voltage at GATE\_BIAS than would otherwise be available.

Figure 16. External Charge Pump

When BCLK is low, node 1 charges up to  $V_{CC} - V_{diode}$ . When BCLK goes high, node 1 is  $2 \, V_{CC} - V_{diode}$ . The capacitor C8 charges up to  $2 \, V_{CC} - 2 \, V_{diode}$ . This voltage can then be connected to  $V_{DD}$ .

The magnitude of  $V_{ripple}$  of  $V_{DD}$  is determined by the value of C8. Capacitor value must be large enough that the discharge during one period is not as great as the maximum voltage variation allowable. The discharge of C8 depends on the load current.

$$C8 = \frac{I_{O(GATE\_BIAS)}}{V_{ripple} \times f}$$

With a supply voltage of  $V_{CC}$  = 3.3 V, a maximum voltage variation ( $V_{ripple}$ ) of 2% = 66 mV and a load of  $I_{CC}$  = 10 mA, the value of C8 is 3  $\mu$ F. A 4.7  $\mu$ F meets this requirement.

The capacitance of C7 can be calculated using an equivalent resistance method:

$$R_{equivalent} = \frac{1}{C7 \times f}$$

Using 0.22 µF for C7, the equivalent resistance is:

$$R_{\text{equivalent}} = \frac{1}{0.22 \text{ } \mu\text{F} \times 50 \text{ kHz}} = 90 \Omega$$

Add the equivalent resistance to the internal resistance of the switch (10  $\Omega$ ):

$$R_{TOTAL} = 90 + 10 = 100 \Omega$$

With a total resistance of 100  $\Omega$  and with 10 mA flowing through it, a voltage drop of 1 V occurs. Thus with 3.3 V on V<sub>CC</sub> the output is 4.2 V with a 42-mV ripple.

Care must be taken that the maximum voltages are not exceeded when using BCLK as a charge pump (see Figure 17).

Figure 17. TPS9103 Configured With External Charge Pump

#### dimensioning the external voltage divider

Drain voltage should only be applied to the power amplifier when the complete negative voltage from the GATE\_BIAS output is provided to the gate of the GaAs power amplifier. For that reason there is an internal voltage divider R/0.6R and a PG comparator in the TPS9103 (see Figure 15). When the voltage at the inverting input of the comparator reaches zero, the output goes high and the high-side MOSFET switches on, provided a SW\_EN high signal is applied. For example, when the supply voltage at  $V_{DD}$  is 5 V, the high-side switch is switched on when the voltage at GATE\_BIAS reaches -3 V.

This trip point can be changed to another value by using an external voltage divider connected between  $V_{DD}$ , GATE\_BIAS, and PGP. The resistor values should be low enough to minimize the error that is present when the internal resistor values (typ R = 100 k $\Omega$  ± 30%) are taken into consideration. Therefore, the external resistor values, R1 and R2, are chosen within the 10-k $\Omega$  range.

Figure 18. External Voltage Divider for Setting the Trip Point

R1 = 10 k $\Omega$ . The value of R2 can then be calculated using:

$$R2 = \frac{-0.6 \times R \times R1 \times V_{trip}}{0.6 \times V_{DD} \times [R1 + R] + V_{trip} \times R1}$$

where  $V_{DD}$  = supply voltage, and  $V_{trip}$  = chosen value to trip PG comparator.

The values of the internal resistor can vary about 30%, and can move the trip point. In a worst-case condition, with a resistor variation of 30%, the shifting of the trip point can be calculated to:

$$\Delta V_{trip\_point} = V_{DD} \times \left( \frac{R1 + 1.3 \times R}{R1} \times \frac{0.6 \times R2}{R2 + 0.78 \times R} - \frac{R1 + R}{R1} \times \frac{0.6 \times R2}{R2 + 0.6 \times R} \right)$$

#### **MECHANICAL DATA**

## PW (R-PDSO-G\*\*)

#### 14 PIN SHOWN

#### PLASTIC SMALL-OUTLINE PACKAGE

NOTES: A. All linear dimensions are in millimeters.

B. This drawing is subject to change without notice.

C. Body dimensions do not include mold flash or protrusion not to exceed 0,15.

D. Falls within JEDEC MO-153

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1998, Texas Instruments Incorporated