# 捷多邦,专业PCB打样工厂,24小时的B8284A CLOCK GENERATOR AND DRIVER FOR 8086/8088 MICROPROCESSORS

## Description

The  $\mu$ PB8284 is a clock generator and driver for the 8086 and 8088 microprocessors. This bipolar driver provides the microprocessor with a reset signal and also provides properly synchronized READY timing. A TTL clock is also provided for peripheral devices.

#### **Features**

- Generates system clock for the 8086 and 8088

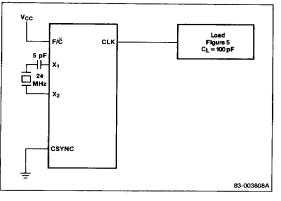

- Frequency source can be a crystal or a TTL signal

- MOS level output for the processor

- TTL level output for the peripheral devices

- Power-up reset for the processor

- READY synchronization

- □ +5V supply

### **Ordering Information**

| Part<br>Number     | Package Type  | Max Frequency<br>of Operation |

|--------------------|---------------|-------------------------------|

| μ <b>PB8</b> 284AD | 18-Pin cerdip | 25 MHz ÷ 3                    |

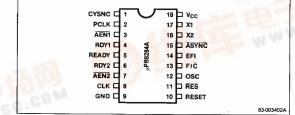

### **Pin Identification**

| No.    | Symbol     | Function                 |  |  |  |  |  |

|--------|------------|--------------------------|--|--|--|--|--|

| CSYNC  |            | Clock synchronization    |  |  |  |  |  |

| 2      | PCLK       | Peripheral clock         |  |  |  |  |  |

| 3, 7   | AEN1, AEN2 | Address enable           |  |  |  |  |  |

| 4,6    | RDY1, RDY2 | Bus ready                |  |  |  |  |  |

| 5      | READY      | Ready                    |  |  |  |  |  |

| 8      | CLK        | Processor clock          |  |  |  |  |  |

| 9      | GND        | Ground                   |  |  |  |  |  |

| 10     | RESET      | Reset                    |  |  |  |  |  |

| 11     | RES        | Reset in                 |  |  |  |  |  |

| 12     | OSC        | Oscillator output        |  |  |  |  |  |

| 13     | F/C        | Frequency crystal select |  |  |  |  |  |

| 14     | EFI        | External frequency in    |  |  |  |  |  |

| 15     | ASYNC      | Asynchronous input       |  |  |  |  |  |

| 16, 17 | X1, X2     | Crystal in               |  |  |  |  |  |

| 18     | Vcc        | V <sub>CC</sub>          |  |  |  |  |  |

|        |            |                          |  |  |  |  |  |

## **Pin Configuration**

## **Pin Functions**

#### **Clock Synchronization**

An active high signal which allows multiple 8284s to be synchronized. When CYSNC is low, the internal counters count, and when high, the counters are reset. CYSNC should be grounded when the internal oscillator is used.

### Peripheral Clock

A TTL level clock for use with peripheral devices. This clock is one-half the frequency of CLK.

### **Address Enable**

This active low signal is used to qualify its respective RDY inputs. If there is only one bus to interface to, AEN inputs are to be grounded.

#### **Bus Ready**

This signal is sent to the 8284 from a peripheral device on the bus to indicate that data has been received or data is available to be read.

### Ready

The READY signal to the microprocessor is synchronized by the RDY inputs to the processor CLK. READY is cleared after the guaranteed hold time to the processor has been met.

### Processor Clock

This is the MOS level clock output of 33% duty cycle to drive the microprocessor and bipolar support devices (8288) connected to the processor. The frequency of CLK is one third of the crystal or EFI frequency.

### Ground

Ground.

### Reset

This is used to initialize the processor. Its input is derived from an RC connection to a Schmitt trigger input for power up operation.

#### **Reset In**

The Schmitt trigger input is used to determine the timing of RESET out via an RC circuit.

#### **Oscillator Output**

This TTL level clock is the output of the oscillator circuit running at the crystal frequency.

#### **Frequency Crystal Select**

$F/\overline{C}$  is a strapping option used to determine where CLK is generated. A high is for the EFI input, and a low is for the crystal.

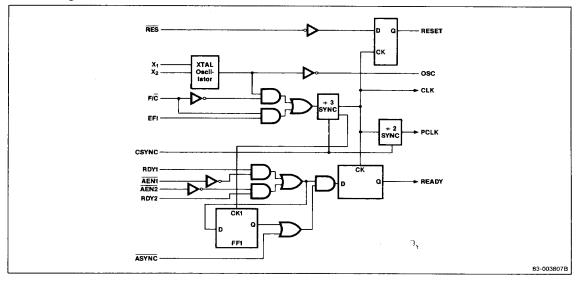

#### **Block Diagram**

#### **External Frequency In**

A square wave in at three times the CLK output. A TTL level clock to generate CLK.

#### Asynchronous Input

Ready Synchronization Select. ASYNC is an input which defines the synchronization mode of the READY logic. When ASYNC is low, two stages of READY synchronization are provided. When ASYNC is left open or HIGH, a single stage of READY synchronization is provided.

### **Crystal In**

A crystal is connected to these inputs to generate the processor clock. The crystal frequency is three times the desired CLK output.

### V<sub>CC</sub> Supply Voltage

+5V supply.

### **Functional Description**

The clock generator can provide the system clock from either a crystal or an external TTL source. There is an internal divide-by-three counter which receives its input from either the crystal or TTL source (EFI pin) depending on the state of the  $F/\bar{C}$  input strapping. There is also a clear input (C SYNC) which is used for either inhibiting the clock, or synchronizing it with an external event (or perhaps another clock generator chip). Note that if the TTL input is used, the crystal oscillator section can still be used for an independent clock source, using the OSC output.

For driving the MOS output level, there is a 33% duty cycle MOS output (CLK) for the microprocessor, and a TTL output (PCLK) with a 50% duty cycle for use as a peripheral clock signal. This clock is at one-half of the processor clock speed.

Reset timing is provided by a Schmitt trigger input ( $\overline{RES}$ ) and a flip-flop to synchronize the reset timing to the falling edge of CLK. Power-on reset is provided by a simple RC circuit on the  $\overline{RES}$  input.

### **Absolute Maximum Ratings**

T<sub>A</sub> = 25 °C

| -0.5 V to +7 V    |  |  |

|-------------------|--|--|

| - 1.0 V to +5.5 V |  |  |

| -0.5 V to +7 V    |  |  |

| -0°C to +70°C     |  |  |

| -65°C to +150°C   |  |  |

|                   |  |  |

**Comment:** Exposing the device to stresses above those listed in Absolute Maximum Ratings could cause permanent damage. The device is not meant to be operated under conditions outside the limits described in the operational sections of the specification. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **DC Characteristics**

$T_A = 0$  °C to +70 °C,  $V_{CC} = +5 V \pm 10\%$

|                                  |                                        | Limits |     |       |      | Test                         |

|----------------------------------|----------------------------------------|--------|-----|-------|------|------------------------------|

| Parameter                        | Symbol                                 | Min    | Тур | Max   | Unit | Conditions                   |

| Input voltage<br>low             | VIL                                    |        |     | +0.8  | V    | V <sub>CC</sub> = 5.0 V      |

| Input voltage<br>high            | VIH                                    | 2      |     |       | V    | V <sub>CC</sub> = 5.0 V      |

| Output voltage<br>low            | V <sub>OL</sub>                        |        |     | +0.45 | ۷    | $5 \text{ mA} = I_{OL}$      |

| Output voltage<br>high (CLK)     | V <sub>0H</sub>                        | 4      |     |       | V    | $-1 \text{ mA} = I_{OH}$     |

| (Other outputs)                  |                                        | 2.4    |     |       | ٧    | $-1 \text{ mA} = I_{OH}$     |

| Forward input<br>current (ASYNC) | IF                                     |        |     | - 1.3 | mA   | $V_{F} = 0.45 V$             |

| (Other inputs)                   |                                        |        |     | -0.5  | mA   | $V_{\rm F} = 0.45  \rm V$    |

| Reverse input<br>current         | I <sub>R</sub>                         |        |     | 50    | μA   | $V_{R} = 5.25 V$             |

| Input forward<br>clamp voltage   | V <sub>C</sub>                         |        |     | -1.0  | ۷    | $I_{\rm C} = -5 \mathrm{mA}$ |

| Reset input high<br>voltage      | V <sub>IHR</sub>                       | 2.6    |     |       | ۷    | $V_{CC} = 5.0 V$             |

| RES input<br>hysteresis          | V <sub>IHR</sub> -<br>V <sub>ILR</sub> | 0.25   |     |       | ۷    | V <sub>CC</sub> =5.0V        |

| Power supply<br>current          | lcc                                    |        |     | 140   | mA   |                              |

There are two READY inputs, each with its own qualifier (AEN1, AEN2). The unused AEN signal should be tied low.

The READY logic in the 8284A synchronizes the RDY1 and RDY2 asynchronous inputs to the processor clock to insure proper set up time, and to guarantee proper hold time before clearing the ready signal.

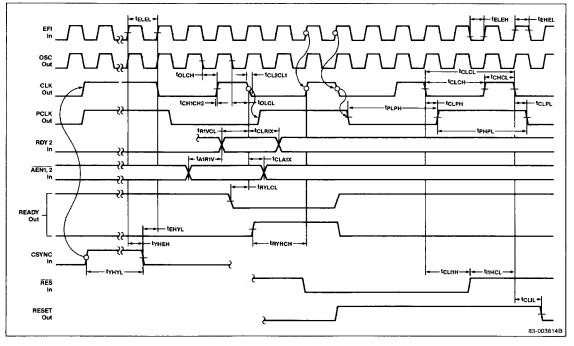

#### **AC Characteristics**

$T_A = 0^{\circ}C$  to +70°C,  $V_{CC} = 5 V \pm 10\%$

|                                         | Limits              |                     |     |     |      | Test                    |

|-----------------------------------------|---------------------|---------------------|-----|-----|------|-------------------------|

| Parameter                               | Symbol              | Min                 | Тур | Max | Unit | Conditions              |

| Timing Requiren                         | nents               |                     |     |     |      |                         |

| External<br>frequency time<br>high      | tehel               | 13                  |     |     | ns   | 90%-90% V <sub>IN</sub> |

| External<br>frequency time<br>low       | t <sub>eleh</sub>   | 13                  |     |     | ns   | 10%-10% V <sub>IN</sub> |

| EFI period                              | telel               | (5)                 |     |     | ns   | (Note 1)                |

| XTAL frequency                          |                     | 12                  |     | 25  | MHz  |                         |

| RDY1, RDY2<br>set-up to CLK             | t <sub>r1vcl</sub>  | 35                  | -   |     | ns   |                         |

| RDY1, RDY2<br>hold to CLK               | t <sub>CLR1X</sub>  | 0                   |     |     | ns   |                         |

| AEN1, AEN2<br>set-up to RDY1,<br>RDY2   | t <sub>A1VR1V</sub> | 15                  |     |     | ns   |                         |

| AEN1, AEN2<br>hold to CLK               | <sup>t</sup> CLA1X  | 0                   |     |     | ns   |                         |

| CSYNC set-up to<br>EFI                  | tyheh               | 20                  |     |     | ns   |                         |

| CSYNC hold to<br>EFI                    | t <sub>ehyl</sub>   | 10                  |     |     | ns   |                         |

| CSYNC width                             | tyhyl               | 2 t <sub>ELEL</sub> |     | _   | ns   |                         |

| RES set-up to<br>CLK                    | t <sub>I1HCL</sub>  | 65                  |     |     | ns   | (Note 2)                |

| RES hold to CLK                         | t <sub>CLI1H</sub>  | 20                  |     |     | ns   | (Note 2)                |

| RDY1, RDY2<br>active set-up to<br>CLK   | <sup>t</sup> r1VCH  | 35                  | •   |     | ns   | ASYNC = Low             |

| RDY1, RDY2<br>inactive set-up<br>to CLK | <sup>†</sup> R1VCL  | 35                  |     |     | ns   |                         |

| ASYNC set-up to<br>CLK                  | TAYVCL              | 50                  |     |     | ns   |                         |

| ASYNC hold to<br>CLK                    | t <sub>CLAYX</sub>  | 0                   |     |     | ns   |                         |

| Input rise time                         | t <sub>ILIH</sub>   |                     |     | 20  | ns   | From 0.8 V to 2.0       |

| Input fall time                         | t <sub>ILIL</sub>   |                     |     | 12  | ns   | From 2.0 V to 0.8       |

#### **AC Characteristics (cont)**

$T_A = 0$  °C to +70 °C,  $V_{CC} = 5 V \pm 10\%$

|                                  | Limits              |     |     |     |      | Test                               |

|----------------------------------|---------------------|-----|-----|-----|------|------------------------------------|

| Parameter                        | Symbol              | Min | Тур | Max | Unit | Conditions                         |

| Timing Response                  | 8                   |     |     |     |      |                                    |

| CLK cycle period                 | t <sub>CLCL</sub>   | 125 |     |     | ns   |                                    |

| CLK time high                    | tchcl.              | (6) |     |     | ns   | Figure 1 and figure 2              |

| CLK time low                     | tclch               | (7) |     |     | ns   | Figure 1 and figure 2              |

| CLK rise and fall<br>time        | tCH1CH2,<br>tCL2CL1 |     |     | 10  | ns   | 1.0 V to 3.5 V                     |

| PCLK time high                   | t <sub>PHPL</sub>   | (8) |     |     | กร   |                                    |

| PCLK time low                    | t <sub>PLPH</sub>   | (8) |     |     | ns   |                                    |

| Ready inactive to<br>CLK         | TRYLCL              | - 8 |     |     | ns   | Figure 3 and figure<br>4, (Note 4) |

| Ready active to<br>CLK           | tryhch              | (7) |     |     | ns   | Figure 3 and figure<br>4, (Note 3) |

| CLK to reset<br>delay            | t <sub>CLIL</sub>   |     |     | 40  | ΠS   |                                    |

| CLK to PCLK<br>high delay        | tclph               |     |     | 22  | ns   |                                    |

| CLK to PCLK low<br>delay         | tCLPL               |     |     | 22  | ns   |                                    |

| OSC to CLK high<br>delay         | tolch               | -5  |     | 12  | ns   |                                    |

| OSC to CLK low<br>delay          | tolcl               | 2   |     | 22  | ns   |                                    |

| Output rise time<br>(except CLK) | toloh               |     |     | 20  | ns   | From 0.8 V to 2.0 V                |

| Output fall time<br>(except CLK) | tohol               |     |     | 12  | ns   | From 2.0 V to 0.8 V                |

## **AC Test Circuits**

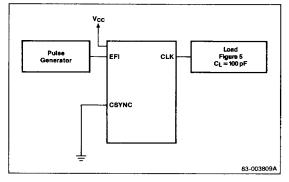

## Figure 1. Clock High and Low Time

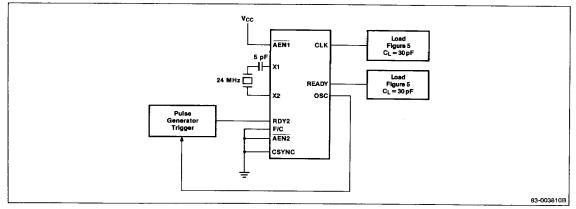

## Figure 2. Clock High and Low Time

#### Note:

į

(1)  $\delta = EFI$  rise (5 ns max) + EFI fall (5 ns max).

(2) Set-up and hold only necessary to guarantee recognition at next clock.

(3) Applies only to T3 and TW states.

(4) Applies only to T2 states.

(5) tEHEL +tELEH +d

(6) (1/3 t<sub>CLCL</sub>) + 2.0

(7) (2/3 t<sub>CLCL</sub>) - 15.0

(8) t<sub>CLCL</sub> - 20

## μ**ΡΒ8284Α**

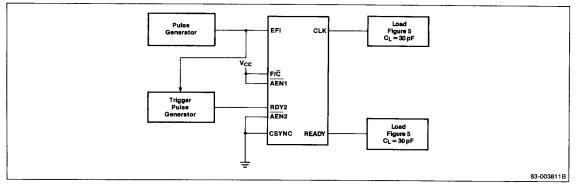

## Figure 3. Ready to CLK

#### Figure 4. Ready to CLK Output

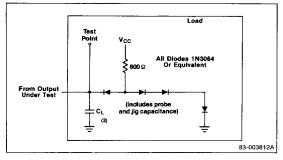

Figure 5. AC Load

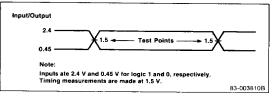

Figure 6. Timing Measurement Points

# μ**ΡΒ8284Α**

## **Timing Waveform**