#### Description

The  $\mu$ PD7003 is a high speed, high performance, low power, 8-bit analog-to-digital Converter designed to be easily interfaced to the 8080 and 8086, 8- and 16-bit microprocessors. Using the parallel conversion technique, the  $\mu$ PD7003 features a conversion speed of 4  $\mu$ s and eliminates the need of sample and hold circuits in most applications. The  $\mu$ PD7003 is also capable of running under DMA control using a DMA controller such as the  $\mu$ PD8257. Available in a 24-pin ceramic/plastic DIP, the  $\mu$ PD7003 is the ideal converter for high speed 8-bit designs.

#### **Features**

- ☐ High speed conversion (250 k samples/sec. max.)

☐ Input consists of 255/1 matched autozeroed comparators

☐ No missing codes over temperature range

☐ Linearity +1 25 L SB max

- ☐ Linearity ±1.25 LSB max.

- ☐ Three-state outputs

- □ Overrange output

- ☐ Operates from single +5 V supply

- ☐ Low power consumption (50 mW)

# **Ordering Information**

| Part<br>Number | Package     | Operating<br>Temperature<br>Range |

|----------------|-------------|-----------------------------------|

| μP07003C       | Plastic DIP | -20°C to +70°C                    |

# **Absolute Maximum Ratings**

| Analog GND Voltage    | ±0.3              |

|-----------------------|-------------------|

| Power Dissipation     | 300 mV            |

| Power Supply          | -0.3 to +7 \      |

| All Input Voltages    | -0.3 to V+ +0.3 \ |

| Storage Temperature   | −65 to +125°C     |

| Operating Temperature | -20 to +70°C      |

Comment: Stress above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

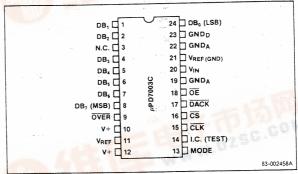

## Pin Configuration

#### Pin Identification

| Pin | Name                  | Function                                                              |

|-----|-----------------------|-----------------------------------------------------------------------|

| 1   | DB <sub>1</sub>       | 7th bit output                                                        |

| 2   | DB <sub>2</sub>       | 6th bit output                                                        |

| 3   | NC                    | Non connection                                                        |

| 4   | DB <sub>3</sub>       | 5th bit output                                                        |

| 5   | DB <sub>4</sub>       | 4th bit output                                                        |

| 6   | DB <sub>5</sub>       | 3th bit output                                                        |

| 7   | DB <sub>6</sub>       | 2th bit output                                                        |

| 8   | DB <sub>7</sub>       | MSB output                                                            |

| 9   | OVER                  | Overrange output                                                      |

| 10  | V+                    | Power supply (+5 V)                                                   |

| 11  | VREF                  | Reference voltage input (positive)                                    |

| 12  | V+                    | Power supply (+5 V)                                                   |

| 13  | MODE                  | MODE control (note 1)                                                 |

| 14  | TEST                  | Low: Device test (used for inspecting the device)<br>High: Conversion |

| 15  | CLK                   | Low: Previous data output<br>High: Quantizing                         |

| 16  | CS                    | Chip select                                                           |

| 17  | DACK                  | DMA Acknowledge                                                       |

| 18  | ŌĒ                    | Low: Data output<br>High: High impedance                              |

| 19  | AGND                  | Analog ground                                                         |

| 20  | VIN                   | Voltage input                                                         |

| 21  | V <sub>REF(GND)</sub> | GND for V <sub>REF</sub>                                              |

| 22  | AGND                  | Analog ground                                                         |

| 23  | GND                   | Digital ground                                                        |

| 24  | DB <sub>O</sub> (LSB) | LSB                                                                   |

|     |                       |                                                                       |

# Pin Identification (Cont.)

| Pin | Name             | Function                                    |

|-----|------------------|---------------------------------------------|

| 19  | GNDA             | Analog ground                               |

| 20  | VSIN             | Analog input                                |

| 21  | VREFN            | Reference voltage input (negative) (Note 2) |

| 22  | GNDA             | Analog ground                               |

| 23  | GND <sub>D</sub> | Digital Ground                              |

| 24  | DBO              | LSB output                                  |

Notes: 1.

|      | Inputs |                                  |  |  |  |

|------|--------|----------------------------------|--|--|--|

| Mode | ŌĒ     | 8-Bit Register                   |  |  |  |

| 1    | 1      | Data refreshed with every CONV 1 |  |  |  |

| •    | 0      | -<br>-                           |  |  |  |

| n    | 1      | <br>Tanaké                       |  |  |  |

|      | 0      | No change                        |  |  |  |

2. Tie to the analog ground unless external zero adjustment required

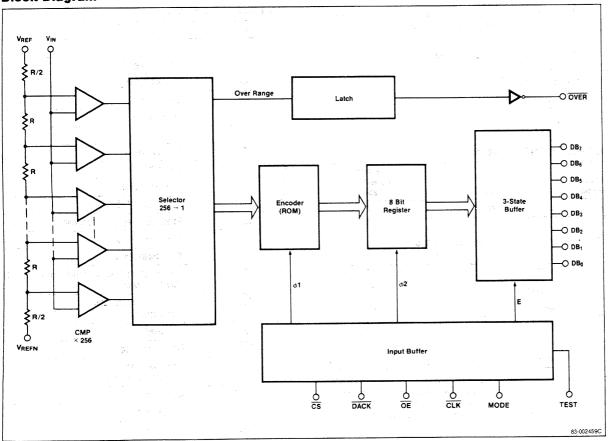

# **Block Diagram**

# **DC** Characteristics

$T_A = +25 \,^{\circ}C$ ,  $V+ = V_{REF} = 5.0 \pm 0.25 \,^{\circ}V$

|                                |        | Lim  | Limits |      |         | Test                                                                                      |  |

|--------------------------------|--------|------|--------|------|---------|-------------------------------------------------------------------------------------------|--|

| Parameter                      | Symbol | Min. | Тур.   |      | Unit    | Conditions                                                                                |  |

| Power Supply Current           | Icc    | 2.1  | 6.0    | 18.0 | mA      | $t_{	extsf{CY}} = 4.0~\mu 	extsf{s}, t_{	extsf{WLC}} = 2.0~\mu 	extsf{s}$ Note 1          |  |

| High Level Output Voltage      | VOH    | 2.8  | :      |      | ٧       | $I_0=-2.0$ mA                                                                             |  |

| Low Level Output Voltage       | VOL    |      |        | 0.4  | ٧       | $I_0 = -1.0 \text{ mA}$                                                                   |  |

| Digital Input Leakage Current  | lilk   |      | -1     | 10   | $\mu$ A | $0 \text{ V} \leq \text{V}_{\text{IN}} \leq \text{V} +$                                   |  |

| Digital Output Leakage Current | IOLK   |      | . 1    | 10   | μA      | $0 \text{ V} \leq \text{V}_0 \leq \text{V} +$                                             |  |

| Reference Input Current        | IREF   | 1.19 | 1.79   | 3.57 | mA      | CLK = H or L Note 1                                                                       |  |

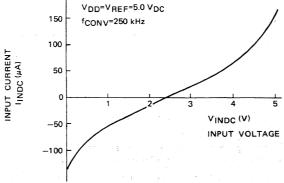

| Analog Input Resistance        | RIN    | 1    | 35     |      | kΩ      | $V_{\sf EN}=$ 2.5 V, t <sub>CY</sub> $=$ 4 $\mu$ s, t <sub>WLC</sub> $=$ 2 $\mu$ s Note 2 |  |

| Reference Input Capacitance    | CREF   |      | 100    |      | pF      | $f_{clk} = 1$ MHz; unmeasured pins returned to Ground                                     |  |

| Analog Input Capacitance       | CIN    |      | 100    |      | pF      | $f_{ m clk}=1$ MHz; unmeasured pins returned to Ground                                    |  |

| Power Dissipation              | PD     |      |        | 50   | mW      | $t_{	extsf{CY}} = 4.0~\mu 	extsf{s}, t_{	extsf{WLC}} = 2.0~\mu 	extsf{s}$                 |  |

Notes: 1. This means DC current. Tie the bypass capacitors (electrolytic capacitor  $\geq$  10  $\mu$ F, ceramic capacitor  $\approx$  0.01  $\mu$ F) to V+ and V<sub>REF</sub> pins, in order to absorb rush current ( $\approx$  10 mA).

2. DC input equivalent circuit is shown below.

Tie the bypass capacitor (> 0.01  $\mu F$ ) to the analog input pin. 3 mA peak current flows into this pin.

# **AC Characteristics**

$T_A = 25 \pm 2$  °C; V + = 5.0 V

| . 1                       |             | Limits               |     |      | Test          |  |

|---------------------------|-------------|----------------------|-----|------|---------------|--|

| Parameter                 | Symbol Min. | Symbol Min. Typ. Max |     | Unit | Conditions    |  |

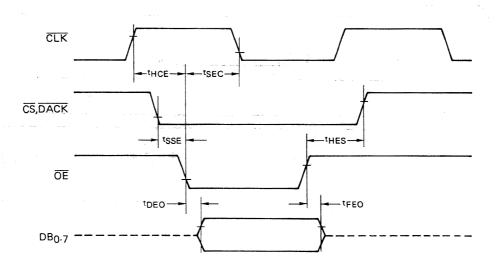

|                           | tDEO        | 100                  | 350 | ns   | ŌĒ↓ → DO      |  |

| Output                    | toco        | 150                  | 450 | ns   | CONV   - DO   |  |

| Delay Time                | toso        | 100                  | 350 | ns   | CS ↓ → DO     |  |

|                           | †DCOVR      | 100                  | 350 | ns   | CONV 1 - OVER |  |

| Delay Time<br>to Floating | tFEO        | 70                   | 200 | ns   | ŌĒ 1 — DO     |  |

|                           | tFSO        | 150                  | 450 | пѕ   | CS 1 → DO     |  |

# **Conversion Characteristics**

$T_A = 25 \pm 2$  °C; V+ =  $V_{REF} = 5.0$  V;  $t_{CY} = 4.0 \ \mu s$ ;  $t_{WLC} = 2.0 \ \mu s$

| 100                                                 |        |       | Limit | ts    |        | Test<br>Conditions |

|-----------------------------------------------------|--------|-------|-------|-------|--------|--------------------|

| Parameter                                           | Symbol | Min.  | Typ.  | Max.  | Unit   |                    |

| Resolution                                          | RES    | 8     | 8     | 8     | Bits   | -20°C to<br>+80°C  |

| Nonlinearity                                        | NL     |       |       | ±1.25 | LSB    | kii (              |

| Full Scale<br>Error                                 | -      |       |       | ±1.00 | LSB    |                    |

| Full Scale<br>Error Tem-<br>perature<br>Coefficient |        |       | 20    |       | ppm/°C |                    |

| Zero Scale<br>Error                                 |        | -0.75 | j     | +0.75 | LSB    |                    |

| Zero Scale<br>Error Tem-<br>perature<br>Coefficient |        |       | -20   |       | ppm/°C |                    |

**Note:**  $\mu$ PD7003C:  $T_A = 0^{\circ}$ C to +70°C.

### **Recommended Operating Conditions**

$T_A = 0$ °C to 70°C:  $\mu$ PD7003C,

$T_A = -20$ °C to +80°C:  $\mu$ PD7003D

| -                                         |                                 |      | Limi       | ts      |         | Test                                                            |

|-------------------------------------------|---------------------------------|------|------------|---------|---------|-----------------------------------------------------------------|

| Parameter                                 | Symbol                          | Min. | Тур.       | Max.    | Unit    | Conditions                                                      |

| Supply<br>Voltage                         | ۷+                              | 4.75 | 5.0        | 5.25    | V       |                                                                 |

| Reference<br>Input Voltage                | VREF                            | 4.0  | <b>V</b> + | V+      | V       |                                                                 |

| Analog<br>Input<br>Voltage                | ViN                             | -0.1 |            | V+ +0.1 | ۷.      |                                                                 |

| High Level<br>Logic Input                 | VIH                             | 2.4  |            | V+      | V .     |                                                                 |

| Low Level<br>Logic Input                  | VIL                             | -0.1 |            | 0.8     | ۷       |                                                                 |

| Sampling<br>Rate                          |                                 | 10   |            | 250k    | times/s |                                                                 |

| Conversion<br>Cycle Time                  | tCY                             | 4.0  |            | 100     | μ       |                                                                 |

| CONV High<br>Level Width                  | twhc                            | 2.0  |            |         | μ\$     |                                                                 |

| CONV Low<br>Level Width                   | twlc                            | 2.0  |            |         | μ\$     |                                                                 |

| CONV Setup<br>Time                        | tsce                            | 0    |            | Note 1  | ns      | CONV ↓ → OE (                                                   |

| CS Setup<br>Time                          | tsse                            | 100  |            | ,       | ns      | $\overline{CS} \downarrow \rightarrow \overline{OE} \downarrow$ |

| CS Hold<br>Time                           | thes                            | 0    |            |         | ns      | OE ↑ → CS ↑                                                     |

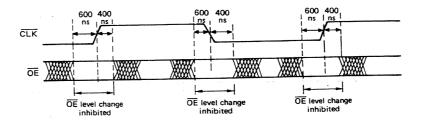

| OE Setup<br>Time                          | tsec                            | 600  |            |         | ns      | OE 1 - CONV                                                     |

| OE Hold<br>Time                           | tHCE                            | 400  |            |         | ns      | CONV ↑ → OE                                                     |

| OE Low<br>Level Width                     | twle                            | 400  |            | Note 2  | ns      |                                                                 |

| Digital<br>Input Rise<br>and Fall<br>Time | t <sub>r</sub> . t <sub>f</sub> |      |            | 50      | ns      |                                                                 |

Notes: 1.  $t_{SCE}$  (ns)  $\leq t_{CY}$  (ns)  $-t_{WLE}$  (ns) - 100 (ns).

2.  $t_{WLE}$  (ns)  $\leq t_{CY}$  (ns)  $-t_{SCE}$  (ns) -100 (ns).

#### **Converter Operation**

Referring to the block diagram, the reference voltage is set externally to some desired level which references the individual internal components such that  $V_{REF}$  is divided equally by 256 resistors in a ladder/divider configuration. The applied voltage to  $V_{IN}$  is then compared to the reference level and the individual samples are sent to the selector section where the individual signals are multiplexed to form an address data word. The data word is then further encoded to form the final 8-bit data byte by the encoder ROM, and stored in the 8-bit register until the Output Enable Command. Then the data is sent to the data bus via a three-state buffer.

#### **Mode Select**

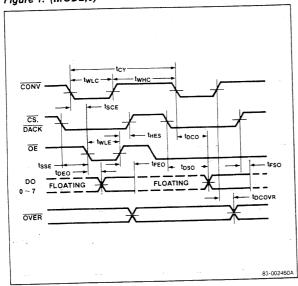

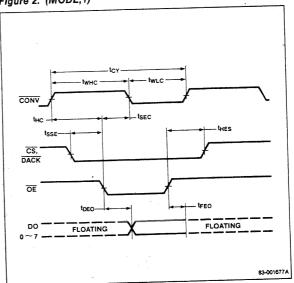

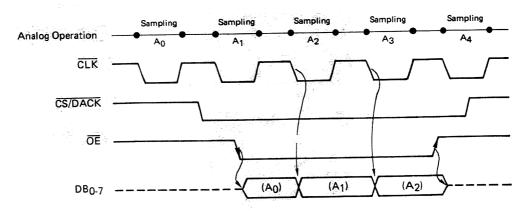

There are two modes of operation for the  $\mu$ PD7003. Figure 1 shows the timing diagram for mode "0" where the converter is operating in continuous output mode. The analog input is sampled when the clock is in the "low" state. When the clock is in the "high" state the conversion from analog-to-digital takes place and the resultant data is output on the next falling edge of the clock pulse and the cycle is repeated.

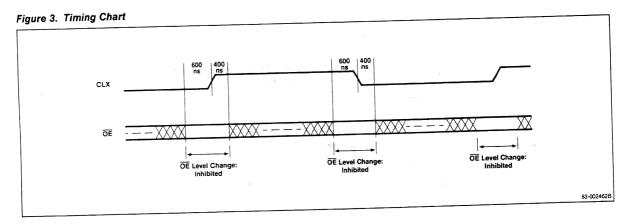

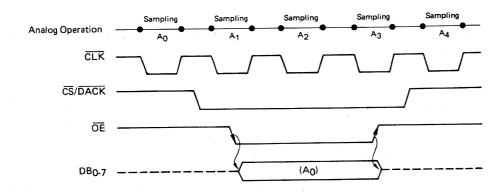

The second mode (Mode 1) is shown in figure 2. In this mode of operation, one conversion takes place while the clock is in the "low" state and the resultant data is held as long as output enable and Chip Select (CS) or DMA Acknowledge (DACK) are "low." Data refresh is inhibited until CS and DACK are recycled.

#### MODE = "HIGH"

Data is refreshed on the falling edge of  $\overline{\text{CLK}}$ , loaded during the "low" clock state, and converted and output during the "high" clock state.

## MODE = "LOW"

Data is loaded and converted when Output Enable is "low" and refreshed only when  $\overline{OE}$  makes the transition from high to low again.

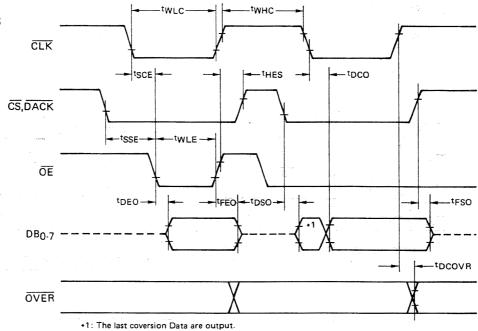

Note that in either case data will only be accepted and output when  $\overline{OE}$  and  $\overline{CS}$  or  $\overline{DACK}$  are active ("low"). Output enable should not be changed during the intervals shown in figure 3. The timing for output enable change versus clock transition is 600 ns before and 500 ns after the rising or falling edge of  $\overline{CLK}$  any attempt to change  $\overline{OE}$  during these periods will be inhibited.

# **Timing Waveforms**

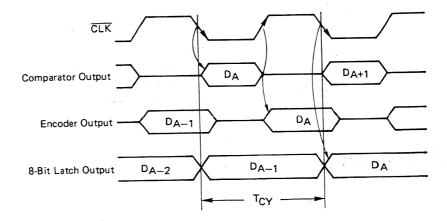

Figure 1. (MODE;0)

Figure 2. (MODE;1)

# $\mu$ PD7003

## TIMING DIAGRAMS

# 1. CONTINUOUS OUTPUT MODE

#### 2. LATCH OUTPUT MODE

OPERATION OF INTERNAL CIRCUIT BLOCK

## 1. COMPARATOR

Reference voltage ( $V_{REF}$ ) is divided by 256 resistors, and 256 comparators simultaneously compare analog input voltage ( $V_{IN}$ ) with the divided voltages.

#### 2. SELECTOR, ENCODER

Selector accepts the outputs of comparators, and detects the position of comparator which corresponds to analog input voltage.

The encoder generates an 8 bit code by translating the output data from selector.

When the analog input voltage ( $V_{IN}$ ) is higher than the reference voltage ( $V_{REF}$ ), the selector generates an over range signal ( $\overline{OVER}$ ).

#### 3.8-BIT LATCH

This register temporally stores 8-Bit data from encoder.

## 4. LOGIC CONTROL

This circuit block generates internal control signals according to external control signals.

#### **OPERATION MODES**

According to the different conversion output, two modes of operation are available.

1. CONTINUOUS OUTPUT MODE (MODE = H)

The actual conversion time of  $\mu PD7003$  is shortened by using pipeline processing mode.

## INTERNAL TIMING

The pipeline processing consists of 3 steps:

- Comparing by comparators,

Generating 8-Bit data in selector and encoder,

- Holding conversion data in 8-Bit latch.

Analog input signals are sampled at the low level interval of CLK. The conversion data are output at the subsequent falling edge of CLK.

## CONTINUOUS **OUTPUT** MODE TIMING

#### 2. LATCH OUTPUT MODE (MODE = L)

In this mode,  $\mu$ PD7003 operates the same A/D conversion operation as continuous output mode, but with an additional 8-Bit latch operation. In latch output mode, updating of 8-Bit latch data is inhibited at the low level interval of  $\overline{OE}$ , and holding the last latched data.

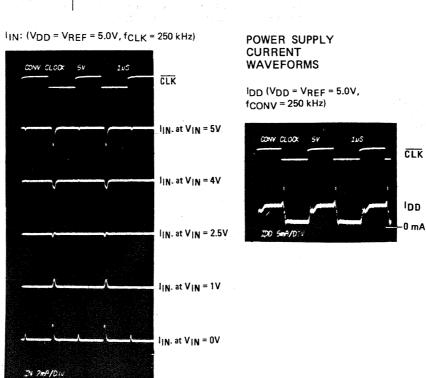

## INPUT CHARACTERISTICS

# INPUT CURRENT WAVEFORMS

# APPLICATION HINTS

Note 1: Data of A<sub>1</sub> and A<sub>2</sub> are not held.

Note 2: Please do not change the level of  $\overline{OE}$  signal during the intervals shown below.

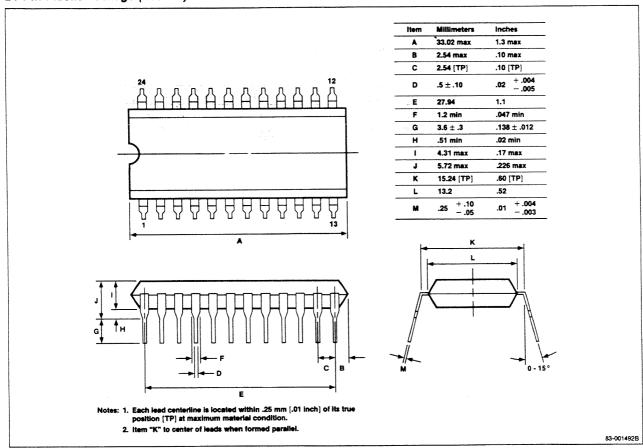

# **Packaging Information**

## 24-Pin Plastic Package (600 mil)