## VN330SP-32-E

# QUAD HIGH SIDE SMART POWER SOLID STATE RELAY

### **General Features**

| Туре            | V <sub>demag</sub> (*) | R <sub>DSon</sub> (*) | I <sub>out</sub> (*) | V <sub>CC</sub> |

|-----------------|------------------------|-----------------------|----------------------|-----------------|

| VN330SP-32-E    | V <sub>CC</sub> -55V   | 0.32Ω(**)             | 1A                   | 36V             |

| (*)Per channel. |                        |                       |                      |                 |

(\*)Per channel. (\*\*)at TJ = 85 ℃

#### **Features**

- **OUTPUT CURRENT: 1A PER CHANNEL**

- DIGITAL INPUT CLAMPED AT 32V MINIMUM **VOLTAGE**

- SHORTED LOAD AND OVER-TEMPERATURE PROTECTIONS

- BUILT-IN CURRENT LIMITER

- UNDERVOLTAGE SHUT-DOWN

- **OPEN DRAIN DIAGNOSTIC OUTPUT**

- FAST DEMAGNETIZATION OF INDUCTIVE LOADS

## **Description**

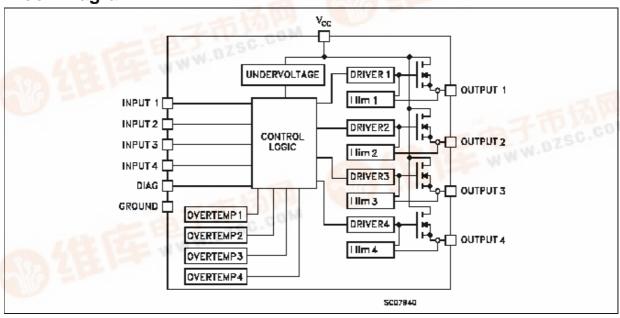

The VN330SP-32-E is a monolithic device made using STMicroelectronics VIPower Technology, intended for driving four indipendent resistive or inductive loads with one side connected to ground. Active current limitation avoids dropping the system power supply in case of shorted load. Built-in thermal shut-down protects the chip from overtemperature and short circuit. The open drain diagnostic output indicates over-temperature conditions.

## **Block Diagram**

September 2005

Rev 3 1/14

Table 1. Absolute Maximum Rating

| Symbol            | Parameter                                                                      | Value              | Unit |  |

|-------------------|--------------------------------------------------------------------------------|--------------------|------|--|

| V <sub>CC</sub>   | Power supply voltage                                                           | 45                 | V    |  |

| -V <sub>CC</sub>  | Reverse supply voltage -0.3                                                    |                    |      |  |

| I <sub>OUT</sub>  | Output current (continuos) Internally limite                                   |                    | Α    |  |

| I <sub>R</sub>    | Reverse output current (per channel) -6                                        |                    | Α    |  |

| I <sub>IN</sub>   | Input current (per channel)                                                    | ± 10               | mA   |  |

| I <sub>DIAG</sub> | Diag pin current                                                               | ± 10               | mA   |  |

| V <sub>ESD</sub>  | Electrostatic discharge (R = 1.5KW; C = 100pF)                                 | 2000               | V    |  |

| E <sub>AS</sub>   | Single pulse avalanche energy per channel not simultaneously <i>Figure 3</i> . | 400                | mJ   |  |

| P <sub>tot</sub>  | Power dissipation at T <sub>C</sub> <= 25°C                                    | Internally limited | W    |  |

| TJ                | Junction operating temperature                                                 | Internally limited | °C   |  |

| T <sub>stg</sub>  | Storage Temperature                                                            | -55 to 150         | °C   |  |

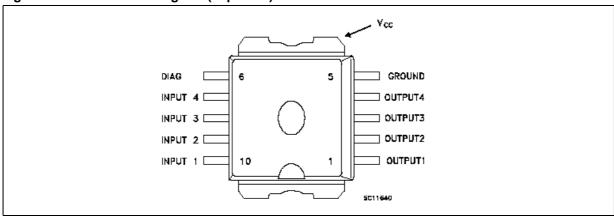

Figure 1. Connection Diagram (Top View)

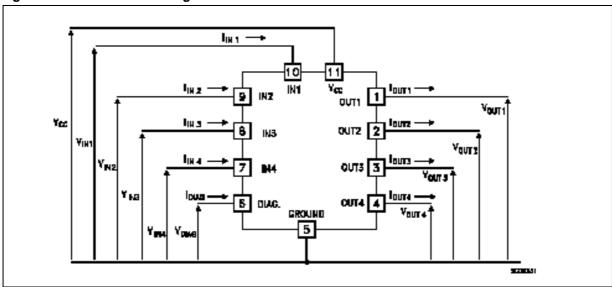

Figure 2. Current and Voltage Conventions

#### VN330SP-32-E

Table 2. Thermal data

| Symbol            | ol Parameter                                 |     | Max Value | Unit |

|-------------------|----------------------------------------------|-----|-----------|------|

| R <sub>thJC</sub> | Thermal resistance junction-case (Note:1)    | Max | 2         | °C/W |

| R <sub>thJA</sub> | Thermal resistance junction-ambient (Note:2) | Max | 50        | °C/W |

Note: 1.Per channel

Note: 2.When mounted using minimum recommended pad size on FR-4 board

**Electrical Chracteristics** (10V <  $V_{CC}$  < 36V; -25°C <  $T_{J}$  < 125°C; unless otherwise specified)

Table 3. Power Section

| Symbol             | Parameter                  | Test Conditions                                      | Min.                | Тур.                | Max.                | Unit |

|--------------------|----------------------------|------------------------------------------------------|---------------------|---------------------|---------------------|------|

| V <sub>CC</sub>    | Supply voltage             |                                                      | 10                  |                     | 36                  | V    |

|                    |                            | I <sub>OUT</sub> = 0.5A; T <sub>J</sub> = 125°C      |                     |                     | 0.4                 | Ω    |

| R <sub>ON</sub>    | On state resistance        | I <sub>OUT</sub> = 0.5A; T <sub>J</sub> = 85°C       |                     |                     | 0.32                | Ω    |

|                    |                            | $I_{OUT} = 0.5A; T_J = 25^{\circ}C$                  |                     |                     | 0.2                 | Ω    |

| l-                 | Cupply ourrant             | All channels OFF; V <sub>IN</sub> = 30V;             |                     |                     | 1                   | mA   |

| I <sub>S</sub>     | Supply current             | On state; $T_J = 125^{\circ}C I_{OUT1}I_{OUT4} = 0V$ |                     |                     | 10                  | mA   |

| V <sub>demag</sub> | Output voltage at turn-off | $I_{OUT} = 0.5A; L_{LOAD} >= 1mH$                    | V <sub>CC</sub> -65 | V <sub>CC</sub> -55 | V <sub>CC</sub> -45 | V    |

Table 4. Logical Input

| Symbol               | Parameter                              | Test Conditions                                               | Min. | Тур. | Max. | Unit |

|----------------------|----------------------------------------|---------------------------------------------------------------|------|------|------|------|

| V <sub>IL</sub>      | Input low level voltage                |                                                               |      |      | 2    | V    |

| V <sub>IH</sub>      | Input high level voltage .             | Note:3                                                        | 3.5  |      |      | V    |

| V <sub>I(HYST)</sub> | Input hysteresis voltage               |                                                               |      | 0.5  |      | V    |

| l                    | Input current                          | V <sub>IN</sub> = 0 to 30V                                    |      |      | 600  | μΑ   |

| I <sub>IN</sub>      | input current                          | $V_{IN} = 0$ to 2V                                            | 25   |      |      | μΑ   |

| I <sub>LGND</sub>    | Output current in ground disconnection | $V_{CC} = V_{INn} = GND = DIAG = 24V;$<br>$T_J = 25^{\circ}C$ |      |      | 25   | mA   |

| V                    | Input clamp voltage                    | I <sub>IN</sub> = 1mA                                         | 32   | 36   |      | V    |

| $V_{ICL}$            | Note:3                                 | I <sub>IN</sub> = -1 mA                                       |      | -0.7 |      | V    |

Note: 3. The input voltage is internally clamped at 32V minimum, it is possible to connect the input pins to an higher voltage via an external resistor calculate to not exceed 10mA

577

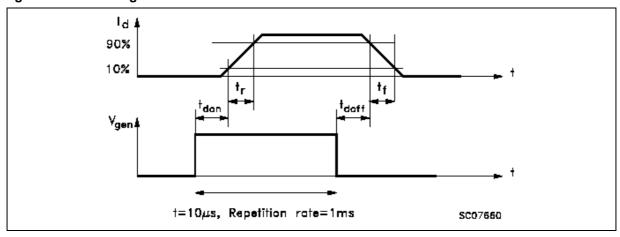

Table 5. Switching ( $V_{CC} = 24V$ )

| Symbol                 | Parameter              | Test Conditions                                    | Min. | Тур. | Max. | Unit |

|------------------------|------------------------|----------------------------------------------------|------|------|------|------|

|                        |                        | I <sub>OUT</sub> = 0.5A, Resistive Load Input rise |      |      |      |      |

| 1                      | Turn-on delay time of  | time < 0.1µs,                                      |      |      |      |      |

| t <sub>d(ON)</sub>     | Output current         | $T_J = 25$ °C                                      |      | 30   | 40   | μs   |

|                        |                        | $T_J = 125$ °C                                     |      |      | 60   | μs   |

|                        |                        | I <sub>OUT</sub> = 0.5A, Resistive Load Input rise |      |      |      |      |

| +                      | Rise time of Output    | time $< 0.1 \mu s$ ,                               |      |      |      |      |

| t <sub>r</sub>         | current                | $T_J = 25$ °C                                      |      | 50   | 100  | μs   |

|                        |                        | $T_J = 125$ °C                                     |      |      | 115  | μs   |

|                        |                        | I <sub>OUT</sub> = 0.5A, Resistive Load Input rise |      |      |      |      |

| 4                      | Turn-off delay time of | time $< 0.1 \mu s$ ,                               |      |      |      |      |

| t <sub>d(OFF)</sub>    | Output current         | $T_J = 25$ °C                                      |      | 20   | 30   | μs   |

|                        |                        | $T_J = 125$ °C                                     |      |      | 40   | μs   |

|                        |                        | I <sub>OUT</sub> = 0.5A, Resistive Load Input rise |      |      |      |      |

|                        | Fall time of Output    | time < 0.1µs,                                      |      |      |      |      |

| t <sub>f</sub>         | current                | $T_J = 25$ °C                                      |      | 8    | 15   | μs   |

|                        |                        | $T_J = 125$ °C                                     |      |      | 20   | μs   |

| (di/dt) <sub>on</sub>  | Turn on current clans  | I <sub>OUT</sub> = 0.5A,                           |      |      | 0.5  | A/μs |

| (di/di/on              | Turn-on current slope  | $I_{OUT} = I_{LIM}, T_J = 25$ °C                   |      |      | 2    | A/μs |

| (di/dt) <sub>off</sub> | Turn-off current slope | I <sub>OUT</sub> = 0.5A,                           |      |      | 2    | A/μs |

| (di/dt/off             | rum-on current slope   | $I_{OUT} = I_{LIM}, T_J = 25$ °C                   |      |      | 4    | A/μs |

Table 6. Protections

| Symbol                | Parameter                         | Test Conditions                                                                          | Min. | Тур. | Max. | Unit |

|-----------------------|-----------------------------------|------------------------------------------------------------------------------------------|------|------|------|------|

| V <sub>DIAG</sub> (*) | Status voltage output low         | I <sub>DIAG</sub> = 5mA ( Fault condition )                                              |      |      | 1    | V    |

| \/(*)                 | Ctatus alama valtaga              | I <sub>DIAG</sub> = 1mA                                                                  | 32   | 36   |      | V    |

| V <sub>SCL</sub> (*)  | Status clamp voltage              | I <sub>DIAG</sub> = -1mA                                                                 |      | -0.7 |      | V    |

| V <sub>USD</sub>      | Undervoltage shut down            |                                                                                          | 5    |      | 8    | V    |

| I <sub>LIM</sub>      | DC Short circuit current          | $V_{CC} = 24V; R_{LOAD} < 10m\Omega$                                                     | 1    |      | 2.5  | Α    |

| I <sub>OVPK</sub>     | Peak short circuit current        | $V_{CC} = 24V; V_{IN} = 30V; R_{LOAD} < 10m\Omega$                                       |      |      | 4    | Α    |

| I <sub>DIAGH</sub>    | Leakage on diag pin in high state | V <sub>DIAG</sub> = 24V                                                                  |      |      | 100  | μΑ   |

| I <sub>LOAD</sub>     | Output leakage current            | V <sub>CC</sub> = 10 to 36V; V <sub>IN</sub> = V <sub>IL</sub><br>4 Channels in Parallel |      |      | 25   | μΑ   |

| t <sub>SC</sub>       | Delay time of current limiter     |                                                                                          |      |      | 100  | μs   |

| T <sub>TSD</sub>      | Thermal shut down temperature     |                                                                                          | 150  | 170  |      | °C   |

| $T_{R}$               | Thermal reset temperature         |                                                                                          | 135  | 155  |      | °C   |

<sup>(\*)</sup>Status determination > 100ms after the switching edge.

Note: If INPUT pin is floating the corrisponding channel will automatically switch OFF. If GND pin is disconnected, the channel will switch OFF provided  $V_{\rm CC}$  not exceed 36V.

577

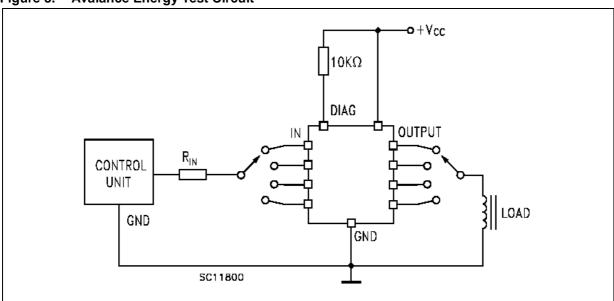

Figure 3. Avalance Energy Test Circuit

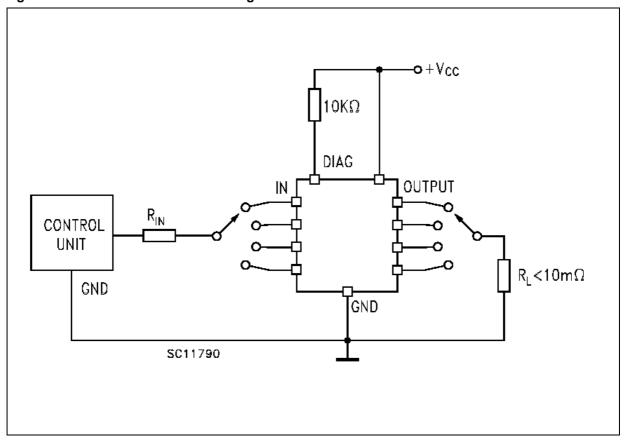

Figure 4. Peak Short Circuit Test Diagram

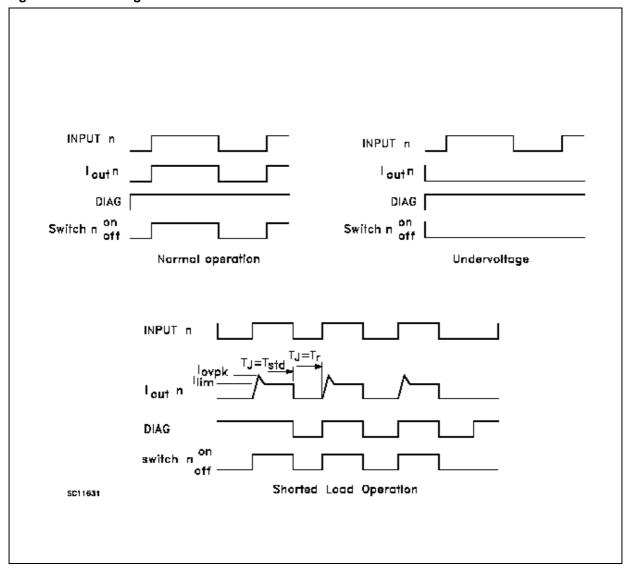

Table 7. Truth Table

| Conditions              | INPUTn | OUTPUTn | Diagnostic |

|-------------------------|--------|---------|------------|

| Name al an austicu      | L      | L       | Н          |

| Normal operation        | Н      | Н       | Н          |

| Ou combo mo m o modulmo | L      | L       | Н          |

| Overtemperature         | Н      | L       | L          |

| Lindomioltogo           | L      | L       | Н          |

| Undervoltage            | Н      | L       | Н          |

| Shorted load            | L      | L       | Н          |

| ( Current limitation )  | Н      | Н       | Н          |

Figure 5. Switching Waveforms

Figure 6. Switching Parameter Test Conditions

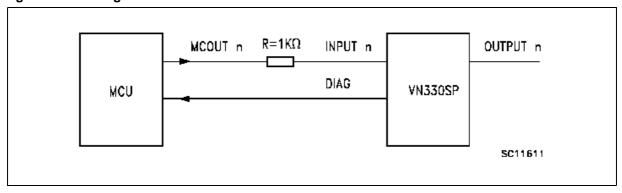

Figure 7. Driving Circuit

## PowerSO-10<sup>TM</sup> Thermal Data

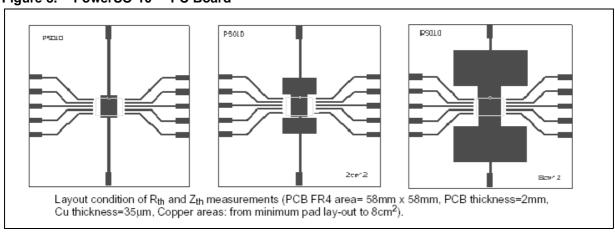

Figure 8. PowerSO-10<sup>TM</sup> PC Board

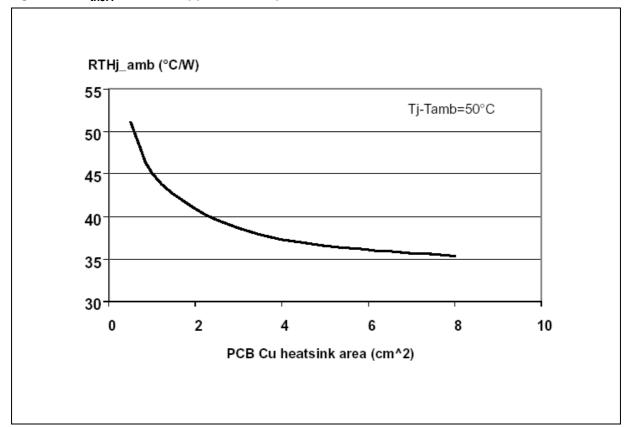

Figure 9.  $R_{thJA}$  Vs. PBC copper area in open box free air condition

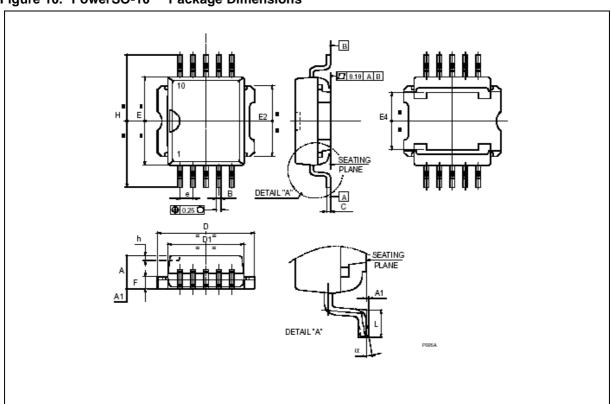

#### **Mechanical Data**

In order to meet environmental requirements, ST offers these devices in ECOPACK<sup>®</sup> packages. These packages have a Lead-free second level interconnect . The category of second level interconnect is marked on the package and on the inner box label, in compliance with JEDEC Standard JESD97. The maximum ratings related to soldering conditions are also marked on the inner box label. ECOPACK is an ST trademark. ECOPACK specifications are available at: <a href="https://www.st.com">www.st.com</a>

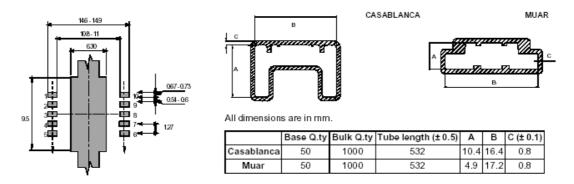

Table 8. PowerSO-10<sup>TM</sup> Mechanical Data

| Symbol |       | millimeters |       |

|--------|-------|-------------|-------|

| Зушьы  | Min   | Тур         | Max   |

| A      | 3.35  |             | 3.65  |

| A (*)  | 3.4   |             | 3.6   |

| A1     | 0.00  |             | 0.10  |

| В      | 0.40  |             | 0.60  |

| B (*)  | 0.37  |             | 0.53  |

| С      | 0.35  |             | 0.55  |

| C (*)  | 0.23  |             | 0.32  |

| D      | 9.40  |             | 9.60  |

| D1     | 7.40  |             | 7.60  |

| E      | 9.30  |             | 9.50  |

| E2     | 7.20  |             | 7.60  |

| E2 (*) | 7.30  |             | 7.50  |

| E4     | 5.90  |             | 6.10  |

| E4 (*) | 5,90  |             | 6.30  |

| e      |       | 1.27        |       |

| F      | 1.25  |             | 1.35  |

| F (*)  | 1.20  |             | 1.40  |

| Ĥ.     | 13.80 |             | 14.40 |

| H (*)  | 13.85 |             | 14.35 |

| h      |       | 0.50        |       |

| L      | 1.20  |             | 1.80  |

| L (*)  | 0.80  |             | 1.10  |

| а      | 0°    |             | 8°    |

| α (*)  | 2°    |             | 8°    |

Note: (\*) Muar only POA P013P

Figure 10. PowerSO-10<sup>TM</sup> Package Dimensions

Figure 11. PowerSO-10<sup>TM</sup> Suggested Pad and Tube Shipment (No Suffix)

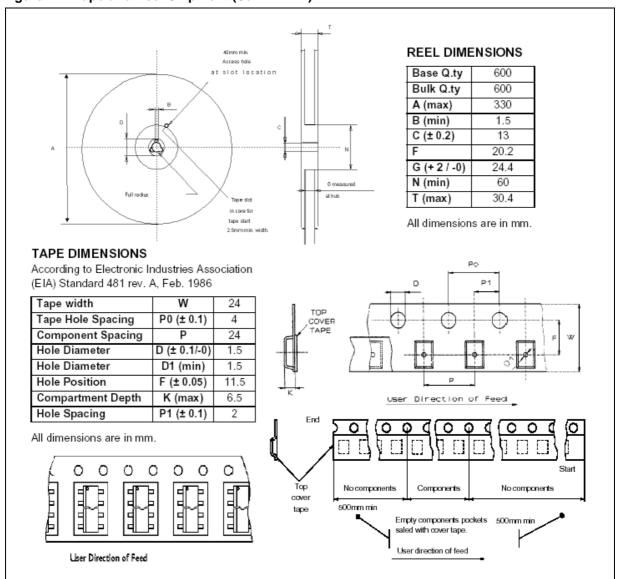

Figure 12. Tape and Reel Shipment (Suffix "TR")

## Table 9. Order Codes

| Package                  | Tube         | Tape and Reel  |  |

|--------------------------|--------------|----------------|--|

| PowerSO-10 <sup>TM</sup> | VN330SP-32-E | VN330SPTR-32-E |  |

## VN330SP-32-E

## Table 10. Revision History

| Date       | Revision | Changes       |

|------------|----------|---------------|

| 5-Sep-2005 | 3        | Final release |

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners

© 2005 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com