查询VSP2100Y供应商

<mark>捷多邦,专业PCB打样工厂,24小时加急出货</mark>

International Airport Industrial Park • Mailing Address: PO Box 11400, Tucson, AZ 85734 • Street Address: 6730 S. Tucson Blvd., Tucson, AZ 85706 • Tel: (520) 746-1111 • Twx: 910-952-1111 Internet: http://www.burr-brown.com/ • FAXLine: (800) 548-6133 (US/Canada Only) • Cable: BBRCORP • Telex: 066-6491 • FAX: (520) 889-1510 • Immediate Product Info: (800) 548-6132

Dummy

Pixel Auto- Zero

DUMC

+28d

A/D

Convert

A/D

Reference

Latch

Double

Sampling

Clamp

CCD Out

CCD R

# **SPECIFICATIONS**

At  $T_A = +25^{\circ}C$ , all power supply voltages = +3.0V, and conversion rate = 18MHz, unless otherwise specified.

| PARAMETER                                            | CONDITIONS                 | MIN    | ТҮР        | MAX  | UNITS         |

|------------------------------------------------------|----------------------------|--------|------------|------|---------------|

| RESOLUTION                                           |                            |        | 10         |      | Bits          |

| DIGITAL INPUT                                        |                            |        |            |      |               |

| Logic Family                                         |                            |        | CMOS       |      |               |

| Logic Levels                                         | Logic HI                   | 2.5    |            |      | V             |

|                                                      | Logic LO                   | 0      |            | +0.4 | V             |

| Logic Currents                                       | Logic HI, $V_{IN} = +3V$   |        |            | 10   | μA            |

| A/D Clock Duty Cycle                                 | Logic LO, $V_{IN} = 0V$    |        | 50         | 10   | μA<br>%       |

| DIGITAL OUTPUT                                       |                            |        |            |      | ,0            |

| Logic Family                                         |                            |        | CMOS       |      |               |

| Logic Levels                                         | Logic HI, $C_{L} = 10 pF$  | 2.5    |            | 3    | V             |

|                                                      | Logic LO, $C_L = 10 pF$    | 0      |            | +0.4 | V             |

| ANALOG OUTPUT                                        |                            |        |            |      |               |

| General Purpose D/A Converter Output                 |                            | 0.3    |            | 2.4  | V             |

| DAC Settling TIme                                    |                            |        | 1.0        |      | μs            |

| TRANSFER CHARACTERISTICS                             |                            |        |            |      |               |

| Differential Non-Linearity                           |                            |        | ±0.4       |      | LSB           |

| Integral Non-Linearity                               |                            |        | ±2.0       |      | LSB           |

| No Missing Codes                                     |                            |        | Guaranteed |      |               |

| Signal Settling Time                                 | Black to Full-Scale Change |        |            | 110  | ns            |

|                                                      | to 1/4 LSB into A/D        | 500111 |            | 07   |               |

| Conversion Rate                                      |                            | 500kHz |            | 27   | MHz<br>Clocks |

| Data Latency<br>Signal-to-Noise Ratio <sup>(1)</sup> | Grounded Input Cap,        |        | 5.5<br>53  |      | dB            |

| Signal-to-Noise Ratio                                | VCA Gain max               |        | 55         |      | uВ            |

| Black Clamp Level                                    | Von Gain max               |        | 32         |      | LSB           |

| CDS                                                  |                            |        |            |      |               |

| Data Settling Time to $\pm 0.1\%$ for FS Change      | From Leading Edge          |        | 11         |      | ns            |

| with $R_s = 40$                                      | of DATCK                   |        |            |      |               |

| Input Capacitance                                    | DATCK LOW                  |        | 20         |      | pF            |

| Input Time Constant                                  |                            |        | 300        |      | ps            |

| Data Full-Scale Input                                | After AC-Coupling Cap      | 600    |            |      | mV            |

| INPUT CLAMP                                          |                            |        |            |      |               |

| Clamp-On Resistance                                  |                            |        | 3.3        |      | kΩ            |

| Clamp Level                                          |                            |        | 1          |      | V             |

| VCA CHARACTERISTICS                                  |                            |        |            |      |               |

| Gain Control Voltage Range                           |                            | 0.3    |            | 2.4  | V             |

| Gain at Control Voltage, max                         |                            | 32     | 34         |      | dB            |

| Gain at Control Voltage, min                         |                            |        | -2         |      | dB            |

| Gain Control Linearity                               |                            |        | ±1.0<br>10 |      | dB            |

| Gain Control Settling Time<br>Transfer Function      |                            |        | 17         |      | μs<br>dB/V    |

| POWER SUPPLY                                         |                            |        |            |      | (L), V        |

| Rated Voltage                                        |                            | +2.7   | +3.0       | +3.6 | v             |

| Quiescent Current                                    |                            | 72.1   | 63         | +3.0 | mA            |

| Power Dissipation                                    |                            |        | 190        |      | mW            |

| Power-Down Mode                                      |                            |        | 18         |      | mW            |

| TEMPERATURE RANGE                                    |                            |        |            |      |               |

| Specified Range                                      | Ambient                    | -25    |            | +85  | °C            |

| Thermal Resistance, $\theta_{IA}$                    |                            | -      |            |      | -             |

| 48-Lead LQFP                                         |                            |        | 100        |      | °C/W          |

NOTE: (1) SNR = 20log (full-scale voltage/rms noise).

The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes no responsibility for the use of this information, and all use of such information shall be entirely at the user's own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not authorize or warrant any BURR-BROWN product for use in life support devices and/or systems.

### **ABSOLUTE MAXIMUM RATINGS**

| Power Supply (+V <sub>S</sub> )<br>Analog Input<br>Logic Input<br>Case Temperature<br>Junction Temperature<br>Storage Temperature |                                 |

|-----------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| Analog Input                                                                                                                      | 0.3V to (+V <sub>S</sub> +0.3V) |

| Logic Input                                                                                                                       | 0.3V to (+V <sub>S</sub> +0.3V) |

| Case Temperature                                                                                                                  |                                 |

| Junction Temperature                                                                                                              | +150°C                          |

| Storage Temperature                                                                                                               | –40°C to +150°C                 |

# ELECTROSTATIC DISCHARGE SENSITIVITY

This integrated circuit can be damaged by ESD. Burr-Brown recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

## PACKAGE/ORDERING INFORMATION

| PRODUCT  | PACKAGE      | PACKAGE<br>DRAWING<br>NUMBER <sup>(1)</sup> | SPECIFIED<br>TEMPERATURE<br>RANGE | PACKAGE<br>MARKING | ORDERING<br>NUMBER <sup>(2)</sup> | TRANSPORT<br>MEDIA |

|----------|--------------|---------------------------------------------|-----------------------------------|--------------------|-----------------------------------|--------------------|

| VSP2100Y | 48-Lead LQFP | 340                                         | –25°C to +85°C                    | VSP2100Y           | VSP2100Y                          | 50-Piece Tray      |

| "        | "            | "                                           | "                                 | "                  | VSP2100Y/2K                       | Tape and Reel      |

NOTES: (1) For detailed drawing and dimension table, please see end of data sheet, or Appendix C of Burr-Brown IC Data Book. (2) Models with a slash (/) are available only in Tape and Reel in the quantities indicated (e.g., /2K indicates 2000 devices per reel). Ordering 2000 pieces of "VSP2100Y/2K" will get a single 2000-piece Tape and Reel. For detailed Tape and Reel mechanical information, refer to Appendix B of Burr-Brown IC Data Book.

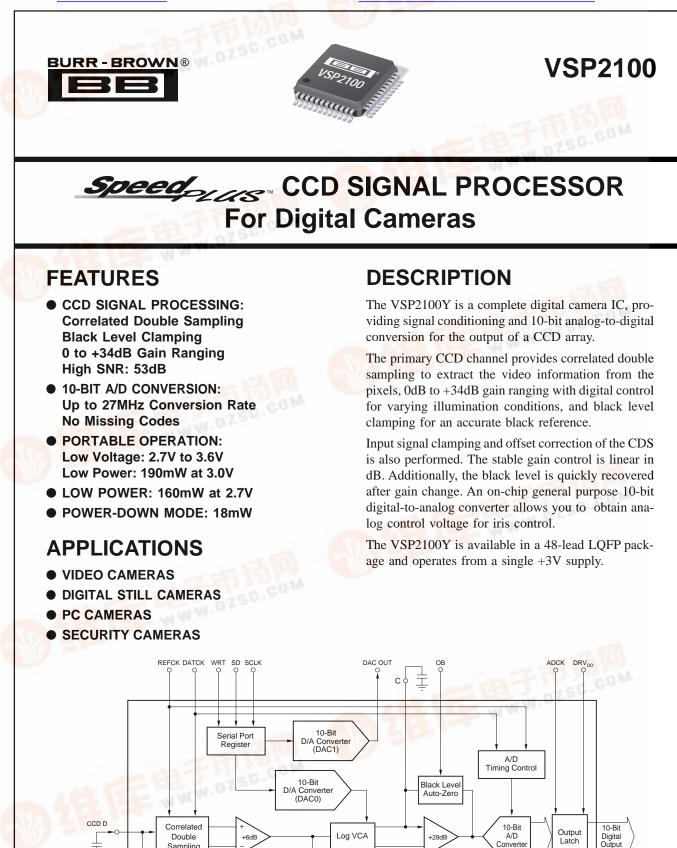

### **PIN CONFIGURATION**

### **PIN DESCRIPTIONS**

| PIN | DESIGNATOR        | DESCRIPTION                                       | PIN | DESIGNATOR        | DESCRIPTION                                            |  |  |

|-----|-------------------|---------------------------------------------------|-----|-------------------|--------------------------------------------------------|--|--|

| 1   | DV <sub>SS1</sub> | Digital Ground                                    | 24  | С                 | Capacitor for Optical Feedback Loop                    |  |  |

| 2   | B10 (LSB)         | Bit 10, ADC Output, Least Significant Bit         | 25  | AV <sub>SS1</sub> | Analog Ground                                          |  |  |

| 3   | B9                | Bit 9, ADC Output                                 | 26  | CCD D             | CCD Signal Input                                       |  |  |

| 4   | B8                | Bit 8, ADC Output                                 | 27  | CCD R             | Capacitor for Dummy Feedback Loop                      |  |  |

| 5   | B7                | Bit 7, ADC Output                                 | 28  | AV <sub>SS2</sub> | Analog Ground                                          |  |  |

| 6   | B6                | Bit 6, ADC Output                                 | 29  | TP1               | Test Pin 1, Open                                       |  |  |

| 7   | B5                | Bit 5, ADC Output                                 | 30  | TP2               | Test Pin 2, Open                                       |  |  |

| 8   | B4                | Bit 4, ADC Output                                 | 31  | AV <sub>SS4</sub> | Analog Ground                                          |  |  |

| 9   | B3                | Bit 3, ADC Output                                 | 32  | LCM               | Attenuator Common-Mode Bypass                          |  |  |

| 10  | B2                | Bit 2, ADC Output                                 | 33  | AV <sub>DD2</sub> | Analog Power Supply                                    |  |  |

| 11  | B1 (MSB)          | Bit 1, ADC Output, Most Significant Bit           | 34  | SD                | Serial Data Input for D/A Converters                   |  |  |

| 12  | DRV <sub>DD</sub> | Digital Power Supply for Digital Outputs (B1-B10) | 35  | SCLK              | Clock for Serial Data Input                            |  |  |

| 13  | DRV <sub>SS</sub> | Digital Ground for Digital Outputs (B1-B10)       | 36  | WRT               | Write Pulse for Serial Data Input, Rising Edge Trigger |  |  |

| 14  | DV <sub>SS2</sub> | Digital Ground                                    | 37  | 2.4V              | Attenuator Ladder Bypass                               |  |  |

| 15  | DV <sub>SS3</sub> | Digital Ground                                    | 38  | CM                | ADC Common-Mode Voltage                                |  |  |

| 16  | ADCK              | Clock for Digital Data Output Latch               | 39  | AV <sub>DD3</sub> | Analog Power Supply                                    |  |  |

| 17  | DV <sub>DD</sub>  | Digital Power Supply                              | 40  | AV <sub>DD4</sub> | Analog Power Supply                                    |  |  |

| 18  | PD                | Power Down: LOW = Normal Operation                | 41  | RESET             | Resets DAC Registers, Active LOW                       |  |  |

|     |                   | HIGH = Reduced Power (digital                     | 42  | DACOUT            | D/A Converter (DAC1) Output                            |  |  |

|     |                   | output= 000000000)                                | 43  | AV <sub>DD5</sub> | Analog Power Supply                                    |  |  |

| 19  | PB                | Preblanking: LOW = ADC Output: -FS +32LSB         | 44  | AV <sub>DD6</sub> | Analog Power Supply                                    |  |  |

|     |                   | HIGH = ADC Output: Normal                         | 45  | AV <sub>SS5</sub> | Analog Ground                                          |  |  |

| 20  | OB                | Optical Black Clamp Pulse, Active LOW             | 46  | AV <sub>SS6</sub> | Analog Ground                                          |  |  |

| 21  | REFCK             | CDS Reference Sampling Pulse, Active LOW          | 47  | REFN              | ADC Negative Reference, Bypass to Ground               |  |  |

| 22  | DATCK             | CDS Data Sampling Pulse, Active LOW               | 48  | REFP              | ADC Positive Reference, Bypass to Ground               |  |  |

| 23  | DUMC              | Dummy Clamp, Active LOW                           |     |                   |                                                        |  |  |

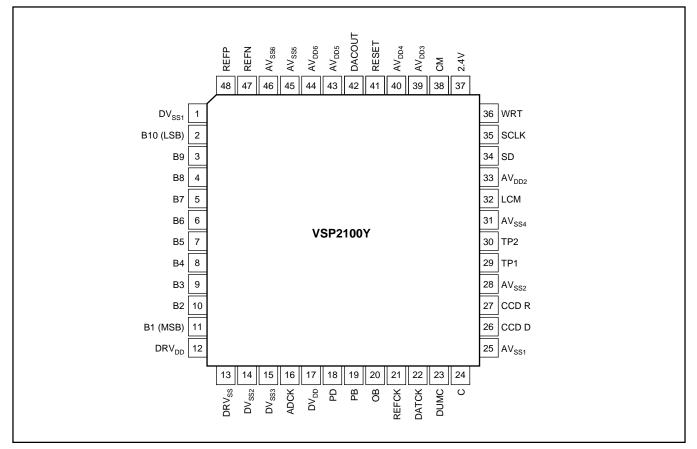

### SERIAL CONTROL DATA FORMAT FOR DAC0/DAC1

| BIT<br>NO. | DESIGNATOR | DESCRIPTION                                                                                            |

|------------|------------|--------------------------------------------------------------------------------------------------------|

| 1          | A1         | Start Bit. Either HIGH or LOW will be acceptable.                                                      |

| 2          | A0         | Address Bit. Selects internal DACs.<br>LOW = DAC0, VGA control DAC<br>HIGH = DAC1, general purpose DAC |

| 3          | D9         | Digital Input Data for DAC, Bit 10 (MSB)                                                               |

| 4          | D8         | Digital Input Data for DAC, Bit 9                                                                      |

| 5          | D7         | Digital Input Data for DAC, Bit 8                                                                      |

| 6          | D6         | Digital Input Data for DAC, Bit 7                                                                      |

| 7          | D5         | Digital Input Data for DAC, Bit 6                                                                      |

| 8          | D4         | Digital Input Data for DAC, Bit 5                                                                      |

| 9          | D3         | Digital Input Data for DAC, Bit 4                                                                      |

| 10         | D2         | Digital Input Data for DAC, Bit 3                                                                      |

| 11         | D1         | Digital Input Data for DAC, Bit 2                                                                      |

| 12         | D0         | Digital Input Data for DAC, Bit 1 (LSB)                                                                |

### TIMING SPECIFICATIONS FOR SERIAL REGISTERS

Timing Specifications =  $t_{MIN}$  to  $t_{MAX}$  with +3V power supply.

| SYMBOL           | PARAMETER                     | MIN | ТҮР | МАХ | UNITS |

|------------------|-------------------------------|-----|-----|-----|-------|

| t <sub>CKP</sub> | Serial Clock Period           | 100 |     |     | ns    |

| t <sub>CKL</sub> | Serial Clock Pulse Width LOW  | 50  |     |     | ns    |

| t <sub>скн</sub> | Serial Clock Pulse Width HIGH | 50  |     |     | ns    |

| t <sub>SD</sub>  | Data Setup Time               | 50  |     |     | ns    |

| t <sub>HD</sub>  | Data Hold Time                | 25  |     |     | ns    |

| t <sub>SW</sub>  | Write Pulse Setup Time        | 100 |     |     | ns    |

| t <sub>W</sub>   | Write Pulse Width             | 50  |     |     | ns    |

| t <sub>WD</sub>  | Data Valid Delay Time         | 50  |     |     | ns    |

| t <sub>RS</sub>  | Register Reset Pulse Width    | 50  |     |     | ns    |

| t <sub>RSD</sub> | Register Reset Delay Time     | 50  |     |     | ns    |

### TIMING FOR SERIAL PORT WRITING

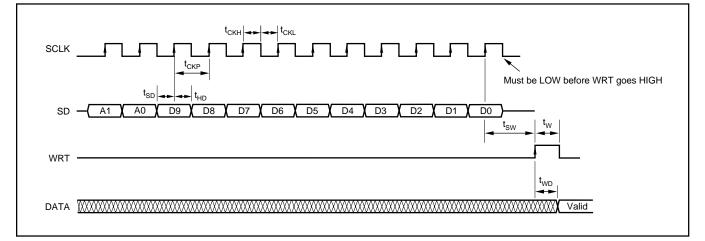

### TIMING FOR REGISTER RESET

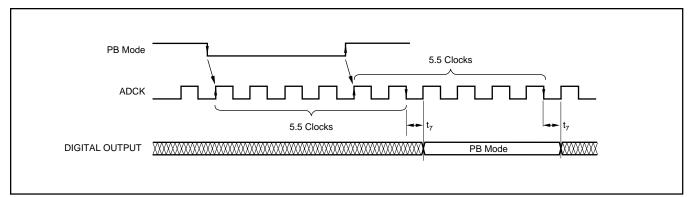

### TIMING FOR PREBLANKING

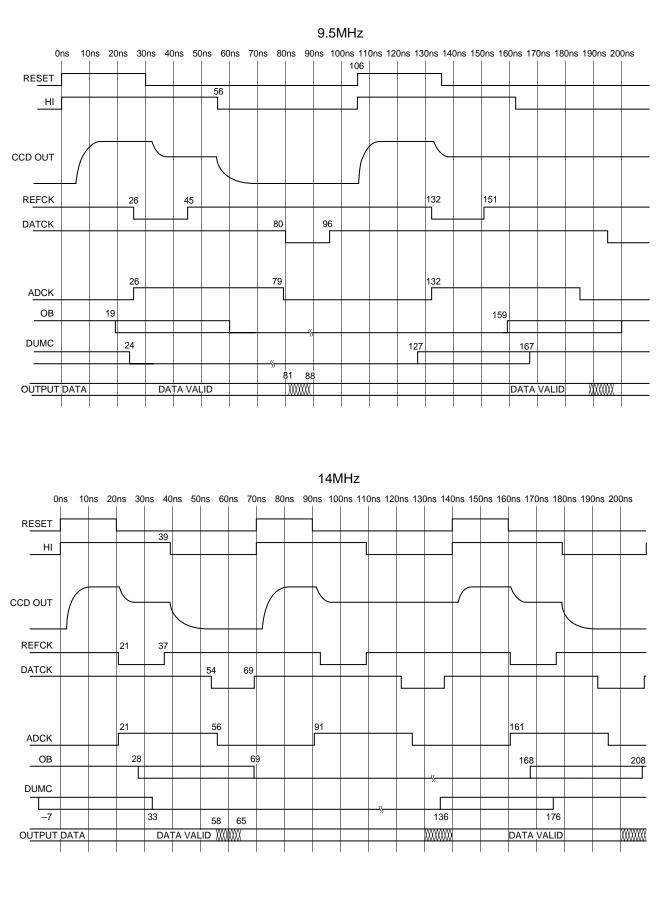

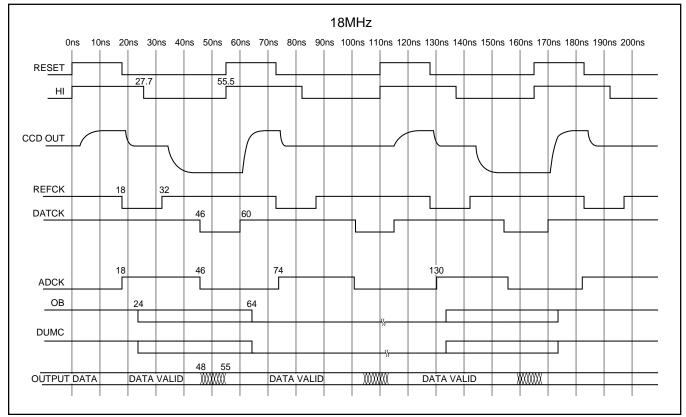

### TIMING DIAGRAMS

### **TIMING DIAGRAMS (CONT)**

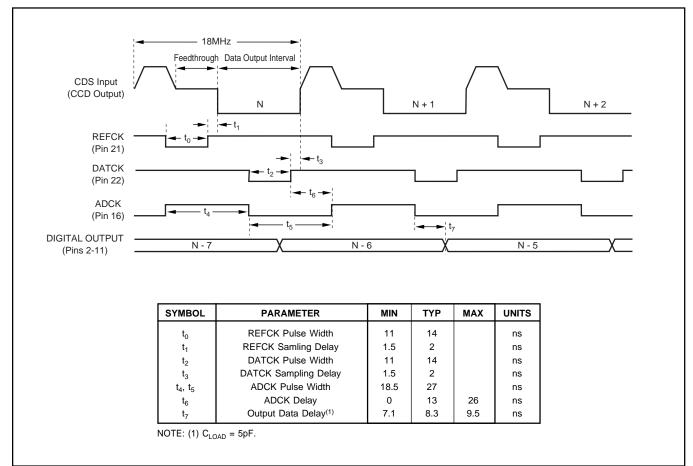

# **CDS/ADC TIMING DIAGRAM**

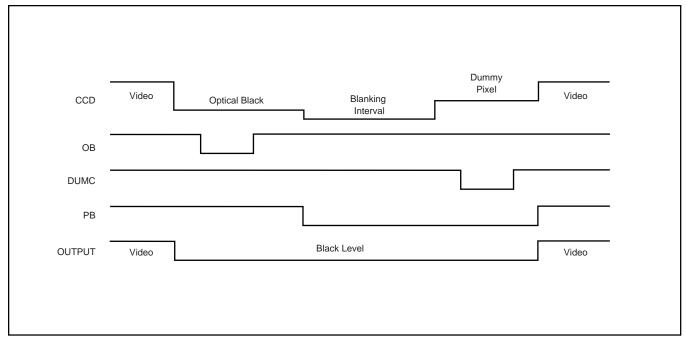

## **TYPICAL HORIZONTAL INTERVAL TIMING**

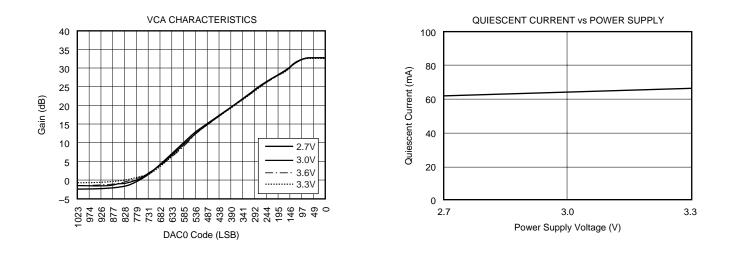

# **TYPICAL PERFORMANCE CURVES**

At  $T_A = +25^{\circ}$ C, all power supply voltages = +3.0V, and conversion rate = 18MHz, unless otherwise specified.

# THEORY OF OPERATION

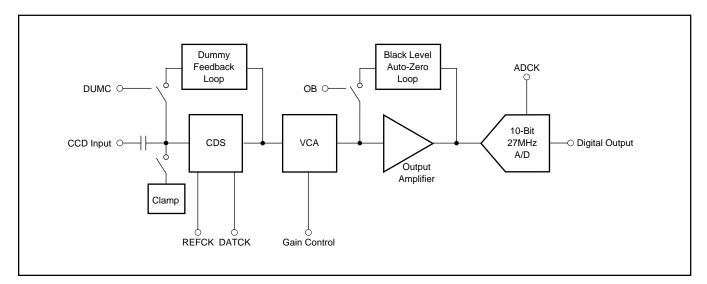

The VSP2100 is an integrated circuit that contains many of the key features associated with the processing of analog signals in a video camera or a digital-still camera. Figure 1 shows a simplified block diagram of the VSP2100.

The output from the CCD array is first sent to a Correlated Double Sampler (CDS), then a voltage-controlled attenuator with a logarithmic control characteristic, and an output amplifier prior to being applied to the input of a 10-bit A/D converter.

Two calibration cycles are employed to reduce the offset variation of the VSP2100. During the dummy pixel time, an input auto-zero circuit is activated that eliminates the offset of the correlated double sampler. During the optical black timing interval, another auto-zero circuit is employed to eliminate the offset associated with the output amplifier and the remaining offset from the CDS.

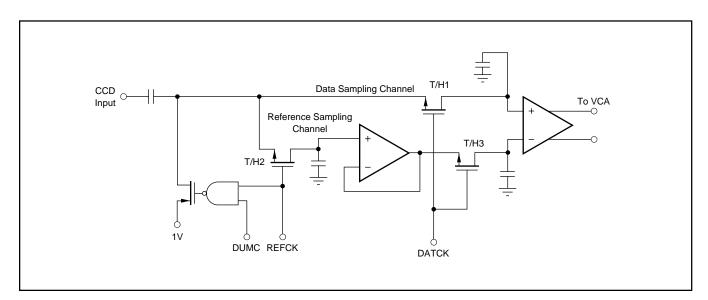

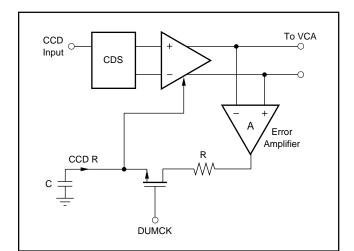

## CORRELATED DOUBLE SAMPLER (CDS)

The CDS removes low frequency noise from the output of the image sensor. Refer to Figure 2 which shows a block diagram of the CDS. The output from the CCD array is sampled during the reference interval as well as during the data interval. Noise that is present at the input and is of a period greater than the pixel interval will be eliminated by subtraction.

The VSP2100 employs a three track/hold correlated double sampler architecture. Track/Hold 2 is sampled during the reference interval by the REFCK signal. Track/Hold 3 is resampled at the same time that the data Track/Hold 1 is sampled by the DATCK signal. This is done to remove large transients from Track/Hold 2 that results from a portion of the reset transient being present during the acquisition time of this track and hold. The output of Track/Hold 2 is buffered by a voltage follower.

FIGURE 1. Simplified Block Diagram of VSP2100.

FIGURE 2. Block Diagram of Correlated Double Sampler.

### DIFFERENCE AMPLIFIER

The correlated double sampler function is completed when the output of the data and reference channel are sent to the difference amplifier where the signals are subtracted. In addition to providing the difference function, the difference amplifier amplifies the signal by a factor of 2 which helps to improve the overall signal-to-noise ratio. The difference amplifier also generates a differential signal to drive the voltage-controlled attenuator.

### **INPUT CLAMP**

The output from the CCD array is capacitively coupled to the VSP2100. To prevent shifts in the DC level from taking place due to varying input duty cycles, the input capacitor is clamped during the dummy pixel interval by the REFCK signal and the DUMC signal. A P-channel transistor is used for this input clamp switch to allow a 2V negative change at the input that would bring the signal below ground by 1. Under typical conditions, the bias at the input to the VSP2100 is at 1V.

### DUMMY PIXEL AUTO-ZERO LOOP

The output from the data and reference channel is processed by the previously mentioned difference amplifier. The differential output from the difference amplifier is sent to both the voltage-controlled logarithmic attenuator and to an error amplifier. The error amplifier amplifies and feeds a signal to the difference amplifier to drive the offset measured at the output of the difference amplifier to zero. A block diagram of this circuit is shown in Figure 3. This error amplifier serves the purpose of reducing the offset of the CDS to avoid a large offset from being amplified by the output amplifier.

The effective time constant of this loop is given by:

$$T = \frac{RC}{AD}$$

where R is  $10k\Omega$ , C is an external capacitor connected to pin 27 (CCD R), A is the gain of the error amplifier with a value of 50, and D is the duty cycle of the time that the dummy

FIGURE 3. Block Diagram of Dummy Pixel Loop.

pixel auto-zero loop is in operation. The duty cycle (D) must be considered as the loop operates in a sampled mode. Operation of the dummy auto-zero loop is activated by the DUMC signal that happens once during each horizontal line interval.

#### TIMING

The REFCK and DATCK signals are used to operate the CDS as previously explained. These same two signals are also used by internal timing circuitry to create the necessary timing signals for the A/D. The output from the A/D is read out to external circuitry by the ADCK signal. DUMC is used to activate the dummy pixel auto-zero loop and OB is used to activate the black level auto-zero loop. The input digital timing signals REFCK, DATCK, DUMC and OB are capable of being driven from either 3V or 5V logic levels.

## **VOLTAGE-CONTROLLED ATTENUATOR**

To maximize the dynamic range of the VSP2100, a voltagecontrolled attenuator is included with a control range from 0dB to -34dB. The gain control has a logarithmic relationship between the control voltage and the attenuation. The attenuator processes a differential signal from the difference amplifier to improve linearity and to reject both power supply and common-mode noise. The output from the attenuator is amplified by 28dB prior to being applied to the A/D. A typical gain control characteristic of the VSP2100 is shown in the typical performance curve, "VCA Characteristics".

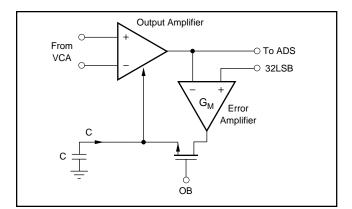

### BLACK LEVEL AUTO-ZERO LOOP

The black level auto-zero loop amplifies the difference between the output of the output amplifier and a reference signal during the optical black timing interval. This difference signal is amplified and fed back into the output amplifier to correct the offset. In doing so, the output level of the entire CCD channel can be controlled to be approximately – FS + 32LSBs under zero input signal conditions. The black level auto-zero loop is activated by the OB timing signal.

Figure 4 shows a block diagram of the black level auto-zero loop. The loop time constant is given by:

$$\Gamma = \frac{C}{(G_{\rm M}) (\rm D)}$$

FIGURE 4. Black Level Auto-Zero Loop.

where C is the external filter capacitance applied to pin 24 (C),  $G_M$  is .001 $\Omega$  and D is the duty cycle of the time that the black level auto-zero loop is in operation. The duty cycle (D) must be considered as the loop operates in a sampled mode. Operation of the black level auto-zero loop is activated by the OB signal that happens once during each horizontal line interval.

### A/D CONVERTER

The A/D converter utilizes a pipline architecture. The fully differential topology and digital error correction guarantee 10-bit resolution. The A/D converter circuitry includes a reference circuit that provides bias voltages for the entire system.

### SERIAL INTERFACE AND DACs

The VSP2100 incorporates two identical 10-bit DACs (DAC0 and DAC1). DAC0 is for controlling the amount of attenuation of the log Voltage Controlled Attenuator (VCA) and DAC1 is for user-defineable options such as iris control.

The input data for these DACs are set by the written data through the serial interface. The serial port has an 12-bit register which is controlled by four signals (SD, SCLK, WRT, RESET). SD is the serial data input, SCLK is the clock for the serial data, WRT pulse takes the serial register data into another internal parallel register at the rising edge, RESET resets all the registers' data to zeros asynchronously when RESET = LOW. The serial register uses master-slave dual flip-flops and the master flip-flop receives the input data at the rising edge of SCLK and transmits this data into the slave at the falling edge of SCLK. Therefore, the clock SCLK must be normally LOW.

When the DAC input data is all zeros, this corresponds to a maximum output voltage of 2.4V. In a similar manner, all ones correspond to a DAC output voltage of 0.3V. The VCA attenuation is at a minimum—which is the same as the channel gain being a maximum—when the DAC voltage is at 0.3V.

The serial data format and the related signal timing are shown page 5. When the input serial data is longer than 12 bits, the last 12 bits become effective and the former bits are erased.

When the registers are reset, the user should be careful that the channel gain setting becomes maximum and DAC1 output voltage goes to maximum.

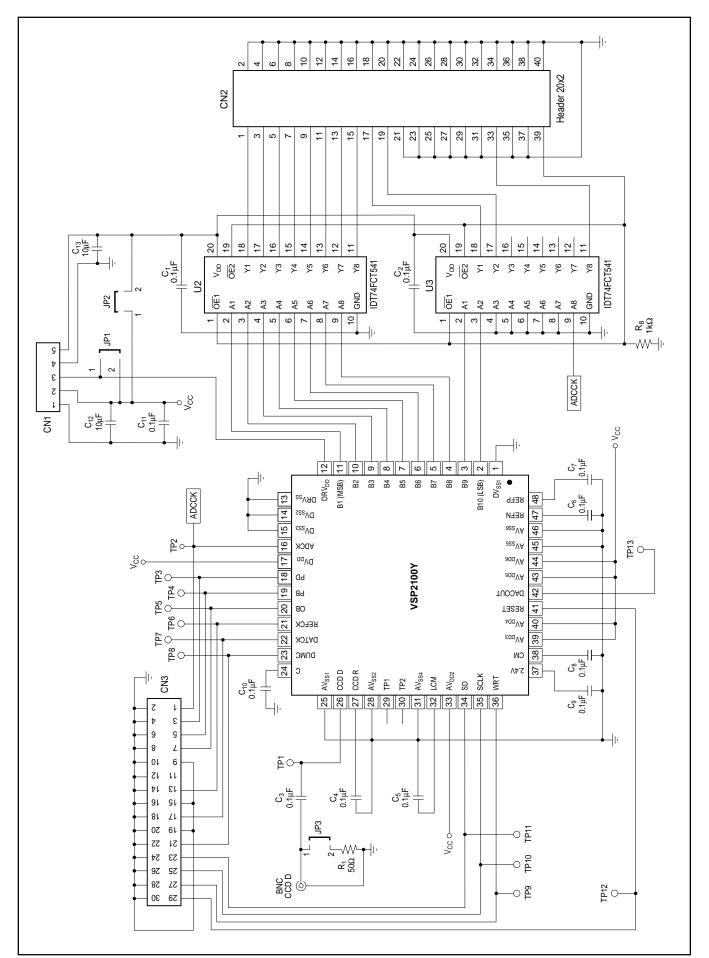

### DECOUPLING AND GROUNDING CONSIDERATIONS

The VSP2100 has several supply pins, one of which is dedicated to supply only the digital output driver (pin 12,  $DRV_{DD}$ ). The remaining supply pins are not, as is often the case, divided into analog and digital supply pins since they are internally connected on the chip. For this reason, it is recommended that the VSP2100 be treated as an analog component and be powered from the analog supply only. Digital supply lines often carry high levels of wide band noise which can couple back into the VSP2100 and limit performance.

Figure 5 shows the recommended decoupling scheme for the VSP2100. In most cases,  $0.1\mu$ F ceramic chip capacitors are adequate to keep the impedance low over a wide frequency range. Their effectiveness largely depends on the proximity to the individual pin. Therefore, they should be located as close as possible to the pins. In addition, one larger capacitor (1 $\mu$ F to 22 $\mu$ F) should be placed on the PC board in proximity of the VSP2100.

### **OTHER RECOMMENDATIONS**

$DRV_{DD}$  is a power supply used exclusively for the digital output driver and should not be connected to  $AV_{DD}$  and  $DV_{DD}$ , even if the power supply voltage is the same. The voltage level difference between  $DRV_{DD}$ ,  $AV_{DD}$ , and  $DV_{DD}$  should be kept less than 0.3V.

If your PC board has analog and digital ground,  $AV_{SS}$ ,  $DV_{SS}$ , and  $DRV_{SS}$  should be connected to analog ground.

### DEMONSTRATION BOARD

A demonstration board, DEM-VSP2100, is available to assist in the initial evaluation of the circuit performance using the VSP2100. The schematic of the DEM-VSP2100 is shown in Figure 5.

FIGURE 5. DEM-VSP2100Y Schematic.