###

SMMS649A - DECEMBER 1994 - REVISED JUNE 1995

- Organization

TM124BBK32F...1 048 576 × 32

TM248CBK32F...2 097 152 × 32

- Single 5-V Power Supply (±10% Tolerance)

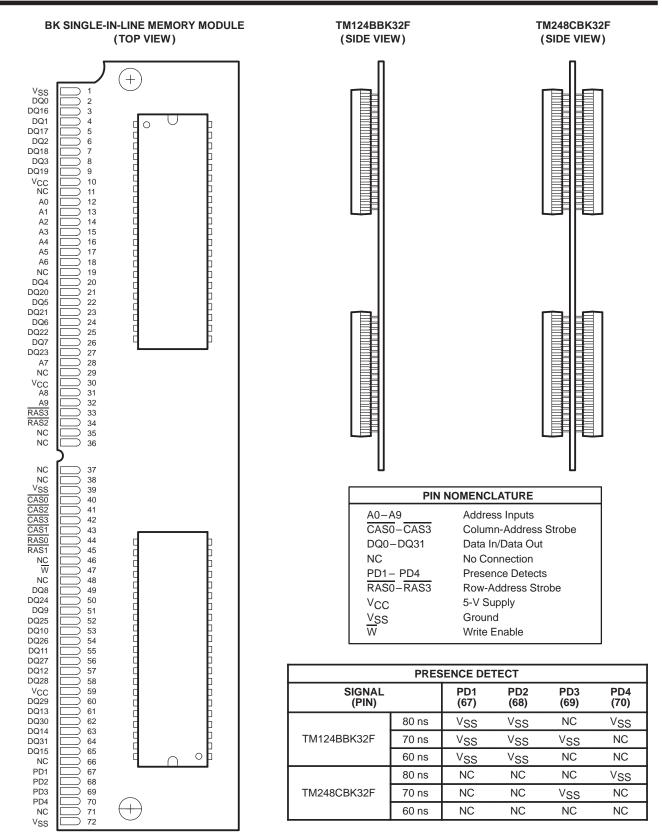

- 72-Pin Single-In-Line Memory Module (SIMM) for Use With Socket

- TM124BBK32F Utilizes Two 16-Megabit DRAMs in Plastic Small-Outline J-Lead (SOJ) Packages

- TM248CBK32F Utilizes Four 16-Megabit DRAMs in Plastic Small-Outline J-Lead (SOJ) Packages

- Long Refresh Period

16 ms (1024 Cycles)

- All Inputs, Outputs, Clocks Fully TTL Compatible

- 3-State Output

- Common CAS Control for Eight Common Data-In and Data-Out Lines in Four Blocks

- Enhanced Page-Mode Operation With CAS-Before-RAS (CBR), RAS-Only, and Hidden Refresh

- Presence Detect

- Performance Ranges:

|               | ACCESS<br>TIME<br>tRAC | ACCESS<br>TIME<br>tAA | ACCESS<br>TIME<br>tCAC | READ<br>OR<br>WRITE<br>CYCLE |

|---------------|------------------------|-----------------------|------------------------|------------------------------|

|               | (MAX)                  | (MAX)                 | (MAX)                  | (MIN)                        |

| '124BBK32F-60 | 60 ns                  | 30 ns                 | 15 ns                  | 110 ns                       |

| '124BBK32F-70 | 70 ns                  | 35 ns                 | 18 ns                  | 130 ns                       |

| '124BBK32F-80 | 80 ns                  | 40 ns                 | 20 ns                  | 150 ns                       |

| '248CBK32F-60 | 60 ns                  | 30 ns                 | 15 ns                  | 110 ns                       |

| '248CBK32F-70 | 70 ns                  | 35 ns                 | 18 ns                  | 130 ns                       |

| '248CBK32F-80 | 80 ns                  | 40 ns                 | 20 ns                  | 150 ns                       |

- Low Power Dissipation

- Operating Free-Air Temperature Range

0°C to 70°C

- Gold-Tabbed Versions Available:†

- TM124BBK32F

- TM248CBK32F

- Tin-Lead (Solder) Tabbed Versions Available:

- TM124BBK32U

- TM248CBK32U

#### description

#### TM124BBK32F

The TM124BBK32F is a 32-megabit dynamic random-access memory (DRAM) organized as four times  $1048576\times8$  in a 72-pin SIMM. The SIMM is composed of two TMS418160DZ,  $1048576\times16$ -bit DRAMs, each in a 42-lead plastic SOJ package mounted on a substrate with decoupling capacitors. The TMS418160DZ is described in the TMS418160 data sheet. The TM124BBK32F SIMM is available in the single-sided BK-leadless module for use with sockets.

#### TM248CBK32F

The TM248CBK32F is a 64-megabit DRAM organized as four times 2 097 152  $\times$  8 in a 72-pin SIMM. The SIMM is composed of four TMS418160DZ, 1 048 576  $\times$  16-bit DRAMs, each in a 42-lead plastic SOJ package mounted on a substrate with decoupling capacitors. The TMS418160DZ is described in the TMS418160 data sheet. The TM248CBK32F SIMM is available in the double-sided BK-leadless module for use with sockets.

#### operation

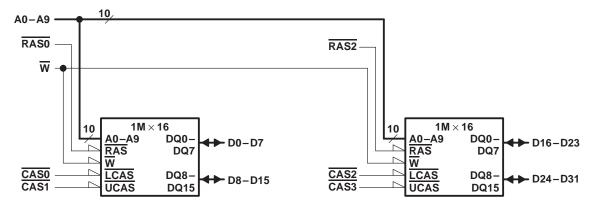

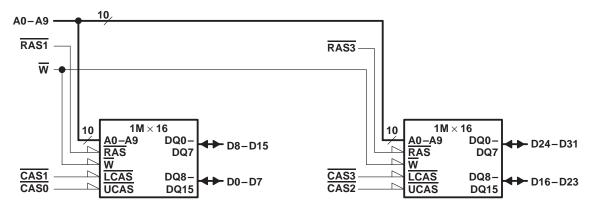

The TM124BBK32F operates as two TMS418160DZs connected as shown in the functional block diagram and Table 1. The TM248CBK32F operates as four TMS418160DZs connected as shown in the functional block diagram and Table 1. The common I/O feature dictates the use of early-write cycles to prevent contention on D and Q.

SMMS649A - DECEMBER 1994 - REVISED JUNE 1995

SMMS649A - DECEMBER 1994 - REVISED JUNE 1995

**Table 1. Connection Table**

| DATA BLOCK | RA     | .Sx                 |      |

|------------|--------|---------------------|------|

| DATA BLOCK | SIDE 1 | SIDE 2 <sup>†</sup> | CASx |

| DQ0-DQ7    | RAS0   | RAS1                | CAS0 |

| DQ8-DQ15   | RAS0   | RAS1                | CAS1 |

| DQ16-DQ23  | RAS2   | RAS3                | CAS2 |

| DQ24-DQ31  | RAS2   | RAS3                | CAS3 |

<sup>†</sup> Side 2 applies to the TM248CBK32F only.

### single-in-line memory module and components

PC substrate:  $1,27 \pm 0,1$  mm (0.05 inch) nominal thickness; 0.005 inch/inch maximum warpage Bypass capacitors: Multilayer ceramic

Contact area for TM124BBK32F and TM248CBK32F: Nickel plate and gold plate over copper Contact area for TM124BBK32U and TM248CBK32U: Nickel plate and tin/lead over copper

### functional block diagram (TM124BBK32F and TM248CBK32F, side 1)

### functional block diagram (TM248CBK32F, side 2)

SMMS649A - DECEMBER 1994 - REVISED JUNE 1995

### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)†

NOTE 1: All voltage values are with respect to VSS.

### recommended operating conditions

|                 |                                      | MIN | NOM | MAX | UNIT |

|-----------------|--------------------------------------|-----|-----|-----|------|

| VCC             | Supply voltage                       | 4.5 | 5   | 5.5 | V    |

| VIH             | High-level input voltage             | 2.4 |     | 6.5 | V    |

| V <sub>IL</sub> | Low-level input voltage (see Note 2) | - 1 |     | 0.8 | V    |

| TA              | Operating free-air temperature       | 0   |     | 70  | °C   |

NOTE 2: The algebraic convention, where the more negative (less positive) limit is designated as minimum, is used for logic-voltage levels only.

## electrical characteristics over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

|                  | PARAMETER                                 | TEST CONDITIONS                                                                                     | '124BBK32F-60 |      | '124BBK | 32F-70 | '124BBK | UNIT |      |

|------------------|-------------------------------------------|-----------------------------------------------------------------------------------------------------|---------------|------|---------|--------|---------|------|------|

|                  | PARAMETER                                 | TEST CONDITIONS                                                                                     | MIN MAX       |      | MIN     | MAX    | MIN     | MAX  | UNIT |

| Vон              | High-level output voltage                 | I <sub>OH</sub> = - 5 mA                                                                            | 2.4           |      | 2.4     |        | 2.4     |      | V    |

| VOL              | Low-level output voltage                  | I <sub>OL</sub> = 4.2 mA                                                                            |               | 0.4  |         | 0.4    |         | 0.4  | V    |

| Ι <sub>Ι</sub>   | Input current (leakage)                   | $V_{CC} = 5.5 \text{ V},  V_I = 0 \text{ V to } 6.5 \text{ V},$<br>All other pins = 0 V to $V_{CC}$ |               | ± 10 |         | ± 10   |         | ± 10 | μА   |

| lo               | Output current (leakage)                  | $V_{CC} = 5.5 \text{ V},$<br>$V_{O} = 0 \text{ V to V}_{CC},$<br>$\overline{CAS}$ high              |               | ± 10 |         | ± 10   |         | ± 10 | μА   |

| I <sub>CC1</sub> | Read- or write-cycle current              | V <sub>CC</sub> = 5.5 V, Minimum cycle                                                              |               | 180  |         | 160    |         | 140  | mA   |

|                  |                                           | V <sub>IH</sub> = 2.4 V (TTL),<br><u>After</u> 1 memory cycle,<br>RAS and CAS high                  |               | 4    |         | 4      |         | 4    | mA   |

| ICC2             | Standby current                           | $V_{IH} = V_{CC} - 0.2 V (CMOS),$<br>After 1 memory cycle,<br>RAS and CAS high                      |               | 2    |         | 2      |         | 2    | mA   |

| ICC3             | Average refresh current (RAS only or CBR) | VCC = 5.5 V, Minimum cycle,  RAS cycling,  CAS high (RAS only);  RAS low after CAS low (CBR)        |               | 180  |         | 160    |         | 140  | mA   |

| I <sub>CC4</sub> | Average page current                      | $\frac{V_{CC}}{RAS} = 5.5 \text{ V},  \frac{t_{PC}}{CAS} = MIN,$                                    |               | 180  |         | 160    |         | 140  | mA   |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

SMMS649A - DECEMBER 1994 - REVISED JUNE 1995

### electrical characteristics over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)<sup>†</sup>

|                  | DADAMETED                                              | TEST CONDITIONS                                                                                           | '248CBK | 32F-60 | '248CBK3 | 32F-70 | '248CBK3 | UNIT |      |

|------------------|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|---------|--------|----------|--------|----------|------|------|

|                  | PARAMETER                                              | TEST CONDITIONS                                                                                           | MIN     | MAX    | MIN      | MAX    | MIN      | MAX  | UNIT |

| Vон              | High-level output voltage                              | I <sub>OH</sub> = – 5 mA                                                                                  | 2.4     |        | 2.4      |        | 2.4      |      | >    |

| VOL              | Low-level output voltage                               | I <sub>OL</sub> = 4.2 mA                                                                                  |         | 0.4    |          | 0.4    |          | 0.4  | ٧    |

| Ι <sub>Ι</sub>   | Input current (leak-<br>age)                           | $V_{CC} = 5.5 \text{ V},$ $V_I = 0 \text{ V to } 6.5 \text{ V},$ All other pins = 0 V to $V_{CC}$         |         | ± 10   |          | ± 10   |          | ± 10 | μΑ   |

| IO               | Output current (leakage)                               | $V_{CC} = 5.5 \text{ V},$<br>$V_{O} = 0 \text{ V to } V_{CC}, \overline{CAS} \text{ high}$                |         | ± 20   |          | ± 20   |          | ± 20 | μΑ   |

| ICC1             | Read- or write-cycle current (see Note 3)              | V <sub>CC</sub> = 5.5 V, Minimum cycle                                                                    |         | 184    |          | 164    |          | 144  | mA   |

| laga             | Standby current                                        | V <sub>IH</sub> = 2.4 V (TTL),<br><u>After</u> 1 memory cycle,<br>RAS and CAS high                        |         | 8      |          | 8      |          | 8    | mA   |

| ICC2             |                                                        | V <sub>IH</sub> = V <sub>CC</sub> - 0.2 V (CMOS),<br>After 1 memory cycle,<br>RAS and CAS high            |         | 4      |          | 4      |          | 4    | mA   |

| ICC3             | Average refresh current (RAS only or CBR) (see Note 3) | V <sub>CC</sub> = 5.5 V, Minimum cycle,  RAS cycling,  CAS high (RAS only);  RAS low after CAS low (CBR)  |         | 360    |          | 320    |          | 280  | mA   |

| I <sub>CC4</sub> | Average page current (see Note 4)                      | $\frac{\text{V}_{CC}}{\text{RAS}} = 5.5 \text{ V}, \qquad \frac{\text{t}_{PC}}{\text{CAS}} = \text{MIN},$ |         | 184    |          | 164    |          | 144  | mA   |

<sup>†</sup> For test conditions shown as MIN/MAX, use the appropriate value specified under recommended operating conditions.

NOTES: 3. Measured with a maximum of one address change while  $\overline{RAS} = V_{IL}$

### capacitance over recommended ranges of supply voltage and operating free-air temperature, f = 1 MHz (see Note 5)

|                    | PARAMETER '1                               | '124BE | K32F | '248CB | UNIT |      |

|--------------------|--------------------------------------------|--------|------|--------|------|------|

|                    | FARAINETER                                 | MIN    | MAX  | MIN    | MAX  | UNIT |

| C <sub>i(A)</sub>  | Input capacitance, A0-A9                   |        | 10   |        | 20   | pF   |

| C <sub>i(R)</sub>  | Input capacitance, RAS inputs              |        | 7    |        | 7    | pF   |

| C <sub>i(C)</sub>  | Input capacitance, CAS inputs              |        | 7    |        | 14   | pF   |

| C <sub>i(W)</sub>  | Input capacitance, $\overline{\mathbb{W}}$ |        | 14   |        | 28   | pF   |

| C <sub>o(DQ)</sub> | Output capacitance on DQ0-DQ31             |        | 7    |        | 14   | pF   |

NOTE 5:  $V_{CC}$  = 5 V  $\pm$  0.5 V, and the bias on pins under test is 0 V.

<sup>4.</sup> Measured with a maximum of one address change while CAS = VIH

SMMS649A - DECEMBER 1994 - REVISED JUNE 1995

### switching characteristics over recommended ranges of supply voltage and operating free-air temperature

|                  | PARAMETER                                       |   | '124BBK32F-60<br>'248CBK32F-60 |     | '124BBK32F-70<br>'248CBK32F-70 |     |     |    |

|------------------|-------------------------------------------------|---|--------------------------------|-----|--------------------------------|-----|-----|----|

|                  |                                                 |   | MAX                            | MIN | MAX                            | MIN | MAX |    |

| t <sub>AA</sub>  | Access time from column address                 |   | 30                             |     | 35                             |     | 40  | ns |

| tCAC             | Access time from CAS low                        |   | 15                             |     | 18                             |     | 20  | ns |

| t <sub>RAC</sub> | Access time from RAS low                        |   | 60                             |     | 70                             |     | 80  | ns |

| tCPA             | Access time from column precharge               |   | 35                             |     | 40                             |     | 45  | ns |

| tCLZ             | CAS to output in low-impedance state            | 0 |                                | 0   |                                | 0   |     | ns |

| tOH              | Output disable time from start of CAS high      | 3 |                                | 3   |                                | 3   |     | ns |

| tOFF             | Output disable time after CAS high (see Note 6) | 0 | 15                             | 0   | 18                             | 0   | 20  | ns |

NOTE 6: t<sub>OFF</sub> is specified when the output is no longer driven.

### timing requirements over recommended ranges of supply voltage and operating free-air temperature

|                   |                                                         |     | '124BBK32F-60<br>'248CBK32F-60 |     | K32F-70<br>K32F-70 |     |         | UNIT |

|-------------------|---------------------------------------------------------|-----|--------------------------------|-----|--------------------|-----|---------|------|

|                   |                                                         | MIN | MAX                            | MIN | MAX                | MIN | MAX     |      |

| tRC               | Cycle time, random read or write (see Note 7)           | 110 |                                | 130 |                    | 150 |         | ns   |

| tRWC              | Cycle time, read-write                                  | 155 |                                | 181 |                    | 205 |         | ns   |

| t <sub>PC</sub>   | Cycle time, page-mode read or write (see Notes 7 and 8) | 40  |                                | 45  |                    | 50  |         | ns   |

| t <sub>RASP</sub> | Pulse duration, page mode, RAS low                      | 60  | 100 000                        | 70  | 100 000            | 80  | 100 000 | ns   |

| tRAS              | Pulse duration, nonpage mode, RAS low                   | 60  | 10 000                         | 70  | 10 000             | 80  | 10 000  | ns   |

| tCAS              | Pulse duration, CAS low                                 | 15  | 10 000                         | 18  | 10 000             | 20  | 10 000  | ns   |

| tCP               | Pulse duration, CAS high                                | 10  |                                | 10  |                    | 10  |         | ns   |

| t <sub>RP</sub>   | Pulse duration, RAS high (precharge)                    | 40  |                                | 50  |                    | 60  |         | ns   |

| tWP               | Pulse duration, $\overline{W}$ low                      | 10  |                                | 10  |                    | 10  |         | ns   |

| tASC              | Setup time, column address before CAS low               | 0   |                                | 0   |                    | 0   |         | ns   |

| t <sub>ASR</sub>  | Setup time, row address before RAS low                  | 0   |                                | 0   |                    | 0   |         | ns   |

| tDS               | Setup time, data before CAS low                         | 0   |                                | 0   |                    | 0   |         | ns   |

| tRCS              | Setup time, W high before CAS low                       | 0   |                                | 0   |                    | 0   |         | ns   |

| tCWL              | Setup time, W low before CAS high                       | 15  |                                | 18  |                    | 20  |         | ns   |

| tRWL              | Setup time, W low before RAS high                       | 15  |                                | 18  |                    | 20  |         | ns   |

| twcs              | Setup time, W low before CAS low                        | 0   |                                | 0   |                    | 0   |         | ns   |

| tWRP              | Setup time, W high before RAS low (CBR refresh only)    | 10  |                                | 10  |                    | 10  |         | ns   |

| <sup>t</sup> CAH  | Hold time, column address after CAS low                 | 10  |                                | 15  |                    | 15  |         | ns   |

| <sup>t</sup> RHCP | Hold time, RAS high from CAS precharge                  | 35  |                                | 40  |                    | 45  |         | ns   |

| <sup>t</sup> DH   | Hold time, data after CAS low                           | 10  |                                | 15  |                    | 15  |         | ns   |

| <sup>t</sup> RAH  | Hold time, row address after RAS low                    | 10  |                                | 10  |                    | 10  |         | ns   |

| <sup>t</sup> RCH  | Hold time, W high after CAS high (see Note 9)           | 0   |                                | 0   |                    | 0   |         | ns   |

| <sup>t</sup> RRH  | Hold time, W high after RAS high (see Note 9)           | 0   |                                | 0   |                    | 0   |         | ns   |

NOTES: 7. All cycles assume  $t_T = 5$  ns.

8. To assure tpc min, tasc should be  $\geq$  tcp .

9. Either t<sub>RRH</sub> or t<sub>RCH</sub> must be satisfied for a read cycle.

SMMS649A - DECEMBER 1994 - REVISED JUNE 1995

### timing requirements over recommended ranges of supply voltage and operating free-air temperature (continued)

|      |                                                     |     | '124BBK32F-60<br>'248CBK32F-60 |     | '124BBK32F-70<br>'248CBK32F-70 |     | 32F-80<br>32F-80 | UNIT |

|------|-----------------------------------------------------|-----|--------------------------------|-----|--------------------------------|-----|------------------|------|

|      |                                                     | MIN | MAX                            | MIN | MAX                            | MIN | MAX              |      |

| tWCH | Hold time, W low after CAS low                      | 10  |                                | 15  |                                | 15  |                  | ns   |

| tWRH | Hold time, W high after RAS low (CBR refresh only)  | 10  |                                | 10  |                                | 10  |                  | ns   |

| tCHR | Delay time, RAS low to CAS high (CBR refresh only)  | 10  |                                | 10  |                                | 10  |                  | ns   |

| tCRP | Delay time, CAS high to RAS low                     | 5   |                                | 5   |                                | 5   |                  | ns   |

| tCSH | Delay time, RAS low to CAS high                     | 60  |                                | 70  |                                | 80  |                  | ns   |

| tCSR | Delay time, CAS low to RAS low (CBR refresh only)   | 5   |                                | 5   |                                | 5   |                  | ns   |

| tRAD | Delay time, RAS low to column address (see Note 10) | 15  | 30                             | 15  | 35                             | 15  | 40               | ns   |

| tRAL | Delay time, column address to RAS high              | 30  |                                | 35  |                                | 40  |                  | ns   |

| tCAL | Delay time, column address to CAS high              | 30  |                                | 35  |                                | 40  |                  | ns   |

| tRCD | Delay time, RAS low to CAS low (see Note 10)        | 20  | 45                             | 20  | 52                             | 20  | 60               | ns   |

| tRPC | Delay time, RAS high to CAS low (CBR only)          | 0   |                                | 0   |                                | 0   |                  | ns   |

| tRSH | Delay time, CAS low to RAS high                     | 15  |                                | 18  |                                | 20  |                  | ns   |

| tREF | Refresh time interval                               |     | 16                             |     | 16                             |     | 16               | ms   |

| tŢ   | Transition time                                     | 3   | 30                             | 3   | 30                             | 3   | 30               | ns   |

NOTE 10: The maximum value is specified only to assure access time.

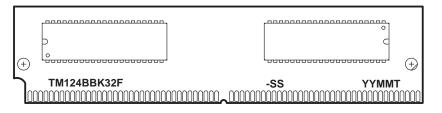

### device symbolization (TM124BBK32F illustrated)

YY = Year Code MM = Month Code

T = Assembly Site Code

-SS = Speed Code

NOTE: Location of symbolization may vary.

SMMS649A - DECEMBER 1994 - REVISED JUNE 1995

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1998, Texas Instruments Incorporated