# 21285 Core Logic for SA-110 Microprocessor

**Datasheet**

September 1998

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Product Name may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright © Intel Corporation, 1998

\*Third-party brands and names are the property of their respective owners.

# intel® Contents

| 1 | Introd | luction                         | 1–1  |

|---|--------|---------------------------------|------|

|   | 1.1    | Features                        |      |

|   | 1.2    | System Applications             |      |

| 2 | Signa  | ll Description                  | 2–1  |

|   | 2.1    | PCI Signals                     | 2–1  |

|   | 2.2    | SA-110 Signals                  | 2–3  |

|   | 2.3    | ROM Signals                     |      |

|   | 2.4    | SDRAM Signals                   | 2–5  |

|   | 2.5    | Serial Port Signals             | 2–7  |

|   | 2.6    | Miscellaneous Signals           | 2–7  |

|   | 2.7    | X-Bus/Arbiter Signals           | 2–8  |

|   |        | 2.7.1 X-Bus Selection           | 2-9  |

|   |        | 2.7.2 PCI Arbiter Selection     | 2–10 |

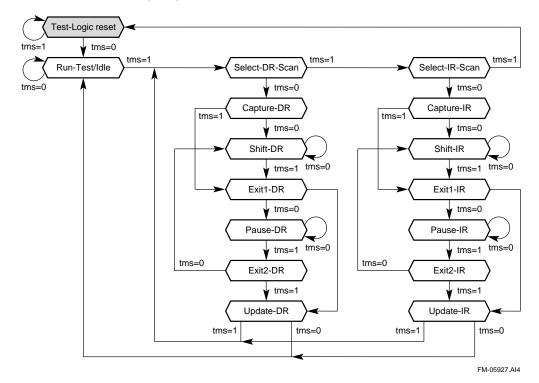

|   | 2.8    | JTAG Signals                    | 2–10 |

|   | 2.9    | Pin State During Reset          | 2–11 |

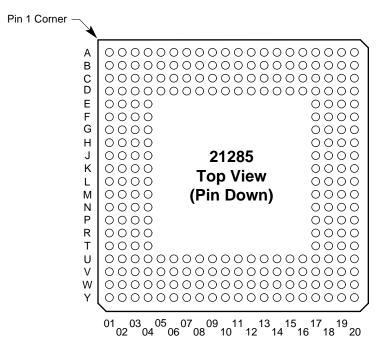

|   | 2.10   | Pin Assignment                  | 2–12 |

|   | 2.11   | Pins Listed in Numeric Order    | 2–13 |

|   | 2.12   | Pins Listed in Alphabetic Order | 2–17 |

| 3 | Trans  | actions                         | 3–1  |

|   | 3.1    | SA-110 Originated Transactions  | 3–1  |

|   |        | 3.1.1 CSR Write                 |      |

|   |        | 3.1.2 CSR Read                  | 3–1  |

|   |        | 3.1.3 SDRAM All-Banks Precharge | 3–2  |

|   |        | 3.1.4 SDRAM Mode Register Set   |      |

|   |        | 3.1.5 SDRAM Write               |      |

|   |        | 3.1.6 SDRAM First Read          |      |

|   |        | 3.1.6.1 Lock                    |      |

|   |        | 3.1.7 ROM Read                  |      |

|   |        | 3.1.8 ROM Write                 |      |

|   |        | 3.1.9 PCI Memory Write          |      |

|   |        | 3.1.10 PCI Memory Read          |      |

|   |        | 3.1.11 PCI I/O Write            |      |

|   |        | 3.1.12 PCI I/O Read             |      |

|   |        | 3.1.13 PCI Configuration Write  |      |

|   |        | 3.1.14 PCI Configuration Read   |      |

|   |        | 3.1.15 PCI Special Cycle        |      |

|   |        | 3.1.16 PCI IACK Read            |      |

|   |        | 3.1.17 X-Bus Write              |      |

|   |        | 3.1.18 X-Bus Read               |      |

|   |        | 3.1.19 Outbound Write Flush     |      |

|   |        | 3.1.20 SA-110 Cache Flush       |      |

|   |        | 3.1.21 Reserved Addresses       |      |

|   | 3.2    | PCI Target Transactions         |      |

|   |       | 3.2.1<br>3.2.2 | Unsupported PCI Cycles As Target                                                              |     |

|---|-------|----------------|-----------------------------------------------------------------------------------------------|-----|

|   |       | 3.2.3          | Memory Read, Memory Read Line, Memory Read Multiple to SDRAM                                  |     |

|   |       | 3.2.4          | Type 0 Configuration Write                                                                    |     |

|   |       | 3.2.5          | Type 0 Configuration Read                                                                     |     |

|   |       | 3.2.6          | Write to CSR                                                                                  |     |

|   |       | 3.2.7          | Read to CSR                                                                                   |     |

|   |       | 3.2.7          | Write to I <sub>2</sub> O Address                                                             |     |

|   |       | 3.2.9          | Read to I <sub>2</sub> O Address                                                              |     |

|   |       |                | <u> </u>                                                                                      |     |

|   |       | 3.2.10         | Memory Write to ROM                                                                           |     |

|   | 2.2   | 3.2.11         | Memory Read to ROM                                                                            |     |

|   | 3.3   |                | aster Transactions                                                                            |     |

|   |       | 3.3.1          | Dual Address Cycles (DAC) Support                                                             |     |

|   |       |                | 3.3.1.1 For SA-110 Accesses                                                                   |     |

|   |       | 0 0 0          | 3.3.1.2 For DMA Accesses                                                                      |     |

|   |       | 3.3.2          | Memory Write, Memory Write and Invalidate                                                     |     |

|   |       |                | 3.3.2.1 From SA-110                                                                           |     |

|   |       |                | 3.3.2.2 From DMA                                                                              |     |

|   |       | 2 2 2          | 3.3.2.3 Selecting PCI Command for Writes  Memory Read, Memory Read Line, Memory Read Multiple |     |

|   |       | 3.3.3          |                                                                                               |     |

|   |       |                | 3.3.3.1 From SA-110                                                                           |     |

|   |       |                | 3.3.3.2 From DMA                                                                              |     |

|   |       | 3.3.4          | I/O Write                                                                                     |     |

|   |       | 3.3.5          | I/O Read                                                                                      |     |

|   |       |                |                                                                                               |     |

|   |       | 3.3.6          | Configuration Write                                                                           |     |

|   |       | 3.3.7          | Configuration Read                                                                            |     |

|   |       | 3.3.8          | Special Cycle                                                                                 |     |

|   |       | 3.3.9          | IACK Read                                                                                     |     |

|   |       | 3.3.10         | PCI Request Operation                                                                         |     |

|   |       | 3.3.11         | Master Latency Timer                                                                          |     |

|   | 3.4   |                | ror Summary                                                                                   |     |

|   |       | 3.4.1          | Errors As PCI Target                                                                          |     |

|   |       |                | 3.4.1.1 Address Parity Error                                                                  |     |

|   |       |                | 3.4.1.2 Write Data Parity Error                                                               |     |

|   |       | 0.40           | 3.4.1.3 Read Data Parity Error                                                                |     |

|   |       | 3.4.2          | Errors As PCI Master                                                                          |     |

|   |       |                | 3.4.2.1 Master Abort                                                                          |     |

|   |       |                | 3.4.2.2 Write Data Parity Error                                                               |     |

|   |       |                | 3.4.2.3 Target Abort on Write                                                                 |     |

|   |       |                | 3.4.2.5 Target Abort on Read                                                                  |     |

|   |       |                |                                                                                               |     |

| 4 | SDRAN | A and R        | OM Operation                                                                                  | 4–1 |

|   | 4.1   | SDRAN          | M Control                                                                                     | 4–1 |

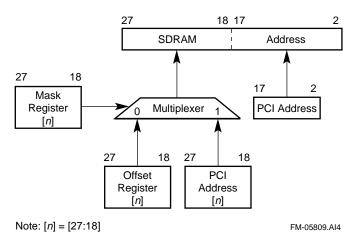

|   |       | 4.1.1          | SDRAM Addresses                                                                               | 4–2 |

|   |       | 4.1.2          | Commands                                                                                      | 4–3 |

|   |       | 4.1.3          | Parity                                                                                        | 4–4 |

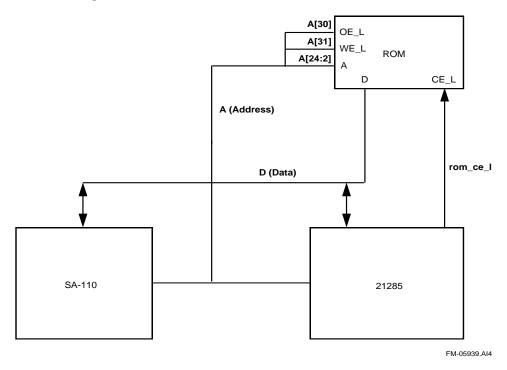

|   | 4.2   | ROM C          | Control                                                                                       |     |

|   |       | 4.2.1          | Addressing                                                                                    | 4–5 |

|   |       |                | -                                                                                             |     |

# intel<sub>®</sub>

|   |       | 4.2.2               | Reads                                    | 4–7  |

|---|-------|---------------------|------------------------------------------|------|

|   |       | 4.2.3               | Writes                                   | 4–7  |

|   |       | 4.2.4               | Timing                                   | 4–7  |

|   |       | 4.2.5               | Blank ROM Programming                    | 4–8  |

| 5 | SA-11 | 10 Opera            | tion                                     | 5–1  |

|   | 5.1   | SA-11               | 0 Control                                | 5–1  |

|   |       | 5.1.1               | Address Map Partitioning                 |      |

|   |       | 5.1.2               | Byte Enables                             |      |

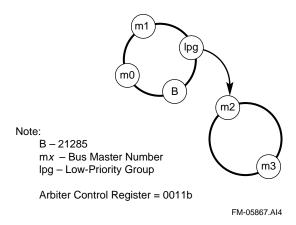

|   |       | 5.1.3               | SA-110 Bus Arbiter                       |      |

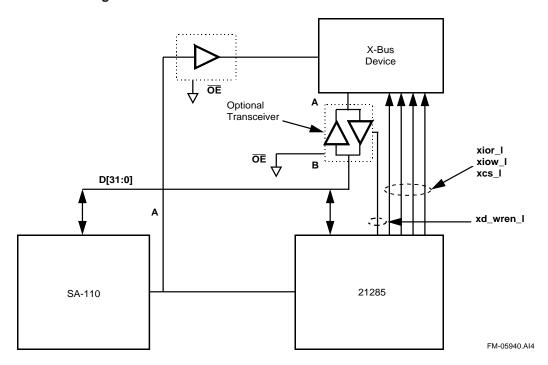

|   | 5.2   | X-Bus               | Interface                                |      |

|   |       | 5.2.1               | Address and Data Bus Generation          |      |

|   |       | 5.2.2               | Device Support                           |      |

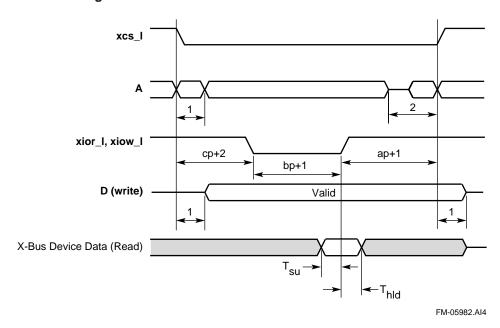

|   |       | 5.2.3               | Timing                                   |      |

|   | 5.3   | Orderi              | ng and Deadlock Avoidance                |      |

|   |       | 5.3.1               | Transaction Ordering                     |      |

|   |       | 5.3.2               | Ordering Rules                           |      |

|   |       | 5.3.3               | Deadlock Avoidance                       |      |

| 6 | Funct | ional Uni           | ts                                       | 6–1  |

|   | 6.1   | PCI Bi              | us Arbiter                               | 6–1  |

|   |       | 6.1.1               | Priority Algorithm                       |      |

|   |       | 6.1.2               | Determining Priority                     |      |

|   | 6.2   | DMA (               | Channels                                 |      |

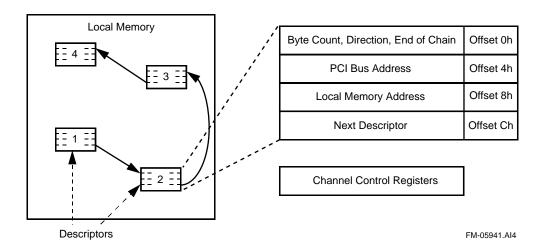

|   |       | 6.2.1               | DMA Channel Operation                    |      |

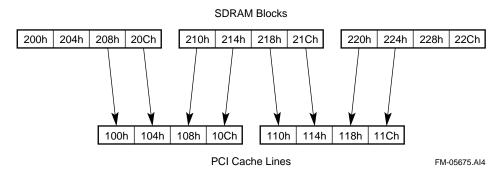

|   |       | 6.2.2               | SDRAM-to-PCI Transfer                    |      |

|   |       | 6.2.3               | PCI-to-SDRAM Transfer                    | 6–6  |

|   |       | 6.2.4               | Channel Alignment                        | 6–6  |

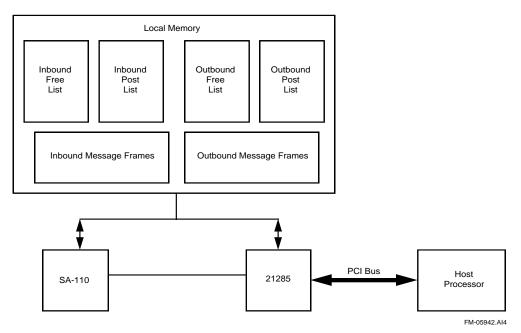

|   | 6.3   | I <sub>2</sub> O Me | essage Unit                              | 6–7  |

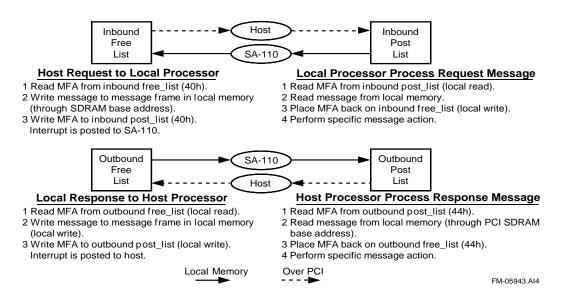

|   |       | 6.3.1               | I <sub>2</sub> O Inbound FIFO Operation  | 6-9  |

|   |       | 6.3.2               | I <sub>2</sub> O Outbound FIFO Operation | 6–9  |

|   |       | 6.3.3               | Circulation of MFAs                      | 6–10 |

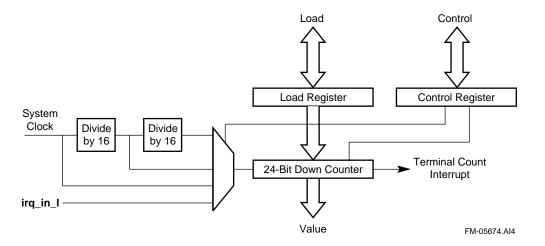

|   | 6.4   | Timers              | 3                                        | 6–11 |

|   |       | 6.4.1               | Timer 4 Application                      | 6–11 |

|   | 6.5   | Serial              | Port                                     | 6–12 |

|   |       | 6.5.1               | Data Handling                            | 6–12 |

|   |       | 6.5.2               | Initialization                           | 6–12 |

|   |       | 6.5.3               | Frame Format                             |      |

|   |       | 6.5.4               | Baud Rate Generation                     |      |

|   |       | 6.5.5               | Receive Operation                        |      |

|   |       | 6.5.6               | Transmit Operation                       |      |

|   |       | 6.5.7               | Serial Port Interrupts                   |      |

|   | 6.6   |                     | Register Definitions                     |      |

|   |       | 6.6.1               | UARTDR—Offset 160h                       |      |

|   |       | 6.6.2               | RXSTAT—Offset 164h                       |      |

|   |       | 6.6.3               | H_UBRLCR—Offset 168h                     |      |

|   |       | 6.6.4               | M_UBRLCR—Offset 16Ch                     |      |

|   |       | 6.6.5               | L_UBRLCR—Offset 170h                     |      |

|   |       | 6.6.6               | UARTCON-Offset 174h                      |      |

|   |       | 6.6.7               | UARTFLG—Offset 178h                      | 6–18 |

| 1 | Regis | ters   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | /-1  |

|---|-------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|   | 7.1   | PCI Co | onfiguration Space Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 7–1  |

|   |       | 7.1.1  | Vendor ID Register—Offset 00h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |

|   |       | 7.1.2  | Device ID Register—Offset 02h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |

|   |       | 7.1.3  | Command Register—Offset 04h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |

|   |       | 7.1.4  | Status Register—Offset 06h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |

|   |       | 7.1.5  | Revision ID Register—Offset 08h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

|   |       | 7.1.6  | Class Code Register—Offset 0Ah                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |

|   |       | 7.1.7  | Cache Line Size Register—Offset 0Ch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |

|   |       | 7.1.8  | Latency Timer Register—Offset 0Dh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |

|   |       | 7.1.9  | Header Type Register—Offset 0Eh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

|   |       | 7.1.10 | BIST Register—Offset 0Fh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |

|   |       | 7.1.11 | CSR Memory Base Address Register—Offset 10h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |

|   |       |        | CSR I/O Base Address Register—Offset 14h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |

|   |       |        | SDRAM Base Address Register—Offset 18h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |

|   |       | 7.1.14 | <del>-</del>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |

|   |       | 7.1.15 | Expansion ROM Base Address Register—Offset 30h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |

|   |       |        | Capabilities Pointer—Offset 34h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

|   |       |        | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |

|   |       | 7.1.18 | Subsystem ID Register—Offset 2Eh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |

|   |       | 7.1.19 | Interrupt Line Register—Offset 3Ch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |

|   |       | 7.1.20 | Interrupt Pin Register—Offset 3Dh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |

|   |       | 7.1.21 | Min_Gnt Register—Offset 3Eh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |

|   |       | 7.1.21 | Max_Lat Register—Offset 3Fh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |

|   |       | 7.1.23 | Capability Identifier Register—Offset 70h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |

|   |       | _      | Power Management Capabilities (PMC) Register—Offset 72h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |

|   |       | 7.1.25 | Power Management Control/Status (PMCSR) Register—Offset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |

|   |       | _      | Data—Offset 77h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

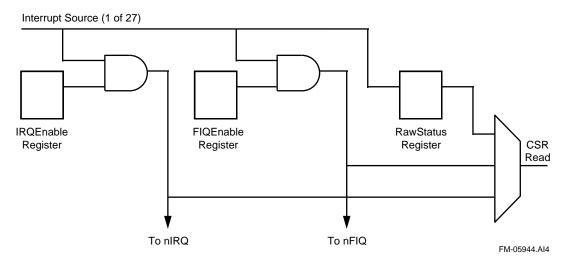

|   | 7.2   |        | ontrol and Status Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |