查询33800供应商

Freescale Semiconductor Advance Information LPCB打样工厂,24小时加急出货 Document Number: MC33800

Rev. 5.0, 10/2007

**VRoHS**

# Engine Control Integrated Circuit

The 33800 is a combination output switch and driver Integrated Circuit (IC) which can be used in numerous powertrain applications. The IC contains two programmable constant current drivers (CCD), an octal, low side, serial switch (OSS), and six, external MOSFET gate pre-drivers (GD). The IC has over-voltage, under-voltage, and thermal protection. All drivers and switches, including the external MOSFETs, have over-current protection, off-state open load detection, on-state shorted load detection, and fault annunciation via the serial peripheral interface (SPI).

Additional features include: Low power Sleep Mode, Heated Exhaust Gas Oxygen (HEGO) sensor diagnostics, output control via serial and/or parallel inputs, PWM capability, and programmable current output with dithering. These features, along with cost effective packaging, make the 33800 ideal for Powertrain Engine Control applications.

#### Features

- Wide operating voltage range, 5 < VPWR < 36V</li>

- Interfaces to 3.3V and 5V microprocessors via SPI protocol

- Low, Sleep Mode, standby current, typically 10uA.

- Internal or external voltage reference

- Internal oscillator with calibrate capability

- Measures resistance to monitor HEGO sensors

- CCDs have programmable current, dither frequency and amplitude

- OSSs can be paralleled to increase current capability

- GDs have programmable frequency and duty cycle PWM

- All outputs controllable via serial and/or parallel inputs

- Pb-free packaging designated by suffix code EK

#### ORDERING INFORMATION

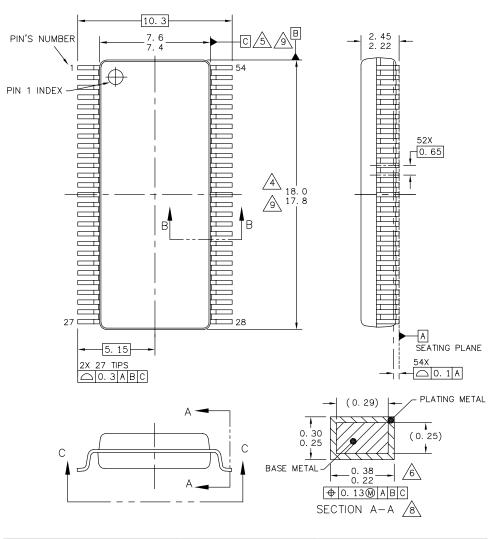

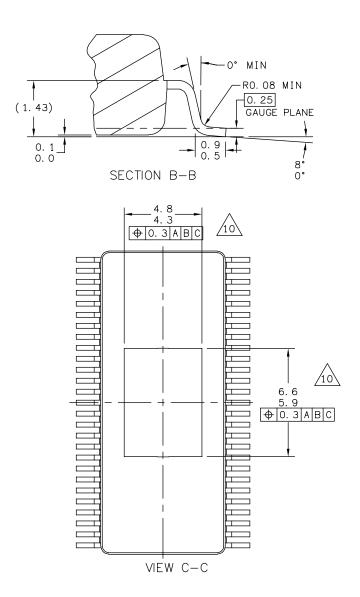

| Device        | Temperature<br>Range (T <sub>A</sub> ) | Package     |

|---------------|----------------------------------------|-------------|

| MCZ33800EK/R2 | -40°C to 125°C                         | 54 SOICW EP |

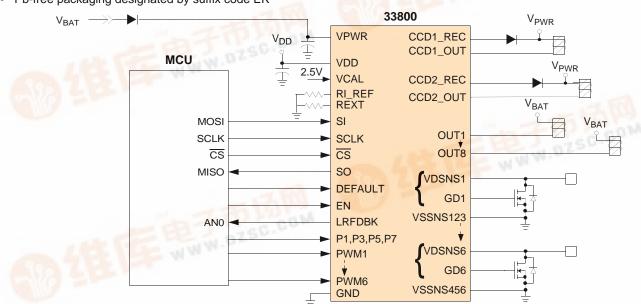

Figure 1. MC33800 Simplified Application Diagram

This document contains certain information on a new product. Specifications and information herein are subject to change without notice.

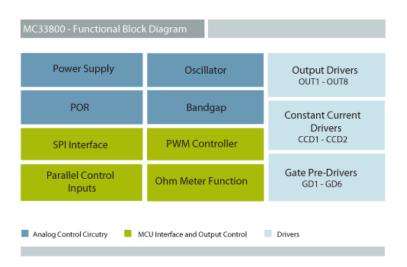

## INTERNAL BLOCK DIAGRAM

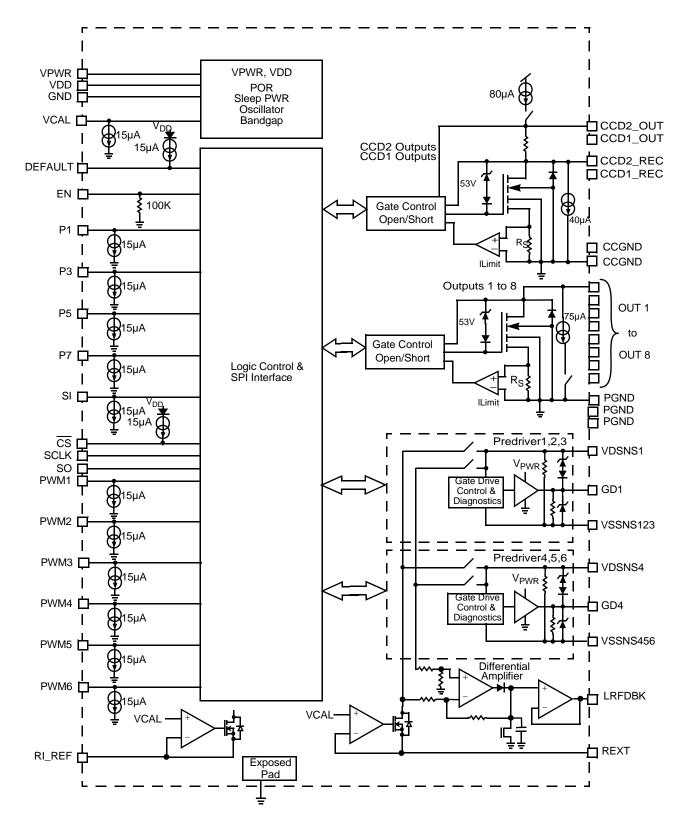

Figure 2. 33800 Simplified Internal Block Diagram

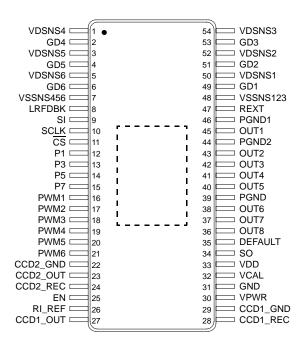

## **PIN CONNECTIONS**

#### Table 1. 33800 Pin Definitions

A functional description of each pin can be found in the Functional Pin Description section beginning on page 16.

| Pin Number             | Pin Name             | Pin Function | Formal Name                 | Definition                                                                                                                                                                                                 |

|------------------------|----------------------|--------------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 3, 5, 50,<br>52, 54 | VDSNS1-<br>VDSNS6    | Input        | Drain Voltage Sense         | The VDSNS pin is used to monitor the drain voltage of the external MOSFET.                                                                                                                                 |

| 2, 4, 6, 49,<br>51, 53 | GD1-GD6              | Output       | Gate Driver Output          | The GD pin provides gate drive for an external MOSFET                                                                                                                                                      |

| 7<br>48                | VSSNS456<br>VSSNS123 | Input        | Source Voltage Sense        | The VSSNS pins are used to monitor the source voltage of the external MOSFETS.                                                                                                                             |

| 8                      | LRFDBK               | Output       | Load Resistance<br>Feedback | The LRFDBK pin is an operational amplifier output.                                                                                                                                                         |

| 9                      | SI                   | Input        | Serial Input Data           | The SI input pin is used to receive serial data from the MCU. The serial input data is latched on the rising edge of SCLK, and the input data transitions on the falling edge of SCLK.                     |

| 10                     | SCLK                 | Input        | Serial Clock Input          | The SCLK input pin is used to clock in and out the serial data on the SI and SO Pins while being addressed by the $\overline{\text{CS}}$ .                                                                 |

| 11                     | CS                   | Input        | Chip Select                 | The Chip Select input pin is an active low signal sent by the MCU to indicate that the device is being addressed. This input requires CMOS logic levels and has an internal active pull up current source. |

| 12                     | P1                   | Input        | Input One                   | Input control of OSS output 1. When configured via the SPI, P1 input may be used to control OSS output 1 and output 2 in parallel.                                                                         |

| 13                     | P3                   | Input        | Input Three                 | Input control of OSS output 3. When configured via the SPI, P3 input may be used to control OSS output 3 and output 4 in parallel.                                                                         |

| 14                     | P5                   | Input        | Input Five                  | Input control of OSS output 5. When configured via the SPI, P5 input may be used to control OSS output 5 and output 6 in parallel.                                                                         |

## Table 1. 33800 Pin Definitions(continued)

A functional description of each pin can be found in the Functional Pin Description section beginning on page 16.

| Pin Number               | Pin Name  | Pin Function | Formal Name                                           | Definition                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------------|-----------|--------------|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15                       | P7        | Input        | Input Seven                                           | Input control of OSS output 7. When configured via the SPI, P7 input may be used to control OSS output 7 and output 8 in parallel.                                                                                                                                                                                                                                                                        |

| 16,17, 18, 19,<br>20, 21 | PWMX      | Input        | Pulse Width<br>Modulated Input                        | The PWMX input pin is used for direct parallel control of the GDX (Gate Drive Output X) predriver or as on/off control of the internal PWM controller. Control strategy is programmed via the SPI.                                                                                                                                                                                                        |

| 22                       | CCD2_GND  | Ground       | CCD2 Ground                                           | The CCD2_GND pin provides a dedicated ground for the CCD2 constant current controller                                                                                                                                                                                                                                                                                                                     |

| 23                       | CCD2_OUT  | Output       | Current Controlled<br>Driver 2 Output                 | The CCD2_OUT pin is connected to a series internal sense resistor and power MOSFET driver. The CCD2_OUT has a pull up and pull down current source and is used for fault threshold monitoring.                                                                                                                                                                                                            |

| 24                       | CCD2_REC  | Input        | Current Controlled<br>Driver 2 Recirculation<br>Input | The CCD2_REC pin provides a recirculation path for the load current.<br>The CCD2_REC pin is connected to the node between the internal sense<br>resistor and power MOSFET driver. The device uses the differential<br>voltage between CCD2_REC and CCD2_OUT to determine the load<br>solenoid current.                                                                                                    |

| 25                       | EN        | Input        | ENABLE                                                | The EN pin is an active high input.                                                                                                                                                                                                                                                                                                                                                                       |

| 26                       | RI_REF    | Output       | Resistor for Current<br>Reference                     | The RI_REF pin is used to generate a reference current. The reference is used in the regulation of the constant current controller. The constant current controller regulation current is inversely proportional to the reference current through the external resistor. A 39.2k $\Omega$ 1% resistor to ground will set the 1FF programmed current value of the CCD1 to 1075mA and the CCD2 to be 232mA. |

| 27                       | CCD1_OUT  | Output       | Current Controlled<br>Driver 1 Output                 | The CCD1_OUT pin is connected to a series internal sense resistor and power MOSFET driver. The CCD1_OUT has a pull up and pull down current source and is used for fault threshold monitoring.                                                                                                                                                                                                            |

| 28                       | CCD1_REC  | Input        | Current Controlled<br>Driver 1 Recirculation<br>Input | The CCD1_REC pin provides a recirculation path for the load current.<br>The CCD1_REC pin is connected to the node between the internal sense<br>resistor and power MOSFET driver. The device uses the differential<br>voltage between CCD1_REC and CCD1_OUT to determine the load<br>solenoid current.                                                                                                    |

| 29                       | CCD1_GND  | Ground       | CCD1 Ground                                           | The CCD1_GND pin provides a dedicated ground for the CCD1 constant current controller                                                                                                                                                                                                                                                                                                                     |

| 30                       | VPWR      | Power Input  | Analog Voltage Supply                                 | The VPWR pin provides power to all pre-driver, driver and output circuits and other internal functions such as the oscillator and SPI circuits.                                                                                                                                                                                                                                                           |

| 31                       | GND       | Ground       | Ground                                                | Analog ground for the internal control circuits of the IC. This ground should be used for decoupling of VDD and VPWR supply.                                                                                                                                                                                                                                                                              |

| 32                       | VCAL      | Input        | Voltage Calibrated<br>Input                           | VCAL input is a precision (2.5V, +8.0mV, -20mV over temperature) reference input, used in several internal circuits. A 1.0nF to 10nF decoupling capacitor is required on the VCAL input pin to ground.                                                                                                                                                                                                    |

| 33                       | VDD       | Power Input  | Digital Voltage Supply                                | The VDD pin supplies power to the Serial Output (SO) buffer along with the pull up current sources for the chip select (CS) and DEFAULT inputs.                                                                                                                                                                                                                                                           |

| 34                       | SO        | Output       | Serial Output Data                                    | The SO output pin is used to transmit serial data from the device to the MCU. The SO pin remains tri-stated until selected by the active low $\overline{CS}$ . The serial output data is available to be latched by the MCU on the rising edge of SCLK. The SO data transitions on falling edge of the SCLK.                                                                                              |

| 35                       | DEFAULT   | Input        | Default Mode Enable                                   | The DEFAULT pin is an active high input.                                                                                                                                                                                                                                                                                                                                                                  |

| 36-38, 40,<br>41-43, 45  | OUT1-OUT8 | Output       | OSS Output 1-8                                        | Octal Serial Switch (OSS) low side driver output 1-8.                                                                                                                                                                                                                                                                                                                                                     |

| Pin Number | Pin Name | Pin Function | Formal Name                    | Definition                                                                                                 |

|------------|----------|--------------|--------------------------------|------------------------------------------------------------------------------------------------------------|

| 39         | PGND3    | Ground       | OSS 3-8 Ground                 | This PGND pins provide a dedicated ground for the Octal Serial Switch (OSS) low side driver outputs 3 - 8. |

| 44         | PGND2    | Ground       | OSS 2 Ground                   | This PGND pin provides a dedicated ground for the Octal Serial Switch (OSS) low side driver output 2.      |

| 46         | PGND1    | Ground       | OSS 1 Ground                   | This PGND pin provides a dedicated ground for the Octal Serial Switch (OSS) low side driver output 1.      |

| 47         | REXT     | Output       | Resistor External<br>Reference | The REXT pin is used to generate a reference current.                                                      |

| _          | _        | Ground       | Exposed Pad Ground             | The package exposed pad provides thermal conductivity for the die and should be grounded to system ground. |

## Table 1. 33800 Pin Definitions(continued)

A functional description of each pin can be found in the Functional Pin Description section beginning on page 16.

## **ELECTRICAL CHARACTERISTICS**

## **MAXIMUM RATINGS**

#### Table 2. Maximum Ratings

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Ratings                                                   | Symbol              | Value                   | Unit            |

|-----------------------------------------------------------|---------------------|-------------------------|-----------------|

| ELECTRICAL RATINGS                                        |                     |                         |                 |

| Supply Voltage                                            |                     |                         | V <sub>DC</sub> |

| V <sub>PWR</sub>                                          | V <sub>PWR</sub>    | -1.5 to 45              |                 |

| V <sub>DD</sub>                                           | V <sub>DD</sub>     | -0.3 to 7.0             |                 |

| CS, SI, SO, SCLK, EN, DEFAULT, PWMx, P1, P3, P5, P7       | -                   | -0.3 to V <sub>DD</sub> | V <sub>DC</sub> |

| Predriver Drain Voltage (VDSNS1 to VDSNS6)                | V <sub>DSNS</sub>   | -0.3 to 60              | V <sub>DC</sub> |

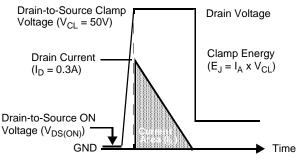

| OSS Output Clamp Energy (OUT3 to OUT8)(Single Pulse)      | E <sub>CLAMP</sub>  | 30                      | mJ              |

| $T_{Junction} = 150^{\circ}C, I_{OUT} = 0.45A$            |                     |                         |                 |

| OSS Output Clamp Energy (OUT1 & OUT2)(Single Pulse)       | E <sub>CLAMP</sub>  | 45                      | mJ              |

| $T_{Junction} = 150^{\circ}C, I_{OUT} = 0.45A$            |                     |                         |                 |

| CCD1 Output Clamp Energy (Single Pulse)                   | E <sub>CLAMP</sub>  | 75                      | mJ              |

| $T_{Junction} = 150^{\circ}C, I_{OUT} = 0.45A$            |                     |                         |                 |

| CCD2 Output Clamp Energy (Single Pulse)                   | E <sub>CLAMP</sub>  | 25                      | mJ              |

| $T_{Junction} = 150^{\circ}C$ , $I_{OUT} = 0.45A$         |                     |                         |                 |

| OSS Output Continuous Current (OUT1 to OUT8 Steady State) | I <sub>OSS_SS</sub> | 350                     | mA              |

| T <sub>Junction</sub> = 150°C                             |                     |                         |                 |

| CCD1 Output Clamp Energy (CCD1_REC OUTPUT)                | E <sub>CLAMP</sub>  | 75                      | mJ              |

| $T_{Junction} = 150^{\circ}C, I_{OUT} = 1.0 A$            |                     |                         |                 |

| Frequency of SPI Operation $(V_{DD} = 5.0V)^{(3)}$        | -                   | 4.0                     | MHz             |

| ESD Voltage <sup>(1)</sup>                                |                     |                         | V               |

| Human Body Model                                          | V <sub>ESD1</sub>   | ±2000                   |                 |

| Machine Model                                             | V <sub>ESD2</sub>   | ±200                    |                 |

#### THERMAL RATINGS

| Storage Temperature                           | T <sub>STG</sub> | -55 to 150 | °C |

|-----------------------------------------------|------------------|------------|----|

| Operating Case Temperature                    | т <sub>с</sub>   | -40 to 125 | °C |

| Operating Junction Temperature                | Τ <sub>J</sub>   | -40 to 150 | °C |

| Power Dissipation $(T_A = 25^{\circ}C)^{(2)}$ | P <sub>D</sub>   | 1.7        | W  |

#### THERMAL RESISTANCE

| Thermal Resistance                      |                       |     |      |

|-----------------------------------------|-----------------------|-----|------|

| Junction to Ambient                     | $R_{	extsf{	heta}JA}$ | 71  | °C/W |

| Between the Die and the Exposed Die Pad | $R_{	extsf{	heta}JC}$ | 1.2 |      |

Notes

1. ESD data available upon request. All pins tested individually. ESD1 testing is performed in accordance with the Human Body Model (AEC-Q100-002). and the Machine Model (AEC-Q100-003).

2. Maximum power dissipation at  $T_J$  =150°C junction temperature with no heat sink used.

3. This parameter is guaranteed by design but is not production tested.

## STATIC ELECTRICAL CHARACTERISTICS

#### **Table 3. Static Electrical Characteristics**

Characteristics noted under conditions  $3.0V \le V_{DD} \le 5.5V$ ,  $9.0V \le V_{PWR} \le 18V$ ,  $-40^{\circ}C \le T_A \le 125^{\circ}C$ , GND = 0V, unless otherwise noted. Typical values noted reflect the approximate parameter means at  $T_A = 25^{\circ}C$  under nominal conditions, unless otherwise noted.

| Characteristic                                                                                                                                          | Symbol                            | Min         | Тур            | Max            | Unit |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-------------|----------------|----------------|------|

| POWER INPUT (VPWR, VDD)                                                                                                                                 |                                   |             |                |                |      |

| Supply Voltage<br>Fully Operational                                                                                                                     | V <sub>PWR(FO)</sub>              | 5.0         | _              | 36             | V    |

| Supply Current<br>All Outputs Disabled (Normal & Default Mode)                                                                                          | I <sub>PWR(ON)</sub>              | _           | 10.0           | 14.0           | mA   |

| Sleep State Supply Current $V_{DD} \le 0.8 \text{ V}, \text{ V}_{PWR} = 18 \text{ V}$ $\text{EN} \le 0.8 \text{ V}, \text{ V}_{DD} = 5.5 \text{ V}$     | I <sub>PWR</sub> (SS)<br>Ivdd(SS) | -           | 10<br>2.0      | 30<br>5.0      | μΑ   |

| V <sub>PWR</sub> Over-voltage Shutdown Threshold Voltage <sup>(4)</sup>                                                                                 | V <sub>PWR(OV)</sub>              | 36.5        | 39             | 44             | V    |

| V <sub>PWR</sub> Over-voltage Shutdown Hysteresis Voltage                                                                                               | V <sub>PWR(OVHYS)</sub>           | 0.5         | 1.5            | 3.0            | V    |

| V <sub>PWR</sub> Under-voltage Shutdown Threshold Voltage <sup>(5)</sup>                                                                                | V <sub>PWR(UV)</sub>              | 3.0         | 4.0            | 4.4            | V    |

| V <sub>PWR</sub> Under-voltage Shutdown Hysteresis Voltage                                                                                              | V <sub>PWR(UVHYS)</sub>           | 100         | 200            | 650            | mV   |

| Logic Supply Voltage                                                                                                                                    | V <sub>DD</sub>                   | 3.0         | _              | 5.5            | V    |

| Logic Supply Current<br>Static Condition                                                                                                                | I <sub>DD</sub>                   | 180         | 300            | 525            | μΑ   |

| Logic Supply Under-voltage Shutdown Threshold Voltage <sup>(5)</sup>                                                                                    | V <sub>DD(UV)</sub>               | 0.8         | 2.5            | 2.8            | V    |

| Logic Supply Under-voltage Hysteresis                                                                                                                   | V <sub>DD(UVHYS)</sub>            | 100         | -              | 650            | mV   |

| Internally Generated V <sub>CAL</sub> <sup>(6)</sup>                                                                                                    | V <sub>BIAS</sub>                 | 2.2         | 2.5            | 2.8            | V    |

| CONSTANT CURRENT SOLENOID DRIVER OUTPUT (CCD1_OUT)                                                                                                      |                                   |             |                |                |      |

| Drain-to-Source ON Resistance<br>$T_J = 125^{\circ}C, V_{PWR} = 13V$<br>$T_J = 25^{\circ}C, V_{PWR} = 13V$<br>$T_J = -40^{\circ}C, V_{PWR} = 13V$       | RDS(ON)                           | -<br>-<br>- | _<br>0.25<br>_ | 0.60<br>_<br>_ | Ω    |

| Internal Current Sense Resistor<br>DAC Value = 000, $V_{CCD1REC}$ = 0.0V, $I_{CCD1OUT}$ = 100mA<br>R <sub>SENSE</sub> = $V_{CCD1OUT} / I_{CCD1OUT}$     | R <sub>SENSE</sub>                |             | 0.7            | 1.2            | Ω    |

| Current Regulation<br>DAC Value = 17C HEX +/- (3%)<br>DAC Value = 05F HEX +/- (15%)<br>Load Resistance = $5\Omega$ , Load Inductance = 10mH, Dither Off | I <sub>CCD1</sub>                 | 775<br>157  | 800<br>200     | 823<br>235     | mA   |

| Programmable Dither Frequency<br>Programmable from 50Hz to 500Hz in 50Hz Increments after<br>Calibration                                                | f <sub>DITHER</sub>               | -10         |                | 10             | %    |

Notes

4. Over-voltage thresholds minimum and maximum include hysteresis.

5. Under-voltage thresholds minimum and maximum include hysteresis.

6. Using the internally generated  $V_{CAL}$  increases all applicable parametric tables by +- 10%

Characteristics noted under conditions  $3.0V \le V_{DD} \le 5.5V$ ,  $9.0V \le V_{PWR} \le 18V$ ,  $-40^{\circ}C \le T_A \le 125^{\circ}C$ , GND = 0V, unless otherwise noted. Typical values noted reflect the approximate parameter means at  $T_A = 25^{\circ}C$  under nominal conditions, unless otherwise noted.

| Characteristic                                                                                                                                                                  | Symbol                    | Min         | Тур           | Max           | Unit |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|-------------|---------------|---------------|------|

| CONSTANT CURRENT SOLENOID DRIVER OUTPUT (CDD1_OUT)                                                                                                                              | (CONTINUED)               |             |               | 1             |      |

| Programmable Dither Amplitude Peak to Peak<br>Programmable from 0.0mA to 350mA in 50mA increments                                                                               | IDITHER                   | -10         |               | 10            | %    |

| CCD1 Fault Detection Voltage Threshold<br>Outputs Programmed OFF                                                                                                                | V <sub>OUT(FLTTH)</sub>   | 2.0         | 2.5           | 3.0           | V    |

| CCD1 Output Clamp Voltage<br>Outputs Programmed OFF                                                                                                                             | V <sub>OC</sub>           | 50          | 55            | 60            | V    |

| CCD1 Output Self Limiting Current                                                                                                                                               | I <sub>OUT (LIM)</sub>    | 1.5         | -             | 2.8           | А    |

| CCD1 Output Leakage Current<br>Pull-up enabled, Dither Off, CCD1OUT = $V_{OC}$ - 1.0V<br>Pull-up enabled, Dither Off, CCD1OUT = $V_{PWR}$ = 24V                                 | I <sub>CCD1</sub> (LKG)   | -           | _             | 8000<br>20    | μA   |

| CCD1 Pull Up Current<br>Pull-up enabled, DAC = 000, CCD1OUT = CCD1REC = 2.0V                                                                                                    | I <sub>CCD1(PULLUP)</sub> | -60         | -40           | -20           | μΑ   |

| CCD1 Pull Down Current<br>Pull-up disabled, DAC = 000, CCD1OUT = CCD1REC = 2.0V                                                                                                 | ICCD1(PULLDOWN)           | 20          | 40            | 60            | μΑ   |

| CONSTANT CURRENT SOLENOID DRIVER OUTPUT (CCD2_OUT)                                                                                                                              | )                         |             | 1             | 1             |      |

| Drain-to-Source ON Resistance<br>$T_J = 125^{\circ}C, V_{PWR} = 13V$<br>$T_J = 25^{\circ}C, V_{PWR} = 13V$<br>$T_J = -40^{\circ}C, V_{PWR} = 13V$                               | RDSON                     | -<br>-<br>- | _<br>1.0<br>_ | 2.0<br>_<br>_ | Ω    |

| Internal Current Sense Resistor<br>DAC Value = 000, V <sub>CCD2REC</sub> = 0V, I <sub>CCD2OUT</sub> = 100mA<br>R <sub>SENSE</sub> = V <sub>CCD2OUT</sub> / I <sub>CCD2OUT</sub> | R <sub>SENSE</sub>        |             | 3.5           | 5.0           | Ω    |

| Current Regulation<br>DAC Value = 17C HEX +/- (4%)<br>DAC Value = 05F HEX +/- (10%)<br>Load Resistance = $32\Omega$ , Load Inductance = 130mH, Dither Off                       | I <sub>CCD2</sub>         | 166<br>38.9 | 173<br>43.2   | 180<br>47.5   | mA   |

| Programmable Dither Frequency<br>Programmable from 50Hz to 500Hz in 50Hz Increments after<br>Calibration                                                                        | f <sub>DITHER</sub>       | -10         |               | 10            | %    |

| Programmable Dither Amplitude Peak to Peak<br>Programmable from 0.0mA to 90mA in 10.9mA increments                                                                              | IDITHER                   | -10         |               | 10            | %    |

| CCD2 Fault Detection Voltage Threshold<br>Outputs Programmed OFF                                                                                                                | V <sub>OUT(FLTTH)</sub>   | 2.0         | 2.5           | 3.0           | V    |

| CCD2 Output Clamp Voltage<br>Outputs Programmed OFF                                                                                                                             | V <sub>oc</sub>           | 50          | 55            | 60            | V    |

| CCD2 Output Leakage Current<br>Pull-up enabled, Dither Off, CCD2OUT = $V_{OC}$ - 1.0V<br>Pull-up enabled, Dither Off, CCD2OUT = $V_{PWR}$ = 24V                                 | I <sub>CCD2(LKG)</sub>    | -<br>-      | _             | 8000<br>20    | μA   |

| CCD2 Output Self Limiting Current                                                                                                                                               | I <sub>OUT(LIM)</sub>     | 0.5         | -             | 1.0           | A    |

Characteristics noted under conditions  $3.0V \le V_{DD} \le 5.5V$ ,  $9.0V \le V_{PWR} \le 18V$ ,  $-40^{\circ}C \le T_A \le 125^{\circ}C$ , GND = 0V, unless otherwise noted. Typical values noted reflect the approximate parameter means at  $T_A = 25^{\circ}C$  under nominal conditions, unless otherwise noted.

| Characteristic                                                                                                                                                                                                                                | Symbol                    | Min                   | Тур           | Мах                   | Unit |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|-----------------------|---------------|-----------------------|------|

| CONSTANT CURRENT SOLENOID DRIVER OUTPUT (CCD2_OUT)                                                                                                                                                                                            | (CONTINUED)               |                       |               | <u> </u>              |      |

| CCD2 Pull Up Current<br>Pull-up enabled, DAC = 000, CCD1OUT = CCD1REC = 2.0V                                                                                                                                                                  | I <sub>CCD2(PULLUP)</sub> | -60                   | -40           | -20                   | μA   |

| CCD2 Pull Down Current<br>Pull-up disabled, DAC = 000, CCD2OUT = CCD2REC = 2.0V                                                                                                                                                               | ICCD2(PULLDOWN)           | 20                    | 40            | 60                    | μA   |

| OCTAL SERIAL DRIVERS (OUT1 - 8)                                                                                                                                                                                                               | ·                         |                       |               |                       |      |

| Drain-to-Source ON Resistance <b>(OUT1 - 2)</b><br>$I_{OUT} = 0.350A, T_J = 125^{\circ}C, V_{PWR} = 13V$<br>$I_{OUT} = 0.350A, T_J = 25^{\circ}C, V_{PWR} = 13V$<br>$I_{OUT} = 0.350A, T_J = -40^{\circ}C, V_{PWR} = 13V$                     | R <sub>DS (ON)</sub>      | -<br>-<br>-           | _<br>0.7<br>_ | 1.4<br>_<br>_         | Ω    |

| Drain-to-Source ON Resistance <b>(OUT3 - 8)</b><br>$I_{OUT} = 0.350A, T_J = 125^{\circ}C, V_{PWR} = 13V$<br>$I_{OUT} = 0.350A, T_J = 25^{\circ}C, V_{PWR} = 13V$<br>$I_{OUT} = 0.350A, T_J = -40^{\circ}C, V_{PWR} = 13V$                     | R <sub>DS (ON)</sub>      | -<br>-<br>-           | -<br>1.0<br>- | 1.7<br>-<br>-         | Ω    |

| Output Self Limiting Current<br>Output 3 to Output 8<br>Output 1, Output 2                                                                                                                                                                    | I <sub>OUT</sub> (LIM)    | 1.0<br>4.0            | -             | 2.0<br>6.0            | A    |

| Output Fault Detection Voltage Threshold. <sup>(7)</sup><br>Outputs Programmed OFF                                                                                                                                                            | V <sub>OUT(FLTTH)</sub>   | 2.0                   | 2.5           | 3.0                   | V    |

| Output OFF Open Load Detection Current<br>V <sub>Drain</sub> = 18V, Outputs Programmed OFF                                                                                                                                                    | loco                      | 40                    | 75            | 100                   | μΑ   |

| Output Clamp Voltage Low Side Drive<br>I <sub>D</sub> = 20mA                                                                                                                                                                                  | V <sub>OC</sub>           | 50                    | 55            | 60                    | V    |

| Output Leakage Current<br>$V_{DD} = 5.0V, V_{Drain} = 24V$ , Open Load Detection Current Disabled<br>$V_{DD} = 5.0V, V_{Drain} = V_{OC} - 1.0V$ , Open Load Detection Current<br>Disabled<br>$V_{DD} = 0V, V_{Drain} = 24V$ , Device Disabled | I <sub>OUT(LKG)</sub>     | -<br>-<br>-           | -<br>-<br>-   | 20<br>3000<br>10      | μA   |

| Over-temperature Shutdown <sup>(8)</sup>                                                                                                                                                                                                      | TLim                      | 155                   | _             | 185                   | °C   |

| Over-temperature Shutdown Hysteresis <sup>(8)</sup>                                                                                                                                                                                           | TLim <sub>(HYS)</sub>     | 5.0                   | 10            | 15                    | °C   |

| SPI DIGITAL INTERFACE (SO, SI, CS, SCLK)                                                                                                                                                                                                      | •                         |                       |               | <u> </u>              |      |

| Input Logic High-voltage Thresholds <sup>(8)</sup>                                                                                                                                                                                            | V <sub>IH</sub>           | 0.7 x V <sub>DD</sub> | _             | V <sub>DD</sub> + 0.3 | V    |

| Input Logic Low-voltage Thresholds <sup>(8)</sup>                                                                                                                                                                                             | VIL                       | GND - 0.3             | _             | 0.2 x V <sub>DD</sub> | V    |

| Input Logic Voltage Hysteresis <sup>(8)</sup>                                                                                                                                                                                                 | V <sub>HYS</sub>          | 100                   | -             | 300                   | mV   |

| Input Logic Capacitance <sup>(8)</sup>                                                                                                                                                                                                        | C <sub>IN</sub>           | _                     | _             | 20                    | pF   |

|                                                                                                                                                                                                                                               | 1                         |                       |               |                       |      |

Notes

$V_{DD} = 0.0V$

Sleep Mode Input Logic Current<sup>(8)</sup>

7. Output fault detection thresholds with outputs programmed OFF. Output fault detect thresholds are the same for output open and shorts.

**I**LOGICSS

-10

\_

8. This parameter is guaranteed by design, however is not production tested.

μΑ

10

Characteristics noted under conditions  $3.0V \le V_{DD} \le 5.5V$ ,  $9.0V \le V_{PWR} \le 18V$ ,  $-40^{\circ}C \le T_A \le 125^{\circ}C$ , GND = 0V, unless otherwise noted. Typical values noted reflect the approximate parameter means at  $T_A = 25^{\circ}C$  under nominal conditions, unless otherwise noted.

| Characteristic                                                                                                                                 | Symbol                                      | Min                   | Тур        | Max        | Unit |

|------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|-----------------------|------------|------------|------|

| SPI DIGITAL INTERFACE (SO, SI, CS, SCLK) (CONTINUED)                                                                                           |                                             |                       |            | 1          |      |

| Sleep Mode EN and DEFAULT Input Current $V_{D D} = 0.0V, V_{EN} = 5.0V, V_{D E FA U LT} = 5.0V$                                                | ILOGICSS                                    | -10                   | _          | 10         | μΑ   |

| Normal Mode Input Logic Pull-down Current <sup>(9)</sup><br>0.8V to 5.0V                                                                       | ILOGICPD                                    | 5.0                   | 15         | 25         | μΑ   |

| Normal Mode DEFAULT Pull-up Current                                                                                                            | IDEFAULTPU                                  | -5.0                  | _          | -25        | μA   |

| SCLK, Tri-state SO Output<br>0.0V to 5.0V                                                                                                      | I <sub>SCLK,</sub> I <sub>TRISO</sub>       | -10                   | _          | 10         | μΑ   |

| $\overline{CS} \text{ Input Current}$ $\overline{CS} = V_{DD}$                                                                                 | I <sub>CS</sub>                             | -10                   | _          | 10         | μΑ   |

| $\overline{CS}$ Pull-up Current<br>$\overline{CS} = 0.0V$                                                                                      | ICSPU                                       | -5.0                  | _          | -30        | μA   |

| $\frac{\overline{\text{CS}}}{\overline{\text{CS}}} = 5.0\text{V}, \text{ V}_{\text{DD}} = 0.0\text{V}$                                         | I <sub>CS(LKG)</sub>                        | _                     | _          | 10         | μΑ   |

| SO High-state Output Voltage<br>I <sub>SOHIGH</sub> = -1.0mA                                                                                   | V <sub>SOHIGH</sub>                         | V <sub>DD</sub> - 0.4 | _          | _          | V    |

| SO Low-state Output Voltage<br>I <sub>SOLOW</sub> = 1.0mA                                                                                      | V <sub>SOLOW</sub>                          | _                     | _          | 0.4        | V    |

| EN Input Pull-down Current<br>EN = $V_{DD}$                                                                                                    | <sup>I</sup> ENPD                           | 10                    | 50         | 100        | μA   |

| PREDRIVER OUTPUT FUNCTION (GD1 - GD6)                                                                                                          |                                             |                       |            |            |      |

| Gate Drive Output Voltage<br>I <sub>GATEDRIVE</sub> = 100μA<br>I <sub>GATEDRIVE</sub> = - 100μA                                                | V <sub>GS(ON)</sub><br>V <sub>GS(OFF)</sub> | 5.0<br>-              | 7.0<br>0.2 | 9.0<br>0.5 | V    |

| Gate Drive Sink and Source Current                                                                                                             | IGATEDRIVE                                  | _                     | 2.0        | 5.0        | mA   |

| Sleep Mode Gate to Source Resistor                                                                                                             | R <sub>GS(PULLDOWN)</sub>                   | 65                    | 200        | 300        | KΩ   |

| Short Fault Detection Voltage Threshold<br>V <sub>DD</sub> = High, Outputs Programmed ON<br>Programmable from 0.5V to 3.0V in 0.5V increments. | V <sub>DS(FLTTH)</sub>                      | -20%                  |            | +20%       | V    |

| Open Fault Detection Voltage Threshold<br>V <sub>DD</sub> = High, Outputs Programmed OFF                                                       | V <sub>DS(FLTTH)</sub>                      | 2.0                   | 2.5        | 3.0        | V    |

Notes

9. Parameter applies to P1, P3, P5, P7, PWM1 to PWM6, SI and VCAL, and are guaranteed by design.

Characteristics noted under conditions  $3.0V \le V_{DD} \le 5.5V$ ,  $9.0V \le V_{PWR} \le 18V$ ,  $-40^{\circ}C \le T_A \le 125^{\circ}C$ , GND = 0V, unless otherwise noted. Typical values noted reflect the approximate parameter means at  $T_A = 25^{\circ}C$  under nominal conditions, unless otherwise noted.

| Characteristic                                                                       | Symbol                     | Min  | Тур | Max  | Unit |

|--------------------------------------------------------------------------------------|----------------------------|------|-----|------|------|

| PREDRIVER OUTPUT FUNCTION (GD1 - GD6) (CONTINUED)                                    |                            |      | 1   |      |      |

| Drain Sense Fault Detection Current                                                  | I <sub>DSNS(flt-sns)</sub> |      |     |      | μΑ   |

| Gate Drive Off, VDS = 18V                                                            |                            | 40   | 180 | 400  |      |

| Output Clamp Voltage                                                                 | V <sub>OC</sub>            |      |     |      | V    |

| Driver Command Off, $V_{GATE} = 2.0V$                                                |                            | 50   | 55  | 60   |      |

| Sleep Mode Drain Sense Leakage Current                                               | I <sub>DSNS(LKG)</sub>     |      |     |      | μA   |

| $V_{DD} = 0.0V, V_{DSNS} = 24V,$                                                     |                            | -    | -   | 25   |      |

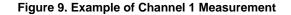

| Load Resistance Feedback Accuracy Sample and Hold After 150ms                        | LR <sub>FBCKACC</sub>      | -10% | 2.6 | +10% | V    |

| $R_{EXT}$ = 24ohm, $R_{LOAD}$ = 10ohm, $LR_{FDBK}$ = VCAL*2.5*( $R_{LOAD}/R_{EXT}$ ) |                            |      |     |      |      |

| Load Resistance Feedback Output Voltage                                              | LR <sub>FBCKMax</sub>      |      |     | 6.0  | V    |

| $(V_{DSNS1} - V_{DSNS2}) \ge 10V$ , PWM Diagnostics Select = 0001                    |                            |      |     |      |      |

## **DYNAMIC ELECTRICAL CHARACTERISTICS**

#### **Table 4. Dynamic Electrical Characteristics**

Characteristics noted under conditions  $3.0V \le V_{DD} \le 5.5V$ ,  $9.0V \le V_{PWR} \le 18V$ ,  $-40^{\circ}C \le T_A \le 125^{\circ}C$ , GND = 0V, unless otherwise noted. Typical values noted reflect the approximate parameter means at  $T_A = 25^{\circ}C$  under nominal conditions, unless otherwise noted.

| Characteristic                                                                                               | Symbol                    | Min  | Тур  | Мах  | Unit |

|--------------------------------------------------------------------------------------------------------------|---------------------------|------|------|------|------|

| CONSTANT CURRENT SOLENOID DRIVER OUTPUT (CCD1_OUT)                                                           |                           | 4    |      |      |      |

| On State Open Load Detect Timer <sup>(10)</sup>                                                              |                           |      |      |      | ms   |

| Fault is detected with driver on, timer expired                                                              | t <sub>ONOPENTIMER</sub>  | 6.0  | 12   | 24   |      |

| Off State Open Load Detect Timer <sup>(10)</sup>                                                             |                           |      |      |      | μs   |

| Fault detected with driver off & voltage threshold not achieved (Driver off timer)                           | t <sub>OFFOPENTIMER</sub> | 30   | 60   | 90   |      |

| On State Shorted Load Detect Timer <sup>(10)</sup>                                                           | tONSHORTTIMER             |      |      |      | μs   |

| Fault is detected with driver switching and drain voltage remains greater than threshold for specified time. |                           | 30   | 60   | 90   |      |

| Short Retry Time <sup>(10)</sup>                                                                             | t <sub>RETRY</sub>        | 10   | 14   | 24   | ms   |

| Output Slew Rate                                                                                             |                           |      |      |      |      |

| $V_{BAT}$ = 14V, Measured from 4.0V to 10.0V                                                                 | t <sub>SR(RISE)</sub>     | 2.0  | 3.0  | 4.0  | V/µs |

| V <sub>BAT</sub> = 14V, Measured from 10.0V to 4.0V                                                          | t <sub>SR(FALL)</sub>     | -2.0 | -3.0 | -4.0 |      |

| Driver On Time Blanking Period <sup>(10)</sup>                                                               | t <sub>BP(OFF)</sub>      |      | 7.0  | 10   | μs   |

| Driver Off Time Blanking Period <sup>(10)</sup>                                                              | t <sub>BP(ON)</sub>       |      | 7.0  | 10   | μs   |

| CONSTANT CURRENT SOLENOID DRIVER OUTPUT (CCD2_OUT)                                                           |                           |      |      |      |      |

| On State Open Load Detect Timer <sup>(10)</sup>                                                              |                           |      |      |      | ms   |

| Fault is detected with driver on, timer expires (Driver on timer)                                            | t <sub>ONOPENTIMER</sub>  | 6.0  | 12   | 24   |      |

| Off State Open Load Detect Timer <sup>(10)</sup>                                                             |                           |      |      |      | μs   |

| Fault is detected with driver off and voltage threshold is not achieved. (Driver off timer)                  |                           | 30   | 60   | 90   |      |

| On State Shorted Load Detect Timer <sup>(10)</sup>                                                           | tONSHORTTIMER             |      |      |      | μs   |

| Fault is detected with driver switching and drain voltage remains greater than threshold for specified time. |                           | 30   | 60   | 90   |      |

| Short Retry Time <sup>(10)</sup>                                                                             | t <sub>RETRY</sub>        | 10   | 14   | 24   | ms   |

| Output Slew Rate                                                                                             |                           |      |      |      | V/µs |

| $V_{BAT}$ = 14V, Measured from 4.0V to 10.0V                                                                 | t <sub>SR(RISE)</sub>     | 1.5  | -    | 4.0  |      |

| V <sub>BAT</sub> = 14V, Measured from 10.0V to 4.0V                                                          | t <sub>SR(FALL)</sub>     | -1.5 | -    | -4.0 |      |

| CCD2 DAC Update Rate <sup>(10)</sup>                                                                         |                           |      |      |      | ms   |

| Response time from present current level to new programmed level                                             | t <sub>RESPONSE</sub>     | 1.0  |      |      |      |

| Driver On Time Blanking Period <sup>(10)</sup>                                                               | t <sub>BP(ON)</sub>       |      | 3.0  | 4.3  | μs   |

| Driver Off Time Blanking Period <sup>(10)</sup>                                                              | t <sub>BP(OFF)</sub>      |      | 12   | 17.2 | μs   |

| OCTAL SERIAL DRIVERS (OUT1 - OUT8)                                                                           |                           |      |      |      |      |

| Output On Current Limit Fault Filter Timer <sup>(10)</sup>                                                   | t <sub>CL</sub>           | 30   | 50   | 90   | μs   |

| Output Refresh Timer <sup>(10)</sup>                                                                         | t <sub>REF</sub>          | 5.0  | 10   | 15   | ms   |

| Output On Short Circuit Fault Filter Timer <sup>(10)</sup>                                                   | t <sub>SC</sub>           | 400  | 500  | 650  | μs   |

|                                                                                                              |                           | 1    | 1    | 1    | 1    |

Notes

10. Assumes oscillator has been calibrated using SPI Calibrate Command.

#### **Table 4. Dynamic Electrical Characteristics**

Characteristics noted under conditions  $3.0V \le V_{DD} \le 5.5V$ ,  $9.0V \le V_{PWR} \le 18V$ ,  $-40^{\circ}C \le T_A \le 125^{\circ}C$ , GND = 0V, unless otherwise noted. Typical values noted reflect the approximate parameter means at  $T_A = 25^{\circ}C$  under nominal conditions, unless otherwise noted.

| Characteristic                                                                | Symbol                   | Min | Тур | Max | Unit |

|-------------------------------------------------------------------------------|--------------------------|-----|-----|-----|------|

| OCTAL SERIAL DRIVERS (OUT1 - OUT8) (CONTINUED)                                |                          | ł   |     | •   |      |

| Output Off Open Circuit Fault Filter Timer <sup>(11)</sup>                    | t <sub>OC</sub>          | 400 | 500 | 650 | μs   |

| Output Slew Rate                                                              |                          |     |     |     | V/µs |

| $R_{LOAD} = 51\Omega$                                                         | t <sub>SR(RISE)</sub>    | 1.0 | 5.0 | 10  |      |

| $R_{LOAD} = 51\Omega$                                                         | t <sub>SR(FALL)</sub>    | 1.0 | 5.0 | 10  |      |

| P1 Input Propagation Delay                                                    |                          |     |     |     | μs   |

| Input @ 50% $V_{DD}$ to Output voltage 10% of final value                     | t <sub>(RISEDELAY)</sub> |     |     | 6.0 |      |

| Input $@~50\%~V_{DD}$ to Output voltage 90% of initial value                  | t(FALLDELAY)             |     |     | 6.0 |      |

| P3, P5, P7 Input Propagation Delay                                            |                          |     |     |     | μs   |

| Input @ 50% $V_{DD}$ to Output voltage 10% of final value                     | t <sub>(RISEDELAY)</sub> |     |     | 5.0 |      |

| Input @ 50% $V_{DD}$ to Output voltage 90% of initial value                   | t <sub>(FALLDELAY)</sub> |     |     | 5.0 |      |

| DSCILLATOR AND TIMER ACCURACY                                                 |                          |     |     |     |      |

| Calibrated Timer Accuracy <sup>(11)</sup>                                     | t <sub>TIMER</sub>       | -   | -   | ±10 | %    |

| Un-calibrated Timer Accuracy                                                  | t <sub>TIMER</sub>       | -   | -   | ±80 | %    |

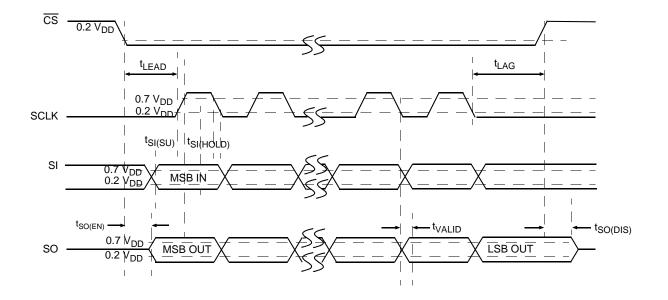

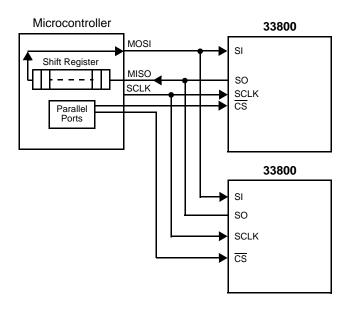

| SPI DIGITAL INTERFACE TIMING (SO, SI, CS, SCLK) <sup>(12)</sup>               |                          |     |     |     |      |

| Required Low State Duration on V <sub>PWR</sub> for Reset <sup>(13)</sup>     | t <sub>RESET</sub>       |     |     | İ   | μS   |

| $V_{PWR} \le 0.2V$                                                            |                          | 1.0 | -   | -   |      |

| Falling Edge of CS to Rising Edge of SCLK                                     | t <sub>LEAD</sub>        |     |     |     | ns   |

| Required Setup Time                                                           |                          | 100 | -   | -   |      |

| Falling Edge of SCLK to Rising Edge of CS                                     | t <sub>LAG</sub>         |     |     |     | ns   |

| Required Setup Time                                                           |                          | 50  | -   | -   |      |

| SI to Rising Edge of SCLK                                                     | t <sub>SI(SU)</sub>      |     |     |     | ns   |

| Required Setup Time                                                           |                          | 16  | -   | -   |      |

| Rising Edge of SCLK to SI                                                     | t <sub>SI(HOLD)</sub>    |     |     |     | ns   |

| Required Hold Time                                                            |                          | 20  | -   | -   |      |

| SI, CS, SCLK Signal Rise Time <sup>(14)</sup>                                 | t <sub>R(SI)</sub>       | -   | 5.0 | -   | ns   |

| SI, CS, SCLK Signal Fall Time <sup>(14)</sup>                                 | t <sub>F(SI)</sub>       | -   | 5.0 | -   | ns   |

| Time from Falling Edge of $\overline{CS}$ to SO Low-impedance <sup>(15)</sup> | t <sub>SO(EN)</sub>      | -   | -   | 150 | ns   |

| Time from Rising Edge of $\overline{CS}$ to SO High-impedance <sup>(16)</sup> | t <sub>SO(DIS)</sub>     | -   | -   | 150 | ns   |

| Time from Falling Edge of SCLK to SO Data Valid <sup>(17)</sup>               | t <sub>VALID</sub>       | -   | 25  | 150 | ns   |

| Sequential Transfer Rate                                                      | t <sub>STR</sub>         |     |     | 1.0 | μs   |

| Time required between data transfers                                          |                          |     |     |     |      |

Notes

11. Assumes oscillator has been calibrated using SPI Calibrate Command

12. These parameters are guaranteed by design. Production test equipment uses 1MHz, 5.0V SPI interface.

13. This parameter is guaranteed by design, however it is not production tested.

14. Rise and Fall time of incoming SI, CS, and SCLK signals for design consideration to prevent the occurrence of double pulsing.

15. Time required for valid output status data to be available on SO pin.

16. Time required for output states data to be terminated at SO pin.

17. Time required to obtain valid data out from SO following the fall of SCLK with 200pF load.

## **Table 4. Dynamic Electrical Characteristics**

Characteristics noted under conditions  $3.0V \le V_{DD} \le 5.5V$ ,  $9.0V \le V_{PWR} \le 18V$ ,  $-40^{\circ}C \le T_A \le 125^{\circ}C$ , GND = 0V, unless otherwise noted. Typical values noted reflect the approximate parameter means at  $T_A = 25^{\circ}C$  under nominal conditions, unless otherwise noted.

| Characteristic                                                                                                                                                    | Symbol                   | Min  | Тур | Max  | Unit |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|------|-----|------|------|

| PREDRIVER OUTPUT FUNCTION (GD1 - GD6)                                                                                                                             | •                        |      |     |      |      |

| Open Fault Detection Filter Timer <sup>(18)</sup><br>V <sub>DD</sub> = High, Outputs Programmed OFF                                                               | V <sub>DS(FLTTH)</sub>   | 100  | 128 | 400  | μs   |

| Short Fault Detection Filter Timer <sup>(18)</sup><br>V <sub>DD</sub> = High, Outputs Programmed ON<br>Programmable from 30µs to 960µs in replicating increments. | <sup>t</sup> DS(FLTTMR)  | -10% |     | +10% | μs   |

| Gate Drive Rise Slew Rate<br>Cload = 1.0nF, VGS from 0.5 to 5.0V                                                                                                  | t <sub>GDSR</sub> (RISE) | _    | 1.7 | _    | V/µs |

| Gate Drive Fall Slew Rate<br>Cload = 1.0nF, VGS from 5.0 to 0.5V                                                                                                  | t <sub>GDSR</sub> (FALL) | _    | 1.7 | _    | V/µs |

| PWM1 to PWM6 Input Propagation Delay<br>Measured from PWM input at 4.5V and GDx output at 0.5V.                                                                   | t <sub>PWMDELAY</sub>    | 20   |     | 300  | ns   |

| Load Resistance Feedback Output Rise Slew Rate<br>$C_{LOAD} = 40 pF$                                                                                              | t <sub>LRSR(RISE)</sub>  | 0.5  | _   | 2.0  | V/µs |

| Load Resistance Feedback Output Fall Slew Rate<br>$C_{LOAD} = 40 pF$                                                                                              | t <sub>LRSR(FALL)</sub>  | 0.5  | _   | 2.0  | V/µs |

| Load Resistance Sample Duration <sup>(18)</sup>                                                                                                                   | t <sub>LOADSAMPLE</sub>  |      |     | 200  | μs   |

| Load Resistance Feedback Valid $^{(18)}$<br>Time from rising edge of $\overline{CS}$ to Load Resistance measurement valid                                         | <sup>t</sup> FDBKVALID   |      |     | 400  | us   |

Notes

18. Assumes oscillator has been calibrated using SPI Calibrate Command.

## **TIMING DIAGRAMS**

Figure 4. SPI Timing Characteristics

# FUNCTIONAL DESCRIPTION

## FUNCTIONAL PIN DESCRIPTION

## ANALOG VOLTAGE SUPPLY (VPWR)

The VPWR pin is battery input to the 33800 IC. The VPWR pin requires external reverse battery and transient protection. Maximum input voltage on VPWR is 45V. All IC analog current and internal logic current is provided from the VPWR pin. With  $V_{DD}$  and EN applied to the IC, the application of  $V_{PWR}$  will perform a Power-ON Reset (**POR**).

## **DIGITAL VOLTAGE SUPPLY (VDD)**

The VDD input pin is used to determine communication logic levels between the microprocessor and the 33800 device. Current from  $V_{DD}$  is used to drive SO output and pull-up current for  $\overline{CS}$ .  $V_{DD}$  must be applied for Normal Mode operation. Removing  $V_{DD}$  from the IC will place the device in Sleep Mode. Power-ON Reset will be performed with the application of  $V_{DD}$  supply.

## **GROUND (GND)**

The GND pin provides a low current analog ground for the IC. The VPWR and VDD supplies are both referenced to the GND pin. GND pin should be used for decoupling both supplies.

# CONSTANT CURRENT DRIVER GROUND (CCDX\_GND)

The Constant Current Driver Ground (CCDX\_GND) pins provide dedicated grounds for the Constant Current output drivers. Both CCDX\_GND1 and CCDX\_GND2 grounds are isolated from the other grounds of the IC.

## GROUND (PGND1 - 3, CCD1\_GND, CCD2\_GND)

There are three PGND pins associated with the OSS drivers. OUT1 driver and OUT2 driver have dedicated PGND1 & PGND2 pins. Drivers OUT3 through Driver OUT8 share one PGND3 pin. In general all ground pins must be connected together and terminated to ground on the circuit board.

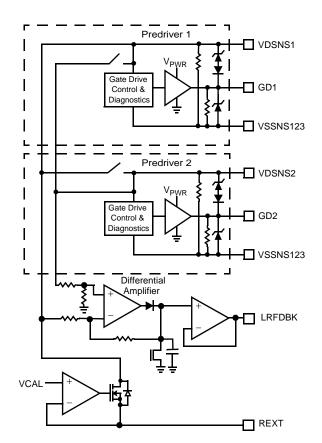

# SOURCE VOLTAGE SENSE (VSSNS123, VSSNS456)

The Source Sense Ground pins (VSSNS123, VSSNS456) provide dedicated grounds for the hex MOSFET pre-drivers. The pins are used by the IC to monitor the drain to source voltage of the external MOSFET. This pin must be connected to the source of the external MOSFET and system ground. VSSNS123 and VSSNS456 ground pins are isolated from other internal IC grounds.

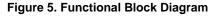

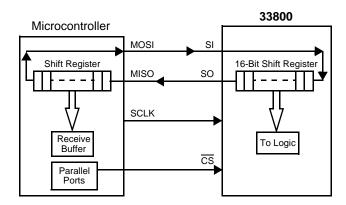

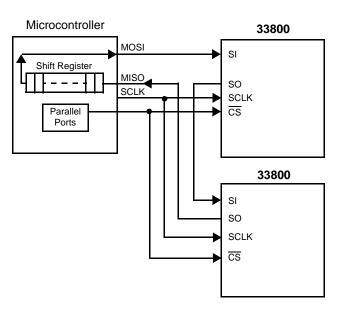

## SERIAL CLOCK INPUT (SCLK)

The system clock (SCLK) pin clocks the internal shift register of the 33800. The SI data is latched into the input shift register on the rising edge of SCLK signal. The SO pin shifts status bits out on the falling edge of SCLK. The SO data is available for the MCU to read on the rising edge of SCLK. With CS in a logic high state, signals on the SCLK and SI pins will be ignored and the SO pin is tri-state.

# CHIP SELECT (CS)

The system MCU selects the 33800 to receive communication using the chip select  $(\overline{CS})$  pin. With the  $\overline{CS}$  in a logic low state, command words may be sent to the 33800 via the serial input (SI) pin, and status information is received by the MCU via the serial output (SO) pin. The falling edge of  $\overline{CS}$  enables the SO output and transfers status information into the SO buffer.

Rising edge of the  $\overline{CS}$  initiates the following operation:

- 1. Disables the SO driver (high-impedance)

- 2. Activates the received command word, allowing the 33800 to activate/deactivate output drivers.

To avoid any spurious data, it is essential the high-to-low and low-to-high transitions of the  $\overline{CS}$  signal occur only when SCLK is in a logic low state. Internal to the 33800 device is an active pull-up to VDD on  $\overline{CS}$ . In cases were voltage exists on  $\overline{CS}$  without the application of V<sub>DD</sub>, no current will flow from  $\overline{CS}$  to the VDD pin.

#### SERIAL INPUT DATA (SI)

The SI pin is used for serial instruction data input. SI information is latched into the input register on the rising edge of SCLK. A logic high state present on SI will program a *one* in the command word on the rising edge of the CS signal. To program a complete word, 16-bits of information must be entered into the device.

#### **SERIAL OUTPUT DATA (SO)**

The SO pin is the output from the shift register. The SO pin remains tri-stated until the  $\overline{CS}$  pin transitions to a logic low state. All normal operating drivers are reported as zero, all faulted drivers are reported as one. The negative transition of  $\overline{CS}$  enables the SO driver.

The SI/SO shifting of the data follows a first-in-first-out protocol, with both input and output words transferring the most significant bit (MSB) first.

## ENABLE (EN)

The ENABLE pin is an active high digital input pin used to enable the device. With the EN pin low the device is in Sleep Mode. With the EN pin high, the device is in Normal Mode ( $V_{DD}$  and  $V_{PWR}$  applied). Exit from Sleep Mode initiates a

Power On Reset (POR). All internal registers will be placed in the reset state. The device has an Internal 100 k $\Omega$  resistor pull down on the ENABLE pin.

## PULSE WIDTH MODULATION (PWM)

The PWM pins are control input pins for the MOSFET predrivers. The PWM pins provide parallel control and can be programmed for an OR function with the SPI bit or an AND function with the SPI bit (See <u>Table 12</u>, on page 25 for SPI message detail). Each PWM input pin has an internal  $15\mu$ A pull down current source. The current sources are active when the device is in Normal Mode.

## DRAIN VOLTAGE SENSE (VDSNSX)

The VDSNSx pin has multiple functions for control and diagnostics of the external MOSFET:

- By monitoring the drain voltage of the external device, short circuits and open circuits are detected. The filter timer and threshold voltage are easily programmed through SPI (see <u>Table 10, on page 23</u> and <u>Table 11, on page 24</u> for SPI messages).

- 2. The VDSNSx pins are use to determine the external load resistance. Further information is provided in the Device Operation section of this specification.

- 3. The VDSNSx pins provide a drain to gate clamp for fast turn off of inductive loads and MOSFET protection.

#### GATE DRIVER OUTPUTS (GDX)

The GDX pins are the gate drive outputs for an external MOSFETS. Internal to the device is a Gate to Source resistor designed to hold the external MOSFET in the OFF state while the device is in POR.

## **INPUTS (P1, P3, P5, P7)**

The input pins for octal serial switch outputs 1,3,5,7. Each input control pin has an internal pull down current source. Two outputs may be controlled in parallel using the PX pins (See Functional Device Operation on page 25).

## **VOLTAGE CALIBRATED INPUT (VCAL)**

The Voltage calibrated input (VCAL) provides the IC with a reference voltage for analog circuits. VCAL (EXT or INT) must be applied for the CCD1 and CCD2 constant current controllers and Load Resistance measurement function to operate. For applications where measurements are not critical, the VCAL pin may grounded and an internally generated reference will be used. Using the internally generated reference will add  $\pm 10\%$  to all tolerances in the parametric table.

## LOAD RESISTANCE FEEDBACK (LRFDBK)

The LRFDBK pin is an operational amplifier output. The amplifier output voltage is proportional to the load resistance for the selected channel. The channel is selected via the SPI.

## DEFAULT

The DEFAULT input controls the operation of each driver to a Default Mode. The DEFAULT input must be logic 0 for full function of all output drivers. For more information on the DEFAULT operation (<u>See Functional Device Operation on</u> <u>page 19</u>).

With the DEFAULT pin HIGH, the device is placed in Default Mode. The DEFAULT pin is pulled up to the VDD supply through an active pull up current source. In Default Mode the device operates in the following manner:

- 1. OSS outputs are disabled.

- 2. CCD1 and CCD2 outputs are disabled.

3. SPI ON/OFF control of GATE DRIVE (GD1 to GD6) outputs and on board PWM controllers are disabled. PWMx input control is enabled.

In the Default Mode the device retains all register information and output status information. Normal operation will resume when the DEFAULT pin transitions low again and the device will operate as programmed prior to Default Mode.

## **RESISTOR EXTERNAL REFERENCE (REXT)**

The reference current is used in the equation to calculate the load resistance of the PWM outputs. The load resistance measurement current is inversely proportional to REXT current. The resistor value may be changed to adjust the load measurement current. A  $24\Omega$  resistor to ground sets the LRFDBK output to 260mV/ $\Omega$ .

#### **EXPOSED PAD**

The silicon die is epoxy attached to the top side of the pad. Although the device does not use the pad for electrical conduction, the bottom side exposed pad of the package should be grounded.

## FUNCTIONAL INTERNAL BLOCK DESCRIPTION

## ANALOG CONTROL CIRCUITRY

The 33800 is designed to operate from 5.0 to 36V on the VPWR pin. The VPWR pin supplies power to all internal regulators, analog and logic circuit blocks. The VDD supply is used for setting communication threshold levels and supplying power to the SO driver. This IC architecture provides low quiescent current Sleep Modes. Applying VPWR to the device will cause a Power On Reset (POR). The on-chip oscillator supports the selectable PWM frequency and duty cycle. The on-chip voltage regulator and bandgap supply the required voltages to the internal circuitry.

## MCU INTERFACE AND OUTPUT CONTROL

The device is designed with six flexible PWM gate driver outputs. Each driver may be controlled directly from the MCU and may be programmed through the SPI for a specific frequency and duty cycle.

#### LOW-SIDE DRIVERS: OUT1 - OUT8

The 33800 provides flexible control of 8 low side driver outputs. Outputs 1 and 2 are specifically designed with higher

current limits to accommodate lamp inrush current. The device allows for parallel control of the outputs or SPI control through the use of several input command words.

## CONSTANT CURRENT LOW SIDE DRIVERS: CCD1 AND CCD2

The CCD1/CCD2 constant current controllers are switching hysteretic current controllers with a superimposed dither. The controllers are designed to provide a programmable constant current through a solenoid valve. Fluid flow is controlled by the amount of current run through the driven solenoid valve.

#### GATE PRE-DRIVERS: GD1 - GD6

The GD1 – GD6 pins are the gate drive outputs for external MOSFETS. They can be PWM'ed with speed and duty cycle choices per the SPI command registers. Internal to the device is a Gate to Source resistor designed to hold the external MOSFET in the OFF state while the device is in POR.

# FUNCTIONAL DEVICE OPERATION

## **OPERATIONAL MODES**

#### **POWER SUPPLY**

The 33800 is designed to operate from 5.0 to 36V on the VPWR pin. The VPWR pin supplies power to all internal regulators, analog and logic circuit blocks. The  $V_{DD}$  supply is used for setting communication threshold levels and supplying power to the SO driver. This IC architecture provides flexible microprocessor interfacing with low quiescent current Sleep Modes.

#### **POWER-ON RESET (POR)**

Applying  $V_{PWR}$ ,  $V_{DD}$  and EN to the device will cause a Power On Reset (POR) and place the device in Normal or Default Mode.

#### Table 5. Modes of Operation

| V <sub>PWR</sub> | V <sub>DD</sub> | ENable | DEFAULT | MODE         |

|------------------|-----------------|--------|---------|--------------|

| L                | Х               | Х      | х       | Power<br>Off |

| Н                | L               | Х      | Х       | SLEEP        |

| Н                | Н               | L      | Х       | SLEEP        |

| Н                | Н               | Н      | L       | NORMAL       |

| Н                | Н               | Н      | Н       | DEFAULT      |

Command register settings from Power-ON Reset (POR) via  $V_{PWR}$  or  $V_{DD}$  are as follows:

- · All Outputs Off

- Inputs Enabled and OR'd with SPI Bit.

- PWM Frequency and Duty Cycle Control Disabled.

- OSS Open Load Detect Current Enabled.

- OSS Outputs with Individual Control.

- Control Inputs P1,P3,P5,P7 Enabled and OR'd with the SPI Bit.

- CCD1 Output Off, Diagnostic Pull-up Enabled, DAC = 0.

- CCD2 Output Off, Diagnostic Pull-up Enabled, DAC = 0.

Power On Reset circuit incorporates a 0.5 $\mu$ s timer to prevent high frequency transients from causing a POR. During the low-voltage condition, internal logic states are maintained. To guarantee a POR from V<sub>PWR</sub>, the VPWR pin must be less than 0.2V for greater than 1.0 $\mu$ s.

#### MODES OF OPERATION

The 33800 has three operating modes, Normal, Sleep and Default Mode. A discussion on Normal Mode follows.

#### NORMAL MODE

Normal Mode allows full functional control of the device. Transferring from Sleep Mode to Normal Mode performs a POR and resets all internal registers to the POR state. When entering Normal Mode from Default Mode, no POR is performed and register states are maintained.

Features programmed in Normal Mode are listed below. Further explanation of each feature is provided in subsequent paragraphs.

- Programmable PWM Frequency & Duty Cycle

- Programmable PWM Drain Fault Threshold

- CCD2 Constant Current Dither Frequency and Amplitude

- CCD2 DAC Programming

- CCD1 Constant Current Dither Frequency and Amplitude

- CCD1 DAC Programming

- On/Off OSS Open Load Detect Current

- Calibration of Timers (Calibration Command)

- Reset (Reset Command)

- No Operation (NO\_OP Command)

#### DEFAULT MODE

The Default Mode allows the user to disable all outputs except the PWM pre-driver. In Default Mode the PWM predriver outputs may only be controlled via the PWM input pins. All register control bits and fault bits are maintained in Default Mode, however control for the pre-driver is accomplished through the PWM pins only.

With the DEFAULT pin HIGH, the device is placed in Default Mode. When exiting Default Mode, output control reverts to the internal register settings.

In Default Mode the device operates with the following parameters.

- 1. OSS outputs are disabled.

- 2. CCD1 and CCD2 outputs are disabled.

3. SPI ON/OFF control of GATE DRIVE (GD1 to GD6) outputs is disabled. PWMx input control is enabled. The device will operate as programmed prior to Default Mode.

In Default Mode the device retains all register information and output status information. Normal operation will resume when the DEFAULT pin transitions low again.

#### SLEEP MODE