# **4-STAGE PRESETTABLE** RIPPLE COUNTERS

The SN54/74LS196 decade counter is partitioned into divide-by-two and divide-by-five sections which can be combined to count either in BCD (8, 4, 2, 1) sequence or in a bi-quinary mode producing a 50% duty cycle output. The SN54/74LS197 contains divide-by-two and divide-by-eight sections which can be combined to form a modulo-16 binary counter. Low Power Schottky technology is used to achieve typical count rates of 70 MHz and power dissipation of only 80 mW.

Both circuit types have a Master Reset (MR) input which overrides all other inputs and asynchronously forces all outputs LOW. A Parallel Load input (PL) overrides clocked operations and asynchronously loads the data on the Parallel Data inputs (Pn) into the flip-flops. This preset feature makes the circuits usable as programmable counters. The circuits can also be used as 4-bit latches, loading data from the Parallel Data inputs when PL is LOW and storing the data when PL is HIGH.

- Low Power Consumption Typically 80 mW

- High Counting Rates Typically 70 MHz

- Choice of Counting Modes BCD, Bi-Quinary, Binary

- Asynchronous Presettable

- Asynchronous Master Reset

- Easy Multistage Cascading

- Input Clamp Diodes Limit High Speed Termination Effects

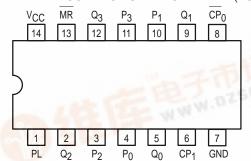

#### **CONNECTION DIAGRAM DIP (TOP VIEW)**

NOTE: The Flatpak version has the same pinouts (Connection Diagram) as the Dual In-Line Package. SN54/74LS196 SN54/74LS197

4-STAGE PRESETTABLE RIPPLE COUNTERS

LOW POWER SCHOTTKY

LOGIC SYMBOL 4 10 3 11 P<sub>0</sub> P<sub>1</sub> P<sub>2</sub> P<sub>3</sub> CP<sub>0</sub> CP<sub>1 MR</sub> Q<sub>0</sub> Q<sub>1</sub> Q<sub>2</sub> Q<sub>3</sub> 13 9 2 12 V<sub>CC</sub> = PIN 14 GND = PIN 7

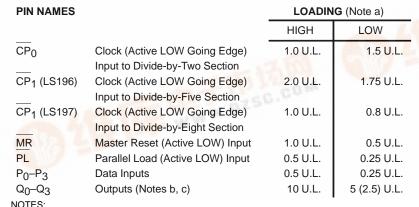

1 TTL Unit Load (U.L.) = 40μA HIGH/1.6 mA LOW.

The Output LOW drive factor is 2.5 U.L. for Military (54) and 5 U.L. for Commercial (74)

emperature Ranges. In addition to loading shown, Q0 can also drive CP1.

f.dzsc.com

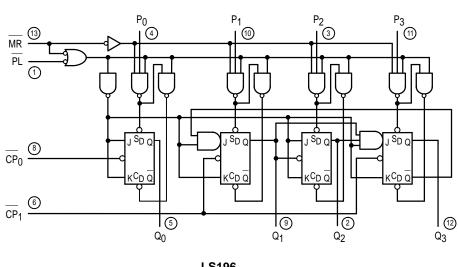

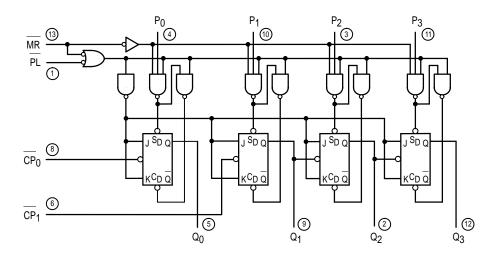

### LOGIC DIAGRAM

LS196

LS197

V<sub>CC</sub> = PIN 14 GND = PIN 7 = PIN NUMBERS

#### **FUNCTIONAL DESCRIPTION**

The LS196 and LS197 are asynchronously presettable decade and binary ripple counters. The LS196 Decade Counter is partitioned into divide-by-two and divide-by-five sections while the LS197 is partitioned into divide-by-two and divideby-eight sections, with all sections having a separate Clock input. In the counting modes, state changes are initiated by the HIGH to LOW transition of the clock signals. State changes of the Q outputs, however, do not occur simultaneously because of the internal ripple delays. When using external logic to decode the Q outputs, designers should bear in mind that the unequal delays can lead to decoding spikes and thus a decoded signal should not be used as a clock or strobe. The CPn input serves the Q<sub>0</sub> flip-flop in both circuit types while the CP<sub>1</sub> input serves the divide-by-five or divide-by-eight section. The Q<sub>0</sub> output is designed and specified to drive the rated fan-out plus the CP1 input. With the input frequency connected to CP0 and Q<sub>0</sub> driving CP<sub>1</sub>, the LS197 forms a straightforward module-16 counter, with Q<sub>0</sub> the least significant output and Q<sub>3</sub> the most significant output.

The LS196 Decade Counter can be connected up to operate in two different count sequences, as indicated in the tables of Figure 2. With the input frequency connected to CP0 and with Q0 driving CP1, the circuit counts in the BCD (8, 4, 2, 1) sequence. With the input frequency connected to CP1 and Q3 driving CP0, Q0 becomes the low frequency output and has a 50% duty cycle waveform. Note that the maximum counting rate is reduced in the latter (bi-quinary) configuration because of the interstage gating delay within the divide-by-five section.

The LS196 and LS197 have an asynchronous active LOW Master Reset input (MR) which overrides all other inputs and forces all outputs LOW. The counters are also asynchronously presettable. A LOW on the Parallel Load input (PL) overrides the clock inputs and loads the data from Parallel Data (P $_0$ –P $_3$ ) inputs into the flip-flops. While PL is LOW, the counters act as transparent latches and any change in the P $_n$  inputs will be reflected in the outputs.

**DECADE (NOTE 1) BI-QUINARY (NOTE 2)** COUNT COUNT  $Q_3$  $Q_2$  $Q_1$  $Q_0$  $Q_0$  $Q_3$  $Q_2$  $Q_1$ 0 L L L L L L L L 1 L L L Н 1 L L L Н 2 L 2 L L Н L L Η L 3 L Н 3 L Н Н L Н L 4 L Н L L 4 L Н L L 5 5 Н Н L L L Н L L 6 L 6 Н Η Н L Н L L 7 L Н 7 Н Н Н Н L L 8 Н L L L 8 Н L Н Н 9 Н Н Н Н ı 1

Figure 2. LS196 COUNT SEQUENCES

#### NOTES:

- 1. Signal applied to CP<sub>0</sub>, Q<sub>0</sub> connected to CP<sub>1</sub>.

- 2. Signal applied to CP<sub>1</sub>, Q<sub>3</sub> connected to CP<sub>0</sub>.

#### **MODE SELECT TABLE**

|    | INPUTS |    | RESPONSE      |

|----|--------|----|---------------|

| MR | PL     | СР | RESPONSE      |

| L  | Х      | Х  | Reset (Clear) |

| Н  | L      | X  | Parallel Load |

| Н  | Н      | _  | Count         |

H = HIGH Voltage Level

L = LOW Voltage Level

X = Don't Care

= HIGH to Low Clock Transition

#### **GUARANTEED OPERATING RANGES**

| Symbol         | Parameter                           |          | Min         | Тур        | Max         | Unit |

|----------------|-------------------------------------|----------|-------------|------------|-------------|------|

| VCC            | Supply Voltage                      | 54<br>74 | 4.5<br>4.75 | 5.0<br>5.0 | 5.5<br>5.25 | V    |

| T <sub>A</sub> | Operating Ambient Temperature Range | 54<br>74 | -55<br>0    | 25<br>25   | 125<br>70   | °C   |

| IOH            | Output Current — High               | 54, 74   |             |            | -0.4        | mA   |

| lOL            | Output Current — Low                | 54<br>74 |             |            | 4.0<br>8.0  | mA   |

## DC CHARACTERISTICS OVER OPERATING TEMPERATURE RANGE (unless otherwise specified)

|                  |                                                                                                                                                |        |     | Limits |                                      |      |                                                |                                                                                                |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|--------|--------------------------------------|------|------------------------------------------------|------------------------------------------------------------------------------------------------|--|

| Symbol           | Parameter                                                                                                                                      |        | Min | Тур    | Max                                  | Unit | Test Conditions                                |                                                                                                |  |

| VIH              | Input HIGH Voltage                                                                                                                             |        | 2.0 |        |                                      | V    | Guaranteed Input HIGH Voltage for All Inputs   |                                                                                                |  |

| VIL              | Input LOW Voltage                                                                                                                              | 54     |     |        | 0.7                                  | V    | Guaranteed Input LOW Voltage for All Inputs    |                                                                                                |  |

| VIL.             | Imput 20 VV Voltage                                                                                                                            | 74     |     |        | 0.8                                  | v    |                                                |                                                                                                |  |

| VIK              | Input Clamp Diode Voltage                                                                                                                      |        |     | -0.65  | -1.5                                 | V    | $V_{CC} = MIN, I_{IN} = -18 \text{ mA}$        |                                                                                                |  |

| \/a              | Output HIGH Voltage                                                                                                                            | 54     | 2.5 | 3.5    |                                      | V    |                                                | = MAX, V <sub>IN</sub> = V <sub>IH</sub>                                                       |  |

| Vон              | Output HIGH voltage                                                                                                                            | 74     | 2.7 | 3.5    |                                      | V    | or V <sub>IL</sub> per Truth T                 | able                                                                                           |  |

| V <sub>2</sub> . | Output LOW Voltage                                                                                                                             | 54, 74 |     | 0.25   | 0.4                                  | V    | I <sub>OL</sub> = 4.0 mA                       | V <sub>CC</sub> = V <sub>CC</sub> MIN,<br>V <sub>IN</sub> = V <sub>IL</sub> or V <sub>IH</sub> |  |

| VOL              | Output LOW Voltage                                                                                                                             | 74     |     | 0.35   | 0.5                                  | V    | I <sub>OL</sub> = 8.0 mA                       | per Truth Table                                                                                |  |

| lıн              | Input HIGH Current <u>Data, PL</u> <u>MR, CP<sub>0</sub> (LS196)</u> <u>MR, CP<sub>0</sub>, CP<sub>1</sub> (LS197)</u> CP <sub>1</sub> (LS196) |        |     |        | 20<br>40<br>40<br>80                 | μА   | $V_{CC} = MAX, V_{IN} = 2.7 V$                 |                                                                                                |  |

|                  | Data, PL<br>MR, CP <sub>0</sub> (LS196)<br>MR, CP <sub>0</sub> , CP <sub>1</sub> (LS197)<br>CP <sub>1</sub> (LS196)                            |        |     |        | 0.1<br>0.2<br>0.2<br>0.4             | mA   | V <sub>CC</sub> = MAX, V <sub>IN</sub> = 7.0 V |                                                                                                |  |

| IIL              | Input LO <u>W</u> Current <u>Dat</u> a, PL  MR <u>CP</u> 0 <u>CP</u> 1 (LS196)  CP <sub>1</sub> (LS197)                                        |        |     |        | -0.4<br>-0.8<br>-2.4<br>-2.8<br>-1.3 | mA   | V <sub>CC</sub> = MAX, V <sub>IN</sub> = 0.4 V |                                                                                                |  |

| los              | Short Circuit Current (Note 1)                                                                                                                 |        | -20 |        | -100                                 | mA   | V <sub>CC</sub> = MAX                          |                                                                                                |  |

| Icc              | Power Supply Current                                                                                                                           |        |     |        | 27                                   | mA   | V <sub>CC</sub> = MAX                          |                                                                                                |  |

Note 1: Not more than one output should be shorted at a time, nor for more than 1 second.

----

#### AC CHARACTERISTICS (T<sub>A</sub> = 25°C)

|                                      |                                                   |     |           | Lin      |     |           |          |      |                                                   |  |

|--------------------------------------|---------------------------------------------------|-----|-----------|----------|-----|-----------|----------|------|---------------------------------------------------|--|

|                                      |                                                   |     | LS196     |          |     | LS197     |          |      |                                                   |  |

| Symbol                               | Parameter                                         | Min | Тур       | Max      | Min | Тур       | Max      | Unit | Test Conditions                                   |  |

| fMAX                                 | Maximum Clock Frequency                           | 30  | 40        |          | 30  | 40        |          | MHz  |                                                   |  |

| <sup>t</sup> PLH<br><sup>t</sup> PHL | CP <sub>0</sub> Input to<br>Q <sub>0</sub> Output |     | 8.0<br>13 | 15<br>20 |     | 8.0<br>14 | 15<br>21 | ns   |                                                   |  |

| <sup>t</sup> PLH<br><sup>t</sup> PHL | CP <sub>1</sub> Input to<br>Q <sub>1</sub> Output |     | 16<br>22  | 24<br>33 |     | 12<br>23  | 19<br>35 | ns   | V <sub>CC</sub> = 5.0 V<br>C <sub>L</sub> = 15 pF |  |

| <sup>t</sup> PLH<br><sup>t</sup> PHL | CP <sub>1</sub> Input to<br>Q <sub>2</sub> Output |     | 38<br>41  | 57<br>62 |     | 34<br>42  | 51<br>63 | ns   |                                                   |  |

| <sup>t</sup> PLH<br><sup>t</sup> PHL | CP <sub>1</sub> Input to<br>Q <sub>3</sub> Output |     | 12<br>30  | 18<br>45 |     | 55<br>63  | 78<br>95 | ns   |                                                   |  |

| <sup>t</sup> PLH<br><sup>t</sup> PHL | Data to Output                                    |     | 20<br>29  | 30<br>44 |     | 18<br>29  | 27<br>44 | ns   |                                                   |  |

| <sup>t</sup> PLH<br><sup>t</sup> PHL | PL Input to<br>Any Output                         |     | 27<br>30  | 41<br>45 |     | 26<br>30  | 39<br>45 | ns   |                                                   |  |

| <sup>t</sup> PHL                     | MR Input to Any Output                            |     | 34        | 51       |     | 34        | 51       | ns   |                                                   |  |

#### AC SETUP REQUIREMENTS $(T_A = 25^{\circ}C)$

|                  |                              | Limits |     |     |       |     |     |      |                         |  |

|------------------|------------------------------|--------|-----|-----|-------|-----|-----|------|-------------------------|--|

|                  |                              | LS196  |     |     | LS197 |     |     |      |                         |  |

| Symbol           | Parameter                    | Min    | Тур | Max | Min   | Тур | Max | Unit | <b>Test Conditions</b>  |  |

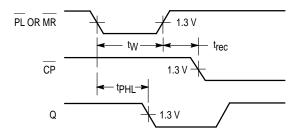

| t <sub>W</sub>   | CP <sub>0</sub> Pulse Width  | 20     |     |     | 20    |     |     | ns   |                         |  |

| t <sub>W</sub>   | CP <sub>1</sub> Pulse Width  | 30     |     |     | 30    |     |     | ns   |                         |  |

| t <sub>W</sub>   | PL Pulse Width               | 20     |     |     | 20    |     |     | ns   |                         |  |

| t <sub>W</sub>   | MR Pulse Width               | 15     |     |     | 15    |     |     | ns   |                         |  |

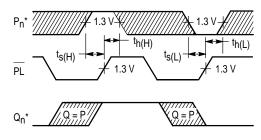

| t <sub>S</sub>   | Data Input Setup Time — HIGH | 10     |     |     | 10    |     |     | ns   | V <sub>CC</sub> = 5.0 V |  |

| t <sub>S</sub>   | Data Input Setup Time — LOW  | 15     |     |     | 15    |     |     | ns   |                         |  |

| t <sub>h</sub>   | Data Hold Time — HIGH        | 10     |     |     | 10    |     |     | ns   |                         |  |

| t <sub>h</sub>   | Data Hold Time — LOW         | 10     |     |     | 10    |     |     | ns   |                         |  |

| t <sub>rec</sub> | Recovery Time                | 30     |     |     | 30    |     |     | ns   |                         |  |

### **DEFINITIONS OF TERMS**

SETUP TIME ( $t_S$ ) — is defined as the minimum time required for the correct logic level to be present at the logic input prior to the clock transition from HIGH to LOW in order to be recognized and transferred to the outputs.

HOLD TIME  $(t_h)$  — is defined as the minimum time following the clock transition from HIGH to LOW that the logic level must be maintained at the input in order to ensure continued recog-

nition. A negative HOLD TIME indicates that the correct logic level may be released prior to the clock transition from HIGH to LOW and still be recognized.

RECOVERY TIME ( $t_{\text{rec}}$ ) — is defined as the minimum time required between the end of the reset pulse and the clock transition from HIGH to LOW in order to recognize and transfer LOW Data to the Q outputs.

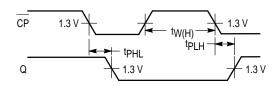

#### **AC WAVEFORMS**

Figure 1

NOTE: PL = LOW

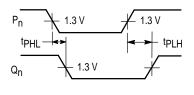

Figure 2

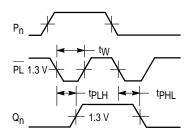

Figure 3

Figure 4

\* The shaded areas indicate when the input is permitted to change for predictable output performance

Figure 5