捷多邦,专业PCB打样工厂,24小时加急出货

ADS7950, ADS7951, ADS7952, ADS7953 ADS7954, ADS7955, ADS7956, ADS7957 ADS7958, ADS7959, ADS7960, ADS7961

www.ti.com

SLAS605-JUNE 2008

# 12/10/8-Bit, 1 MSPS, 16/12/8/4-Channel, Single-Ended, MicroPower, Serial Interface ADCs

#### **FEATURES**

- 1-MHz Sample Rate Serial Devices

- Product Family of 12/10/8-Bit Resolution

- Zero Latency

- 20-MHz Serial Interface

- Analog Supply Range: 2.7 to 5.25V

- I/O Supply Range: 1.7 to 5.25V

- Two SW Selectable Unipolar, Input Ranges: 0 to 2.5V and 0 to 5V

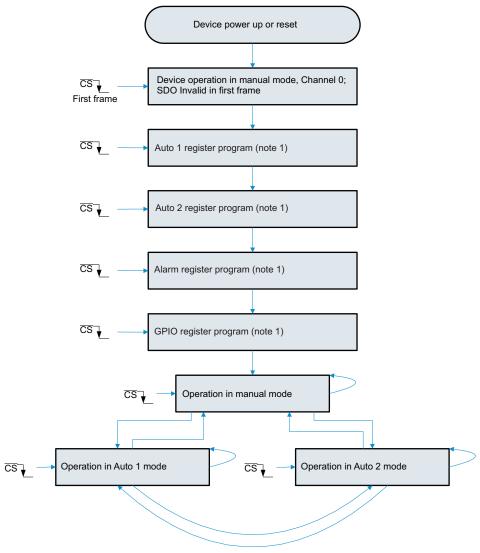

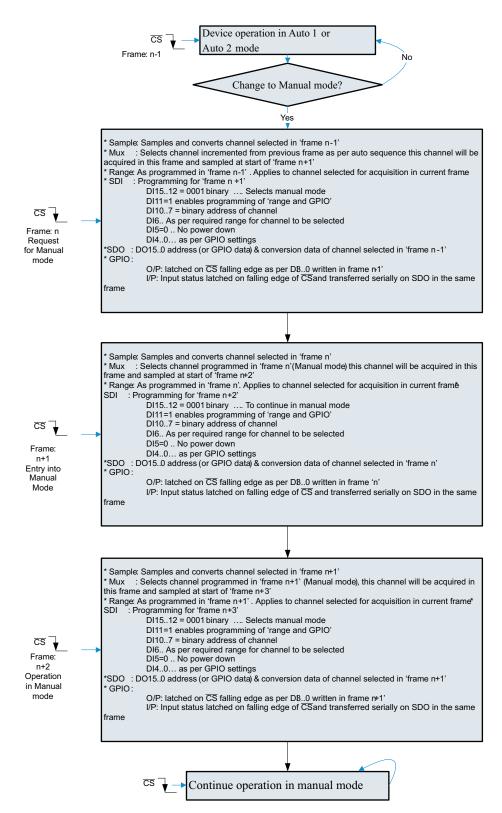

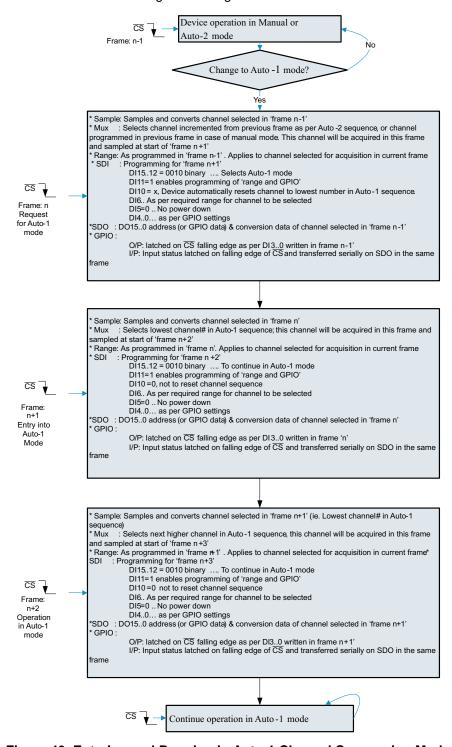

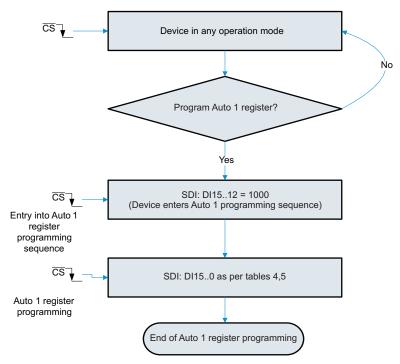

- Auto and Manual Modes for Channel Selection

- 12,8,4-Channel Devices can Share 16 Channel Device Footprint

- Two Programmable Alarm Levels per Channel

- Four Individually Configurable GPIOs

- Typical Power Dissipation: 14.5 mW (+VA = 5V, +VBD = 3V) at 1 MSPS

- Power-Down Current (1 μA)

- Input Bandwidth (47 at 3dB)

- 30-Pin and 38-Pin TSSOP Packages

### **APPLICATIONS**

- PLC / IPC

- Battery Powered Systems

- Medical Instrumentation

- Digital Power Supplies

- Touch Screen Controllers

- High-Speed Data Acquisition Systems

- High-Speed Closed-Loop Systems

### DESCRIPTION

The ADS79XX is a 12/10/8-bit multichannel analog-to-digital converter family. The following table shows all twelve devices from this product family.

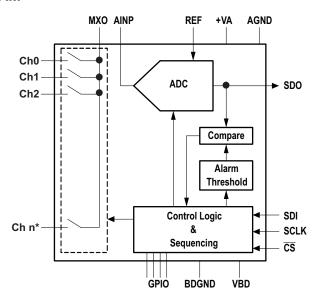

The devices include a capacitor based SAR A/D converter with inherent sample and hold.

The devices accept a wide analog supply range from 2.7V to 5.25V. Very low power consumption makes these devices suitable for battery-powered and isolated power supply applications.

A wide 1.7V to 5.25V I/O supply range facilitates a glue-less interface with the most commonly used CMOS digital hosts.

The serial interface is controlled by  $\overline{\text{CS}}$  and SCLK for easy connection with microprocessors and DSP.

The input signal is sampled with the falling edge of  $\overline{CS}$ . It uses SCLK for conversion, serial data output, and reading serial data in. The devices allow auto sequencing of preselected channels or manual selection of a channel for the next conversion cycle.

There are two software selectable input ranges (0V - 2.5V and 0V - 5V), four individually configurable GPIOs, and two programmable alarm thresholds per channel. These features make the devices suitable for most data acquisition applications.

The devices offer an attractive power-down feature. This is extremely useful for power saving when the device is operated at lower conversion speeds.

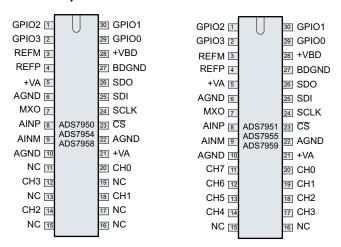

The 16/12-channel devices from this family are available in a 38-pin TSSOP package and the 4/8-channel devices are available in a 30-pin TSSOP package.

### MICROPOWER MULTI-CHANNEL ADS79XX FAMILY

| NUMBER OF | RESOLUTION |         |         |  |  |  |  |

|-----------|------------|---------|---------|--|--|--|--|

| CHANNELS  | 12 BIT     | 10 BIT  | 8 BIT   |  |  |  |  |

| 16        | ADS7953    | ADS7957 | ADS7961 |  |  |  |  |

| 12        | ADS7952    | ADS7956 | ADS7960 |  |  |  |  |

| 8         | ADS7951    | ADS7955 | ADS7959 |  |  |  |  |

| 4         | ADS7950    | ADS7954 | ADS7958 |  |  |  |  |

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

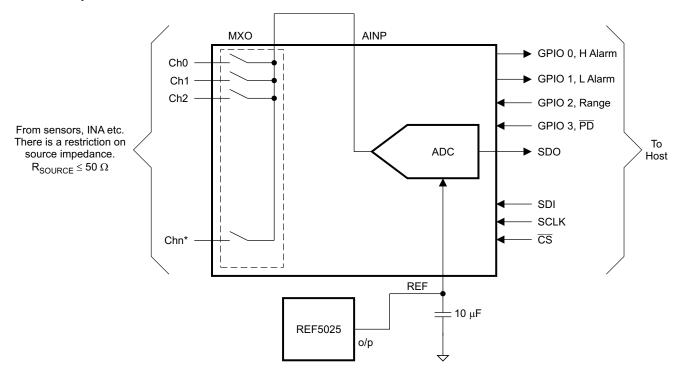

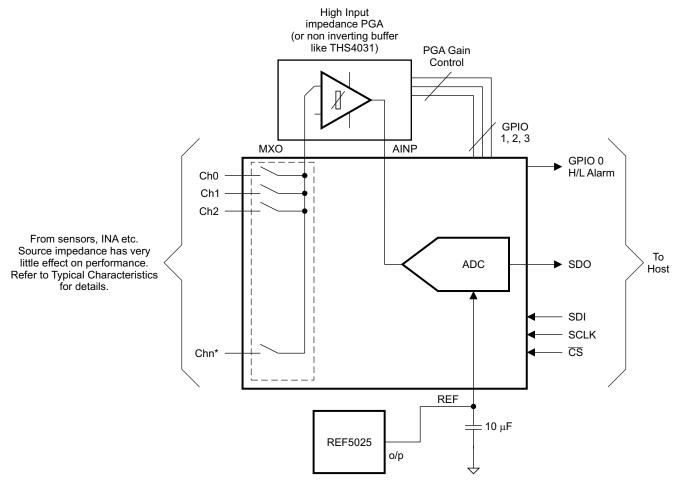

#### **ADS79XX BLOCK DIAGRAM**

NOTE: n\* is number of channels (16,12,8, or 4) depending on the device from the ADS79XX product family.

### **ORDERING INFORMATION - 12-BIT**

| MODEL           | MAXIMUM<br>INTEGRAL<br>LINEARITY<br>(LSB) | MAXIMUM<br>DIFFERENTIAL<br>LINEARITY<br>(LSB) | NO MISSING<br>CODES AT<br>RESOLUTION<br>(BIT) | NUMBER OF<br>CHANNELS | PACKAGE<br>TYPE | PACKAGE<br>DESIGNATOR | TEMPERATURE<br>RANGE | ORDERING<br>INFORMATION | TRANSPORT<br>MEDIA<br>QTY |

|-----------------|-------------------------------------------|-----------------------------------------------|-----------------------------------------------|-----------------------|-----------------|-----------------------|----------------------|-------------------------|---------------------------|

| ADS7953 SB      |                                           |                                               |                                               | 16                    | 38 pin TSSOP    |                       |                      | ADS7953SBDBT            | Tube, 50                  |

| 71207000 OB     |                                           | 10 30 pm 10001                                |                                               | ADS7953SBDBTR         | Reel, 2000      |                       |                      |                         |                           |

| ADS7952 SB      | - ±1                                      |                                               |                                               | 12                    | 38 pin TSSOP    | DBT                   | -40°C to 125°C       | ADS7952SBDBT            | Tube, 50                  |

| AD37932 3B      |                                           | ±1                                            | 12                                            | 12                    |                 |                       |                      | ADS7952SBDBTR           | Reel, 2000                |

| ADS7951 SB      |                                           | Ξ1                                            | 12                                            |                       | 30 pin TSSOP    | DBT                   |                      | ADS7951SBDBT            | Tube, 60                  |

| AD5/951 5B      |                                           |                                               |                                               | 8                     | 30 pm 1550P     |                       |                      | ADS7951SBDBTR           | Reel, 2000                |

| AD07050 OD      |                                           |                                               |                                               | 4                     | 30 pin TSSOP    |                       |                      | ADS7950SBDBT            | Tube, 60                  |

| ADS7950 SB      |                                           |                                               |                                               |                       | 30 pin 1550P    |                       |                      | ADS7950SBDBTR           | Reel, 2000                |

| AD07050 0       |                                           |                                               |                                               | 40                    | 00 -:- T000D    |                       |                      | ADS7953SDBT             | Tube, 50                  |

| ADS7953 S       |                                           |                                               |                                               | 16                    | 38 pin TSSOP    |                       |                      | ADS7953SDBTR            | Reel, 2000                |

| ADS7952 S       |                                           |                                               |                                               | 12                    | 20 min TCCOD    |                       |                      | ADS7952SDBT             | Tube, 50                  |

| AD57952 5       | .4.5                                      | +2                                            | 44                                            | 12                    | 38 pin TSSOP    | DDT                   | 1000 1- 10500        | ADS7952SDBTR            | Reel, 2000                |

| A D 0 7 0 5 4 0 | ±1.5                                      | ±2                                            | 11                                            |                       | 00 - i- T000D   | DBT                   | -40°C to 125°C       | ADS7951SDBT             | Tube, 60                  |

| ADS7951S        |                                           |                                               |                                               | 8                     | 30 pin TSSOP    |                       |                      | ADS7951SDBTR            | Reel, 2000                |

| AD07050 0       |                                           |                                               |                                               | 4                     | 00 min T000D    |                       |                      | ADS7950SDBT             | Tube, 60                  |

| ADS7950 S       |                                           |                                               |                                               | 4                     | 30 pin TSSOP    |                       |                      | ADS7950SDBTR            | Reel, 2000                |

ADS7954, ADS7955, ADS7956, ADS7957 ADS7958, ADS7959, ADS7960, ADS7961

ADS7950, ADS7951, ADS7952, ADS7953

SLAS605-JUNE 2008 www.ti.com

### **ORDERING INFORMATION - 10-BIT**

| MODEL     | MAXIMUM<br>INTEGRAL<br>LINEARITY<br>(LSB) | MAXIMUM<br>DIFFERENTIAL<br>LINEARITY<br>(LSB) | NO MISSING<br>CODES AT<br>RESOLUTION<br>(BIT) | NUMBER<br>OF<br>CHANNELS | PACKAGE<br>TYPE | PACKAGE<br>DESIGNATOR | TEMPERATURE<br>RANGE | ORDERING<br>INFORMATION | TRANSPORT<br>MEDIA<br>QTY |              |            |

|-----------|-------------------------------------------|-----------------------------------------------|-----------------------------------------------|--------------------------|-----------------|-----------------------|----------------------|-------------------------|---------------------------|--------------|------------|

| ADS7957 S |                                           |                                               |                                               | 16                       | 38 pin TSSOP    |                       |                      | ADS7957SDBT             | Tube, 50                  |              |            |

| AD3/93/ 3 |                                           |                                               |                                               | 10                       | 36 pm 1550P     | 36 piii 1330F         |                      |                         | ADS7957SDBTR              | Reel, 2000   |            |

| ADS7956 S |                                           | 12 38 pin TSSOF                               | 38 pin TSSOP                                  |                          |                 | ADS7956SDBT           | Tube, 50             |                         |                           |              |            |

| AD37930 3 | ±0.5                                      | ±0.5                                          | 10                                            | 12                       | 36 pili 1330F   | 36 piii 1330F         | 36 piii 1330F        | DBT                     | -40°C to 125°C            | ADS7956SDBTR | Reel, 2000 |

| ADCZOFF C | ±0.5                                      | ±0.5                                          | 10                                            | 8                        |                 | DRI                   | -40°C to 125°C       | ADS7955SDBT             | Tube, 60                  |              |            |

| ADS7955 S |                                           |                                               |                                               |                          | 0               | 0                     | 30 pin TSSOP         |                         |                           | ADS7955SDBTR | Reel, 2000 |

| ADS7954 S |                                           |                                               |                                               | 4                        | 20 min TCCOD    |                       | ,                    | ADS7954SDBT             | Tube, 60                  |              |            |

| AD5/954 S |                                           |                                               |                                               | 4                        | 30 pin TSSOP    |                       |                      | ADS7954SDBTR            | Reel, 2000                |              |            |

### **ORDERING INFORMATION - 8-BIT**

| MODEL     | MAXIMUM<br>INTEGRAL<br>LINEARITY<br>(LSB) | MAXIMUM<br>DIFFERENTIAL<br>LINEARITY<br>(LSB) | NO MISSING<br>CODES AT<br>RESOLUTION<br>(BIT) | NUMBER OF<br>CHANNELS | PACKAGE<br>TYPE | PACKAGE<br>DESIGNATOR | TEMPERATURE<br>RANGE | ORDERING<br>INFORMATION | TRANSPORT<br>MEDIA<br>QTY |              |            |              |              |              |  |  |              |            |

|-----------|-------------------------------------------|-----------------------------------------------|-----------------------------------------------|-----------------------|-----------------|-----------------------|----------------------|-------------------------|---------------------------|--------------|------------|--------------|--------------|--------------|--|--|--------------|------------|

| ADS7961 S |                                           |                                               |                                               | 16                    | 38 pin TSSOP    |                       |                      | ADS7961SDBT             | Tube, 50                  |              |            |              |              |              |  |  |              |            |

| AD37901 3 |                                           |                                               |                                               | 16                    | 38 pin 1550P    | 36 piii 1330F         | 36 piii 1330F        |                         |                           | ADS7961SDBTR | Reel, 2000 |              |              |              |  |  |              |            |

| ADS7960 S |                                           |                                               | 40 00 70000                                   |                       | ADS7960SDBT     | Tube, 50              |                      |                         |                           |              |            |              |              |              |  |  |              |            |

| ADS/960 S |                                           | .00                                           |                                               | 12                    | 38 pin TSSOP    | 36 piii 1330F         |                      | 4000 +- 40500           | ADS7960SDBTR              | Reel, 2000   |            |              |              |              |  |  |              |            |

| AD07050 0 | ±0.3                                      | ±0.3                                          | 8                                             |                       | 00 - i- T000D   | DBT                   | -40°C to 125°C       | ADS7959SDBT             | Tube, 60                  |              |            |              |              |              |  |  |              |            |

| ADS7959 S |                                           |                                               |                                               | 8                     | 8               | 8                     | 8                    | 8                       | 8                         | 8            | 8          | 30 pin TSSOP | 30 pin TSSOP | 30 pin TSSOP |  |  | ADS7959SDBTR | Reel, 2000 |

| AD07050 C |                                           |                                               |                                               | 4                     | 20 min TCCOD    | 1                     |                      | ADS7958SDBT             | Tube, 60                  |              |            |              |              |              |  |  |              |            |

| ADS7958 S |                                           |                                               |                                               | 4                     | 30 pin TSSOP    |                       |                      | ADS7958SDBTR            | Reel, 2000                |              |            |              |              |              |  |  |              |            |

# **ABSOLUTE MAXIMUM RATINGS**(1)

|                             |                                                   | VALUE                       | UNIT |

|-----------------------------|---------------------------------------------------|-----------------------------|------|

| AINP or CHn to AGN          | ND                                                | -0.3 to +VA +0.3            | V    |

| +VA to AGND, +VBI           | D to BDGND                                        | -0.3 to +7.0                | V    |

| Digital input voltage       | to BDGND                                          | -0.3 to (7.0)               | V    |

| Digital output to BDGND     |                                                   | -0.3 to (+VA + 0.3)         | V    |

| Operating temperature range |                                                   | -40 to 125                  | °C   |

| Storage temperature         | range                                             | -65 to 150                  | °C   |

| Junction temperature        | e (T <sub>J</sub> Max)                            | 150                         | °C   |

| TCCOD mankage               | Power dissipation                                 | $(T_J Max-T_A)/\theta_{JA}$ |      |

| TSSOP package               | $\theta_{JA}$ Thermal impedance                   | 100.6                       | °C/W |

| ADS79XX family of o         | devices are rated for MSL2 260°C per the JSTD-020 |                             |      |

<sup>(1)</sup> Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. Exposure to absolute maximum conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS, ADS7950/51/52/53**

+VA = 2.7 V to 5.25 V, +VBD = 1.7 V to 5.25 V,  $T_A = -40 ^{\circ}\text{C}$  to 125 °C,  $f_{sample} = 1 \text{ MHz}$  (unless otherwise noted)

| PARAMETER                            | TEST CONDITIONS                                                                                                             | MIN   | TYP         | MAX                                                                                      | UNIT               |  |

|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-------|-------------|------------------------------------------------------------------------------------------|--------------------|--|

| ANALOG INPUT                         |                                                                                                                             |       |             | 1                                                                                        |                    |  |

| Full coals (coast coast (1)          | Range 1                                                                                                                     | 0     |             | Vref                                                                                     |                    |  |

| Full-scale input span <sup>(1)</sup> | Range 2                                                                                                                     | 0     |             |                                                                                          | V                  |  |

| Absolute input range                 | Range 1                                                                                                                     | -0.20 |             |                                                                                          | V                  |  |

| Absolute input range                 | Range 2                                                                                                                     | -0.20 |             |                                                                                          | V                  |  |

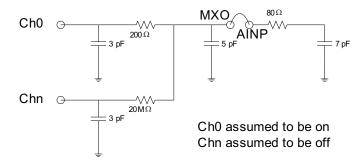

| Input capacitance                    |                                                                                                                             |       | 15          |                                                                                          | ρF                 |  |

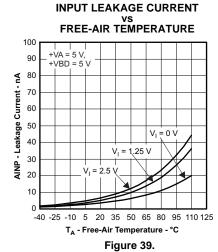

| Input leakage current                | T <sub>A</sub> = 125°C                                                                                                      |       | 61          |                                                                                          | nA                 |  |

| SYSTEM PERFORMANCE                   |                                                                                                                             |       |             |                                                                                          |                    |  |

| Resolution                           |                                                                                                                             |       | 12          |                                                                                          | Bits               |  |

| No estado e a dos                    | ADS795XSB (2)                                                                                                               | 12    |             |                                                                                          | D:1-               |  |

| No missing codes                     | ADS795XS <sup>(2)</sup>                                                                                                     | 11    |             |                                                                                          | Bits               |  |

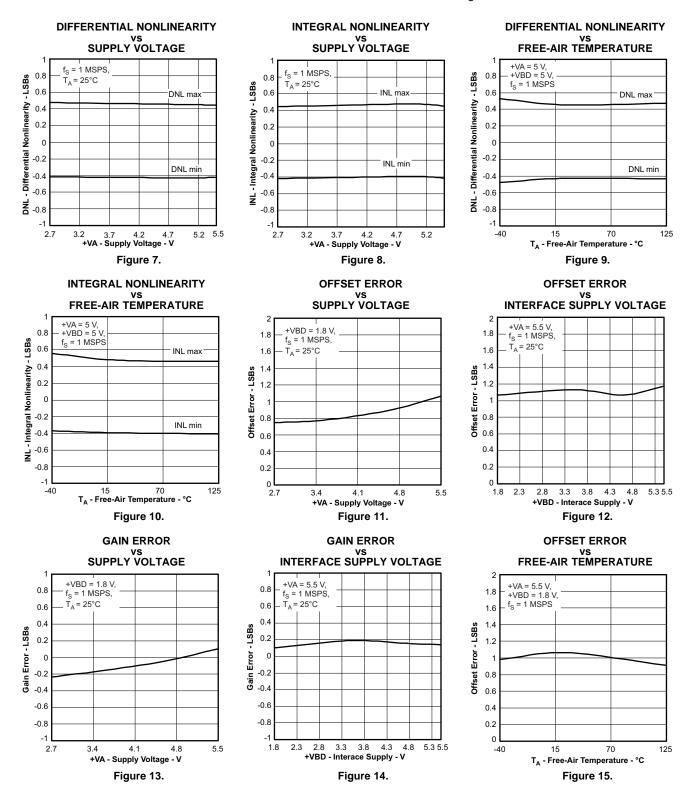

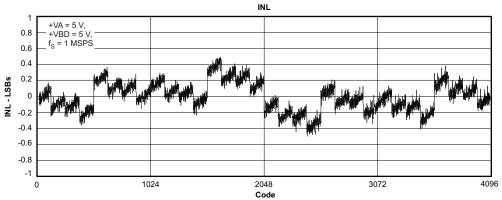

| 1.4 18 %                             | ADS795XSB <sup>(2)</sup>                                                                                                    | -1    | ±0.5        | 1                                                                                        | LOD (3)            |  |

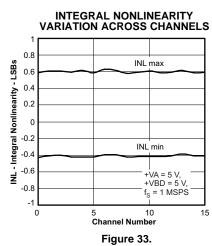

| Integral linearity                   | ADS795XS <sup>(2)</sup>                                                                                                     | -1.5  | ±0.75       | 1.5                                                                                      | LSB <sup>(3)</sup> |  |

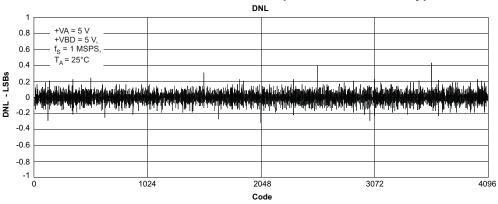

| P                                    | ADS795XSB <sup>(2)</sup>                                                                                                    | -1    | ±0.5        | 1                                                                                        | 1.00               |  |

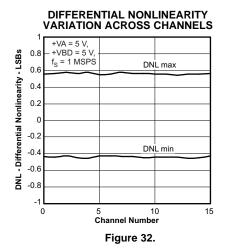

| Differential linearity               | ADS795XS <sup>(2)</sup>                                                                                                     | -2    | ±0.75       | 1.5                                                                                      | LSB                |  |

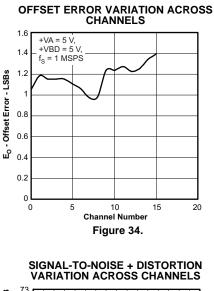

| Offset error <sup>(4)</sup>          |                                                                                                                             | -3.5  | ±1.1        | 3.5                                                                                      | LSB                |  |

| 0.:                                  | Range 1                                                                                                                     | -2    | ±0.2        | 2                                                                                        | 1.00               |  |

| Gain error                           | Range 2                                                                                                                     |       | ±0.2        |                                                                                          | LSB                |  |

| SAMPLING DYNAMICS                    |                                                                                                                             |       |             |                                                                                          |                    |  |

| Conversion time                      | 20 MHz sclk                                                                                                                 |       |             | 800                                                                                      | nSec               |  |

| Acquisition time                     |                                                                                                                             | 325   |             |                                                                                          | nSec               |  |

| Maximum throughput rate              | 20 MHz sclk                                                                                                                 |       |             | 1.0                                                                                      | MHz                |  |

| Aperture delay                       |                                                                                                                             |       | 5           |                                                                                          | nsec               |  |

| Step response                        |                                                                                                                             |       | 150         |                                                                                          | nsec               |  |

| Over voltage recovery                |                                                                                                                             |       | 150         |                                                                                          | nsec               |  |

| DYNAMIC CHARACTERISTICS              |                                                                                                                             |       |             |                                                                                          |                    |  |

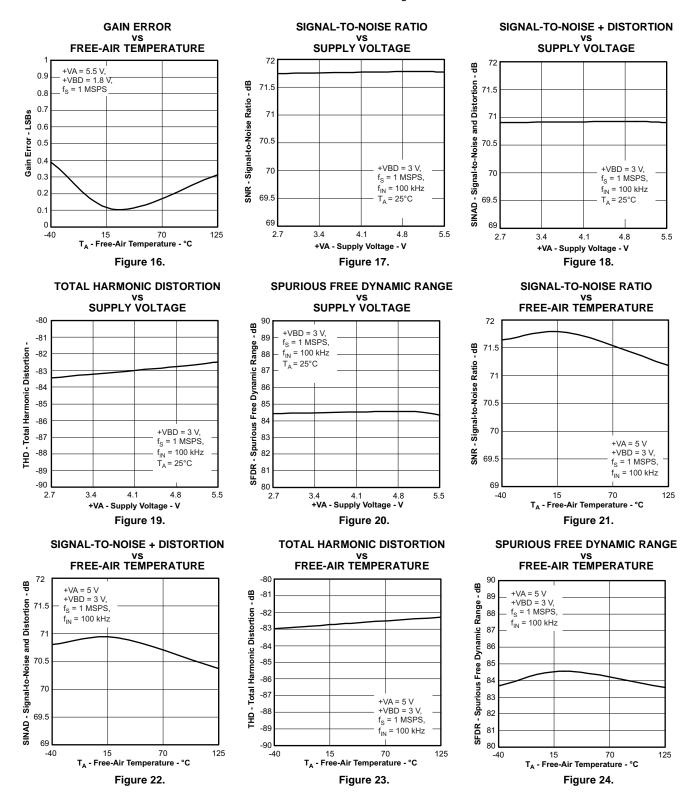

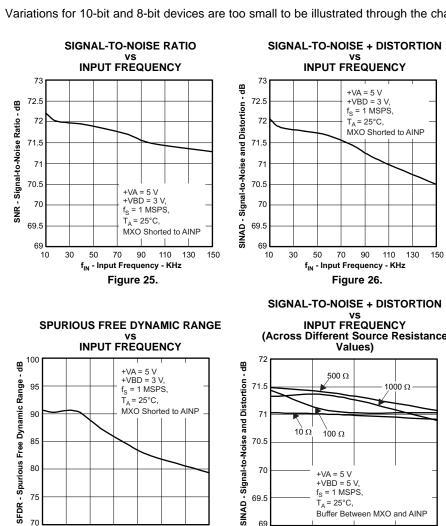

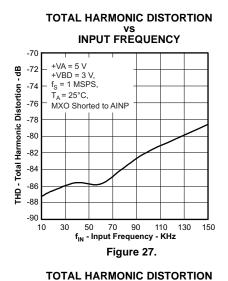

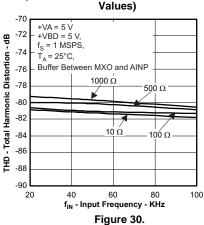

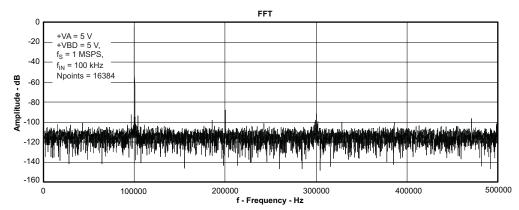

| Total harmonic distortion (5)        | 100 kHz                                                                                                                     |       | -82         |                                                                                          | dB                 |  |

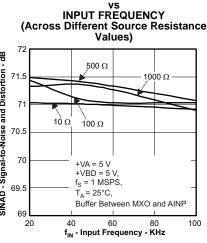

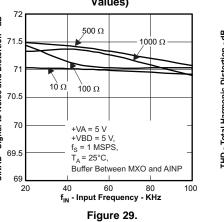

| Signal-to-noise ratio                | 100 kHz, ADS795XSB <sup>(2)</sup>                                                                                           | 70    | 71.7        |                                                                                          | dB                 |  |

|                                      | 100 kHz, ADS795XS <sup>(2)</sup>                                                                                            | 70    | 71.7        |                                                                                          |                    |  |

| Signal-to-noise + distortion         | 100 kHz, ADS795XSB <sup>(2)</sup>                                                                                           | 69    | 71.3        |                                                                                          | dB                 |  |

|                                      | 100 kHz, ADS795XS <sup>(2)</sup>                                                                                            | 68    | 71.3        | Vref<br>2*Vref<br>VREF<br>+0.20<br>2*VREF<br>+0.20<br>1<br>1.5<br>1.5<br>2<br>800<br>1.0 |                    |  |

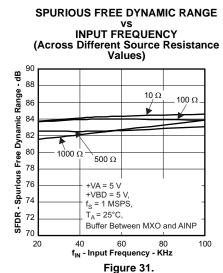

| Spurious free dynamic range          | 100 kHz                                                                                                                     |       | 84          |                                                                                          | dB                 |  |

| Small signal bandwidth               | At –3 dB                                                                                                                    |       | 47          |                                                                                          | MHz                |  |

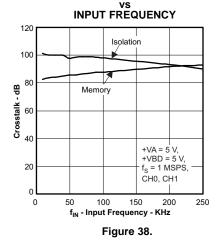

| Charried to alcohol proceeds.        | Any off-channel with 100kHz, Full-scale input to channel being sampled with DC input (isolation crosstalk).                 |       | <b>-</b> 95 |                                                                                          | ٩D                 |  |

| Channel-to-channel crosstalk         | From previously sampled to channel with 100kHz, Full-scale input to channel being sampled with DC input (memory crosstalk). |       | -85         |                                                                                          | dB                 |  |

| ETERNAL REFERENCE INPUT              |                                                                                                                             |       |             |                                                                                          |                    |  |

| Vref reference voltage at REFP       |                                                                                                                             | 2.49  | 2.5         | 2.51                                                                                     | V                  |  |

| Reference resistance                 |                                                                                                                             |       | 100         |                                                                                          | kΩ                 |  |

<sup>(1)</sup> Ideal input span; does not include gain or offset error.

4

<sup>(2)</sup> ADS795X, where X indicates 0, 1, 2, or 3

<sup>(3)</sup> LSB means Least Significant Bit.

<sup>(4)</sup> Measured relative to an ideal full-scale input

<sup>(5)</sup> Calculated on the first nine harmonics of the input frequency.

# **ELECTRICAL CHARACTERISTICS, ADS7950/51/52/53 (continued)**

+VA = 2.7 V to 5.25 V, +VBD = 1.7 V to 5.25 V,  $T_A = -40 ^{\circ}\text{C}$  to 125  $^{\circ}\text{C}$ ,  $f_{sample} = 1 \text{ MHz}$  (unless otherwise noted)

| P                                                    | ARAMETER               | TEST CONDITIONS                             | MIN        | TYP                                                      | MAX  | UNIT        |

|------------------------------------------------------|------------------------|---------------------------------------------|------------|----------------------------------------------------------|------|-------------|

| ALARM SETTI                                          | NG                     |                                             |            |                                                          |      |             |

| Higher threshol                                      | ld range               |                                             | 0          |                                                          | FFC  | Hex         |

| Lower threshold                                      | d range                |                                             | 0          |                                                          | FFC  | Hex         |

| DIGITAL INPU                                         | T/OUTPUT               |                                             | ,          |                                                          |      |             |

| Logic family                                         |                        | CMOS                                        |            |                                                          |      |             |

|                                                      | V <sub>IH</sub>        |                                             | 0.7*(+VBD) |                                                          |      |             |

|                                                      | V <sub>IL</sub>        | +VBD = 5 V                                  |            |                                                          | 0.8  |             |

| Logic level                                          | V <sub>IL</sub>        | +VBD = 3 V                                  |            |                                                          | 0.4  | V           |

|                                                      | V <sub>OH</sub>        | At I <sub>source</sub> = 200 μA             | Vdd-0.2    |                                                          |      |             |

| Data format MSB<br>POWER SUPPLY<br>+VA supply voltag | V <sub>OL</sub>        | At I <sub>sink</sub> = 200 μA               | 0.4        |                                                          |      |             |

| Data format MS                                       | SB first               |                                             | MSI        | 3 First                                                  |      |             |

| POWER SUPP                                           | LY REQUIREMENTS        |                                             |            |                                                          |      |             |

| +VA supply vol                                       | tage                   |                                             | 2.7        | 3.3                                                      | 5.25 | V           |

| +VBD supply v                                        | oltage                 |                                             | 1.7        | 3.3                                                      | 5.25 | V           |

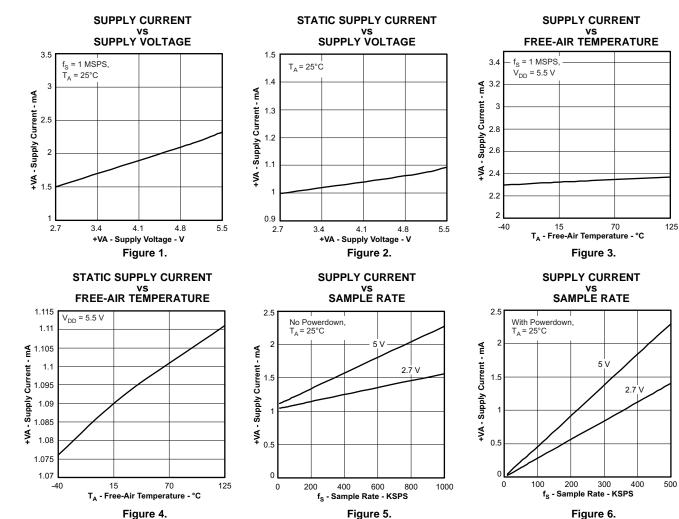

|                                                      |                        | At +VA = 2.7 to 3.6 V and 1MHz throughput   |            | 1.8                                                      |      | mA          |

| Supply current                                       | (normal mada)          | At +VA = 2.7 to 3.6 V static state          |            | 1.05                                                     |      | mA          |

| Supply current                                       | (normal mode)          | At +VA = 4.7 to 5.25 V and 1 MHz throughput |            | 2.3                                                      | 3    | mA          |

|                                                      |                        | At +VA = 4.7 to 5.25 V static state         |            | 7 3.3 5.25<br>7 3.3 5.25<br>1.8 1.05<br>2.3 3<br>1.1 1.5 | mA   |             |

| Power-down st                                        | ate supply current     |                                             |            | 1                                                        |      | μΑ          |

| +VBD supply c                                        | urrent                 | +VA = 5.25V, f <sub>s</sub> = 1MHz          |            | 1                                                        |      | mA          |

| Power-up time                                        |                        |                                             |            |                                                          | 1    | μSec        |

| Invalid convers reset                                | ions after power up or |                                             |            |                                                          | 1    | Number<br>s |

| TEMPERATUR                                           | RE RANGE               |                                             | ·          |                                                          |      |             |

| Specified perfo                                      | rmance                 |                                             | -40        |                                                          | 125  | °C          |

# **ELECTRICAL CHARACTERISTICS, ADS7954/55/56/57**

+VA = 2.7 V to 5.25 V, +VBD = 1.7 V to 5.25 V,  $T_A = -40 ^{\circ}\text{C}$  to  $125 ^{\circ}\text{C}$ ,  $f_{\text{sample}} = 1 \text{ MHz}$  (unless otherwise noted)

| PARAMETER                              | TEST CONDITIONS      | MIN   | TYP  | MAX             | UNIT               |

|----------------------------------------|----------------------|-------|------|-----------------|--------------------|

| ANALOG INPUT                           |                      |       |      |                 |                    |

| Full-scale input span <sup>(1)</sup>   | Range 1              | 0     |      | Vref            | V                  |

| Full-scale input span 7                | Range 2              | 0     |      | 2*Vref          | V                  |

| Abaduta input ranga                    | Range 1              | -0.20 |      | VREF<br>+0.20   | V                  |

| Absolute input range  nput capacitance | Range 2              | -0.20 |      | 2*VREF<br>+0.20 | V                  |

| Input capacitance                      |                      |       | 15   |                 | ρF                 |

| Input leakage current                  | $T_A = 125^{\circ}C$ |       | 61   |                 | nA                 |

| SYSTEM PERFORMANCE                     |                      |       |      |                 |                    |

| Resolution                             |                      |       | 10   |                 | Bits               |

| No missing codes                       |                      | 10    |      |                 | Bits               |

| Integral linearity                     |                      | -0.5  | ±0.2 | 0.5             | LSB <sup>(2)</sup> |

| Differential linearity                 |                      | -0.5  | ±0.2 | 0.5             | LSB                |

| Offset error <sup>(3)</sup>            |                      | -1.5  | ±0.5 | 1.5             | LSB                |

- (1) Ideal input span; does not include gain or offset error.

- (2) LSB means Least Significant Bit.

- (3) Measured relative to an ideal full-scale input

# **ELECTRICAL CHARACTERISTICS, ADS7954/55/56/57 (continued)**

+VA = 2.7 V to 5.25 V, +VBD = 1.7 V to 5.25 V,  $T_A = -40 ^{\circ}\text{C}$  to 125  $^{\circ}\text{C}$ ,  $f_{\text{sample}} = 1 \text{ MHz}$  (unless otherwise noted)

| DADA                         | AMETER              | TEST CONDITIONS                                                                                          | MIN        | TYP        | MAX   | UNIT    |

|------------------------------|---------------------|----------------------------------------------------------------------------------------------------------|------------|------------|-------|---------|

| FARA                         | AIVIE I EK          | Range 1                                                                                                  |            | ±0.1       | 1 MAX | UNIT    |

| Gain error                   |                     | -                                                                                                        | -1         | ±0.1       | !     | LSB     |

| SAMPLING DYNA                | MICS                | Range 2                                                                                                  |            | ±0.1       |       |         |

| Conversion time              |                     | 20 MHz SCLK                                                                                              |            |            | 800   | nSec    |

| Acquisition time             |                     | 20 WH IZ GOLK                                                                                            | 325        |            | 000   | nSec    |

| Maximum throught             | out rate            | 20 MHz SCLK                                                                                              | 323        |            | 1.0   | MHz     |

| Aperture delay               | out rate            | 20 WH IZ COLK                                                                                            |            | 5          | 1.0   | nsec    |

| Step response                |                     |                                                                                                          |            | 150        |       | nsec    |

| Over voltage recov           | /erv                |                                                                                                          |            | 150        |       | nsec    |

| DYNAMIC CHARA                |                     |                                                                                                          |            |            |       |         |

| Total harmonic dis           |                     | 100 kHz                                                                                                  |            | -80        |       | dB      |

| Signal-to-noise rati         |                     | 100 kHz                                                                                                  | 60         |            |       | dB      |

| Signal-to-noise + d          |                     | 100 kHz                                                                                                  | 60         |            |       |         |

| Spurious free dyna           |                     | 100 kHz                                                                                                  |            | 82         |       | dB      |

| Full power bandwig           |                     | At –3 dB                                                                                                 |            | 47         |       | MHz     |

| Channel-to-channel crosstalk |                     | Any off-channel with 100kHz, Full-scale input to channel being sampled with DC input.                    |            | <b>-95</b> |       |         |

|                              |                     | From previously sampled to channel with 100kHz, Full-scale input to channel being sampled with DC input. |            | -85        |       | dB      |

| ETERNAL REFER                | ENCE INPUT          |                                                                                                          | -          |            |       |         |

| Vref reference volta         | age at REFP         |                                                                                                          | 2.49       | 2.5        | 2.51  | V       |

| Reference resistan           | ice                 |                                                                                                          |            | 100        |       | kΩ      |

| ALARM SETTING                |                     |                                                                                                          |            |            |       |         |

| Higher threshold ra          | ange                |                                                                                                          | 000        |            | FFC   | Hex     |

| Lower threshold ra           | nge                 |                                                                                                          | 000        |            | FFC   | Hex     |

| DIGITAL INPUT/O              | UTPUT               |                                                                                                          |            |            |       |         |

| Logic family                 |                     | CMOS                                                                                                     |            |            |       |         |

|                              | V <sub>IH</sub>     |                                                                                                          | 0.7*(+VBD) |            |       |         |

|                              | V <sub>IL</sub>     | +VBD = 5 V                                                                                               |            |            | 8.0   |         |

| Logic level                  | V <sub>IL</sub>     | +VBD = 3 V                                                                                               |            |            | 0.4   | V       |

|                              | V <sub>OH</sub>     | At I <sub>source</sub> = 200 μA                                                                          | Vdd-0.2    |            |       |         |

|                              | V <sub>OL</sub>     | At I <sub>sink</sub> = 200 μA                                                                            | 0.4        |            |       |         |

| Data format MSB f            | irst                |                                                                                                          | MSE        | 3 First    |       |         |

| POWER SUPPLY                 | REQUIREMENTS        |                                                                                                          |            |            |       |         |

| +VA supply voltage           | e                   |                                                                                                          | 2.7        | 3.3        | 5.25  | V       |

| +VBD supply volta            | ge                  |                                                                                                          | 1.7        | 3.3        | 5.25  | V       |

|                              |                     | At +VA = 2.7 to 3.6 V and 1MHz throughput                                                                |            | 1.8        |       | mA      |

| Supply ourrest (se           | rmal modo)          | At +VA = 2.7 to 3.6 V static state                                                                       |            | 1.05       | 1     | mA      |

| Supply current (normal mode) |                     | At +VA = 4.7 to 5.25 V and 1 MHz throughput                                                              |            | 2.3        | 3     | mA      |

|                              |                     | At +VA = 4.7 to 5.25 V static state                                                                      |            | 1.1        | 1.5   | mA      |

| Power-down state             | supply current      |                                                                                                          |            | 1          |       | μΑ      |

| +VBD supply curre            | ent                 | +VA = 5.25V, f <sub>s</sub> = 1MHz                                                                       |            | 1          |       | mA      |

| Power-up time                |                     |                                                                                                          |            |            | 1     | μSec    |

| Invalid conversions reset    | s after power up or |                                                                                                          |            |            | 1     | Numbers |

(4) Calculated on the first nine harmonics of the input frequency.

6

# **ELECTRICAL CHARACTERISTICS, ADS7954/55/56/57 (continued)**

+VA = 2.7 V to 5.25 V, +VBD = 1.7 V to 5.25 V,  $T_A = -40 ^{\circ}\text{C}$  to  $125 ^{\circ}\text{C}$ ,  $f_{\text{sample}} = 1 \text{ MHz}$  (unless otherwise noted)

| PARAMETER             | TEST CONDITIONS | MIN | TYP MAX | UNIT |

|-----------------------|-----------------|-----|---------|------|

| TEMPERATURE RANGE     |                 |     |         |      |

| Specified performance |                 | -40 | 125     | °C   |

# **ELECTRICAL CHARACTERISTICS, ADS7958/59/60/61**

+VA = 2.7 V to 5.25 V, +VBD = 1.7 V to 5.25 V,  $T_A = -40 ^{\circ}\text{C}$  to  $125 ^{\circ}\text{C}$ ,  $f_{\text{sample}} = 1 \text{ MHz}$  (unless otherwise noted)

| PARAMETER                            | TEST CONDITIONS                                                                                          | MIN   | TYP  | MAX             | UNIT               |  |

|--------------------------------------|----------------------------------------------------------------------------------------------------------|-------|------|-----------------|--------------------|--|

| ANALOG INPUT                         | ,                                                                                                        |       |      | '               |                    |  |

| [1]                                  | Range 1                                                                                                  | 0     |      | Vref            | .,                 |  |

| Full-scale input span <sup>(1)</sup> | Range 2                                                                                                  | 0     |      | 2*Vref          | V                  |  |

| About the formation of               | Range 1                                                                                                  | -0.20 |      | VREF<br>+0.20   | V                  |  |

| Absolute input range                 | Range 2                                                                                                  | -0.20 |      | 2*VREF<br>+0.20 | V                  |  |

| Input capacitance                    |                                                                                                          |       | 15   |                 | ρF                 |  |

| Input leakage current                | T <sub>A</sub> = 125°C                                                                                   |       | 61   |                 | nA                 |  |

| SYSTEM PERFORMANCE                   | ,                                                                                                        |       |      |                 |                    |  |

| Resolution                           |                                                                                                          |       | 8    |                 | Bits               |  |

| No missing codes                     |                                                                                                          | 8     |      |                 | Bits               |  |

| Integral linearity                   |                                                                                                          | -0.3  | ±0.1 | 0.3             | LSB <sup>(2)</sup> |  |

| Differential linearity               |                                                                                                          | -0.3  | ±0.1 | 0.3             | LSB                |  |

| Offset error <sup>(3)</sup>          |                                                                                                          | -0.5  | ±0.2 | 0.5             | LSB                |  |

| Goin orror                           | Range 1                                                                                                  | -0.6  | ±0.1 | 0.6             | 1.00               |  |

| Gain error                           | Range 2                                                                                                  |       | ±0.1 |                 | LSB                |  |

| SAMPLING DYNAMICS                    | ,                                                                                                        |       |      | '               |                    |  |

| Conversion time                      | 20 MHz SCLK                                                                                              |       |      | 800             | nSec               |  |

| Acquisition time                     |                                                                                                          | 325   |      |                 | nSec               |  |

| Maximum throughput rate              | 20 MHz SCLK                                                                                              |       |      | 1.0             | MHz                |  |

| Aperture delay                       |                                                                                                          |       | 5    |                 | nsec               |  |

| Step response                        |                                                                                                          |       | 150  |                 | nsec               |  |

| Over voltage recovery                |                                                                                                          |       | 150  |                 | nsec               |  |

| DYNAMIC CHARACTERISTICS              |                                                                                                          |       |      |                 |                    |  |

| Total harmonic distortion (4)        | 100 kHz                                                                                                  |       | -75  |                 | dB                 |  |

| Signal-to-noise ratio                | 100 kHz                                                                                                  | 49    |      |                 | dB                 |  |

| Signal-to-noise + distortion         | 100 kHz                                                                                                  | 49    |      |                 |                    |  |

| Spurious free dynamic range          | 100 kHz                                                                                                  |       | -78  |                 | dB                 |  |

| Full power bandwidth                 | At –3 dB                                                                                                 |       | 47   |                 | MHz                |  |

|                                      | Any off-channel with 100kHz, Full-scale input to channel being sampled with DC input.                    |       | -95  |                 |                    |  |

| Channel-to-channel crosstalk         | From previously sampled to channel with 100kHz, Full-scale input to channel being sampled with DC input. |       | -85  |                 | dB                 |  |

| ETERNAL REFERENCE INPUT              |                                                                                                          |       |      |                 |                    |  |

| Vref reference voltage at REFP       |                                                                                                          | 2.49  | 2.5  | 2.51            | V                  |  |

| Reference resistance                 |                                                                                                          |       | 100  |                 | kΩ                 |  |

- (1) Ideal input span; does not include gain or offset error.

- (2) LSB means Least Significant Bit.

- (3) Measured relative to an ideal full-scale input

- 4) Calculated on the first nine harmonics of the input frequency.

# **ELECTRICAL CHARACTERISTICS, ADS7958/59/60/61 (continued)**

+VA = 2.7 V to 5.25 V, +VBD = 1.7 V to 5.25 V,  $T_A = -40 ^{\circ}\text{C}$  to  $125 ^{\circ}\text{C}$ ,  $f_{sample} = 1 \text{ MHz}$  (unless otherwise noted)

| PA              | RAMETER                | TEST CONDITIONS                             | MIN        | TYP     | MAX  | UNIT    |

|-----------------|------------------------|---------------------------------------------|------------|---------|------|---------|

| ALARM SETTI     | NG                     |                                             |            |         |      |         |

| Higher threshol | d range                |                                             | 000        |         | FF   | Hex     |

| Lower threshold | d range                |                                             | 000        |         | FF   | Hex     |

| DIGITAL INPU    | T/OUTPUT               |                                             |            |         |      |         |

| Logic family    |                        | CMOS                                        |            |         |      |         |

|                 | V <sub>IH</sub>        |                                             | 0.7*(+VBD) |         |      |         |

|                 | V <sub>IL</sub>        | +VBD = 5 V                                  |            |         | 0.8  |         |

| Logic level     | V <sub>IL</sub>        | +VBD = 3 V                                  |            |         | 0.4  | V       |

|                 | V <sub>OH</sub>        | At I <sub>source</sub> = 200 μA             | Vdd-0.2    |         |      |         |

|                 | V <sub>OL</sub>        | At I <sub>sink</sub> = 200 μA               | 0.4        |         |      |         |

| Data format     | 1                      |                                             | MSE        | 3 First |      |         |

| POWER SUPP      | LY REQUIREMENTS        |                                             |            |         |      |         |

| +VA supply vol  | tage                   |                                             | 2.7        | 3.3     | 5.25 | V       |

| +VBD supply ve  | oltage                 |                                             | 1.7        | 3.3     | 5.25 | V       |

|                 |                        | At +VA = 2.7 to 3.6 V and 1MHz throughput   |            | 1.8     |      | mA      |

| Cumply aurent   | (narmal mada)          | At +VA = 2.7 to 3.6 V static state          |            | 1.05    |      | mA      |

| Supply current  | (normal mode)          | At +VA = 4.7 to 5.25 V and 1 MHz throughput |            | 2.3     | 3    | mA      |

|                 |                        | At +VA = 4.7 to 5.25 V static state         |            | 1.1     | 1.5  | mA      |

| Power-down sta  | ate supply current     |                                             |            | 1       |      | μΑ      |

| +VBD supply co  | urrent                 | +VA = 5.25V, f <sub>s</sub> = 1MHz          |            | 1       |      | mA      |

| Power-up time   |                        |                                             |            |         | 1    | μSec    |

| Invalid convers | ions after power up or |                                             |            |         | 1    | Numbers |

| TEMPERATUR      | RE RANGE               |                                             |            |         |      |         |

| Specified perfo | rmance                 |                                             | -40        |         | 125  | °C      |

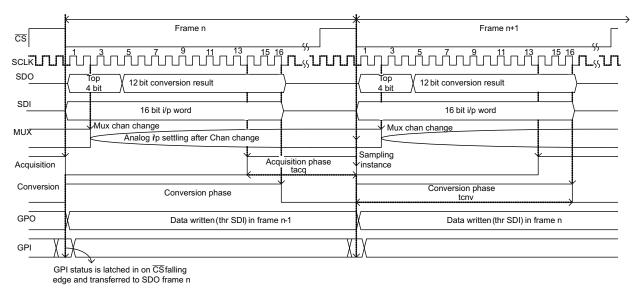

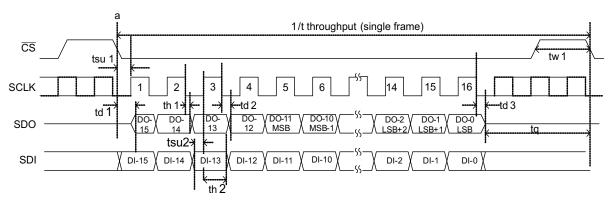

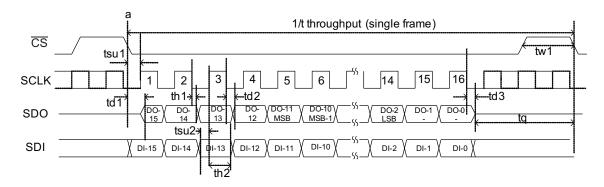

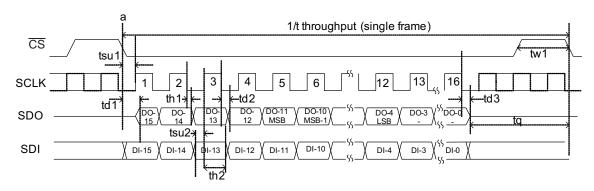

# TIMING REQUIREMENTS (see Figure 43, Figure 44, Figure 45, and Figure 46)

All specifications typical at -40°C to 125°C, +VA = 2.7 V to 5.25 V (unless otherwise specified)

|                   | PARAMETER                                                                          | TEST CONDITIONS (1)(2) | MIN | TYP | MAX | UNIT |

|-------------------|------------------------------------------------------------------------------------|------------------------|-----|-----|-----|------|

|                   |                                                                                    | +VBD = 1.8 V           |     |     | 16  |      |

| t <sub>conv</sub> | Conversion time                                                                    | +VBD = 3 V             |     |     | 16  | SCLK |

|                   |                                                                                    | +VBD = 5 V             |     |     | 16  |      |

|                   |                                                                                    | +VBD = 1.8 V           | 40  |     |     |      |

| tq                | Minimum quiet sampling time needed from bus<br>3-state to start of next conversion | +VBD = 3 V             | 40  |     |     | ns   |

|                   | 5 state to start of flext conversion                                               | +VBD = 5 V             | 40  |     |     |      |

|                   |                                                                                    | +VBD = 1.8 V           |     |     | 38  |      |

| t <sub>d1</sub>   | Delay time, $\overline{\text{CS}}$ low to first data (DO–15) out                   | +VBD = 3 V             |     |     | 27  | ns   |

|                   |                                                                                    | +VBD = 5 V             |     |     | 17  |      |

|                   |                                                                                    | +VBD = 1.8 V           |     |     | 8   |      |

| t <sub>su1</sub>  | Setup time, $\overline{\text{CS}}$ low to first rising edge of SCLK                | +VBD = 3 V             |     |     | 6   | ns   |

|                   |                                                                                    | +VBD = 5 V             |     |     | 4   |      |

|                   |                                                                                    | +VBD = 1.8 V           |     |     | 35  |      |

| t <sub>d2</sub>   | Delay time, SCLK falling to SDO next data bit valid                                | +VBD = 3 V             |     |     | 27  | ns   |

|                   |                                                                                    | +VBD = 5 V             |     |     | 17  |      |

<sup>(1) 1.8</sup>V specifications apply from 1.7V to 1.9V, 3V specifications apply from 2.7V to 3.6V, 5V specifications apply from 4.75V to 5.25V.

<sup>(2)</sup> With 50-pF load

# TIMING REQUIREMENTS (see Figure 43, Figure 44, Figure 45, and Figure 46) (continued)

All specifications typical at -40°C to 125°C, +VA = 2.7 V to 5.25 V (unless otherwise specified)

|                      | PARAMETER                                                     | TEST CONDITIONS (1)(2) | MIN | TYP | MAX | UNIT |  |  |  |  |

|----------------------|---------------------------------------------------------------|------------------------|-----|-----|-----|------|--|--|--|--|

|                      |                                                               | +VBD = 1.8 V           | 7   |     |     |      |  |  |  |  |

| t <sub>h1</sub>      | Hold time, SCLK falling to SDO data bit valid                 | +VBD = 3 V             | 5   |     |     | ns   |  |  |  |  |

|                      |                                                               | +VBD = 5 V             | 3   |     |     |      |  |  |  |  |

|                      |                                                               | +VBD = 1.8 V           |     |     | 26  |      |  |  |  |  |

| $t_{d3}$             | Delay time, 16 <sup>th</sup> SCLK falling edge to SDO 3-state | +VBD = 3 V             |     |     | 22  | ns   |  |  |  |  |

|                      |                                                               | +VBD = 5 V             |     |     | 13  |      |  |  |  |  |

|                      |                                                               | +VBD = 1.8 V           |     |     | 2   |      |  |  |  |  |

| t <sub>su2</sub> Set | Setup time, SDI valid to rising edge of SCLK                  | +VBD = 3 V             |     |     | 3   | ns   |  |  |  |  |

|                      |                                                               | +VBD = 5 V             |     |     | 4   |      |  |  |  |  |

| t <sub>h2</sub>      |                                                               | +VBD = 1.8 V           | 12  |     |     |      |  |  |  |  |

|                      | Hold time, rising edge of SCLK to SDI valid                   | +VBD = 3 V             | 10  |     |     | ns   |  |  |  |  |

|                      |                                                               | +VBD = 5 V             | 6   |     |     |      |  |  |  |  |

|                      |                                                               | +VBD = 1.8 V           | 20  |     |     |      |  |  |  |  |

| t <sub>w1</sub>      | Pulse duration CS high                                        | +VBD = 3 V             | 20  |     |     | ns   |  |  |  |  |

|                      |                                                               | +VBD = 5 V             | 20  |     |     |      |  |  |  |  |

|                      |                                                               | +VBD = 1.8 V           |     | 24  |     |      |  |  |  |  |

| $t_{d4}$             | Delay time CS high to SDO 3-state                             | +VBD = 3 V             |     |     | 21  | +    |  |  |  |  |

|                      |                                                               | +VBD = 5 V             |     |     | 12  |      |  |  |  |  |

|                      |                                                               | +VBD = 1.8 V           | 20  |     |     |      |  |  |  |  |

| t <sub>wh</sub>      | Pulse duration SCLK high                                      | +VBD = 3 V             | 20  |     |     | ns   |  |  |  |  |

|                      |                                                               | +VBD = 5 V             | 20  |     |     |      |  |  |  |  |

|                      |                                                               | +VBD = 1.8 V           | 20  |     |     |      |  |  |  |  |

| t <sub>wl</sub>      | Pulse duration SCLK low                                       | +VBD = 3 V             | 20  |     |     | ns   |  |  |  |  |

|                      |                                                               | +VBD = 5 V             | 20  |     |     |      |  |  |  |  |

|                      |                                                               | +VBD = 1.8 V           |     |     | 20  |      |  |  |  |  |

|                      | Frequency SCLK                                                | +VBD = 3 V             |     |     | 20  | MHz  |  |  |  |  |

|                      |                                                               | +VBD = 5 V             |     |     | 20  |      |  |  |  |  |

### **DEVICE INFORMATION**

# **PIN CONFIGURATION (TOP VIEW)**

| GPIO2 1            |                    | 38 | GPIO1 | GPIO2 1 |                    | 38 | GPIO1 |     |

|--------------------|--------------------|----|-------|---------|--------------------|----|-------|-----|

| GPIO3 <sup>2</sup> |                    | 37 | GPIO0 | GPIO3 2 |                    | 37 | GPIO0 |     |

| REFM 3             |                    | 36 | +VBD  | REFM 3  |                    | 36 | +VBD  |     |

| REFP 4             |                    | 35 | BDGND | REFP 4  |                    | 35 | BDGND |     |

| +VA 5              |                    | 34 | SDO   | +VA 5   |                    | 34 | SDO   |     |

| AGND 6             |                    | 33 | SDI   | AGND 6  |                    | 33 | SDI   |     |

| MXO 7              |                    | 32 | SCLK  | MXO 7   |                    | 32 | SCLK  |     |

| AINP 8             |                    | 31 | CS    | AINP 8  |                    | 31 | CS    |     |

| AINM 9             |                    | 30 | VEE   | AINM 9  |                    | 30 | VEE   |     |

| AGND 10            | ADS7952            | 29 | VCC   | AGND 10 | ADS7953            | 29 | VCC   |     |

| NC 🔟               | ADS7956<br>ADS7960 | 28 | CH0   | CH15 11 | ADS7957<br>ADS7961 | 28 | CH0   |     |

| NC 12              |                    | 27 | CH1   | CH14 12 |                    | 27 | CH1   |     |

| NC 13              |                    | 26 | CH2   | CH13 13 |                    | 26 | CH2   |     |

| NC 14              |                    | 25 | CH3   | CH12 14 |                    | 25 | CH3   |     |

| CH11 15            |                    | 24 | CH4   | CH11 15 |                    | 24 | CH4   |     |

| CH10 16            |                    | 23 | CH5   | CH10 16 |                    | 23 | CH5   |     |

| CH9 17             |                    |    | 22    | CH6     | CH9 17             |    | 22    | CH6 |

| CH8 🖽              |                    | 21 | CH7   | CH8 18  |                    | 21 | CH7   |     |

| AGND 19            |                    | 20 | AGND  | AGND 19 |                    | 20 | AGND  |     |

|                    |                    |    |       |         |                    |    |       |     |

# **TERMINAL FUNCTIONS**

|                               | DEVIC                         | E NAME                        |                               |          |     |                                 |  |  |  |  |

|-------------------------------|-------------------------------|-------------------------------|-------------------------------|----------|-----|---------------------------------|--|--|--|--|

| ADS7953<br>ADS7957<br>ADS7961 | ADS7952<br>ADS7956<br>ADS7960 | ADS7951<br>ADS7955<br>ADS7959 | ADS7950<br>ADS7954<br>ADS7958 | PIN NAME | 1/0 | FUNCTION                        |  |  |  |  |

|                               | PIN                           | NO.                           |                               |          |     |                                 |  |  |  |  |

| REFERENCI                     | Ē                             |                               |                               |          |     |                                 |  |  |  |  |

| 4                             | 4                             | 4                             | 4                             | REFP     | I   | Reference input                 |  |  |  |  |

| 3                             | 3                             | 3                             | 3                             | REFM     | 1   | Reference ground                |  |  |  |  |

| ADC ANALO                     | G INPUT                       |                               |                               |          |     |                                 |  |  |  |  |

| 8                             | 8                             | 8                             | 8                             | AINP     | I   | Signal input to ADC             |  |  |  |  |

| 9                             | 9                             | 9                             | 9                             | AINM     | I   | ADC input ground                |  |  |  |  |

| MULTIPLEX                     | ER                            |                               |                               |          |     |                                 |  |  |  |  |

| 7                             | 7                             | 7                             | 7                             | MXO      | 0   | Multiplexer output              |  |  |  |  |

| 28                            | 28                            | 20                            | 20                            | Ch0      | I   | Analog channels for multiplexer |  |  |  |  |

| 27                            | 27                            | 19                            | 18                            | Ch1      | I   |                                 |  |  |  |  |

| 26                            | 26                            | 18                            | 14                            | Ch2      | I   |                                 |  |  |  |  |

| 25                            | 25                            | 17                            | 12                            | Ch3      | I   |                                 |  |  |  |  |

| 24                            | 24                            | 14                            | -                             | Ch4      | I   |                                 |  |  |  |  |

| 23                            | 23                            | 13                            | -                             | Ch5      | I   |                                 |  |  |  |  |

| 22                            | 22                            | 12                            | -                             | Ch6      | I   |                                 |  |  |  |  |

| 21                            | 21                            | 11                            | -                             | Ch7      | I   |                                 |  |  |  |  |

| 18                            | 18                            | -                             | -                             | Ch8      | I   |                                 |  |  |  |  |

| 17                            | 17                            | -                             | -                             | Ch9      | I   |                                 |  |  |  |  |

| 16                            | 16                            | -                             | -                             | Ch10     | I   |                                 |  |  |  |  |

| 15                            | 15                            | -                             | -                             | Ch11     | I   |                                 |  |  |  |  |

| 14                            | -                             | -                             | -                             | Ch12     | I   |                                 |  |  |  |  |

| 13                            | -                             | -                             | -                             | Ch13     | I   |                                 |  |  |  |  |

| 12                            | -                             | -                             | -                             | Ch14     | I   |                                 |  |  |  |  |

| 11                            | -                             | -                             | -                             | Ch15     | I   |                                 |  |  |  |  |

| DIGITAL CO                    | NTROL SIGN                    | NALS                          | •                             | ·        |     |                                 |  |  |  |  |

| 31                            | 31                            | 23                            | 23                            | CS       | I   | Chip select input               |  |  |  |  |

# **TERMINAL FUNCTIONS (continued)**

|                               | DEVIC                         | E NAME                        |                               |                                    |            |                                                                                     |

|-------------------------------|-------------------------------|-------------------------------|-------------------------------|------------------------------------|------------|-------------------------------------------------------------------------------------|

| ADS7953<br>ADS7957<br>ADS7961 | ADS7952<br>ADS7956<br>ADS7960 | ADS7951<br>ADS7955<br>ADS7959 | ADS7950<br>ADS7954<br>ADS7958 | PIN NAME                           | I/O        | FUNCTION                                                                            |

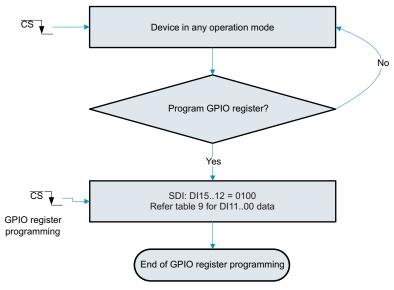

|                               | PIN                           | NO.                           |                               |                                    |            |                                                                                     |