# DC-to-2.5 GHz High IP3 Active Mixer

AD8343

### **FEATURES**

High-Performance Active Mixer Broadband Operation to 2.5 GHz Conversion Gain: 7.1 dB

Input IP3: 16.5 dBm LO Drive: -10 dBm Noise Figure: 14.1 dB Input P1 dB: 2.8 dBm

Differential LO, IF and RF Ports 50 Ω LO Input Impedance

Single-Supply Operation: 5 V @ 50 mA Typical

Power-Down Mode @ 20 μA Typical

APPLICATIONS

Cellular Base Stations

Wireless LAN

Satellite Converters

SONET/SDH Radio

Radio Links

RF Instrumentation

### PRODUCT DESCRIPTION

The AD8343 is a high-performance broadband active mixer. Having wide bandwidth on all ports and very low intermodulation distortion, the AD8343 is well suited for demanding transmit or receive channel applications.

The AD8343 provides a typical conversion gain of 7.1 dB. The integrated LO driver supports a 50  $\Omega$  differential input impedance with low LO drive level, helping to minimize external component count.

The open-emitter differential inputs may be interfaced directly to a differential filter or driven through a balun (transformer) to provide a balanced drive from a single-ended source.

The open-collector differential outputs may be used to drive a differential IF signal interface or converted to a single-ended signal through the use of a matching network or transformer. When centered on the VPOS supply voltage, the outputs may swing  $\pm 1~\rm V$ .

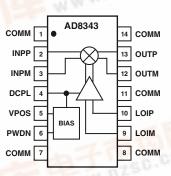

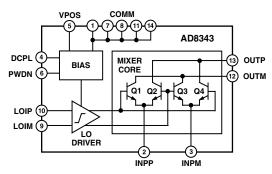

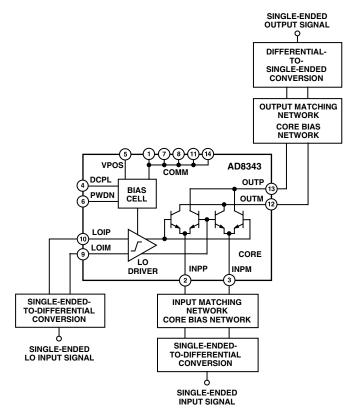

#### **FUNCTIONAL BLOCK DIAGRAM**

The LO driver circuitry typically consumes 15 mA of current. Two external resistors are used to set the mixer core current for required performance resulting in a total current of 20 mA to 60 mA. This corresponds to power consumption of 100 mW to 300 mW with a single 5 V supply.

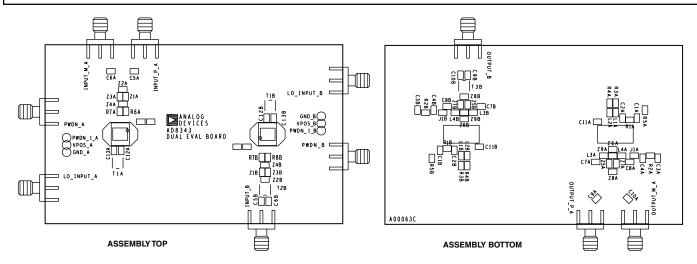

The AD8343 is fabricated on Analog Devices' proprietary, high-performance 25 GHz silicon bipolar IC process. The AD8343 is available in a 14-lead TSSOP package. It operates over a -40°C to +85°C temperature range. A device-populated evaluation board is available to facilitate device matching.

# AD8343—SPECIFICATIONS

# BASIC OPERATING CONDITIONS ( $V_S = 5.0 \text{ V}, \, T_A = 25^{\circ}\text{C}$ )

| Parameter                                                                                                                                                                                     | Conditions                                                                                                                  | Figure        | Min                  | Typ                                                                 | Max                                | Unit                                                       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|---------------|----------------------|---------------------------------------------------------------------|------------------------------------|------------------------------------------------------------|

| INPUT INTERFACE (INPP, INPM) Differential Open Emitter DC Bias Voltage Operating Current Each Input (I <sub>O</sub> ) Value of Bias Setting Resistor <sup>1</sup> Port Differential Impedance | Internally Generated<br>Current Set by R3, R4<br>1% Bias Resistors; R3, R4<br>$f = 50$ MHz; R3 and R4 = $68.1 \Omega$       | 24<br>24<br>9 | 1.1                  | 1.2<br>16<br>68.1<br>2.7 + j 6.8                                    | 1.3<br>20                          | $\begin{array}{c} V \\ mA \\ \Omega \\ \Omega \end{array}$ |

| OUTPUT INTERFACE (OUTP, OUTM) Differential Open Collector DC Bias Voltage Voltage Swing Operating Current Each Output Port Differential Impedance                                             | Externally Applied  Same as Input Current f = 50 MHz                                                                        | 12            | 4.5<br>1.65          | $\begin{array}{c} 5 \\ V_S \pm 1 \\ I_O \\ 900 - j  77 \end{array}$ | 5.5<br>V <sub>S</sub> + 2          | V<br>V<br>mA                                               |

| LO INTERFACE (LOIP, LOIM) Differential Common Base Stage DC Bias Voltage <sup>2</sup> LO Input Power Port Differential Return Loss                                                            | Internally Generated; Port<br>Typically AC-Coupled<br>50 Ω Impedance                                                        | 17<br>16      | 300<br>-12           | 360<br>-10<br>-10                                                   | 450<br>-3                          | mV<br>dBm<br>dB                                            |

| POWER-DOWN INTERFACE (PWDN) PWDN Threshold  PWDN Response Time <sup>3</sup> PWDN Input Bias Current                                                                                           | Assured ON Assured OFF Time from Device ON to OFF Time from Device OFF to ON PWDN = 0 V (Device ON) PWDN = 5 V (Device OFF) | 4 5           | V <sub>S</sub> - 0.5 | 2.2<br>500<br>-85<br>0                                              | V <sub>S</sub> - 1.5               | V<br>V<br>μs<br>ns<br>μA<br>μA                             |

| POWER SUPPLY Supply Voltage Range Total Quiescent Current Powered-Down Current                                                                                                                | R3 and R4 = $68.1 \Omega$<br>Over Temperature<br>$V_S = 5.5 V$<br>$V_S = 4.5 V$<br>Over Temperature, $V_S = 5.5 V$          | 24            | 4.5                  | 5.0<br>50<br>20<br>6<br>50                                          | 5.5<br>60<br>75<br>95<br>15<br>150 | V<br>mA<br>mA<br>μA<br>μA<br>μA                            |

Specifications subject to change without notice.

NOTES

1 The balance in the bias current in the two legs of the mixer input may be important in applications were a low feedthrough of the LO is critical.

1 The balance in the bias current in the two legs of the mixer input may be important in applications were a low feedthrough of the LO is critical.

1 The balance in the bias current in the two legs of the mixer input may be important in applications were a low feedthrough of the LO is critical.

<sup>&</sup>lt;sup>2</sup>This voltage is proportional to absolute temperature (PTAT). Reference section on DC-Coupling the LO for more information regarding this interface.

<sup>&</sup>lt;sup>3</sup>Response time until device meets all specified conditions.

# Table I. Typical AC Performance ( $V_S = 5.0 \text{ V}$ , $T_A = 25^{\circ}\text{C}$ ; See Figure 24 and Tables III Through V.)

| Input Frequency (MHz) | Output Frequency<br>(MHz) | Conversion Gain (dB) | SSB Noise Figure (dB) | Input IP3 (dBm) | Input 1 dB<br>Compression Point<br>(dBm) |

|-----------------------|---------------------------|----------------------|-----------------------|-----------------|------------------------------------------|

| RECEIVER CHAR         | ACTERISTICS               |                      |                       |                 |                                          |

| 400                   | 70                        | 5.6                  | 10.5                  | 20.5            | 3.3                                      |

| 900                   | 170                       | 3.6                  | 11.4                  | 19.4            | 3.6                                      |

| 1900                  | 170                       | 7.1                  | 14.1                  | 16.5            | 2.8                                      |

| 2400                  | 170                       | 6.8                  | 15.3                  | 14.5            | 2.1                                      |

| 2400                  | 425                       | 5.4                  | 16.2                  | 16.5            | 2.2                                      |

| TRANSMITTER C         | CHARACTERISTICS           |                      |                       |                 |                                          |

| 150                   | 900                       | 7.5                  | 17.9                  | 18.1            | 1.9                                      |

| 150                   | 1900                      | 0.25                 | 16.0                  | 13.4            | 0.8                                      |

# Table II. Typical Isolation Performance ( $V_S$ = 5.0 V, $T_A$ = 25°C; See Figure 24 and Tables III Through V.)

| Input Frequency<br>(MHz) | Output Frequency<br>(MHz) | LO to Output<br>Leakage (dBm) | 2 × LO to Output<br>Leakage (dBm) | 3 × LO to Output<br>Leakage (dBm) | Input to Output<br>Leakage (dBm) |

|--------------------------|---------------------------|-------------------------------|-----------------------------------|-----------------------------------|----------------------------------|

| RECEIVER CHAR            | ACTERISTICS               |                               |                                   |                                   |                                  |

| 400                      | 70                        | -40.1                         | -51.0                             | -44.0                             | -62.4                            |

| 900                      | 170                       | -44.4                         | -35.5                             | < -75.0                           | -56.9                            |

| 1900                     | 170                       | -65.6                         | -38.3                             | -73.3                             | -65.7                            |

| 2400                     | 170                       | -66.7                         | -44.4                             | < -75.0                           | -73.7                            |

| 2400                     | 425                       | -51.1                         | -49.4                             | < -75.0                           | -52.3                            |

| TRANSMITTER C            | CHARACTERISTICS           |                               |                                   |                                   |                                  |

| 150                      | 900                       | -27.6                         | < -75 dBm                         | < -75 dBm                         | -35.3                            |

| 150                      | 1900                      | < -75 dBm                     | < -75 dBm                         | < -75 dBm                         | -69.7                            |

NOTE: Low-side LO injection used for typical performance.

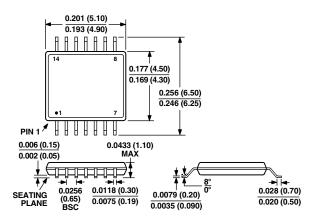

### ABSOLUTE MAXIMUM RATINGS<sup>1</sup>

| VPOS Quiescent Voltage 5.5 V                           |

|--------------------------------------------------------|

| OUTP, OUTM Quiescent Voltage 5.5 V                     |

| INPP, INPM Voltage Differential 500 mV                 |

| Internal Power Dissipation (TSSOP) <sup>2</sup> 320 mW |

| $\theta_{JA}$ (TSSOP)                                  |

| Maximum Junction Temperature 125°C                     |

| Operating Temperature Range40°C to +85°C               |

| Storage Temperature Range65°C to +150°C                |

| Lead Temperature Range (Soldering 60 sec) 300°C        |

|                                                        |

#### NOTES

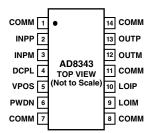

#### PIN CONFIGURATION

### **ORDERING GUIDE**

| Model                                                         | Temperature Range | Package Description   | Package Option                                                     |

|---------------------------------------------------------------|-------------------|-----------------------|--------------------------------------------------------------------|

| AD8343ARU<br>AD8343ARU-REEL<br>AD8343ARU-REEL7<br>AD8343-EVAL | −40°C to +85°C    | 14-Lead Plastic TSSOP | RU-14<br>13" Tape and Reel<br>7" Tape and Reel<br>Evaluation Board |

<sup>&</sup>lt;sup>1</sup>Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may effect device reliability.

$<sup>^2\!</sup>A$  portion of the device power is dissipated by the external bias resistors R3 and R4.

## PIN FUNCTION DESCRIPTIONS

| TSSOP              | Name                | Function                                                                                                                                            | Simplified Interface Schematic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2, 3               | INPP/INPM OUTP/OUTM | Differential input pins. Need to be dc-biased; typically ac-coupled.  Open collector differential output pins. Need to be ac-coupled and dc-biased. | VPOS 5V <sub>DC</sub> 5V <sub>DC</sub> 5V <sub>DC</sub> 1.2V |

| 9, 10              | LOIP/LOIM           | Differential local oscillator (LO) input pins. Typically ac-coupled.                                                                                | LOIP $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 6                  | PWDN                | Power-down interface. Connect pin to ground for normal operating mode. Connect pin to supply for power-down mode.                                   | VPOS 5V <sub>DC</sub> PWDN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4                  | DCPL                | Bias rail decoupling capacitor connection for LO Driver.                                                                                            | DCPL DCPL DCPL DCPL DCPL DCPL DCPL DCPL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 5                  | VPOS                | Positive supply voltage ( $V_S$ ), 4.5 V to 5.5 V. Ensure adequate supply bypassing for proper device operation as shownin Figure 24.               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1, 7, 8,<br>11, 14 | COMM                | Connect to low impedance circuit ground.                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

#### CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD8343 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high-energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

# **Typical Performance Characteristics—AD8343**

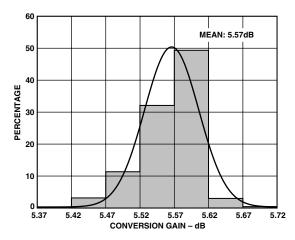

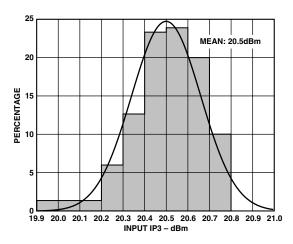

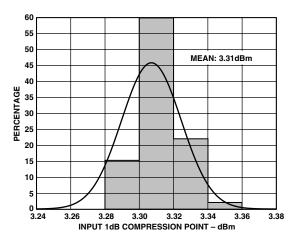

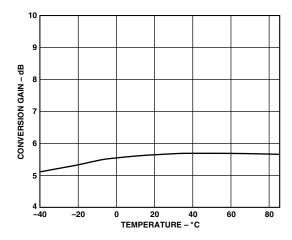

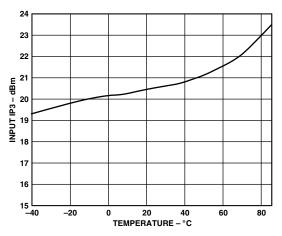

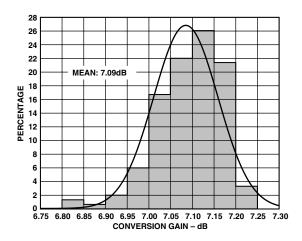

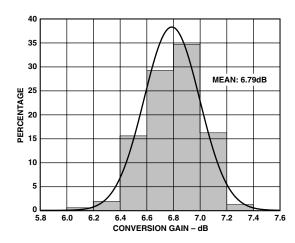

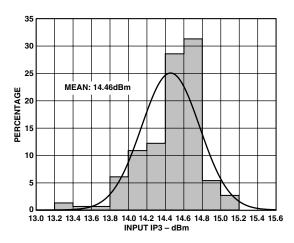

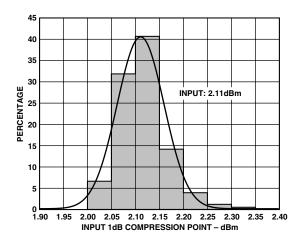

RECEIVER CHARACTERISTICS ( $f_{IN}$  = 400 MHz,  $f_{OUT}$  = 70 MHz,  $f_{LO}$  = 330 MHz [Figure 24, Tables III and IV])

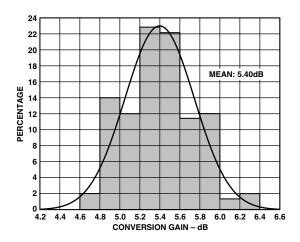

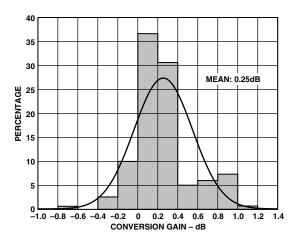

TPC 1. Gain Histogram  $f_{IN}$  = 400 MHz,  $f_{OUT}$  = 70 MHz

TPC 2. Input IP3 Histogram  $f_{IN} = 400$  MHz,  $f_{OUT} = 70$  MHz

TPC 3. Input 1 dB Compression Point Histogram  $f_{\rm IN} = 400$  MHz,  $f_{\rm OUT} = 70$  MHz

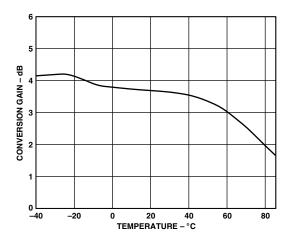

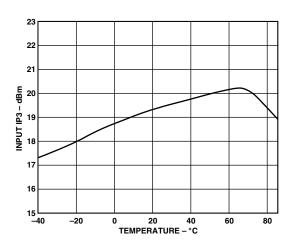

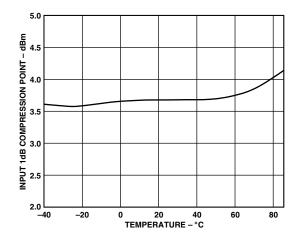

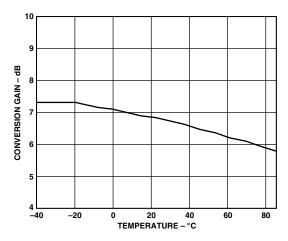

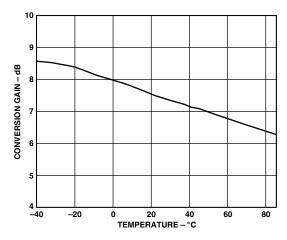

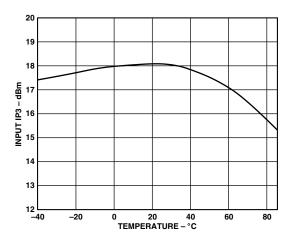

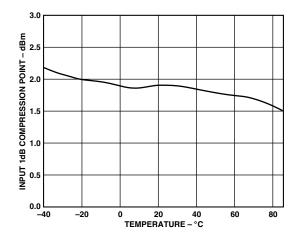

TPC 4. Gain Performance Over Temperature  $f_{\text{IN}} = 400 \text{ MHz}, f_{\text{OUT}} = 70 \text{ MHz}$

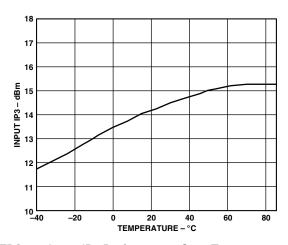

TPC 5. Input IP3 Performance Over Temperature  $f_{\rm IN} = 400~{\rm MHz}, \, f_{\rm OUT} = 70~{\rm MHz}$

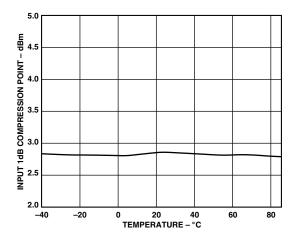

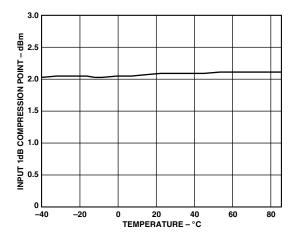

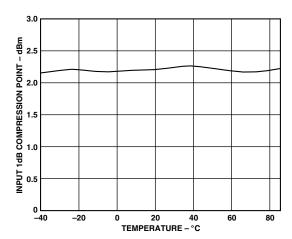

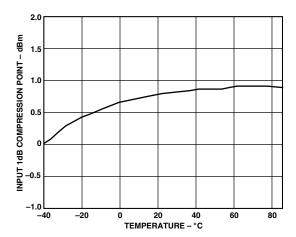

TPC 6. Input 1 dB Compression Point Performance Over Temperature ( $f_{\rm IN}$  = 400 MHz,  $f_{\rm OUT}$  = 70 MHz )

RECEIVER CHARACTERISTICS ( $f_{IN}$  = 900 MHz,  $f_{OUT}$  = 170 MHz,  $f_{LO}$  = 730 MHz [Figure 24, Tables III and IV])

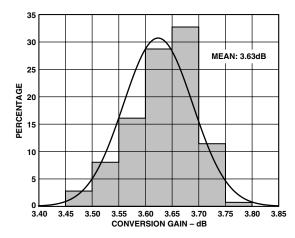

TPC 7. Gain Histogram  $f_{IN} = 900$  MHz,  $f_{OUT} = 170$  MHz

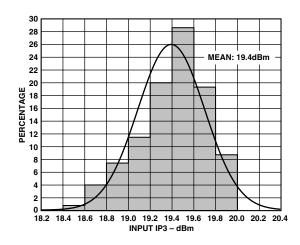

TPC 8. Input IP3 Histogram  $f_{IN} = 900$  MHz,  $f_{OUT} = 170$  MHz

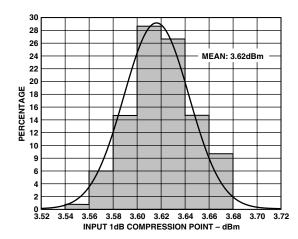

TPC 9. Input 1 dB Compression Point Histogram  $f_{\rm IN} = 900$  MHz,  $f_{\rm OUT} = 170$  MHz

TPC 10. Gain Performance Over Temperature  $f_{\text{IN}} = 900 \text{ MHz}, f_{\text{OUT}} = 170 \text{ MHz}$

TPC 11. Input IP3 Performance Over Temperature  $f_{\text{IN}}$  = 900 MHz,  $f_{\text{OUT}}$  = 170 MHz

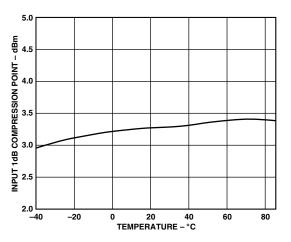

TPC 12. Input 1 dB Compression Point Performance Over Temperature  $f_{\rm IN}$  = 900 MHz,  $f_{\rm OUT}$  = 170 MHz

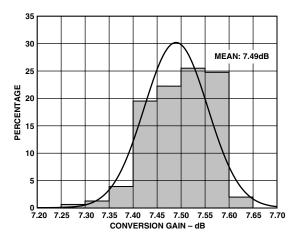

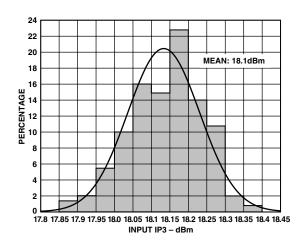

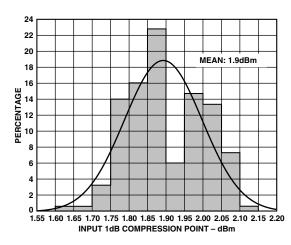

## RECEIVER CHARACTERISTICS ( $f_{IN}$ = 1900 MHz, $f_{OUT}$ = 170 MHz, $f_{LO}$ = 1730 MHz [Figure 24, Tables III and IV])

TPC 13. Gain Histogram  $f_{IN} = 1900 \text{ MHz}$ ,  $f_{OUT} = 170 \text{ MHz}$

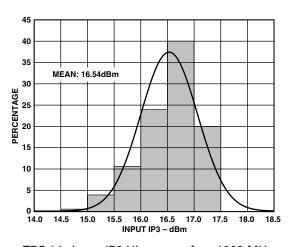

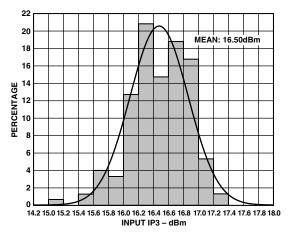

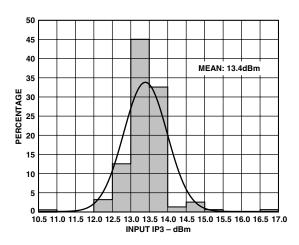

TPC 14. Input IP3 Histogram  $f_{\rm IN}$  = 1900 MHz,  $f_{\rm OUT}$  = 170 MHz

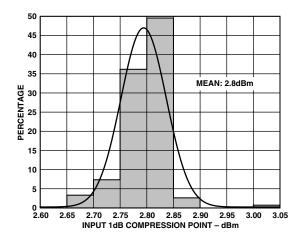

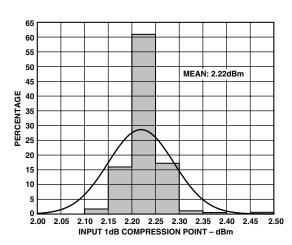

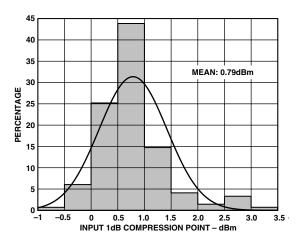

TPC 15. Input 1 dB Compression Point Histogram  $f_{\rm IN} = 1900$  MHz,  $f_{\rm OUT} = 170$  MHz

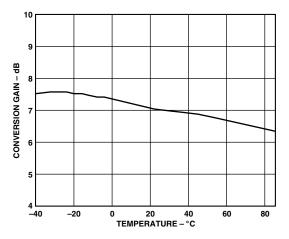

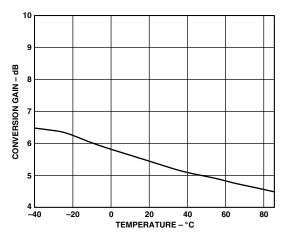

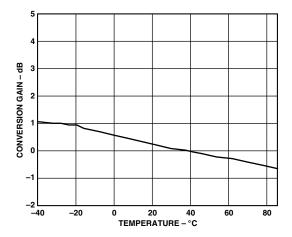

TPC 16. Gain Performance Over Temperature  $f_{IN} = 1900 \text{ MHz}$ ,  $f_{OUT} = 170 \text{ MHz}$

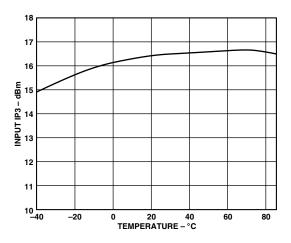

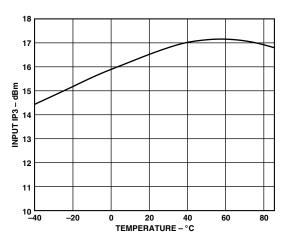

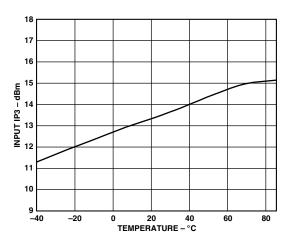

TPC 17. Input IP3 Performance Over Temperature  $f_{\rm IN}$  = 1900 MHz,  $f_{\rm OUT}$  = 170 MHz

TPC 18. Input 1 dB Compression Point Performance Over Temperature  $f_{\text{IN}}$  = 1900 MHz,  $f_{\text{OUT}}$  = 170 MHz

RECEIVER CHARACTERISTICS ( $f_{IN} = 2400 \text{ MHz}$ ,  $f_{OUT} = 170 \text{ MHz}$ ,  $f_{LO} = 2230 \text{ MHz}$  [Figure 24, Tables III and IV])

TPC 19. Gain Histogram  $f_{IN} = 2400 \text{ MHz}$ ,  $f_{OUT} = 170 \text{ MHz}$

TPC 20. Input IP3 Histogram  $f_{IN}$  = 2400 MHz,  $f_{OUT}$  = 170 MHz

TPC 21. Input 1 dB Compression Point Histogram  $f_{\rm IN} = 2400$  MHz,  $f_{\rm OUT} = 170$  MHz

TPC 22. Gain Performance Over Temperature  $f_{IN} = 2400 \text{ MHz}$ ,  $f_{OUT} = 170 \text{ MHz}$

TPC 23. Input IP3 Performance Over Temperature  $f_{\rm IN} = 2400$  MHz,  $f_{\rm OUT} = 170$  MHz

TPC 24. Input 1 dB Compression Point Performance Over Temperature  $f_{\rm IN}$  = 2400 MHz,  $f_{\rm OUT}$  = 170 MHz

## RECEIVER CHARACTERISTICS ( $f_{IN} = 2400 \text{ MHz}$ , $f_{OUT} = 425 \text{ MHz}$ , $f_{LO} = 1975 \text{ MHz}$ [Figure 24, Tables III and IV])

TPC 25. Gain Histogram  $f_{IN} = 2400$  MHz,  $f_{OUT} = 425$  MHz

TPC 26. Input IP3 Histogram  $f_{IN}$  = 2400 MHz,  $f_{OUT}$  = 425 MHz

TPC 27. Input 1 dB Compression Point Histogram  $f_{\text{IN}} = 2400 \text{ MHz}, f_{\text{OUT}} = 425 \text{ MHz}$

TPC 28. Gain Performance Over Temperature  $f_{IN} = 2400 \text{ MHz}$ ,  $f_{OUT} = 425 \text{ MHz}$

TPC 29. Input IP3 Performance Over Temperature  $f_{\text{IN}} = 2400 \text{ MHz}, f_{\text{OUT}} = 425 \text{ MHz}$

TPC 30. Input 1 dB Compression Point Performance Over Temperature  $f_{\rm IN}$  = 2400 MHz,  $f_{\rm OUT}$  = 425 MHz

TRANSMIT CHARACTERISTICS ( $f_{IN}$  = 150 MHz,  $f_{OUT}$  = 900 MHz,  $f_{LO}$  = 750 MHz [Figure 24, Tables III and IV])

TPC 31. Gain Histogram  $f_{IN} = 150$  MHz,  $f_{OUT} = 900$  MHz

TPC 32. Input IP3 Histogram  $f_{IN} = 150$  MHz,  $f_{OUT} = 900$  MHz

TPC 33. Input 1 dB Compression Point Histogram  $f_{\rm IN}$  = 150 MHz,  $f_{\rm OUT}$  = 900 MHz

TPC 34. Gain Performance Over Temperature  $f_{\rm IN} = 150$  MHz,  $f_{\rm OUT} = 900$  MHz

TPC 35. Input IP3 Performance Over Temperature  $f_{\rm IN} = 150$  MHz,  $f_{\rm OUT} = 900$  MHz

TPC 36. Input 1 dB Compression Point Performance Over Temperature  $f_{\rm IN}$  = 150 MHz,  $f_{\rm OUT}$  = 900 MHz

## TRANSMIT CHARACTERISTICS ( $f_{IN}$ = 150 MHz, $f_{OUT}$ = 1900 MHz, $f_{LO}$ = 1750 MHz [Figure 24, Tables III and IV])

TPC 37. Gain Histogram  $f_{IN} = 150$  MHz,  $f_{OUT} = 1900$  MHz

TPC 38. Input IP3 Histogram  $f_{IN} = 150$  MHz,  $f_{OUT} = 1900$  MHz

TPC 39. Input 1 dB Compression Point Histogram  $f_{\rm IN}$  = 150 MHz,  $f_{\rm OUT}$  = 1900 MHz

TPC 40. Gain Performance Over Temperature  $f_{\text{IN}} = 150 \text{ MHz}$ ,  $f_{\text{OUT}} = 1900 \text{ MHz}$

TPC 41. Input IP3 Performance Over Temperature  $f_{IN} = 150 \text{ MHz}$ ,  $f_{OUT} = 1900 \text{ MHz}$

TPC 42. Input 1 dB Compression Point Performance Over Temperature  $f_{IN}$  = 150 MHz,  $f_{OUT}$  = 1900 MHz

#### CIRCUIT DESCRIPTION

The AD8343 is a mixer intended for high-intercept applications. The signal paths are entirely differential and dc-coupled to permit high-performance operation over a broad range of frequencies; the block diagram (Figure 1) shows the basic functional blocks. The bias cell provides a PTAT (proportional to absolute temperature) bias to the LO Driver and Core. The LO Driver consists of a three-stage limiting differential amplifier that provides a very fast (almost square-wave) drive to the bases of the core transistors.

The AD8343 core utilizes a standard architecture in which the signal inputs are directly applied to the emitters of the transistors in the cell (Figure 7). The bases are driven by the hard-limited LO signal that directs the transistors to steer the input currents into periodically alternating pairs of output terminals, thus providing the periodic polarity reversal that effectively multiplies the signal by a square wave of the LO frequency.

Figure 1. Topology

To illustrate this functionality, when LOIP is positive, Q1 and Q4 are turned ON, and Q2 and Q3 are turned OFF. In this condition Q1 connects  $I_{\rm INPP}$  to OUTM and Q4 connects  $I_{\rm INPM}$  to OUTP. When LOIP is negative the roles of the transistors reverse, steering  $I_{\rm INPP}$  to OUTP and  $I_{\rm INPM}$  to OUTM. Isolation and gain are possible because at any instant the signal passes through a common-base transistor amplifier pair.

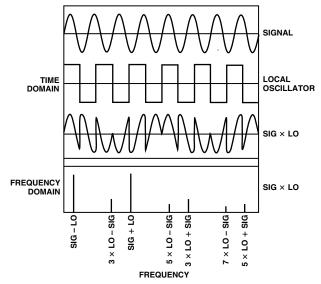

Multiplication is the essence of frequency mixing; an *ideal* multiplier would make an excellent mixer. The theory is expressed in the following trigonometric identity:

$$sin(\omega_{sip}t)sin(\omega_{LO}t) = 1/2 \left[cos(\omega_{sip}t - \omega_{LO}t) - cos(\omega_{sip}t + \omega_{LO}t)\right]$$

This states that the product of two sine-wave signals of different frequencies is a pair of sine waves at frequencies equal to the sum and difference of the two frequencies being multiplied.

Unfortunately, practical implementations of analog multipliers generally make poor mixers because of imperfect linearity and because of the added noise that invariably accompanies attempts to improve linearity. The best mixers to date have proven to be those that use the LO signal to periodically reverse the polarity of the input signal.

In this class of mixers, frequency conversion occurs as a result of multiplication of the signal by a square wave at the LO frequency. Because a square wave contains odd harmonics in addition to the fundamental, the signal is effectively multiplied by each frequency component of the LO. The output of the mixer will therefore contain signals at  $F_{LO}\pm F_{sig}$ ,  $3\times F_{LO}\pm F_{sig}$ ,  $5\times F_{LO}\pm F_{sig}$ ,  $7\times F_{LO}\pm F_{sig}$ , etc. The amplitude of the components arising from signal multiplication by LO harmonics falls off with increasing harmonic order because the amplitude of a square wave's harmonics falls off.

An example of this process is illustrated in Figure 2. The first pane of this figure shows an 800 MHz sinusoid intended to represent an input signal. The second pane contains a square wave representing an LO signal at 600 MHz which has been hard-limited by the internal LO driver. The third pane shows the time domain representation of the output waveform and the fourth pane shows the frequency domain representation. The two strongest lines in the spectrum are the sum and difference frequencies arising from multiplication of the signal by the LO's fundamental frequency. The weaker spectral lines are the result of the multiplication of the signal by various harmonics of the LO square wave.

Figure 2. Signal Switching Characteristics of the AD8343

#### **DC INTERFACES**

## Biasing and Decoupling (VPOS, DCPL)

VPOS is the power supply connection for the internal bias circuit and the LO driver. This pin should be closely bypassed to GND with a capacitor in the range of 0.01  $\mu$ F to 0.1  $\mu$ F. The DCPL pin provides access to an internal bias node for noise bypassing purposes. This node should be bypassed to COMM with 0.1  $\mu$ F.

### Power-Down Interface (PWDN)

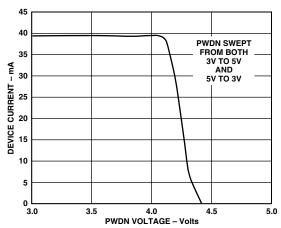

The AD8343 is active when the PWDN pin is held low; otherwise the device enters a low-power state as shown in Figure 3.

Figure 3. Bias Current vs. PWDN Voltage

To assure full power-down, the PWDN voltage should be within 0.5 V of the supply voltage at VPOS. Normal operation requires that the PWDN pin be taken at least 1.5 V below the supply voltage. The PWDN pin sources about 100  $\mu$ A when pulled to GND (refer to Pin Function Descriptions). It is not advisable to leave the pin floating when the device is to be disabled; a resistive pull-up to VPOS is the minimum suggestion.

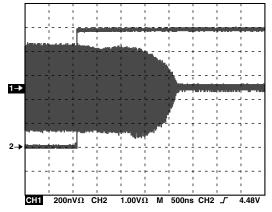

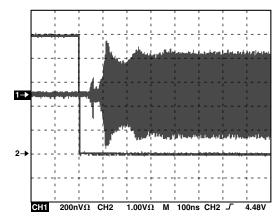

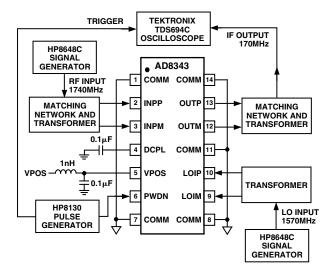

The AD8343 requires about 2.5 µs to turn OFF when PWDN is asserted; turn ON time is about 500 ns. Figures 4 and 5 show typical characteristics (they will vary with bypass component values). Figure 6 shows the test configuration used to acquire these waveforms.

Figure 4. PWDN Response Time Device ON to OFF

Figure 5. PWDN Response Time Device OFF to ON

Figure 6. PWDN Response Time Test Schematic

#### **AC INTERFACES**

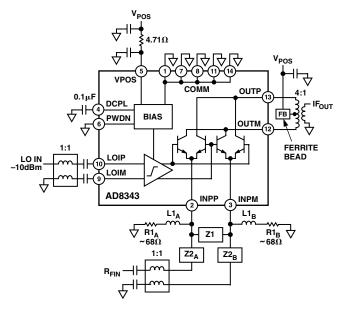

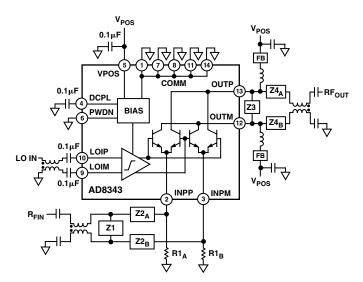

Because of the AD8343's wideband design, there are several points to consider in its ac implementation; the Basic AC Signal Connection diagram shown in Figure 7 summarizes these points. The input signal undergoes a single-ended-to-differential conversion and is then reactively matched to the impedance presented by the emitters of the core. The matching network also provides bias currents to these emitters. Similarly, the LO input undergoes a single-ended-to-differential transformation before it is applied to the 50  $\Omega$  differential LO port. The differential output signal currents appear at high-impedance collectors and may be reactively matched and converted to a single-ended signal.

Figure 7. Basic AC Signal Connection Diagram

### INPUT INTERFACE (INPP AND INPM) Single-Ended-to-Differential Conversion

The AD8343 is designed to accept differential input signals for best performance. While a single-ended input can be applied, the signal capacity is reduced by 6 dB. Further, there would be no cancellation of even-order distortion arising from the nonlinear input impedances, so the effective signal handling capacity will be reduced even further in distortion-sensitive situations. That is, the intermodulation intercepts are degraded.

For these reasons it is strongly recommended that differential signals be presented to the AD8343's input. In addition to commercially available baluns, there are various discrete and printed circuit elements that can produce the required balanced waveforms and impedance match (i.e., rat-race baluns). These alternate circuits can be employed to further reduce the component cost of the mixer.

Baluns implemented in transmission line form (also known as common-mode chokes) are useful up to frequencies of around 1 GHz, but are often excessively lossy at the highest frequencies that the AD8343 can handle. M/A-Com manufactures these baluns with their ETC line. Murata produces a true surfacemount balun with their LDB20C series. Coilcraft and Toko are also manufacturers of RF baluns.

## **Input Matching Considerations**

The design of the input matching network should be undertaken with two goals in mind: matching the source impedance to the input impedance of the AD8343 and providing a dc bias current path for the bias setting resistors.

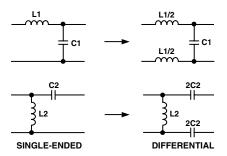

The maximum power transfer into the device will occur when there is a conjugate impedance match between the signal source and the input of the AD8343. This match can be achieved with the differential equivalent of the classic "L" network, as illustrated in Figure 8. The figure gives two examples of the transformation from a single-ended "L" network to its differential counterpart. The design of "L" matching networks is adequately covered in texts on RF amplifier design (for example: "Microwave Transistor Amplifiers" by Guillermo Gonzalez).

Figure 8. Single-Ended-to-Differential Transformation

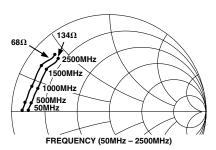

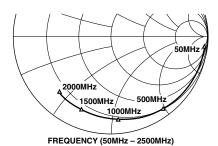

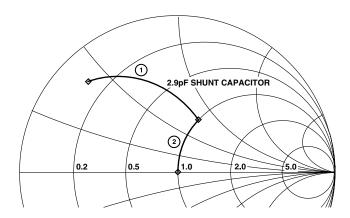

Figure 9 shows the differential input impedance of the AD8343 at the pins of the device. The two measurements shown in the figure are for two different core currents set by resistors R3 and R4; the real value impedance shift is caused by the change in transistor  $r_E$  due to the change in current. The standard S parameter files are available at the ADI web site (www.analog.com).

Figure 9. Input Differential Impedance (INPP, INPM) for Two Values of R3 and R4

Figure 9 provides a reasonable starting point for the design of the network. However, the particular board traces and pads will transform the input impedance at frequencies in excess of about 500 MHz. For this reason it is best to make a *differential* input impedance measurement at the board location where the matching network will be installed, as a starting point for designing an accurate matching network.

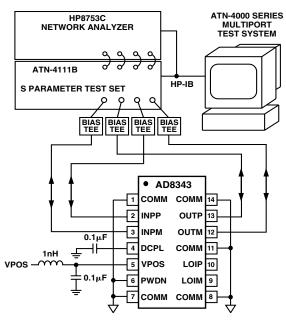

Differential impedance measurement is made relatively easy through the use of a technique presented in an article by Lutz Konstroffer in *RF Design*, January 1999, entitled "Finding the Reflection Coefficient of a Differential One-Port Device." This article presents a mathematical formula for converting from a two-port single-ended measurement to differential impedance. A full two-port measurement is performed using a vector network analyzer with Port 1 and Port 2 connected to the two differential inputs of the device at the desired measurement plane. The two-port measurement results are then processed with Konstroffer's formula (following), which is straightforward and can be implemented through most RF design packages that can read and analyze network analyzer data.

$$\Gamma s = \frac{\left(2 \times S11 - S21\right)\left(1 - S22 - S12\right) + \left(1 - S11 - S21\right)\left(1 + S22 - 2 \times S12\right)}{\left(2 - S21\right)\left(1 - S22 - S12\right) + \left(1 - S11 - S21\right)\left(1 + S22\right)}$$

This measurement can also be made using the ATN 4000 Series Multiport Network Analyzer. This instrument, and accompanying software, is capable of directly producing differential measurements.

At low frequencies and  $I_O$  = 16 mA, the differential input impedance seen at ports INPP and INPM of the AD8343 is low (~5  $\Omega$  in series with parasitic inductances that total about 3 nH). Because of this low value of impedance, it may be beneficial to choose a transformer-type balun that can also perform all or part of the real value impedance transformation. The turns ratio of the transformer will remove some of the matching burden from the differential "L" network and potentially lead to wider bandwidth.

At frequencies above 1 GHz, the real part of the input impedance rises markedly and it becomes more attractive to use a 1:1 balun and rely on the "L" network for the entire impedance transformation.

In order to obtain the lowest distortion, the inputs of the AD8343 should be driven through external ballast resistors. At low frequencies (up to perhaps 200 MHz) about 5  $\Omega$  per side is appropriate; above about 400 MHz, 10  $\Omega$  per side is better. The specified RF performance values for the AD8343 apply with these ballast resistors in use. These resistors improve linearity because their linear ac voltage drop partially swamps the nonlinear voltage swing occurring on the emitters.

In cases where the use of a lossy balun is unavoidable, it may be worthwhile to perform simultaneous matching on both the input and output sides of the balun. The idea is to independently characterize the balun as a two-port device and then arrange a simultaneous conjugate match for it. Unfortunately there seems to be no good way to determine the benefit this approach may offer in any particular case; it remains necessary to characterize the balun and then design and simulate appropriate matching networks to make an optimal decision. One indication that such effort may be worthwhile is the discovery that the adjustment of a post-balun-only matching network for best gain, differs appreciably from that which produces best return loss at the balun's input. A better tactic may be to try a different approach for the balun, either purchasing a different balun or designing a discrete network.

For more information on performing the input match, see "A Step-by-Step Approach to Impedance Matching" in the section covering the AD8343 evaluation board.

### **Input Biasing Considerations**

The mixer core bias current of the AD8343 is adjustable from less than 5 mA to a safe maximum of 20 mA. It is important to note that the reliability of the AD8343 will be compromised for core currents set to higher than 20 mA. The AD8343 is tested to ensure that a value of 68.1  $\Omega \pm 1\%$  will ensure safe operation.

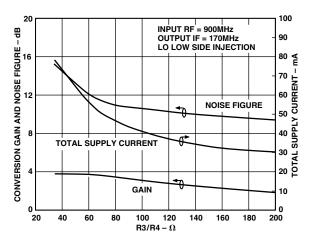

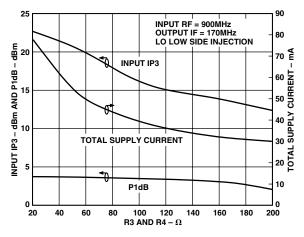

Higher operating currents will reduce distortion and affect gain, noise figure, and input impedance (Figures 10 and 11). As the quiescent current is increased by a factor of N the real part of the input impedance decreases by N. Assuming that a match is maintained, the signal current increases by  $\sqrt{N}$ , but the signal

voltage *decreases* by  $\sqrt{N}$ , which exercises a smaller portion of the nonlinear V–I characteristic of the common base connected mixer core transistors and results in lower distortion.

Figure 10. Effect of R3/R4 Value on Gain and Noise Figure

Figure 11. Effect of R3/R4 Value on Input IP3 and Gain Compression

At low frequencies where the magnitude of the complex input impedance is much smaller than the bias resistor values, adequate biasing can be achieved simply by connecting a resistor from each input to GND. The input terminals are internally biased at 1.2 V dc (nominal), so each resistor should have a resistance value calculated as  $R_{\rm BIAS} = 1.2/I_{\rm BIAS}$ . The resistor values should be well matched in order to maintain full LO to output isolation; 1% tolerance resistors are recommended.

At higher frequencies where the input impedance of the AD8343 rises, it is beneficial to insert an inductor in series between each bias resistor and the corresponding input pin in order to minimize signal shunting (Figure 24). Practical considerations will limit the inductive reactance to a few hundred ohms. The best overall choice of inductor will be that value which places the self-resonant frequency at about the upper end of the desired input frequency range. Note that there is an RF stability concern that argues in favor of erring on the side of too small an inductor value; reference section on Input and Output Stability Considerations. The Murata LQW1608A series of inductors (0603 SMT package) offers values up to 56 nH before the self-resonant frequency falls below 2.4 GHz.

For optimal LO-to-Output isolation it is important not to connect the dc nodes of the emitter bias inductors together in an attempt to share a single bias resistor. Doing so will cause isolation degradation arising from  $V_{BE}$  mismatches of the transistors in the core.

#### **OUTPUT INTERFACE (OUTP, OUTM)**

The output of the AD8343 comprises a balanced pair of open-collector outputs. These should be biased to about the same voltage as is connected to VPOS (see dc specifications table). Connecting them to an appreciably higher voltage is likely to result in conduction of the ESD protection network on signal peaks, which would cause high distortion levels. On the other hand, setting the dc level of the outputs too low is also likely to result in poor device linearity due to collector-base capacitance modulation or saturation of the core transistors.

#### **Output Matching Considerations**

The AD8343 requires a differential load for much the same reasons that the input needs a differential source to achieve optimal device performance. In addition, a differential load will provide the best LO to output isolation and the best input to output isolation.

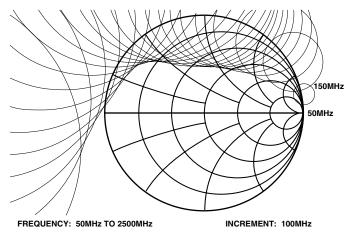

At low output frequencies it is usually not appropriate to arrange a conjugate match between the device output and the load, even though doing so would maximize the small signal conversion gain. This is because the output impedance at low frequencies is quite high (a high resistance in parallel with a small capacitance). Refer to Figure 12 for a plot of the differential output impedance measured at the device pins. This data is available in standard file format at the ADI web site (www.analog.com).

If a matching high impedance load is used, sufficient output voltage swing will occur to cause output clipping even at relatively low input levels, which constitutes a loss of dynamic range. The linear range of voltage swing at each output pin is about  $\pm 1$  volt from the supply voltage VPOS. A good compromise is to provide a load impedance of about 500  $\Omega$  between the output pins at the desired output frequency (based on 15 mA to 20 mA bias current at each input). At output frequencies below 500 MHz, more output power can be obtained before the onset of gross clipping by using a lower load impedance; however, both gain and low order distortion performance will be degraded.

Figure 12. Output Differential Impedance (OUTP, OUTM)

The output load impedance should also be kept reasonably low at the image frequency to avoid developing appreciable extra voltage swing, which would again reduce dynamic range.

If maintaining a good output return loss is not required, a 10:1 (impedance) flux-coupled transformer may be used to present a suitable load to the device and to provide collector bias via a center tap as shown in Figure 21. At all but the lowest output frequencies it becomes desirable to tune out the output capacitance of the AD8343 by connecting an inductor between the output pins.

On the other hand, when a good output return loss is desired, the output may be resistively loaded with a shunt resistance between the output pins in order to set the real value of output impedance. With selection of both the transformer's impedance ratio and the shunting resistance as required, the desired total load (~500  $\Omega$ ) will be achieved while optimizing both signal transfer and output return loss.

At higher output frequencies the output conductance of the device becomes higher (Figure 12), with the consequence that above about 900 MHz it does become appropriate to perform a conjugate match between the load and the AD8343's output. The device's own output admittance becomes sufficient to remove the threat of clipping from excessive voltage swing. Just as for the input, it may become necessary to perform differential output impedance measurements on your board layout to effectively develop a good matching network.

## **Output Biasing Considerations**

When the output single-ended-to-differential conversion takes the form of a transformer whose primary winding is center-tapped, simply apply VPOS to the tap, preferably through a ferrite bead in series with the tap in order to avoid a common-mode instability problem (reference section on Input and Output Stability Considerations). Refer to Figure 21 for an example of this network. The collector dc bias voltage should be nominally equal to the supply voltage applied to Pin 5 (VPOS).

If a 1:1 transmission line balun is used for the output, it will be necessary to bring in collector bias through separate inductors. These inductors should be chosen to obtain a high impedance at the RF frequency, while maintaining a suitable self-resonant frequency. Refer to Figure 22 for an example of this network.

#### INPUT AND OUTPUT STABILITY CONSIDERATIONS

The differential configuration of the input and output ports of the AD8343 raises the need to consider both differential and common-mode RF stability of the device. Throughout the following stability discussion, common mode will be used to refer to a signal that is referenced to ground. The equivalent common-mode impedance will be the value of impedance seen from the node under discussion to ground. The book "Microwave Transistor Amplifiers" by Guillermo Gonzalez also has an excellent section covering stability of amplifiers.

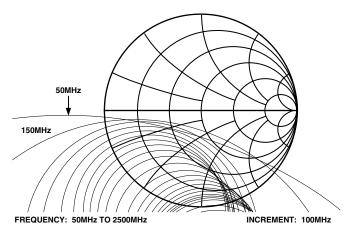

The AD8343 is unconditionally stable for any differential impedance, so device stability need not be considered with respect to the *differential* terminations. However, the device is potentially unstable (k factor is less than one) for some common-mode impedances. Figures 13 and 14 plot the input and output common-mode stability regions, respectively. Figure 15 shows the test equipment configuration to measure these stability circles.

The plotted stability circles in Figure 14 indicate that the guiding principle for preventing stability problems due to common-mode output loading is to avoid high-Q common-mode inductive loading. This stability concern is of particular importance when the output is taken from the device with a center-tapped transformer. The common-mode inductance to the center tap, which arises from imperfect coupling between the halves of the primary winding, produces an unstable common-mode loading condition. Fortunately, there is a simple solution: insert a ferrite bead in series with the center tap, then provide effective RF bypassing on the power supply side of the bead. The bead should develop substantial impedance (tens of ohms) by the time a frequency of about 200 MHz is reached. The Murata BLM21P300S is a possible choice for many applications.

Figure 13. Common-Mode Input Stability Circles

Figure 14. Common-Mode Output Stability Circles

Figure 15. Impedance and Stability Circle Test Schematic

In cases where a transmission line balun is used at the output, the solution needs more exploration. After the differential impedance matching network is designed, it is possible to measure or simulate the common-mode impedance seen by the device. This impedance should be plotted against the stability circles to ensure stable operation. An alternate topology for the matching network may be required if the proposed network produces an unacceptable common-mode impedance.

For the device input, capacitive common-mode loading produces an unstable circuit, particularly at low frequencies (Figure 13). Fortunately, either type of single-ended-to-differential conversion (transmission line balun or flux-coupled transformer) tends to produce inductive loading, although some matching network topologies and/or component values could circumvent this desirable behavior. In general, a simulation of the common-mode termination seen by the AD8343's input port should be plotted against the input stability circles to check stability. This is especially recommended if the single-ended-to-differential conversion is done with a discrete component circuit.

### LO Input Interface (LOIP, LOIM)

The LO terminals of the AD8343 are internally biased; connections to these terminals should include dc blocks, except as noted below in the DC Coupling the LO section.

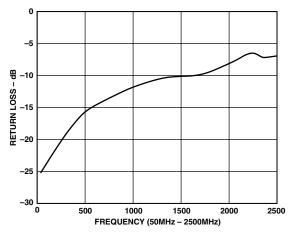

The differential LO input return loss (re  $50\,\Omega$  is presented in Figure 16. As shown, this port has a typical differential return loss of better than 9.5 dB (2:1 VSWR). If better return loss is desired for this port, differential matching techniques can also be applied.

Figure 16. LO Input Differential Return Loss

At low LO frequencies, it is reasonable to drive the AD8343 with a single-ended LO, connecting the undriven terminal to GND through a dc block. This will result in an input impedance closer to 25  $\Omega$  at low frequencies, which should be factored into the design. At higher LO frequencies, differential drive is recommended.

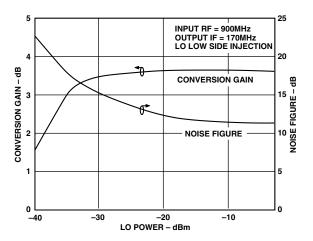

The suggested minimum LO power level is about –12 dBm. This can be seen in Figure 17.

Figure 17. Gain and Noise Figure vs. LO Input Power

### DC Coupling the LO

The AD8343's LO limiting amplifier chain is internally dccoupled. In some applications or experimental situations it is useful to exploit this property. This section addresses some ways in which to do it.

The LO pins are internally biased at about 360 mV with respect to COMM. Driving the LO to either extreme requires injecting several hundred microamps into one LO pin and extracting about the same amount of current from the other. The incremental impedance at each pin is about 25  $\Omega$ , so the voltage level on each pin is disturbed very little by the application of external currents in that range.

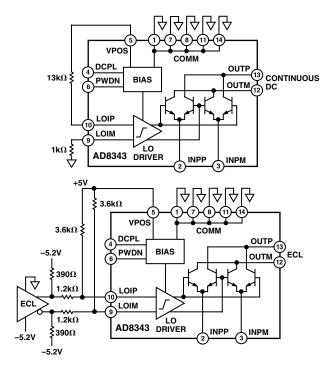

Figure 18 illustrates how to drive the LO port with continuous dc and also from standard ECL powered by -5.2 V.

Figure 18. DC Interface to LO Port

#### A Step-by-Step Approach to Impedance Matching

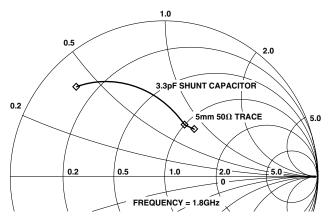

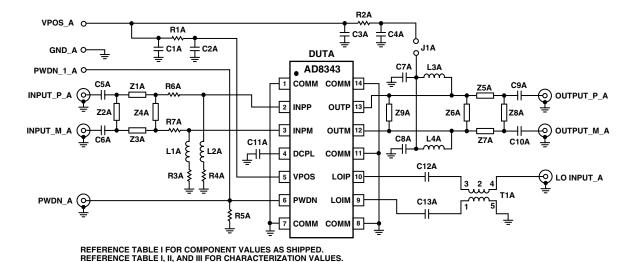

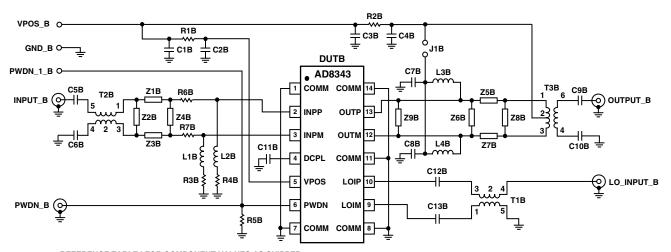

The following discussion addresses, in detail, the matter of establishing a differential impedance match to the AD8343. This section will specifically deal with the input match, and using side "A" of the evaluation board (Figure 23). An analogous procedure would be used to establish a match to the output if desired.

#### Step 1: Circuit Setup

In order to do this work the AD8343 must be powered up, driven with LO; its outputs should be terminated in a manner that avoids the common-mode stability problem as discussed in the Input and Output Stability section. A convenient way to deal with the output termination is to place ferrite chokes at L3A and L4A and omit the output matching components altogether.

It is also important to establish the means of providing bias currents to the input pins because this network may have unexpected loading effects and inhibit matching progress.

## Step 2: Establish Target Impedance

This step is necessary when the single-ended-to-differential network (input balun) does not produce a  $50\,\Omega$  output impedance. In order to provide for maximum power transfer, the input impedance of the matching network, loaded with the AD8343 input impedance (including ballast resistors), should be the conjugate of the output impedance of the single-ended-to-differential network. This step is of particular importance when utilizing transmission line baluns because the differential output impedance of the input balun may differ significantly from what is expected. Therefore, it is a good idea to make a separate measurement of this impedance at the desired operating frequency before proceeding with the matching of the AD8343.

The idea is to make a differential measurement at the output of the balun, with the single-ended port of the balun terminated in 50  $\Omega$ . Again, there are two methods available for making this measurement: use of the ATN Multiport Network Analyzer to measure the differential impedance directly, or use of a standard two-port network analyzer and Konstroffer's transformation equation.

In order to utilize a standard two-port analyzer, connect the two ports of the calibrated vector network analyzer (VNA) to the balanced output pins of the balun, measure the two-port S parameters, then use Konstroffer's formula to convert the two-port parameters to one-port differential  $\Gamma$ .

$$\Gamma s = \frac{\left(2 \times S11 - S21\right)\left(1 - S22 - S12\right) + \left(1 - S11 - S21\right)\left(1 + S22 - 2 \times S12\right)}{\left(2 - S21\right)\left(1 - S22 - S12\right) + \left(1 - S11 - S21\right)\left(1 + S22\right)}$$

# Step 3: Measure AD8343 Differential Impedance at Location of First Matching Component

Once the target impedance is established, the next step in matching to the AD8343 is to measure the differential impedance at the location of the first matching component. The "A" side of the evaluation board is designed to facilitate doing so.

Before doing the board measurements, it is necessary to perform a full two-port calibration of the VNA at the ends of the cables that will be used to connect to the board's input connectors, using the SOLT (Short, Open, Load, Thru) method or equivalent. It is a good idea to set the VNA's sweep span to a few hundred MHz or more for this work because it is often useful to see what the circuit is doing over a large range of frequencies, not just at the intended operating frequency. This is particularly useful for detecting stability problems.

After the calibration is completed, connect network analyzer ports one and two to the differential inputs of the AD8343 Evaluation Board.

On the AD8343 Evaluation Board, it is necessary to temporarily install jumpers at Z1A and Z3A if Z4A is the desired component location. Zero ohm resistors or capacitors of sufficient value to exhibit negligible reactance work nicely for this purpose.