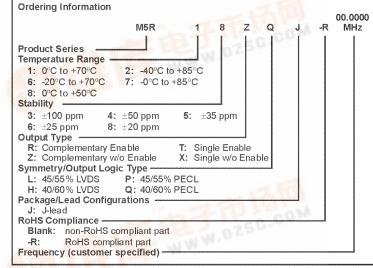

## M5R Series

(5.08)

SUGGESTED SOLDER PAD LAYOUT

0.118 (3.00)

$\mathbf{H} \mathbf{H} \mathbf{H}$

$\mathbf{H} \mathbf{H} \mathbf{H}$

FUNCTION

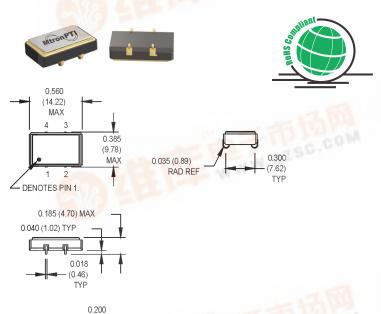

All dimensions in inches (mm).

0.346 (8.80)

0.100 (2.54) TYP

**OPTIONAL 6-PIN** PACKAGE WITH TRISTATE

0.100 (2.54)

## 9x14 mm, 3.3 Volt, LVPECL/LVDS, Clock Oscillator

- Calibration, deviation over temperature, shock, vibration, and aging.

PECL load see load circuit diagram #5. LVDS load see load circuit diagram #9. M2011Sxxx Contact factory for datasheet.

|                | PARAMETER                                             | Symbol                                                 | Min.                                                                     | Тур.                                                      | Max.      | Units                  | Condition/Notes            |

|----------------|-------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------------------------|-----------------------------------------------------------|-----------|------------------------|----------------------------|

|                | Frequency Range                                       | F                                                      | 0.75                                                                     |                                                           | 800       | MHz                    |                            |

|                | Operating Temperature                                 | TA                                                     | (See ordering information)                                               |                                                           |           |                        |                            |

|                | Storage Temperature                                   | Ts                                                     | -55                                                                      |                                                           | +125      | °C                     |                            |

|                | Frequency Stability                                   | ΔF/F                                                   | (See ordering information)                                               |                                                           |           | See Note 1             |                            |

|                | Aging                                                 |                                                        |                                                                          |                                                           |           |                        |                            |

|                | 1st Year                                              |                                                        |                                                                          | ±2                                                        |           | ppm                    | TAIR                       |

|                | Thereafter (per year)                                 |                                                        |                                                                          | ±1                                                        |           | ppm                    | COM.                       |

|                | Input Voltage                                         | Vcc                                                    | 3.135                                                                    | 3.3                                                       | 3.465     | V                      |                            |

|                | PECL Input Current                                    | lcc                                                    |                                                                          |                                                           | 60        | mA                     | 0.75 to 24 MHz             |

|                |                                                       |                                                        |                                                                          |                                                           | 95        | mΑ                     | 24 to 96 MHz               |

| пs             |                                                       |                                                        |                                                                          |                                                           | 105       | mA                     | 96 to 800 MHz              |

| Specifications | LVDS Input Current                                    | lcc                                                    |                                                                          |                                                           | 30        | mA                     | 0.75 to 24 MHz             |

|                |                                                       |                                                        |                                                                          |                                                           | 60        | mΑ                     | 24 to 800 MHz              |

| 5              | Output Type                                           |                                                        |                                                                          |                                                           |           |                        | PECL/LVDS                  |

| Spe            | Load                                                  |                                                        |                                                                          |                                                           |           |                        | See Note 2                 |

| <u>=</u>       |                                                       |                                                        | 50 Ohms to Vcc - 2 VCD                                                   |                                                           |           |                        | PECL Waveform              |

| 10             |                                                       |                                                        | 100 Ohm differential load                                                |                                                           |           |                        | LVDS Waveform              |

| ectrical       | Symmetry (Duty Cycle)                                 |                                                        | (See ordering information)                                               |                                                           |           |                        | @ Vcc-1.3 VDC (LVPECL)     |

| Ш              |                                                       |                                                        |                                                                          |                                                           |           |                        | @ 50% of waveform (LVDS)   |

|                | Output Skew                                           |                                                        |                                                                          |                                                           | 200       | ps                     | PECL                       |

|                | Differential Voltage                                  |                                                        | 250                                                                      | 350                                                       | 450       | mV                     | LVDS                       |

|                | Logic "1" Level                                       | Voh                                                    | Vcc -1.02                                                                |                                                           |           | V                      | PECL                       |

|                | Logic "0" Level                                       | Vol                                                    |                                                                          |                                                           | Vcc -1.63 | V                      | PECL                       |

|                | Rise/Fall Time                                        | Tr/Tf                                                  |                                                                          | 0.35                                                      | 0.55      | ns                     | @ 20/80% LVPECL            |

|                |                                                       |                                                        |                                                                          | 0.50                                                      | 1.0       | ns                     | @ 20/80% LVDS              |

|                | Enable Function                                       |                                                        | 80% Vcc min or N/C: output active 20% Vcc max: output disables to high-Z |                                                           |           |                        |                            |

|                |                                                       |                                                        |                                                                          |                                                           |           | "R" & "T" output types |                            |

|                | Start up Time                                         |                                                        |                                                                          |                                                           | 10        | ms                     |                            |

|                | Phase Jitter                                          | φЈ                                                     |                                                                          |                                                           |           |                        | Integrated 12 kHz – 20 MHz |

|                | >/=20 MHz                                             |                                                        |                                                                          | 3                                                         | 5         | ps RMS                 |                            |

|                |                                                       |                                                        |                                                                          |                                                           |           |                        |                            |

| <u></u>        |                                                       |                                                        |                                                                          |                                                           |           |                        |                            |

| nvironmental   | Mechanical Shock                                      | MIL-STD-202, Method 213, C (100 g's)                   |                                                                          |                                                           |           |                        |                            |

| ĮĚ             | Vibration                                             | MIL-STD-202, Method 201 & 204 (10 g's from 10-2000 Hz) |                                                                          |                                                           |           |                        |                            |

| 5              | Thermal Cycle                                         | <del></del>                                            |                                                                          | lethod 1010, B (-55°C to +125°C, 15 min dwell, 10 cycles) |           |                        |                            |

| Ξ              | ш Solderability Per EIAJ-STD-002                      |                                                        |                                                                          |                                                           |           |                        |                            |

| Ш              |                                                       |                                                        |                                                                          |                                                           |           |                        |                            |

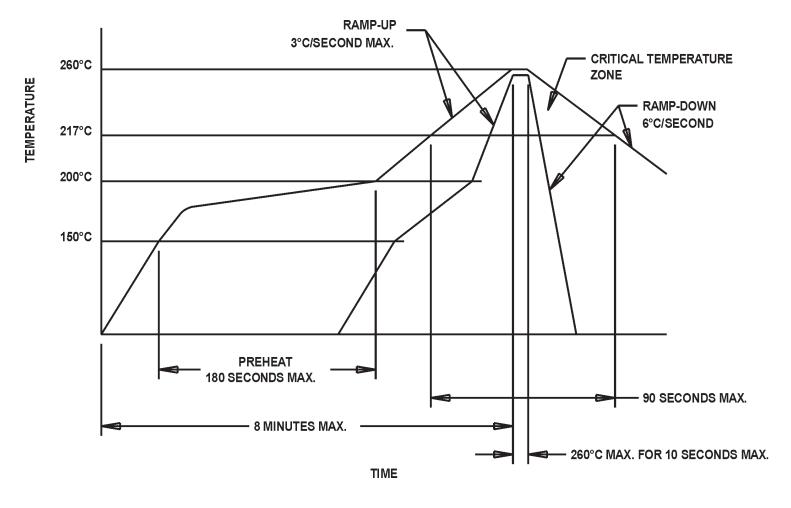

|                | Max Soldering Conditions See solder profile, Figure 1 |                                                        |                                                                          |                                                           |           |                        |                            |

2 3 2

4 Pin

6 Pin

N/C or Output Q Enable Ground/Cover Output Q 3 4 N/O 5

**Pin Connections**

- 1. Calibration, deviation over temperature, shock, vibration and aging.

2. PECL load see Load Circuit Diagram #5. LVDS load see load circuit diagram #9.

rounti com for our complete offering and detailed datasheets. Contact us for your application specific requirements: MtronPTI 1-800-762-8800

## MtronPTI Lead Free Solder Profile