### <u> 专业PCB打样工厂,24小时加急出货</u> LT3585-0/LT3585-1 LT3585-2/LT3585-3

Photoflash Chargers with Adjustable Input Current and IGBT Drivers

### DESCRIPTION

The LT<sup>®</sup>3585 series are highly integrated ICs designed to charge photoflash capacitors in digital and film cameras. A new control technique allows for the use of extremely small transformers. Each part contains an on-chip high voltage NPN power switch. Output voltage detection is completely contained within the part, eliminating the need for any discrete zener diodes or resistors. The output voltage can be adjusted by simply changing the turns ratio of the transformer.

The CHRG/IADJ pin gives full control of the part to the user. Driving CHRG/IADJ low puts the part in low power shutdown. The CHRG/IADJ pin can also be used to reduce the input current of the charger, useful in extending battery life. The DONE pin indicates when the part has completed charging.

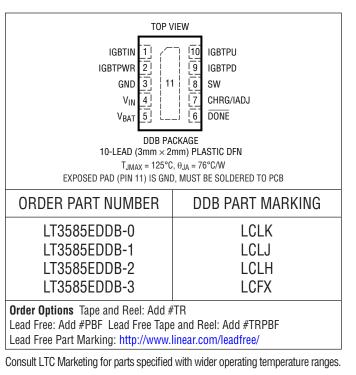

The LT3585 series of parts are housed in tiny 3mm × 2mm DFN packages.

LT, LTC and LTM are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners.

### FEATURES

- Adjustable Input Current

- Integrated IGBT Driver

- No Output Voltage Divider Needed

- Uses Small Transformers: 5.8mm × 5.8mm × 3mm

- Fast Photoflash Charge Times

- Charges Any Size Photoflash Capacitor

- Supports Operation from Single Li-Ion Cell, Two AA Cells or any Supply from 1.5V Up to 16V

- Small 10-Lead (3mm × 2mm) DFN Package

#### Fast Charge Time

| VERSION                  | INPUT<br>CURRENT (mA) | NORMAL MODE<br>Charge time<br>(Sec) | REDUCED MODE<br>CHARGE TIME<br>(Sec) |

|--------------------------|-----------------------|-------------------------------------|--------------------------------------|

| LT3585-3                 | 800/400               | 3.3                                 | 6.6                                  |

| LT3585-0                 | 550/275               | 4.6                                 | 9.2                                  |

| LT3585-2                 | 400/200               | 5.8                                 | 12.6                                 |

| LT3 <mark>585-</mark> 1* | 250/115               | 5.0                                 | 14.6                                 |

100 $\mu$ F capacitor, 320V, V<sub>IN</sub> = V<sub>BAT</sub> = 3.6V

\*50 $\mu$ F capacitor, 320V, V<sub>IN</sub> = V<sub>BAT</sub> = 3.6V

# **APPLICATIONS**

- Digital/Film Camera Flash

- PDA/Cell Phone Flash

- Emergency Strobe

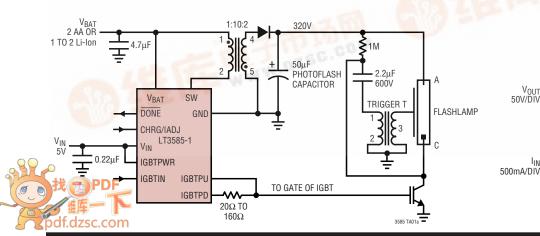

# TYPICAL APPLICATION

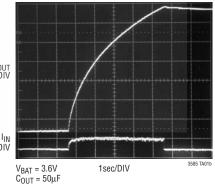

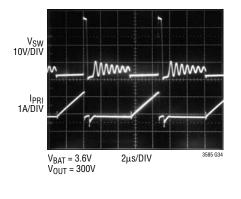

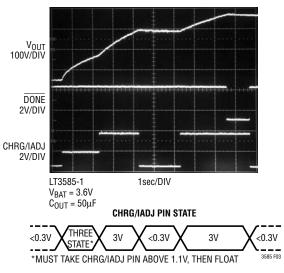

LT3585-1 Charging Waveform Normal Input Current Mode

####

| (NOTE 1)                                          |   |

|---------------------------------------------------|---|

| V <sub>IN</sub> Voltage16                         | V |

| V <sub>BATT</sub> Voltage16                       | V |

| SW Voltage60                                      | V |

| SW Pin Negative Current1.                         | A |

| CHRG/IADJ Voltage10                               | V |

| IGBTPWR Voltage10                                 |   |

| IGBTIN Voltage10                                  | V |

| IGBTPU Voltage10                                  | V |

| IGBTPD Voltage10                                  |   |

| DONE Voltage10                                    |   |

| Current Into DONE Pin 0.2mA/-1m                   |   |

| Maximum Junction Temperature 125°                 | С |

| Operating Temperature Range (Note 2) –40°C to 85° | С |

| Storage Temperature Range65°C to 125°             | С |

|                                                   |   |

### PACKAGE/ORDER INFORMATION

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. V<sub>IN</sub> = V<sub>BAT</sub> = V<sub>CHRG</sub> = 3V unless otherwise noted (Note 2). Specifications are for the LT3585-0, LT3585-1, LT3585-2, LT3585-3 unless otherwise noted.

| PARAMETER                                | CONDITIONS                                                                                                                                   |                                                                              | MIN                         | ТҮР                        | MAX                         | UNITS                |

|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|-----------------------------|----------------------------|-----------------------------|----------------------|

| Quiescent Current                        | V <sub>CHRG</sub> = 3V, Not Switching<br>V <sub>CHRG</sub> = 0V, In Shutdown                                                                 | V <sub>CHRG</sub> = 3V, Not Switching<br>V <sub>CHRG</sub> = 0V, In Shutdown |                             |                            | 8<br>1                      | mA<br>μA             |

| V <sub>IN</sub> Voltage Range            |                                                                                                                                              | •                                                                            | 2.5                         |                            | 16                          | V                    |

| V <sub>BAT</sub> Voltage Range           |                                                                                                                                              | •                                                                            | 1.5                         |                            | 16                          | V                    |

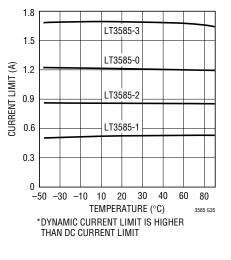

| Switch Current Limit                     | LT3585-3 (Note 3)<br>LT3585-0 (Note 3)<br>LT3585-2 (Note 3)<br>LT3585-2 (Note 3)<br>LT3585-1 (Note 3)                                        |                                                                              | 1.55<br>1.1<br>0.75<br>0.45 | 1.7<br>1.2<br>0.85<br>0.55 | 1.85<br>1.3<br>0.95<br>0.65 | A<br>A<br>A<br>A     |

| Switch V <sub>CESAT</sub>                | LT3585-3, I <sub>SW</sub> = 1.4A<br>LT3585-0, I <sub>SW</sub> = 1A<br>LT3585-2, I <sub>SW</sub> = 700mA<br>LT3585-1, I <sub>SW</sub> = 400mA |                                                                              |                             | 485<br>330<br>230<br>140   |                             | mV<br>mV<br>mV<br>mV |

| V <sub>OUT</sub> Comparator Trip Voltage | Measured as V <sub>SW</sub> – V <sub>BAT</sub>                                                                                               | •                                                                            | 31<br>30.5                  | 31.5<br>31.5               | 32<br>32.5                  | V<br>V               |

| V <sub>OUT</sub> Comparator Overdrive    | 300ns Pulse Width                                                                                                                            |                                                                              |                             | 200                        | 400                         | mV                   |

| DCM Comparator Trip Voltage              | Measured as V <sub>SW</sub> – V <sub>BAT</sub>                                                                                               |                                                                              | 80                          | 130                        | 180                         | mV                   |

| CHRG/IADJ Pin Current                    | V <sub>CHRG</sub> = 3V<br>V <sub>CHRG</sub> = 0V                                                                                             |                                                                              |                             | 45<br>0                    | 70<br>0.1                   | μA<br>μA             |

| Switch Leakage Current                   | V <sub>BAT</sub> = V <sub>SW</sub> = 5V, In Shutdown                                                                                         | •                                                                            |                             | 0.01                       | 1                           | μA                   |

| CHRG/IADJ Minimum Enable Voltage         |                                                                                                                                              | •                                                                            | 1.1                         |                            |                             | V                    |

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. V<sub>IN</sub> = V<sub>BAT</sub> = V<sub>CHRG</sub> = 3V unless otherwise noted (Note 2). Specifications are for the LT3585-0, LT3585-1, LT3585-2, LT3585-3 unless otherwise noted.

| PARAMETER                                                  | CONDITIONS                                                                                                                                                                                                                                       |   | MIN | ТҮР                      | MAX | UNITS          |

|------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|--------------------------|-----|----------------|

| CHRG/IADJ Three-State Voltage for Reduced Input<br>Current | CHRG/IADJ > 1.1V then Float                                                                                                                                                                                                                      |   | 1.1 | 1.28                     | 1.4 | V              |

| CHRG/IADJ Voltage Range for Normal Input Current           |                                                                                                                                                                                                                                                  | • | 1.6 |                          | 10  | V              |

| CHRG/IADJ Low Voltage                                      |                                                                                                                                                                                                                                                  | • |     |                          | 0.3 | V              |

| Delay Time for Reduced Input Current Mode                  | $\begin{array}{l} \mbox{CHRG/IADJ Pin Three Stated:} \\ V_{BAT} = 4.2V, \mbox{ Fresh Li-Ion Cell} \\ V_{BAT} = 2.8V, \mbox{ Dead Li-Ion Cell} \\ V_{BAT} = 3V, \mbox{ Fresh 2 AA Cells} \\ V_{BAT} = 2V, \mbox{ Dead 2 AA Cells} \\ \end{array}$ |   |     | 5.2<br>7.2<br>6.8<br>9.5 |     | μs<br>μs<br>μs |

| Minimum CHRG/IADJ Pin Low Time                             | High→Low→High                                                                                                                                                                                                                                    |   |     | 20                       |     | μs             |

| DONE Output Signal High                                    | 100k $\Omega$ from V <sub>IN</sub> to DONE                                                                                                                                                                                                       |   |     | 3                        |     | V              |

| DONE Output Signal Low                                     | 33µA into DONE Pin                                                                                                                                                                                                                               |   |     | 120                      | 200 | mV             |

| DONE Leakage Current                                       | V <sub>DONE</sub> = 3V, DONE NPN Off                                                                                                                                                                                                             |   |     | 1                        | 100 | nA             |

| IGBTPWR Voltage Range                                      |                                                                                                                                                                                                                                                  | • | 2.5 |                          | 10  | V              |

| IGBT Input High Level                                      |                                                                                                                                                                                                                                                  |   | 1.5 |                          |     | V              |

| IGBT Input Low Level                                       |                                                                                                                                                                                                                                                  | • |     |                          | 0.5 | V              |

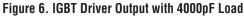

| IGBT Output Rise Time                                      | IGBTPU Pin, C <sub>OUT</sub> = 4000pF,<br>IGBTPWR = 5V, IGBTIN = 0V→1.5V, 10%→90%                                                                                                                                                                |   |     | 0.4                      |     | μs             |

| IGBT Output Fall Time                                      | IGBTPD Pin, C <sub>OUT</sub> = 4000pF,<br>IGBTPWR = 5V, IGBTIN = 1.5V→0V, 90%→10%                                                                                                                                                                |   |     | 0.13                     |     | μs             |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime. Ratings are for DC levels only.

**Note 2:** The LT3585 series is guaranteed to meet performance specifications from 0°C to 85°C. Specifications over the -40°C to 85°C operating temperature range are assured by design, characterization and correlation with statistical process controls.

**Note 3:** Current limit is guaranteed by design and/or correlation to static test.

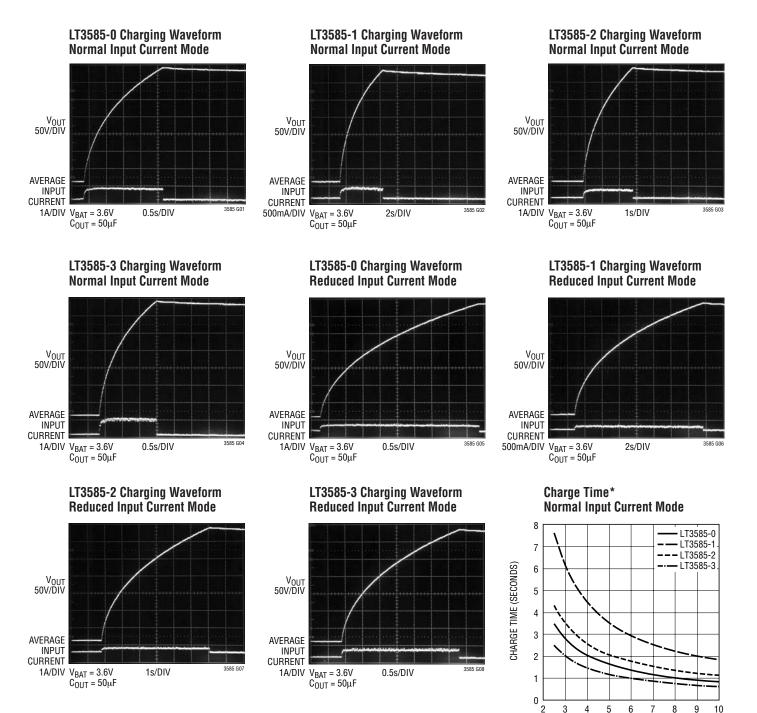

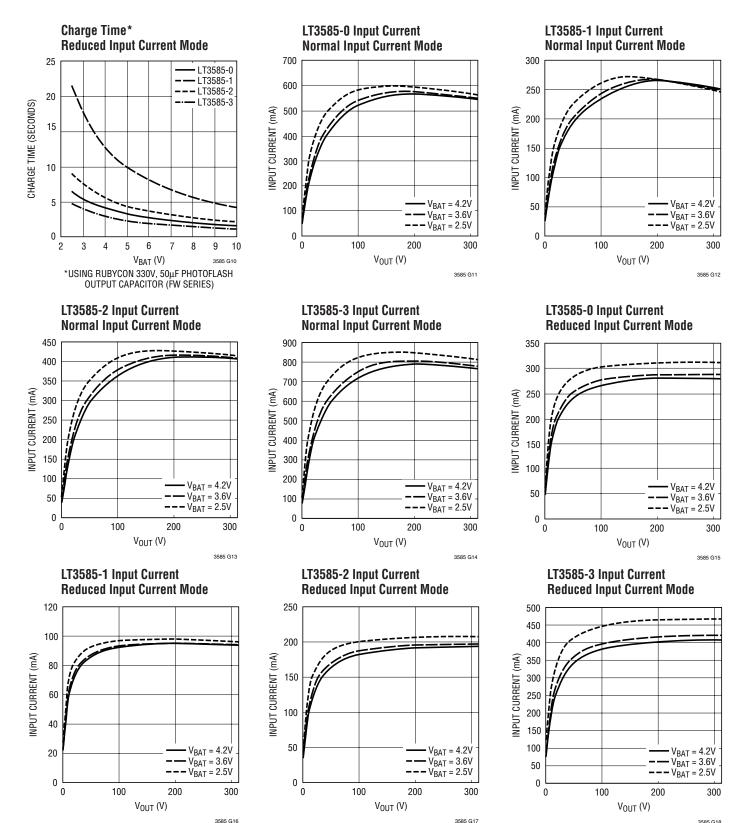

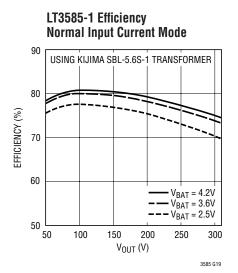

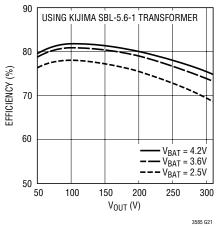

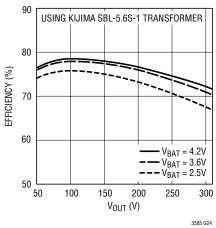

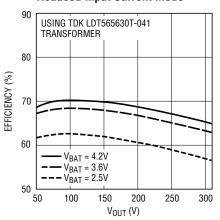

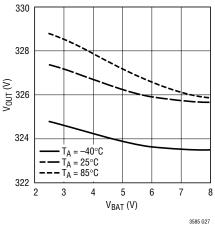

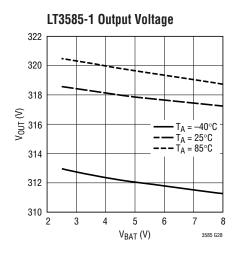

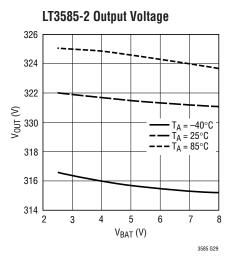

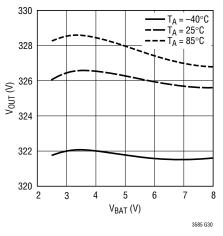

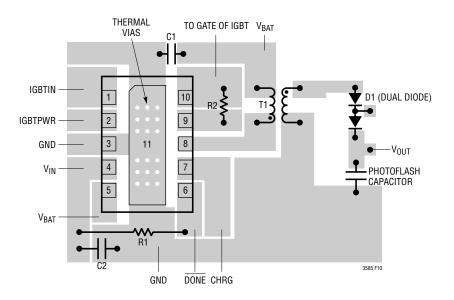

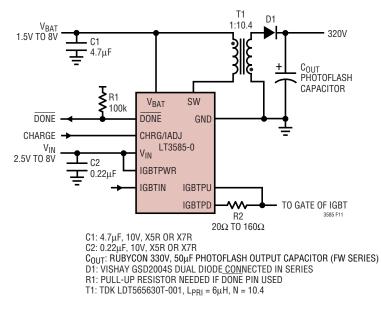

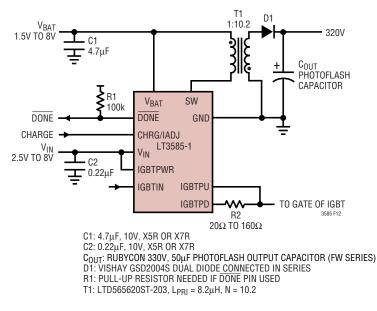

### TYPICAL PERFORMANCE CHARACTERISTICS

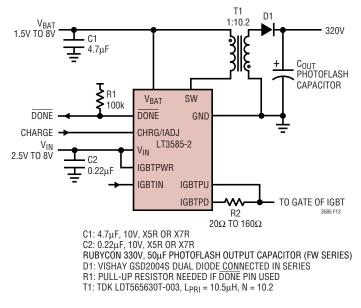

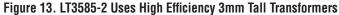

LT3585-0 curves use Figure 11. LT3585-1 curves use Figure 12, LT3585-2 curves use Figure 13 and LT3585-3 curves use Figure 14 unless otherwise noted.

<sup>\*</sup>USING RUBYCON 330V, 50µF PHOTOFLASH OUTPUT CAPACITOR (FW SERIES)

V<sub>BAT</sub> (V)

5 6 7 8

2

9 10

3585 G09

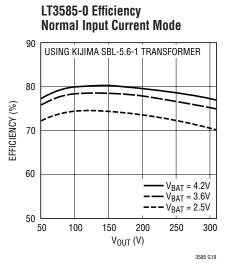

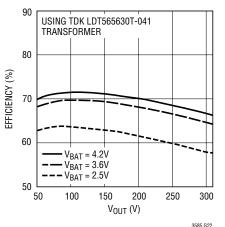

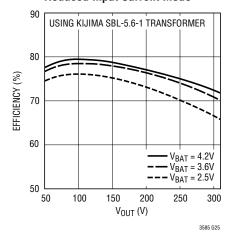

**TYPICAL PERFORMANCE CHARACTERISTICS** LT3585-0 curves use Figure 11, LT3585-1 curves use Figure 12, LT3585-2 curves use Figure 13 and LT3585-3 curves use Figure 14 unless otherwise noted.

3585 G18 3585f

# TYPICAL PERFORMANCE CHARACTERISTICS LT3585-0 curves use Figure 11, LT3585-1 curves

use Figure 12, LT3585-2 curves use Figure 13 and LT3585-3 curves use Figure 14 unless otherwise noted.

LT3585-3 Efficiency Normal Input Current Mode

#### LT3585-2 Efficiency **Reduced Input Current Mode**

LT3585-0 Efficiency

90

80

60

50

50

100

EFFICIENCY (%) 70 **Reduced Input Current Mode**

USING KIJIMA SBL-5.6-1 TRANSFORMER

$V_{BAT} = 4.2V$

V<sub>BAT</sub> = 3.6V

V<sub>BAT</sub> = 2.5V

300

3585 G23

3585 G26

250

LT3585-2 Efficiency **Normal Input Current Mode**

LT3585-1 Efficiency **Reduced Input Current Mode**

LT3585-3 Efficiency **Reduced Input Current Mode**

150

200

$V_{OUT}(V)$

#### LT3585-0 Output Voltage

3585f

**TYPICAL PERFORMANCE CHARACTERISTICS** LT3585-0 curves use Figure 11, LT3585-1 curves use Figure 12, LT3585-2 curves use Figure 13 and LT3585-3 curves use Figure 14 unless otherwise noted.

#### LT3585-3 Output Voltage

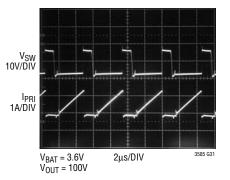

LT3585-0 Switch Waveform Normal Input Current Mode

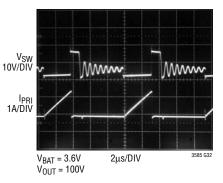

#### LT3585-0 Switch Waveform Reduced Input Current Mode

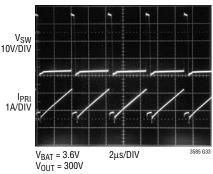

#### LT3585-0 Switch Waveform Normal Input Current Mode

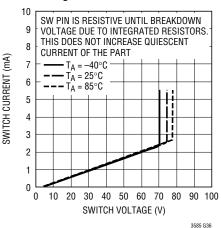

#### LT3585-0/LT3585-1/LT3585-2/ LT3585-3 Switch Breakdown Voltage

#### LT3585-0 Switch Waveform Reduced Input Current Mode

Switch DC Current Limit\*

# PIN FUNCTIONS

**IGBTIN (Pin 1):** Logic Input for the IGBT Driver. When this pin is driven higher than 1.5V, the output goes high. When the pin is below 0.5V, the output will go low.

**IGBTPWR (Pin 2):** Supply Pin for the IGBT Driver. Must be locally bypassed with a good quality ceramic capacitor. The minimum operating voltage for the IGBT driver is 2.5V.

**GND (Pin 3):** Ground. Tie directly to local ground plane.

$V_{IN}$  (Pin 4): Input Supply Pin. Must be locally bypassed with a good quality ceramic capacitor. The minimum operating voltage for  $V_{IN}$  is 2.5V.

$V_{BAT}$  (Pin 5): Battery Supply Pin. Must be locally bypassed with a good quality ceramic capacitor. The minimum operating voltage for  $V_{BAT}$  is 1.5V.

**DONE** (Pin 6): Open NPN Collector Indication Pin. When target output voltage is reached, NPN turns on. This pin needs a proper pull-up resistor or current source.

**CHRG/IADJ (Pin 7):** Charge and Input Current Adjust Pin. A low (<0.3V) to high (>1.1V) transition on this pin puts the part into power delivery mode. Once the target output voltage is reached, the part will stop charging the output. Toggle this pin to start charging again. Ground to shut down. To enter into the input current reduction mode, the voltage on this pin should be driven high (>1.1V) and then floated. (For more information refer to the Operation section of this data sheet.) To enter normal mode, the voltage should be driven higher than 1.6V.

**SW (Pin 8):** Switch Pin. This is the collector of the internal NPN Power switch. Minimize the metal trace area connected to this pin to minimize EMI. Tie one side of the primary of the transformer to this pin. The target output voltage is set by the turns ratio of the transformer.

Choose turns ratio N by the following equation:

$$N = \frac{V_{OUT} + 2}{31.5}$$

where  $V_{OUT}$  is the desired output voltage.

**IGBTPD (Pin 9):** Pull-down Output for IGBT Gate. Connect this pin to the IGBT Gate. Add a series resistor to increase the turn-off time to protect the IGBT.

**IGBTPU (Pin 10):** Pull-up Output for IGBT Gate. Connect this pin to the gate of the IGBT.

**Exposed Pad (Pin 11):** Ground. Tie directly to local ground plane.

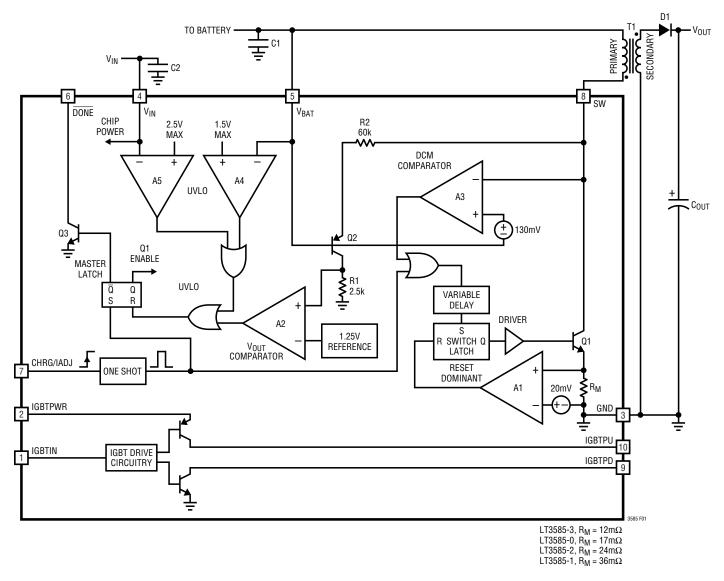

### SIMPLIFIED BLOCK DIAGRAM

Figure 1

# OPERATION

The LT3585 series of parts operate on the edge of discontinuous conduction mode. When CHRG/IADJ is driven higher than 1.1V, the master latch is set. This enables the part to deliver power to the photoflash capacitor. When the power switch, Q1, is turned on, current builds up in the primary of the transformer. When the desired current level is reached, the output of comparator A1 goes high. resetting the switch latch that controls the state of Q1, and the output of the DCM comparator goes low. Q1 now turns off and the flyback waveform on the SW node quickly rises to a level proportional to  $V_{OUT}$ . The secondary current flows through high voltage diode(s), D1, and into the photoflash capacitor. When the secondary current decays to zero, the voltage on the SW node collapses. When this voltage reaches 130mV higher than V<sub>BAT</sub>, the output of A3 goes high. This sets the switch latch and the power switch, Q1, turns back on. This cycle repeats until the target  $V_{OUT}$  level is reached. When the target  $V_{OUT}$  is reached, the master latch resets and the DONE pin goes low.

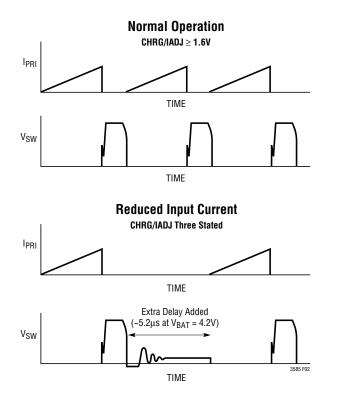

The input current of an LT3585 series circuit can be reduced by changing the voltage of the CHRG/IADJ pin. When this pin is between 1.1V and 1.4V, a time delay is

Figure 2. Normal and Reduced Input Current Waveforms

added between when A3 goes high and the switch latch is set, see Figure 2. If the part is enabled, and the CHRG/ IADJ pin is floated, internal circuitry drives the voltage on the pin to 1.28V. This allows a single I/O port pin, which can be three-stated, to enable or disable the part as well as place the part into the input current reduction mode. This feature effectively reduces the average input current into the flyback transformer. The magnitude of the delay decreases with increasing V<sub>BAT</sub>. This causes the reduced average input current to remain relatively flat with changes in V<sub>BAT</sub>. When CHRG/IADJ is brought higher than 1.6V, no delay is added. The CHRG/IADJ pin functionality is shown in Figure 3.

Both  $V_{BAT}$  and  $V_{IN}$  have undervoltage lockout (UVLO). When one of these pins goes below its UVLO voltage, the DONE pin goes low. With an insufficient bypass capacitor on  $V_{BAT}$ or  $V_{IN}$ , the ripple on the pin is likely to activate UVLO and terminate the charge. The applications circuits in the data sheet suggest values adequate for most applications.

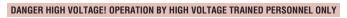

The LT3585 series also includes an integrated IGBT driver. There are two output pins, IGBTPU and IGBTPD. The IGBTPU pin is used to pull the gate of the IGBT up. This should be done quickly to guarantee proper Xenon lamp ignition. Tie this pin directly to the gate of the IGBT. The IGBTPD pin is pinned out separately to allow for greater flexibility in choosing a series resistor between the pin and the gate of the IGBT. This resistor can be used to slow down the turn off of the IGBT.

Figure 3. Basic Operation

# **APPLICATIONS INFORMATION**

#### Choosing the Right Device (LT3585-0/LT3585-1/LT3585-2/LT3585-3)

The only difference between the four versions of the LT3585 series is the peak current level. For the fastest possible charge time, use the LT3585-3. The LT3585-1 has the lowest peak current capability, and is designed for applications that need a more limited drain on the batteries. Due to the lower peak current, the LT3585-1 can use a physically smaller transformer. The LT3585-0 and LT3585-2 have a current limit in between that of the LT3585-1 and the LT3585-3.

#### **Transformer Design**

The flyback transformer is a key element for any LT3585-0/ LT3585-1/LT3585-2/LT3585-3 design. It must be designed carefully and checked that it does not cause excessive current or voltage on any pin of the part. The main parameters that need to be designed are shown in Table 1. The first transformer parameter that needs to be set is the turns ratio, N. The LT3585-0/LT3585-1/LT3585-2/LT3585-3 accomplish output voltage detection by monitoring the flyback waveform on the SW pin. When the SW voltage reaches 31.5V higher than the V<sub>BAT</sub> voltage, the part halts power delivery. Thus, the choice of N sets the target output voltage and changes the amplitude gain of the reflected voltage from the output to the SW pin. Choose N according to the following equation:

$$N = \frac{V_{OUT} + 2}{31.5}$$

where  $V_{OUT}$  is the desired output voltage. The number 2 in the numerator is used to include the forward voltage

drop across the output diode(s). Thus, for a 320V output, N should be 322/31.5 or 10.2. For a 300V output, choose N equal to 302/31.5 or 9.6. The next parameter that needs to be set is the primary inductance,  $L_{PRI}$ . Choose  $L_{PRI}$  according to the following formula:

$$L_{PRI} \ge \frac{V_{OUT} \bullet 200 \bullet 10^{-9}}{N \bullet I_{PK}}$$

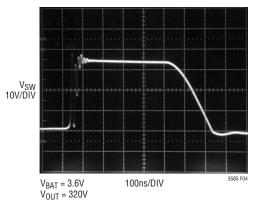

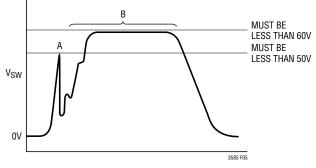

where  $V_{OUT}$  is the desired output voltage. N is the transformer turns ratio. IPK is 1.4 (LT3585-0), 0.7 (LT3585-1), 1 (LT3585-2) and 2 (LT3585-3). LPRI needs to be equal or larger than this value to ensure that the LT3585 series has adequate time to respond to the flyback waveform. All other parameters need to meet or exceed the recommended limits as shown in Table 1. A particularly important parameter is the leakage inductance, LI FAK. When the power switch of the LT3585 series turns off, the leakage inductance on the primary of the transformer causes a voltage spike to occur on the SW pin. The height of this spike must not exceed 50V, even though the absolute maximum rating of the SW pin is 60V. The 60V absolute maximum rating is a DC blocking voltage specification, which assumes that the current in the power NPN is zero. Figure 4 shows the SW voltage waveform for the circuit of Figure 8 (LT3585-0). Note that the absolute maximum rating of the SW pin is not exceeded. Make sure to check the SW voltage waveform with  $V_{OUT}$  near the target output voltage, as this is the worst-case condition for SW voltage. Figure 5 shows the various limits on the SW voltage during switch turn off.

| PARAMETER         | NAME                                      | TYPICAL RANGE<br>LT3585-0 | TYPICAL RANGE<br>LT3585-1 | TYPICAL RANGE<br>LT3585-2 | TYPICAL RANGE<br>LT3585-3 | UNITS |

|-------------------|-------------------------------------------|---------------------------|---------------------------|---------------------------|---------------------------|-------|

| L <sub>PRI</sub>  | Primary Inductance                        | >5                        | >10                       | >7                        | >3.5                      | μH    |

| L <sub>LEAK</sub> | Primary Leakage Inductance                | 100 to 300                | 200 to 500                | 200 to 500                | 100 to 300                | nH    |

| N                 | Secondary/Primary Turns Ratio             | 8 to 12                   | 8 to 12                   | 8 to 12                   | 8 to 12                   |       |

| V <sub>ISO</sub>  | Secondary to Primary Isolation<br>Voltage | >500                      | >500                      | >500                      | >500                      | V     |

| I <sub>SAT</sub>  | Primary Saturation Current                | >1.6                      | >0.8                      | >1.0                      | >2                        | A     |

| R <sub>PRI</sub>  | Primary Winding Resistance                | <300                      | <500                      | <400                      | <200                      | mΩ    |

| R <sub>SEC</sub>  | Secondary Winding Resistance              | <40                       | <80                       | <60                       | <30                       | Ω     |

Table 1. Recommended Transformer Parameters

### **APPLICATIONS INFORMATION**

Figure 4. LT3585 SW Voltage Waveform

Figure 5. New Transformer Design Check

It is important not to minimize the leakage inductance to a very low level. Although this would result in a very low leakage spike on the SW pin, the parasitic capacitance of the transformer would become large. This will adversely affect the charge time of the photoflash circuit. Linear Technology has worked with several leading magnetic component manufacturers to produce predesigned flyback transformers for use with the LT3585-0/LT3585-1/LT3585-2/LT3585-3. Table 2 shows the details of several of these transformers.

#### **Output Diode Selection**

The rectifying diode(s) should be low capacitance type with sufficient reverse voltage and forward current ratings. The peak reverse voltage that the diode(s) will see is approximately:

$$V_{PK(R)} = V_{OUT} + (N \bullet V_{BAT})$$

The peak current of the diode is simply:

$$I_{PK(SEC)} = \frac{2}{N} (LT3585-3)$$

$$I_{PK(SEC)} = \frac{1.4}{N} (LT3585-0)$$

$$I_{PK(SEC)} = \frac{1}{N} (LT3585-2)$$

$$I_{PK(SEC)} = \frac{0.7}{N} (LT3585-1)$$

For the circuit of Figure 8 with  $V_{BAT}$  of 5V,  $V_{PK(R)}$  is 371V and  $I_{PK(SEC)}$  is 137mA. The GSD2004S dual silicon diode is recommended for most applications. Table 3 shows the various diodes and relevant specifications. Use the appropriate number of diodes to achieve the necessary reverse breakdown voltage.

#### **Capacitor Selection**

For the input bypass capacitors, high quality X5R or X7R types should be used. Make sure the voltage capability of the part is adequate.

| FOR USE<br>With                                          | TRANSFORMER<br>Designation                                                              | $\begin{array}{c} \text{SIZE} \\ \text{(W} \times \text{L} \times \text{H) (mm)} \end{array}$                                                                                          | LPRI<br>(µH)                    | LPRI LEAKAGE<br>(nH )                               | N                                    | R <sub>PRI</sub><br>(mΩ)                           | R <sub>SEC</sub><br>(Ω)                             | VENDOR                                                                  |

|----------------------------------------------------------|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|-----------------------------------------------------|--------------------------------------|----------------------------------------------------|-----------------------------------------------------|-------------------------------------------------------------------------|

| LT3585-1<br>LT3585-0/<br>LT3585-2                        | SBL-5.6S-1<br>SBL-5.6-1                                                                 | $5.6 \times 8.5 \times 3.0$<br>$5.6 \times 8.5 \times 4.0$                                                                                                                             | 24<br>10                        | 400 Max<br>200 Max                                  | 10.2<br>10.2                         | 305<br>103                                         | 55<br>26                                            | Kijima Musen<br>Hong Kong Office<br>852-2489-8266                       |

| LT3585-1<br>LT3585-0<br>LT3585-1<br>LT3585-2<br>LT3585-3 | LDT565620ST-203<br>LDT565630T-001<br>LDT565630T-002<br>LDT565630T-003<br>LDT565630T-041 | $5.8 \times 5.8 \times 2.0$<br>$5.8 \times 5.8 \times 3.0$<br>$5.8 \times 5.8 \times 3.0$<br>$5.8 \times 5.8 \times 3.0$<br>$5.8 \times 5.8 \times 3.0$<br>$5.8 \times 5.8 \times 3.0$ | 8.2<br>6<br>14.5<br>10.5<br>4.7 | 390 Max<br>200 Max<br>500 Max<br>550 Max<br>150 Max | 10.2<br>10.4<br>10.2<br>10.2<br>10.4 | 370 Max<br>100 Max<br>240 Max<br>210 Max<br>90 Max | 11.2 Max<br>10 Max<br>16.5 Max<br>14 Max<br>6.4 Max | TDK<br>Chicago Sales Office<br>(847) 803-6100<br>www.components.tdk.com |

| LT3585-0<br>LT3585-1<br>LT3585-2<br>LT3585-3             | TTRN-0530-000-T<br>TTRN-0530-012-T<br>TTRN-0530-021-T<br>TTRN-0530-022-T                | $\begin{array}{c} 5.0 \times 5.0 \times 3.0 \\ 5.0 \times 5.0 \times 3.0 \end{array}$           | 6.6<br>16.0<br>11.8<br>4.0      | 200 Max<br>400 Max<br>300 Max<br>300 Max            | 10.3<br>10.3<br>10.3<br>10.3<br>10.3 | 128 Max<br>515 Max<br>256 Max<br>102 Max           | 28 Max<br>32 Max<br>37 Max<br>16 Max                | Tokyo Coil Engineering<br>Japan Office<br>0426-56-6262                  |

### **APPLICATIONS INFORMATION**

#### **Table 3. Recommended Output Diodes**

Figure 7. IGBT Turn-Off Delay vs R<sub>PD</sub>

| PART                      | MAX REVERSE<br>VOLTAGE (V) | MAX CONTINUOUS<br>FORWARD CURRENT (mA) | CAPACITANCE (pF) | VENDOR                                                         |

|---------------------------|----------------------------|----------------------------------------|------------------|----------------------------------------------------------------|

| GSD2004S<br>(DUAL DIODE)  | 2 × 300                    | 225                                    | 5                | Vishay<br>(402) 563-6866<br>www.vishay.com                     |

| CMSD2004S<br>(DUAL DIODE) | 2 × 300                    | 225                                    | 5                | Central Semiconductor<br>(631) 435-1110<br>www.centralsemi.con |

| MMBD3004S<br>(DUAL DIODE) | 2 × 350                    | 225                                    | 5                | Diodes, Inc<br>(816) 251-8800<br>www.diodes.com                |

#### **IGBT Drive**

The IGBT is a high current switch for the 100A+ current through the photoflash lamp. To create a redeve effect or to adjust the light output, the lamp current needs to be stopped or guenched with an IGBT before discharging the photoflash capacitor fully. The IGBT device also controls the 4kV trigger pulse required to ionize the Xenon gas in the photoflash lamp. Figure 8 is a schematic of a fully functional photoflash application with the LT3585-0 serving as the IGBT driver. An IGBT driver charges the gate capacitance to start the flash. The IGBT driver does not need to pull up the gate significantly fast because of the inherently slow nature of the IGBT. A rise time of 2µs is sufficient to charge the gate of the IGBT and create a trigger pulse. With slower rise times, the trigger circuitry will not have a fast enough edge to create the required 4kV pulse. The fall time of the IGBT driver is critical to the

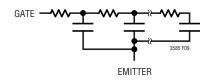

safe operation of the IGBT. The IGBT gate is a network of resistors and capacitors, as shown in Figure 9. When the gate terminal is pulled low, the capacitance closest to the terminal goes low but the capacitance further from the terminal remains high. This causes a smaller portion of the device to handle a larger portion of the current, which can damage the device. The pull-down circuitry needs to pull down slower than the internal RC time constant in the gate of the IGBT. This is easily accomplished with a resistor placed in series with the IGBTPD pin.

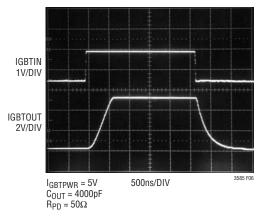

The LT3585 series integrated IGBT drive circuit is independent of the charging function and draws its power from the IGBTPWR pin. The drive pulls high to within 200mV of IGBTPWR and pulls down to 100mV. The circuit's switching waveform is shown in Figure 6. The rise and fall times are measured using a 4000pF output capacitor. The typical 10% to 90% rise time is 320ns when IGBTPWR

## **APPLICATIONS INFORMATION**

is 5V and IGBTIN is driven by a 5V signal. The typical 90% to 10% fall time is 125ns but varies with  $R_{PD}$  given by Figure 7. The IGBT driver pulls a peak of 50mA when driving an IGBT with minimal quiescent current. In the low state, an active pull-down network is used during the initial transition but is deactivated after an internal time constant. This allows the IGBT driver's quiescent current

to drop to approximately 0.1µA during idle conditions. The pull-down circuit will clamp the output below 0.8V for currents not exceeding 10mA in its idle state. The pull-up network is always active when the IGBTIN is greater than 1.5V. Table 4 is a list of recommended IGBT devices for strobe applications. These devices are all packaged in 8-lead TSSOP packages unless otherwise noted.

#### Table 4. Recommended IGBTs

| PART                                                   | DRIVE VOLTAGE (V)    | BREAKDOWN VOLTAGE (V)    | COLLECTOR CURRENT<br>(PULSED) (A) | VENDOR                                                                   |

|--------------------------------------------------------|----------------------|--------------------------|-----------------------------------|--------------------------------------------------------------------------|

| CY25CAH-8F*<br>CY25CAJ-8F*<br>CY25BAH-8F<br>CY25BAJ-8F | 2.5<br>4<br>2.5<br>4 | 400<br>400<br>400<br>400 | 150<br>150<br>150<br>150          | Renesas<br>(408) 382-7500<br>www.renesas.com                             |

| GT8G133                                                | 4                    | 400                      | 150                               | Toshiba Semiconductor<br>(949) 623-2900<br>www.semicon.toshiba.co.jp/eng |

\*Packaged in 8-lead VSON-8 pacakge.

Figure 8. Complete Xenon Circuit

Figure 9. IGBT Gate

### **APPLICATIONS INFORMATION**

#### **Board Layout**

The high voltage operation of these parts demand careful attention to board layout. You will not get advertised performance with careless layout. Figure 10 shows the recommended component placement. Keep the area for the high voltage end of the secondary as small as possible. Also note the larger than minimum spacing for all high voltage nodes in order to meet breakdown voltage requirements for the circuit board. It is imperative to keep the electrical path formed by C1, the primary of T1, and the LT3585 series IC as short as possible. If this path is haphazardly made long, it will effectively increase the leakage inductance of T1, which may result in an overvoltage condition on the SW pin. The CHRG/IADJ pin trace should be kept as short as possible while minimizing the adjacent edge with the SW pin trace. This will eliminate false toggling of the CHRG/IADJ pin during sharp transitions on the SW pin. Thermal vias should be added underneath the Exposed Pad, Pin 11, to enhance the LT3585's thermal performance. These vias should go directly to a large area of ground plane. Acting as a heat sink, the thermal vias/ground plane will lower the device's operating temperature.

Figure 10. LT3585 Suggested Layout

### TYPICAL APPLICATIONS

Figure 11. LT3585-0 Photoflash Charger Uses High Efficiency 3mm Tall Transformer

Figure 12. LT3585-1 Photoflash Charger Uses High Efficiency 2mm Tall Transformer

### **TYPICAL APPLICATIONS**

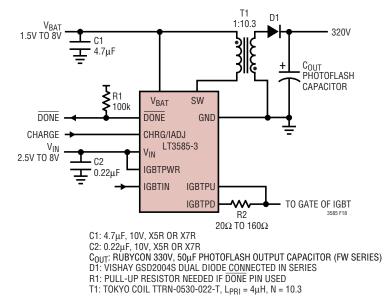

Figure 14. LT3585-3 Uses High Efficiency 3mm Tall Transformers

# TYPICAL APPLICATIONS

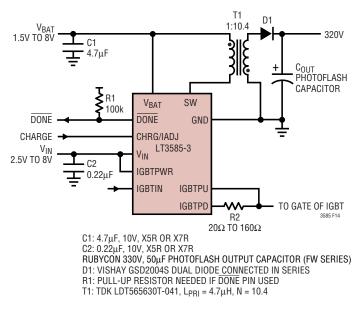

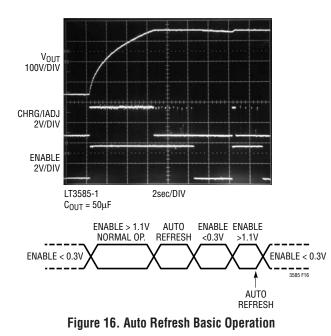

The LT3585 series can be auto-refreshed using the additional circuitry shown in Figure 15 with its basic operation shown in Figure 16. The ENABLE pin is used to enable or disable the auto-refresh charging mode. Without an auto-refresh circuit, the output voltage will droop due to output capacitor and output diode leakage currents. The circuit in Figure 15 uses the DONE and CHRG/IADJ pins to form an open-loop control scheme. The output voltage target is sensed through the DONE pin with the PFET of U1, Panasonic UP04979 composite transistor. When the

U1: PANASONIC UP04979 COMPOSITE TRANSISTORS

Figure 15. Auto Refresh Application

DONE pin goes low during the V<sub>OUT</sub> trip condition, the PFET charges the auto-refresh timing node comprised of R<sub>T</sub> and C<sub>T</sub>, and in turn, pulls the CHRG/IADJ pin low through a NFET and disables the LT3585 series part. The DONE pin immediately goes high in shutdown, releasing the timing node and allowing the voltage at Pins 2 and 3 to decay. After approximately a R<sub>T</sub>C<sub>T</sub> time constant, the CHRG/IADJ pin is released and the LT3585 series part is enabled. This cycle is repeated to maintain a constant DC output voltage. The open-loop control method places a constraint on the control loop dominant time constant, R<sub>T</sub> • C<sub>T</sub>, given by:

$$R_{T}C_{T} > \frac{2 \bullet I_{PK}^{2} \bullet L_{PRI}}{I_{LK} \bullet V_{BAT}}$$

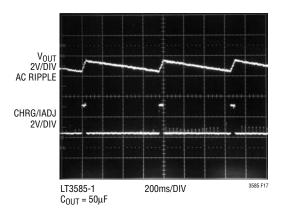

where  $I_{LK}$  is the known leakage current,  $I_{PK}$  is the transformer peak primary current, and  $L_{PRI}$  is the transformer primary inductance. If this condition is not met, a runaway condition could occur. The LT3585 series part would continue to charge the output voltage past the internal output trip voltage. Figure 17 shows the AC ripple of a typical auto-refresh circuit with the proper selection of  $R_T$  and  $C_T$ .

Figure 17. V<sub>OUT</sub> AC Ripple in Auto Refresh Mode

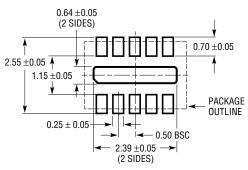

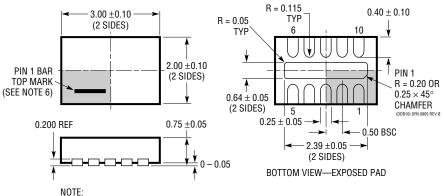

### **PACKAGE DESCRIPTION**

**DDB Package** 10-Lead Plastic DFN ( $3mm \times 2mm$ ) (Reference LTC DWG # 05-08-1722 Rev Ø)

RECOMMENDED SOLDER PAD PITCH AND DIMENSIONS

1. DRAWING CONFORMS TO VERSION (WECD-1) IN JEDEC PACKAGE OUTLINE M0-229

2. DRAWING NOT TO SCALE

ALL DIMENSIONS ARE IN MILLIMETERS

AL DIMENSIONS OF EXPOSED PAD ON BOTTOM OF PACKAGE DO NOT INCLUDE

MOLD FLASH. MOLD FLASH, IF PRESENT, SHALL NOT EXCEED 0.15mm ON ANY SIDE

5. EXPOSED PAD SHALL BE SOLDER PLATED

6. SHADED AREA IS ONLY A REFERENCE FOR PIN 1 LOCATION ON THE TOP AND BOTTOM OF PACKAGE

# TYPICAL APPLICATION

### **RELATED PARTS**

| PART NUMBER                                                 | DESCRIPTION                                                                           | COMMENTS                                                                                                                                                                                                 |  |  |

|-------------------------------------------------------------|---------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| LTC <sup>®</sup> 3407                                       | Dual 600mA (I <sub>OUT</sub> ), 1.5MHz, Synchronous Step-Down DC/DC Converter         | 96% Efficiency, V <sub>IN</sub> : 2.5V to 5.5V, V <sub>OUT</sub> : 0.6V to 5V, I <sub>Q</sub> = 40 $\mu$ A, Converter I <sub>SD</sub> <1 $\mu$ A, 10-Lead MSE/10-Lead DFN Packages                       |  |  |

| LT3420/LT3420-1                                             | 1.4A/1A, Photoflash Capacitor Chargers with Charges<br>Automatic Top-Off              | Charges 220µF to 320V in 3.7 Seconds from 5V, Automatic Top-Off $V_{IN}$ : 2.2V to 16V, $I_Q$ = 90µA, $I_{SD}$ < 1µA, 10-Lead MS/10-Lead DFN Packages                                                    |  |  |

| LTC3425                                                     | 3A (I <sub>OUT</sub> ), 8MHz, 4-Phase Synchronous Step-Up<br>DC/DC Converter          | 95% Efficiency, V <sub>IN</sub> : 0.5V to 4.5V, V <sub>OUT</sub> : 2.4V to 5.25V, I <sub>Q</sub> = 12µA, I <sub>SD</sub> < 1µA, 32-Lead 5mm × 5mm QFN Package                                            |  |  |

| LTC3440                                                     | 600mA (I <sub>OUT</sub> ), Synchronous Buck-Boost DC/DC Converter                     | 95% Efficiency, V <sub>IN</sub> : 2.5V to 5.5V, V <sub>OUT</sub> : 2.5V to 5.5V, Converter $I_Q$ = 25µA, $I_{SD}$ < 1µA, 10-Lead MS/10-Lead DFN Packages                                                 |  |  |

| LT3463/LT3463A                                              | Dual Boost (250mA)/Inverting (250mA/400mA) DC/DC<br>Converter for CCD Bias            | C Integrated Schottkys, $V_{IN}$ : 2.4V to 15V, $V_{OUT(MAX)} = \pm 40V$ , DC/DC Converter for CCD Bias, $I_Q = 40\mu$ A, $I_{SD} < 1\mu$ A, 10-LeadDFN Packa                                            |  |  |

| LT3468                                                      | Photoflash Capacitor Charger in ThinSOT <sup>TM</sup> Package                         | Charges 100µF to 320V in 4.6 Seconds from 3.6V, $V_{IN}$ : 2.5V to 16V, $I_Q$ = 5mA, $I_{SD}$ < 1µA, 5-Lead TSOT-23 Package                                                                              |  |  |

| LT3472                                                      | Dual ±34V, 1.2MHz Boost (350mA)/Inverting (400mA)<br>DC/DC Converter for CCD Bias     | Integrated Schottkys, V <sub>IN</sub> : 2.2V to 16V, V <sub>OUT(MAX)</sub> = ±34V, DC/DC Converter for CCD Bias I <sub>Q</sub> = 2.8mA, I <sub>SD</sub> < 1 $\mu$ A, 10-Lead DFN Package                 |  |  |

| LT3484-0/LT3484-1 Photoflash Capacitor Chargers<br>LT3484-2 |                                                                                       | Charges 100µF to 320V in 4.6 Seconds from 3.6V, LT3484-0 V <sub>IN</sub> : 2.5V to 16V, V <sub>BAT</sub> : 1.8V to 16V, I <sub>Q</sub> = 5mA, I <sub>SD</sub> < 1µA, 6-lead 2mm $\times$ 3mm DFN Package |  |  |

| LT3485-0/LT3485-1<br>LT3485-2/LT3485-3                      | Photoflash Capacitor Charger with Output Voltage<br>Monitor and Integrated IGBT Drive | Charges 100µF Capacitor to 320V in 2.5 Seconds from 3.6V. $V_{IN}$ : 1.8V to 10V, $I_Q$ = 5mA, $I_{SD}$ < 1µA, 10-Lead 3mm $\times$ 3mm DFN Package                                                      |  |  |

ThinSOT is a trademark of Linear Technology Corporation.

3585f