## LTC1403-1/LTC1403A-1

GY Serial 12-Bit/14-Bit, 2.8Msps Sampling ADCs with Shutdown

### **FEATURES**

- 2.8Msps Conversion Rate

- Low Power Dissipation: 14mW

- 3V Single Supply Operation

- 2.5V Internal Bandgap Reference can be Overdriven

- 3-Wire Serial Interface

- Sleep (10μW) Shutdown Mode

- Nap (3mW) Shutdown Mode

- 80dB Common Mode Rejection

- ±1.25V Bipolar Input Range

- Tiny 10-Lead MSE Package

## **APPLICATIONS**

- Communications

- Data Acquisition Systems

- Uninterrupted Power Supplies

- Multiphase Motor Control

- Multiplexed Data Acquisition

## DESCRIPTION

The LTC®1403-1/LTC1403A-1 are 12-bit/14-bit, 2.8Msps serial ADCs with differential inputs. The devices draw only 4.7mA from a single 3V supply and come in a tiny 10-lead MSE package. A Sleep shutdown feature lowers power consumption to 10μW. The combination of speed, low power and tiny package makes the LTC1403-1/LTC1403A-1 suitable for high speed, portable applications.

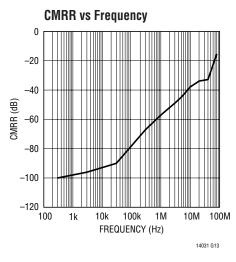

The 80dB common mode rejection allows users to eliminate ground loops and common mode noise by measuring signals differentially from the source.

The devices convert -1.25V to 1.25V bipolar inputs differentially. The absolute voltage swing for  $+A_{IN}$  and  $-A_{IN}$  extends from ground to the supply voltage.

The serial interface sends out the conversion results during the 16 clock cycles following CONV↑ for compatibility with standard serial interfaces. If two additional clock cycles for acquisition time are allowed after the data stream in between conversions, the full sampling rate of 2.8Msps can be achieved with a 50.4MHz clock.

17, LTC and LT are registered trademarks of Linear Technology Corporation.

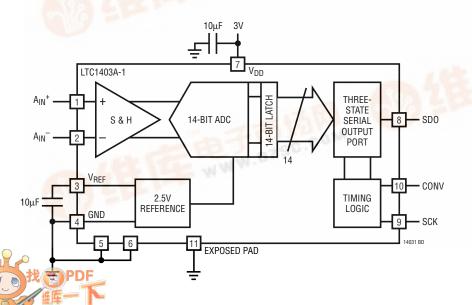

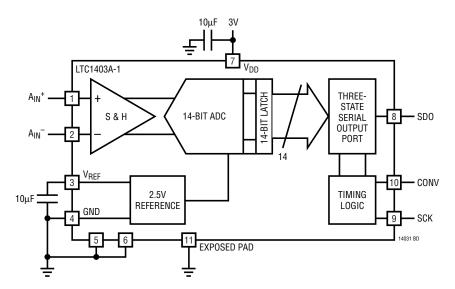

## **BLOCK DIAGRAM**

14031f

## **ABSOLUTE MAXIMUM RATINGS**

| (Notes 1, 2)                      |                              |

|-----------------------------------|------------------------------|

| Supply Voltage (V <sub>DD</sub> ) | 4V                           |

| Analog Input Voltage              |                              |

| (Note 3)                          | $-0.3V$ to $(V_{DD} + 0.3V)$ |

| Digital Input Voltage             | $-0.3V$ to $(V_{DD} + 0.3V)$ |

| Digital Output Voltage            | $-0.3V$ to $(V_{DD} + 0.3V)$ |

| Power Dissipation                 | 100mW                        |

| Operation Temperature Range       |                              |

| LTC1403C-1/LTC1403AC-1            | 0°C to 70°C                  |

| LTC1403I-1/LTC1403AI-1            | 40°C to 85°C                 |

| Storage Temperature Range         | –65°C to 150°C               |

| Lead Temperature (Soldering, 1    | 0 sec) 300°C                 |

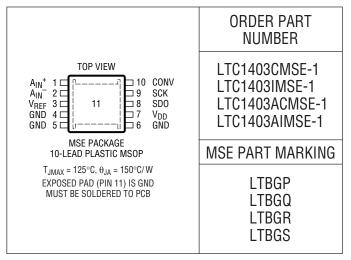

## PACKAGE/ORDER INFORMATION

Consult LTC Marketing for parts specified with wider operating temperature ranges.

## **CONVERTER CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . With internal reference. $V_{DD} = 3V$

|                               |                                                   |   |     | LTC1403-1 |     |     | LTC1403A-1 |     |                  |  |

|-------------------------------|---------------------------------------------------|---|-----|-----------|-----|-----|------------|-----|------------------|--|

| PARAMETER                     | CONDITIONS                                        |   | MIN | TYP       | MAX | MIN | TYP        | MAX | UNITS            |  |

| Resolution (No Missing Codes) |                                                   | • | 12  |           |     | 14  |            |     | Bits             |  |

| Integral Linearity Error      | (Notes 4, 5, 18)                                  | • | -2  | ±0.25     | 2   | -4  | ±0.5       | 4   | LSB              |  |

| Offset Error                  | (Notes 4, 18)                                     | • | -10 | ±1        | 10  | -20 | ±2         | 20  | LSB              |  |

| Gain Error                    | (Note 4, 18)                                      | • | -30 | ±5        | 30  | -60 | ±10        | 60  | LSB              |  |

| Gain Tempco                   | Internal Reference (Note 4)<br>External Reference |   |     | ±15<br>±1 |     |     | ±15<br>±1  |     | ppm/°C<br>ppm/°C |  |

## **ANALOG INPUT** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . $V_{DD} = 3V$

| SYMBOL              | PARAMETER                                                  | CONDITIONS                                 |   | MIN TYP              | MAX | UNITS |

|---------------------|------------------------------------------------------------|--------------------------------------------|---|----------------------|-----|-------|

| V <sub>IN</sub>     | Analog Differential Input Range (Notes 3, 8, 9)            | $2.7V \le V_{DD} \le 3.3V$                 | • | -1.25 to 1.25        |     | V     |

| V <sub>CM</sub>     | Analog Common Mode + Differential<br>Input Range (Note 10) |                                            |   | 0 to V <sub>DD</sub> |     | V     |

| I <sub>IN</sub>     | Analog Input Leakage Current                               |                                            | • |                      | 1   | μА    |

| C <sub>IN</sub>     | Analog Input Capacitance                                   |                                            |   | 13                   |     | pF    |

| t <sub>ACQ</sub>    | Sample-and-Hold Acquisition Time                           | (Note 6)                                   | • |                      | 39  | ns    |

| t <sub>AP</sub>     | Sample-and-Hold Aperture Delay Time                        |                                            |   | 1                    |     | ns    |

| t <sub>JITTER</sub> | Sample-and-Hold Aperture Delay Time Jitter                 |                                            |   | 0.3                  |     | ps    |

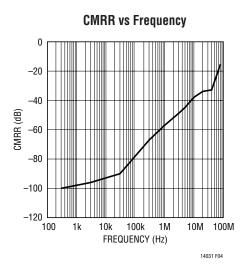

| CMRR                | Analog Input Common Mode Rejection Ratio                   | $f_{IN} = 1 MHz$ , $V_{IN} = 0 V$ to $3 V$ |   | -60                  |     | dB    |

|                     |                                                            | $f_{IN} = 100MHz$ , $V_{IN} = 0V$ to 3V    |   | -15                  |     | dB    |

**DYNAMIC ACCURACY** The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25 \,^{\circ}\text{C}$ .  $V_{DD} = 3V$ . Single-ended  $A_{IN}^+$  signal drive with  $A_{IN}^- = 1.5V$  DC. Differential signal drive with  $V_{CM} = 1.5V$  at  $A_{IN}^+$  and  $A_{IN}^-$

|        |                                          |                                                                                                                                                                                                                                      |   | L   | TC1403                   | -1  | L1  |                              |     |                    |

|--------|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|--------------------------|-----|-----|------------------------------|-----|--------------------|

| SYMBOL | PARAMETER                                | CONDITIONS                                                                                                                                                                                                                           |   | MIN | TYP                      | MAX | MIN | TYP                          | MAX | UNITS              |

| SINAD  | Signal-to-Noise Plus<br>Distortion Ratio | 100kHz Input Signal (Note 19)<br>1.4MHz Input Signal (Note 19)<br>100kHz Input Signal, External $V_{REF} = 3.3V$ ,<br>$V_{DD} \ge 3.3V$ (Note 19)<br>750kHz Input Signal, External $V_{REF} = 3.3V$ ,<br>$V_{DD} \ge 3.3V$ (Note 19) | • | 68  | 70.5<br>70.5<br>72<br>72 |     | 70  | 73.5<br>73.5<br>76.3<br>76.3 |     | dB<br>dB<br>dB     |

| THD    | Total Harmonic<br>Distortion             | 100kHz First 5 Harmonics (Note 19)<br>1.4MHz First 5 Harmonics (Note 19)                                                                                                                                                             | • |     | -87<br>-83               | -76 |     | -90<br>-86                   | -78 | dB<br>dB           |

| SFDR   | Spurious Free<br>Dynamic Range           | 100kHz Input Signal (Note 19)<br>1.4MHz Input Signal (Note 19)                                                                                                                                                                       |   |     | -87<br>-83               |     |     | -90<br>-86                   |     | dB<br>dB           |

| IMD    | Intermodulation<br>Distortion            | 0.625V <sub>P-P</sub> 1.4MHz Summed with 0.625V <sub>P-P</sub> 1.56MHz into A <sub>IN</sub> <sup>+</sup> and Inverted into A <sub>IN</sub> <sup>-</sup>                                                                              |   |     | -82                      |     |     | -82                          |     | dB                 |

|        | Code-to-Code<br>Transition Noise         | V <sub>REF</sub> = 2.5V (Note 18)                                                                                                                                                                                                    |   |     | 0.25                     |     |     | 1                            |     | LSB <sub>RMS</sub> |

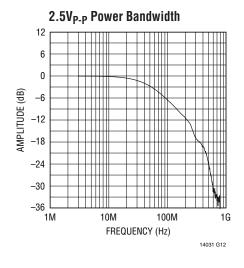

|        | Full Power Bandwidth                     | V <sub>IN</sub> = 2.5V <sub>P-P</sub> , SDO = 11585LSB <sub>P-P</sub> (Note 15)                                                                                                                                                      |   |     | 50                       |     |     | 50                           |     | MHz                |

|        | Full Linear Bandwidth                    | $S/(N + D) \ge 68dB$                                                                                                                                                                                                                 |   |     | 5                        |     |     | 5                            |     | MHz                |

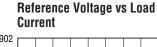

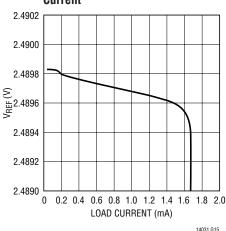

# **INTERNAL REFERENCE CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . $V_{DD} = 3V$

| PARAMETER                          | CONDITIONS                                              | MIN T | /P MAX | UNITS  |

|------------------------------------|---------------------------------------------------------|-------|--------|--------|

| V <sub>REF</sub> Output Voltage    | I <sub>OUT</sub> = 0                                    | 2     | .5     | V      |

| V <sub>REF</sub> Output Tempco     |                                                         | 1     | 5      | ppm/°C |

| V <sub>REF</sub> Line Regulation   | V <sub>DD</sub> = 2.7V to 3.6V, V <sub>REF</sub> = 2.5V | 60    | 00     | μV/V   |

| V <sub>REF</sub> Output Resistance | Load Current = 0.5mA                                    | 0     | .2     | Ω      |

| V <sub>REF</sub> Settling Time     |                                                         | 4     | 2      | ms     |

# **DIGITAL INPUTS AND DIGITAL OUTPUTS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . $V_{DD} = 3V$

| SYMBOL              | PARAMETER                                | CONDITIONS                                                                                           |   | MIN | TYP          | MAX | UNITS |

|---------------------|------------------------------------------|------------------------------------------------------------------------------------------------------|---|-----|--------------|-----|-------|

| $V_{IH}$            | High Level Input Voltage                 | V <sub>DD</sub> = 3.3V                                                                               | • | 2.4 |              |     | V     |

| V <sub>IL</sub>     | Low Level Input Voltage                  | V <sub>DD</sub> = 2.7V                                                                               | • |     |              | 0.6 | V     |

| I <sub>IN</sub>     | Digital Input Current                    | V <sub>IN</sub> = 0V to V <sub>DD</sub>                                                              | • |     |              | ±10 | μА    |

| C <sub>IN</sub>     | Digital Input Capacitance                | (Note 20)                                                                                            |   |     | 5            |     | pF    |

| V <sub>OH</sub>     | High Level Output Voltage                | $V_{DD} = 3V$ , $I_{OUT} = -200\mu A$                                                                | • | 2.5 | 2.9          |     | V     |

| V <sub>OL</sub>     | Low Level Output Voltage                 | V <sub>DD</sub> = 2.7V, I <sub>OUT</sub> = 160μA<br>V <sub>DD</sub> = 2.7V, I <sub>OUT</sub> = 1.6mA | • |     | 0.05<br>0.10 | 0.4 | V     |

| I <sub>OZ</sub>     | Hi-Z Output Leakage D <sub>OUT</sub>     | V <sub>OUT</sub> = 0V to V <sub>DD</sub>                                                             | • |     |              | ±10 | μА    |

| C <sub>OZ</sub>     | Hi-Z Output Capacitance D <sub>OUT</sub> |                                                                                                      |   |     | 1            |     | pF    |

| I <sub>SOURCE</sub> | Output Short-Circuit Source Current      | $V_{OUT} = 0V$ , $V_{DD} = 3V$                                                                       |   |     | 20           |     | mA    |

| I <sub>SINK</sub>   | Output Short-Circuit Sink Current        | $V_{OUT} = V_{DD} = 3V$                                                                              |   |     | 15           |     | mA    |

## LTC 1403-1/LTC 1403A-1

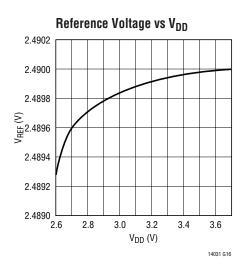

## POWER REQUIREMENTS

The • denotes the specifications which apply over the full operating temperature

range, otherwise specifications are at  $T_A = 25$ °C. (Note 17)

| SYMBOL          | PARAMETER               | CONDITIONS                                                               |   | MIN | TYP                  | MAX                  | UNITS                |

|-----------------|-------------------------|--------------------------------------------------------------------------|---|-----|----------------------|----------------------|----------------------|

| $V_{DD}$        | Supply Voltage          |                                                                          |   | 2.7 |                      | 3.6                  | V                    |

| I <sub>DD</sub> | Positive Supply Voltage | Active Mode<br>Nap Mode<br>Sleep Mode (LTC1403)<br>Sleep Mode (LTC1403A) | • |     | 4.7<br>1.1<br>2<br>2 | 7<br>1.5<br>15<br>10 | mA<br>mA<br>μΑ<br>μΑ |

| $P_{D}$         | Power Dissipation       | Active Mode with SCK in Fixed State (Hi or Lo)                           |   |     | 12                   |                      | mW                   |

## TIMING CHARACTERISTICS The • denotes the specifications which apply over the full operating temperature

range, otherwise specifications are at  $T_A = 25^{\circ}C$ .  $V_{DD} = 3V_{DD}$

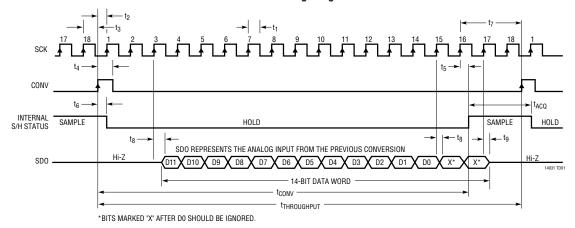

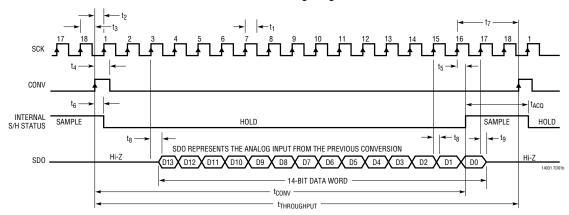

| SYMBOL                   | PARAMETER                                                     | CONDITIONS       |   | MIN  | TYP | MAX   | UNITS       |

|--------------------------|---------------------------------------------------------------|------------------|---|------|-----|-------|-------------|

| f <sub>SAMPLE(MAX)</sub> | Maximum Sampling Frequency per Channel (Conversion Rate)      |                  | • | 2.8  |     |       | MHz         |

| t <sub>THROUGHPUT</sub>  | Minimum Sampling Period (Conversion + Acquisiton Period)      |                  | • |      |     | 357   | ns          |

| t <sub>SCK</sub>         | Clock Period                                                  | (Note 16)        | • | 19.8 |     | 10000 | ns          |

| t <sub>CONV</sub>        | Conversion Time                                               | (Note 6)         |   | 16   | 18  |       | SCLK cycles |

| t <sub>1</sub>           | Minimum Positive or Negative SCLK Pulse Width                 | (Note 6)         |   | 2    |     |       | ns          |

| t <sub>2</sub>           | CONV to SCK Setup Time                                        | (Notes 6, 10)    |   | 3    |     |       | ns          |

| t <sub>3</sub>           | Nearest SCK Edge Before CONV                                  | (Note 6)         |   | 0    |     |       | ns          |

| t <sub>4</sub>           | Minimum Positive or Negative CONV Pulse Width                 | (Note 6)         |   | 4    |     |       | ns          |

| t <sub>5</sub>           | SCK to Sample Mode                                            | (Note 6)         |   | 4    |     |       | ns          |

| t <sub>6</sub>           | CONV to Hold Mode                                             | (Notes 6, 11)    |   | 1.2  |     |       | ns          |

| t <sub>7</sub>           | 16th SCK↑ to CONV↑ Interval (Affects Acquisition Period)      | (Notes 6, 7, 13) |   | 45   |     |       | ns          |

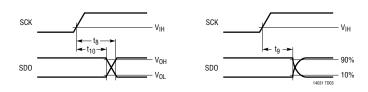

| t <sub>8</sub>           | Minimum Delay from SCK to Valid Data                          | (Notes 6, 12)    |   | 8    |     |       | ns          |

| t <sub>9</sub>           | SCK to Hi-Z at SDO                                            | (Notes 6, 12)    |   | 6    |     |       | ns          |

| t <sub>10</sub>          | Previous SDO Bit Remains Valid After SCK                      | (Notes 6, 12)    |   | 2    |     |       | ns          |

| t <sub>12</sub>          | V <sub>REF</sub> Settling Time After Sleep-to-Wake Transition | (Notes 6, 14)    |   |      | 2   |       | ms          |

**Note 1:** Absolute Maximum Ratings are those values beyond which the life of a device may be impaired.

Note 2: All voltage values are with respect to GND.

**Note 3:** When these pins are taken below GND or above  $V_{DD}$ , they will be clamped by internal diodes. This product can handle input currents greater than 100mA below GND or greater than  $V_{DD}$  without latchup.

**Note 4:** Offset and full-scale specifications are measured for a single-ended  $A_{IN}^+$  input with  $A_{IN}^-$  grounded and using the internal 2.5V reference.

**Note 5:** Integral linearity is tested with an external 2.55V reference and is defined as the deviation of a code from the straight line passing through the actual endpoints of a transfer curve. The deviation is measured from the center of quantization band.

Note 6: Guaranteed by design, not subject to test.

Note 7: Recommended operating conditions.

**Note 8:** The analog input range is defined for the voltage difference between  $A_{IN}^+$  and  $A_{IN}^-$ . Performance is specified with  $A_{IN}^- = 1.5V$  DC while driving  $A_{IN}^+$ .

**Note 9:** The absolute voltage at  $A_{IN}^+$  and  $A_{IN}^-$  must be within this range.

**Note 10:** If less than 3ns is allowed, the output data will appear one clock cycle later. It is best for CONV to rise half a clock before SCK, when running the clock at rated speed.

**Note 11:** Not the same as aperture delay. Aperture delay is smaller (1ns) because the 2.2ns delay through the sample-and-hold is subtracted from the CONV to Hold mode delay.

**Note 12:** The rising edge of SCK is guaranteed to catch the data coming out into a storage latch.

**Note 13:** The time period for acquiring the input signal is started by the 16th rising clock and it is ended by the rising edge of convert.

**Note 14:** The internal reference settles in 2ms after it wakes up from Sleep mode with one or more cycles at SCK and a  $10\mu$ F capacitive load.

**Note 15:** The full power bandwidth is the frequency where the output code swing drops to 3dB with a  $2.5V_{P-P}$  input sine wave.

**Note 16:** Maximum clock period guarantees analog performance during conversion. Output data can be read without an arbitrarily long clock.

**Note 17:**  $V_{DD} = 3V$ ,  $f_{SAMPLE} = 2.8 Msps$ .

**Note 18:** The LTC1403A-1 is measured and specified with 14-bit Resolution (1LSB =  $152\mu V$ ) and the LTC1403-1 is measured and specified with 12-bit Resolution (1LSB =  $610\mu V$ ).

**Note 19:** Full-scale sinewaves are fed into the noninverting input while the inverting input is kept at 1.5V DC.

**Note 20:** The sampling capacitor at each input accounts for 4.1pF of the input capacitance.

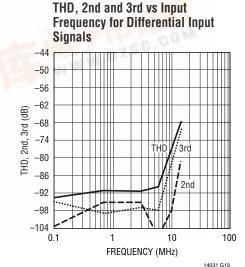

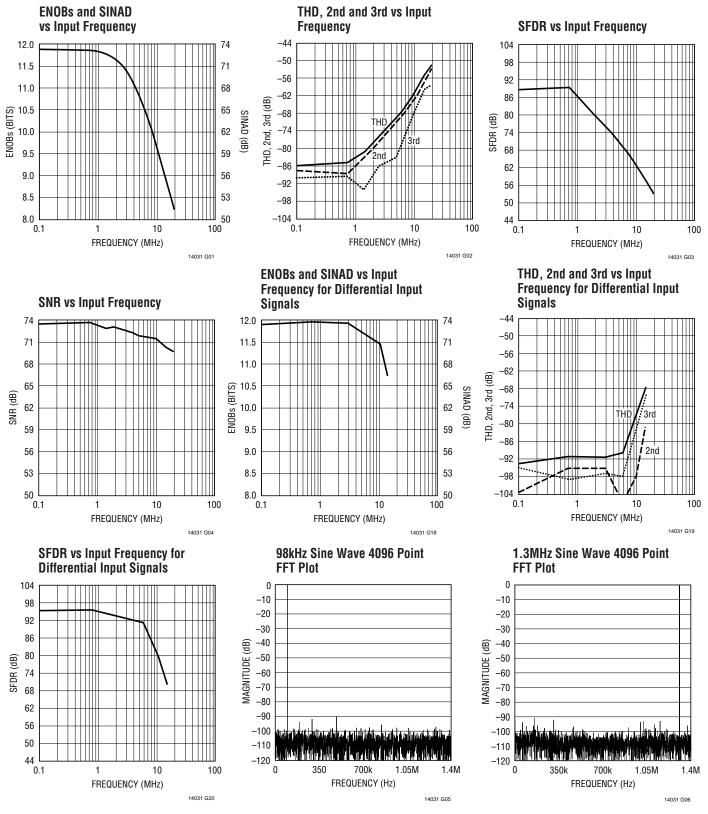

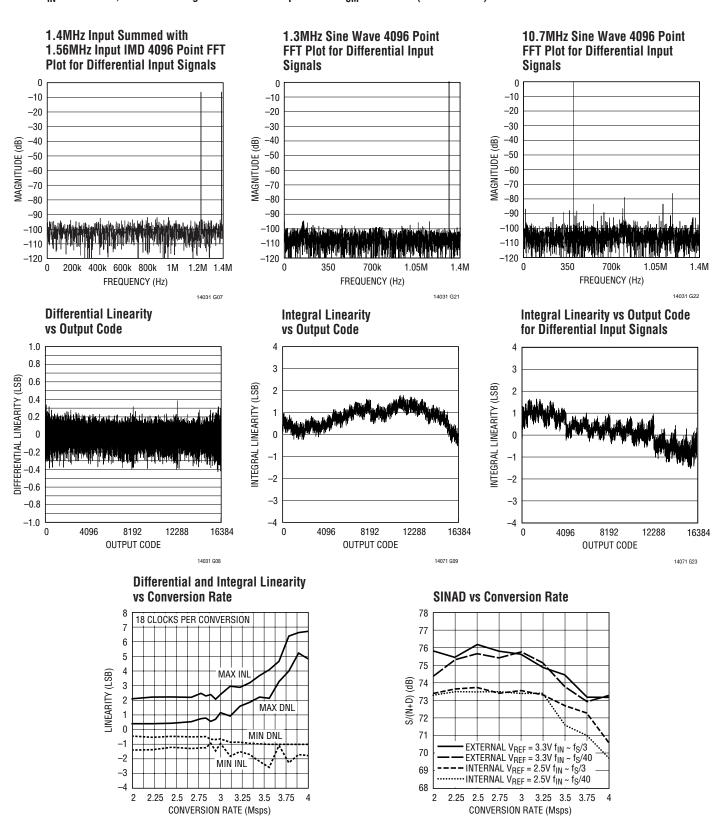

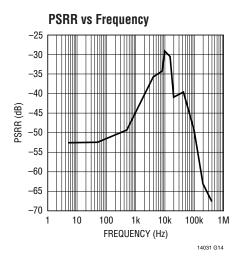

# **TYPICAL PERFORMANCE CHARACTERISTICS** $T_A = 25^{\circ}C$ , $V_{DD} = 3V$ . Single ended $A_{IN}^+$ signal drive with $A_{IN}^- = 1.5V$ DC, differential signals drive both inputs with $V_{CM} = 1.5V$ DC (LTC1403A-1)

# **TYPICAL PERFORMANCE CHARACTERISTICS** $T_A = 25^{\circ}C$ , $V_{DD} = 3V$ . Single ended $A_{IN}^+$ signal drive with $A_{IN}^- = 1.5V$ DC, differential signals drive both inputs with $V_{CM} = 1.5V$ DC (LTC1403A-1)

14031 G11

## TYPICAL PERFORMANCE CHARACTERISTICS $T_A = 25^{\circ}C$ , $V_{DD} = 3V$ (LTC1403-1 and LTC1403A-1)

### PIN FUNCTIONS

$A_{IN}^+$  (Pin 1): Noninverting Analog Input.  $A_{IN}^+$  operates fully differentially with respect to  $A_{IN}^-$  with a -1.25V to 1.25V differential swing with respect to  $A_{IN}^-$  and a 0V to  $V_{DD}$  common mode swing.

$A_{IN}^-$  (Pin 2): Inverting Analog Input.  $A_{IN}^-$  operates fully differentially with respect to  $A_{IN}^+$  with a 1.25V to -1.25V differential swing with respect to  $A_{IN}^+$  and a 0V to  $V_{DD}$  common mode swing.

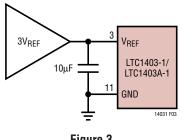

$V_{REF}$  (Pin 3): 2.5V Internal Reference. Bypass to GND and to a solid analog ground plane with a 10μF ceramic capacitor (or 10μF tantalum in parallel with 0.1μF ceramic). Can be overdriven by an external reference between 2.55V and  $V_{DD}$ .

**GND** (Pins 4, 5, 6, 11): Ground and Exposed Pad. These ground pins and the exposed pad must be tied directly to the solid ground plane under the part. Keep in mind that analog signal currents and digital output signal currents flow through these pins.

**V<sub>DD</sub>** (**Pin 7**): 3V Positive Supply. This single power pin supplies 3V to the entire chip. Bypass to GND and to a solid

analog ground plane with a  $10\mu F$  ceramic capacitor (or  $10\mu F$  tantalum in parallel with  $0.1\mu F$  ceramic). Keep in mind that internal analog currents and digital output signal currents flow through this pin. Care should be taken to place the  $0.1\mu F$  bypass capacitor as close to Pins 6 and 7 as possible.

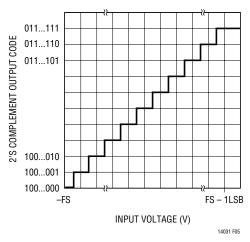

**SDO** (Pin 8): Three-State Serial Data Output. Each of output data words represents the difference between  $A_{IN}^+$  and  $A_{IN}^-$  analog inputs at the start of the previous conversion. The output format is 2's complement.

**SCK (Pin 9):** External Clock Input. Advances the conversion process and sequences the output data on the rising edge. Responds to TTL ( $\leq$ 3V) and 3V CMOS levels. One or more pulses wake from sleep.

**CONV** (Pin 10): Convert Start. Holds the analog input signal and starts the conversion on the rising edge. Responds to TTL (≤3V) and 3V CMOS levels. Two pulses with SCK in fixed high or fixed low state start Nap mode. Four or more pulses with SCK in fixed high or fixed low state start Sleep mode.

## **BLOCK DIAGRAM**

## TIMING DIAGRAM

#### LTC1403 Timing Diagram

#### LTC1403A Timing Diagram

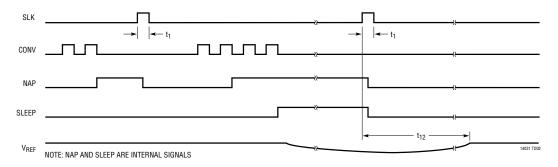

#### Nap Mode and Sleep Mode Waveforms

#### SCK to SDO Delay

#### DRIVING THE ANALOG INPUT

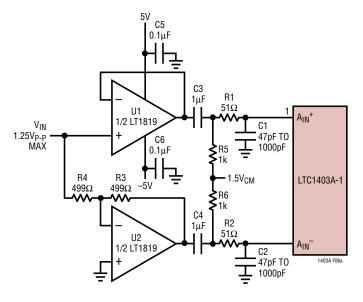

The differential analog inputs of the LTC1403-1/LTC1403A-1 are easy to drive. The inputs may be driven differentially or as a single-ended input (i.e., the  $A_{IN}^-$  input is set to  $V_{CM}$ ). Both differential analog inputs, A<sub>IN</sub><sup>+</sup> with A<sub>IN</sub><sup>-</sup>, are sampled at the same instant. Any unwanted signal that is common to both inputs of each input pair will be reduced by the common mode rejection of the sample-and-hold circuit. The inputs draw only one small current spike while charging the sample-and-hold capacitors at the end of conversion. During conversion, the analog inputs draw only a small leakage current. If the source impedance of the driving circuit is low, then the LTC1403-1/ LTC1403A-1 inputs can be driven directly. As source impedance increases, so will acquisition time. For minimum acquisition time with high source impedance, a buffer amplifier must be used. The main requirement is that the amplifier driving the analog input(s) must settle after the small current spike before the next conversion starts (settling time must be 39ns for full throughput rate). Also keep in mind while choosing an input amplifier, the amount of noise and harmonic distortion added by the amplifier.

#### CHOOSING AN INPUT AMPLIFIER

Choosing an input amplifier is easy if a few requirements are taken into consideration. First, to limit the magnitude of the voltage spike seen by the amplifier from charging the sampling capacitor, choose an amplifier that has a low output impedance ( $<100\Omega$ ) at the closed-loop bandwidth frequency. For example, if an amplifier is used with a gain of 1 and has a unity-gain bandwidth of 50MHz, then the output impedance at 50MHz must be less than  $100\Omega$ . The second requirement is that the closed-loop bandwidth must be greater than 40MHz to ensure adequate small-signal settling for full throughput rate. If slower op amps are used, more time for settling can be provided by increasing the time between conversions. The best choice for an op amp to drive the LTC1403-1/LTC1403A-1 will depend on the application. Generally, applications fall into two categories: AC applications where dynamic specifications are most critical and time domain applications where DC accuracy and settling time are most critical. The following list is a summary of the op amps that are suitable for driving the LTC1403-1/LTC1403A-1. (More detailed information is available in the Linear Technology Databooks and our website at www.linear.com.)

LTC®1566-1: Low Noise 2.3MHz Continuous Time Low-Pass Filter.

**LT1630:** Dual 30MHz Rail-to-Rail Voltage FB Amplifier. 2.7V to  $\pm 15$ V supplies. Very high  $A_{VOL}$ ,  $500\mu V$  offset and 520ns settling to 0.5LSB for a 4V swing. THD and noise are -93dB to 40kHz and below 1LSB to 320kHz ( $A_V=1$ ,  $2V_{P-P}$  into  $1k\Omega$ ,  $V_S=5V$ ), making the part excellent for AC applications (to 1/3 Nyquist) where rail-to-rail performance is desired. Quad version is available as LT1631.

**LT1632:** Dual 45MHz Rail-to-Rail Voltage FB Amplifier. 2.7V to  $\pm 15$ V supplies. Very high A<sub>VOL</sub>, 1.5mV offset and 400ns settling to 0.5LSB for a 4V swing. It is suitable for applications with a single 5V supply. THD and noise are -93dB to 40kHz and below 1LSB to 800kHz (A<sub>V</sub> = 1, 2V<sub>P-P</sub> into 1k $\Omega$ , V<sub>S</sub> = 5V), making the part excellent for AC applications where rail-to-rail performance is desired. Quad version is available as LT1633.

**LT1813:** Dual 100MHz 750V/ $\mu$ s 3mA Voltage Feedback Amplifier. 5V to  $\pm$ 5V supplies. Distortion is -86dB to 100kHz and -77dB to 1MHz with  $\pm$ 5V supplies (2V<sub>P-P</sub> into 500 $\Omega$ ). Excellent part for fast AC applications with  $\pm$ 5V supplies.

**LT1801:** 80MHz GBWP, -75dBc at 500kHz, 2mA/Amplifier, 8.5nV/ $\sqrt{\text{Hz}}$ .

**LT1806/LT1807:** 325MHz GBWP, -80dBc Distortion at 5MHz, Unity-Gain Stable, R-R In and Out, 10mA/Amplifier, 3.5nV/ $\sqrt{\text{Hz}}$ .

**LT1810:** 180MHz GBWP, -90dBc Distortion at 5MHz, Unity-Gain Stable, R-R In and Out, 15mA/Amplifier, 16nV/ $\sqrt{\text{Hz}}$ .

**LT1818/LT1819**: 400MHz,  $2500V/\mu s$ , 9mA, Single/Dual Voltage Mode Operational Amplifier.

**LT6200:** 165MHz GBWP, -85dBc Distortion at 1MHz, Unity-Gain Stable, R-R In and Out, 15mA/Amplifier, 0.95nV/ $\sqrt{\text{Hz}}$ .

**LT6203:** 100MHz GBWP, -80dBc Distortion at 1MHz, Unity-Gain Stable, R-R In and Out, 3mA/Amplifier, 1.9nV/ $\sqrt{Hz}$ .

**LT6600-10:** Amplifier/Filter Differential In/Out with 10MHz Cutoff.

#### INPUT FILTERING AND SOURCE IMPEDANCE

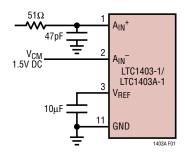

The noise and the distortion of the input amplifier and other circuitry must be considered since they will add to the LTC1403-1/LTC1403A-1 noise and distortion. The small-signal bandwidth of the sample-and-hold circuit is 50MHz. Any noise or distortion products that are present at the analog inputs will be summed over this entire bandwidth. Noisy input circuitry should be filtered prior to the analog inputs to minimize noise. A simple 1-pole RC filter is sufficient for many applications. For example, Figure 1 shows a 47pF capacitor from A<sub>IN</sub><sup>+</sup> to ground and a 51 $\Omega$  source resistor to limit the input bandwidth to 47MHz. The 47pF capacitor also acts as a charge reservoir for the input sample-and-hold and isolates the ADC input from sampling-glitch sensitive circuitry. High quality capacitors and resistors should be used since these components can add distortion. NPO and silvermica type dielectric capacitors have excellent linearity. Carbon surface mount resistors can generate distortion from self heating and from damage that may occur during soldering. Metal film surface mount resistors are much less susceptible to both problems. When high amplitude unwanted signals are close in frequency to the desired signal frequency, a multiple pole filter is required. High external source resistance, combined with the 13pF of input capacitance, will reduce the rated 50MHz bandwidth and increase acquisition time beyond 39ns.

Figure 1. RC Input Filter

#### INPUT RANGE

The analog inputs of the LTC1403-1/LTC1403A-1 may be driven fully differentially with a single supply. Each input may swing up to  $3V_{P-P}$  individually. In the conversion range, each input is always up to 1.25V more positive or more negative than the inverting input of each channel.

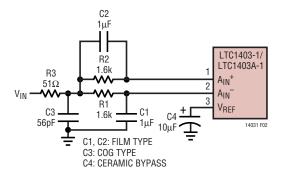

The ±1.25V range is also ideally suited for AC-coupled signals in single supply applications. Figure 2 shows how to AC couple signals in a single supply system without needing a mid-supply 1.5V external reference. The DC common mode level is supplied by the previous stage that is already bounded by the single supply voltage of the system. The common mode range of the inputs extend from ground to the supply voltage  $V_{DD}$ . If the difference between the A<sub>IN</sub><sup>+</sup> and A<sub>IN</sub><sup>-</sup> inputs exceeds 1.25V, the output code will stay fixed at zero and all ones and if this difference goes below -1.25V, the output code will stay fixed at one and all zeros.

Figure 2. AC Coupling of AC Signals with 1kHz Low Cut

#### INTERNAL REFERENCE

The LTC1403-1/LTC1403A-1 has an on-chip, temperature compensated, bandgap reference that is factory trimmed near 2.5V to obtain  $\pm 1.25V$  input span. The reference amplifier output V<sub>RFF</sub>, (Pin 3) must be bypassed with a capacitor to ground. The reference amplifier is stable with capacitors of 1µF or greater. For the best noise performance, a 10μF ceramic or a 10μF tantalum in parallel with a  $0.1\mu F$  ceramic is recommended. The  $V_{RFF}$  pin can be overdriven with an external reference as shown in Figure 3. The voltage of the external reference must be higher than the 2.5V of the class A pull-up output of the internal

Figure 3

reference. The recommended range for an external reference is 2.55V to  $V_{DD}$ . An external reference at 2.55V will see a DC quiescent load of 0.75mA and as much as 3mA during conversion.

#### INPUT SPAN VERSUS REFERENCE VOLTAGE

The differential input range has a unipolar voltage span that equals the difference between the voltage at the reference buffer output  $V_{REF}$  at Pin 3, and the voltage at the ground (Exposed Pad Ground). The differential input range of the ADC is  $\pm 1.25V$  when using the internal reference. The internal ADC is referenced to these two nodes. This relationship also holds true with an external reference.

#### **DIFFERENTIAL INPUTS**

The LTC1403-1/LTC1403A-1 have a unique differential sample-and-hold circuit that allows inputs from ground to  $V_{DD}$ . The ADC will always convert the bipolar difference of  $A_{IN}^+ - A_{IN}^-$ , independent of the common mode voltage at the inputs. The common mode rejection holds up at extremely high frequencies, see Figure 4. The only requirement is that both inputs not go below ground or exceed  $V_{DD}$ . Integral nonlinearity errors (INL) and differential nonlinearity errors (DNL) are largely independent of the common mode voltage. However, the offset error will vary. The change in offset error is typically less than 0.1% of the common mode voltage.

Figure 4

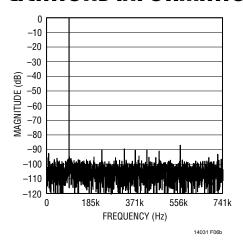

Figure 5 shows the ideal input/output characteristics for the LTC1403-1/LTC1403A-1. The code transitions occur midway between successive integer LSB values (i.e., 0.5LSB, 1.5LSB, 2.5LSB, FS – 1.5LSB). The output code is natural binary with 1LSB = 2.5V/16384 = 153 $\mu$ V for the LTC1403A-1, and 1LSB = 2.5V/4096 = 610 $\mu$ V for the LTC1403-1. The LTC1403A-1 has 1LSB RMS of random white noise. Figure 6a shows the LTC1819 converting a single ended input signal to differential input signals for optimum THD and SFDR performance as shown in the FFT plot (Figure 6b).

#### LTC1403-1/LTC1403A-1 Transfer Characteristic

Figure 5

Figure 6a. The LT1819 Driving the LTC1403A-1 Differentially

Figure 6b. LTC1403-1 6MHz Sine Wave 4096 Point FFT Plot with the LT1819 Driving the Inputs Differentially

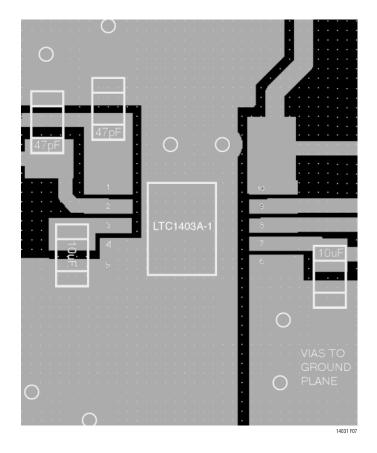

#### **Board Layout and Bypassing**

Wire wrap boards are not recommended for high resolution and/or high speed A/D converters. To obtain the best performance from the LTC1403-1/LTC1403A-1, a printed circuit board with ground plane is required. Layout for the printed circuit board should ensure that digital and analog signal lines are separated as much as possible. In particular, care should be taken not to run any digital track alongside an analog signal track. If optimum phase match between the inputs is desired, the length of the two input wires should be kept matched.

High quality tantalum and ceramic bypass capacitors should be used at the  $V_{DD}$  and  $V_{REF}$  pins as shown in the Block Diagram on the first page of this data sheet. For optimum performance, a  $10\mu F$  surface mount AVX capacitor with a  $0.1\mu F$  ceramic is recommended for the  $V_{DD}$  and  $V_{REF}$  pins. Alternatively,  $10\mu F$  ceramic chip capacitors such as Murata GRM219R60J106M may be used. The capacitors must be located as close to the pins as possible. The traces connecting the pins and the bypass capacitors must be kept short and should be made as wide as possible.

Figure 7 shows the recommended system ground connections. All analog circuitry grounds should be terminated at the LTC1403-1/LTC1403A-1 GND (Pins 4, 5, 6 and exposed pad). The ground return from the LTC1403-1/LTC1403A-1 (Pins 4, 5, 6 and exposed pad) to the power supply should be low impedance for noise free operation.

Figure 7. Recommended Layout

Digital circuitry grounds must be connected to the digital supply common. In applications where the ADC data outputs and control signals are connected to a continuously active microprocessor bus, it is possible to get errors in the conversion results. These errors are due to feedthrough from the microprocessor to the successive approximation comparator. The problem can be eliminated by forcing the microprocessor into a Wait state during conversion or by using three-state buffers to isolate the ADC data bus.

#### POWER-DOWN MODES

Upon power-up, the LTC1403-1/LTC1403A-1 is initialized to the active state and is ready for conversion. The Nap and Sleep mode waveforms show the power-down modes for the LTC1403-1/LTC1403A-1. The SCK and CONV inputs control the power-down modes (see Timing Diagrams). Two rising edges at CONV, without any intervening rising edges at SCK, put the LTC1403-1/LTC1403A-1 in Nap

mode and the power drain drops from 14mW to 6mW. The internal reference remains powered in Nap mode. One or more rising edges at SCK wake up the LTC1403-1/LTC1403A-1 for service very quickly, and CONV can start an accurate conversion within a clock cycle. Four rising edges at CONV, without any intervening rising edges at SCK, put the LTC1403-1/LTC1403A-1 in Sleep mode and the power drain drops from 16mW to  $10\mu W$ . One or more rising edges at SCK wake up the LTC1403-1/LTC1403A-1 for operation. The internal reference (VREF) takes 2ms to slew and settle with a  $10\mu F$  load. Note that, using sleep mode more frequently than every 2ms, compromises the settled accuracy of the internal reference. Note that, for slower conversion rates, the Nap and Sleep modes can be used for substantial reductions in power consumption.

#### **DIGITAL INTERFACE**

The LTC1403-1/LTC1403A-1 has a 3-wire SPI (Serial Protocol Interface) interface. The SCK and CONV inputs and SDO output implement this interface. The SCK and CONV inputs accept swings from 3V logic and are TTL compatible, if the logic swing does not exceed  $V_{DD}$ . A detailed description of the three serial port signals follows:

#### Conversion Start Input (CONV)

The rising edge of CONV starts a conversion, but subseguent rising edges at CONV are ignored by the LTC1403-1/ LTC1403A-1 until the following 16 SCK rising edges have occurred. It is necessary to have a minimum of 16 rising edges of the clock input SCK between rising edges of CONV. But to obtain maximum conversion speed, it is necessary to allow two more clock periods between conversions to allow 39ns of acquisition time for the internal ADC sample-and-hold circuit. With 16 clock periods per conversion, the maximum conversion rate is limited to 2.8Msps to allow 39ns for acquisition time. In either case, the output data stream comes out within the first 16 clock periods to ensure compatibility with processor serial ports. The duty cycle of CONV can be arbitrarily chosen to be used as a frame sync signal for the processor serial port. A simple approach to generate CONV is to create a pulse that is one SCK wide to drive the LTC1403-1/ LTC1403A-1 and then buffer this signal with the appropriate number of inverters to ensure the correct delay driving the frame sync input of the processor serial port. It is good practice to drive the LTC1403-1/LTC1403A-1 CONV input first to avoid digital noise interference during the sample-to-hold transition triggered by CONV at the start of conversion. It is also good practice to keep the width of the low portion of the CONV signal greater than 15ns to avoid introducing glitches in the front end of the ADC just before the sample-and-hold goes into hold mode at the rising edge of CONV.

#### Minimizing Jitter on the CONV Input

In high speed applications where high amplitude sinewaves above 100kHz are sampled, the CONV signal must have as little jitter as possible (10ps or less). The square wave output of a common crystal clock module usually meets this requirement easily. The challenge is to generate a CONV signal from this crystal clock without jitter corruption from other digital circuits in the system. A clock divider and any gates in the signal path from the crystal clock to the CONV input should not share the same integrated circuit with other parts of the system. As shown in the interface circuit examples, the SCK and CONV inputs should be driven first, with digital buffers used to drive the serial port interface. Also note that the master clock in the DSP may already be corrupted with jitter, even if it comes directly from the DSP crystal. Another problem with high speed processor clocks is that they often use a low cost, low speed crystal (i.e., 10MHz) to generate a fast, but jittery, phase-locked-loop system clock (i.e., 40MHz). The jitter in these PLL-generated high speed clocks can be several nanoseconds. Note that if you choose to use the frame sync signal generated by the DSP port, this signal will have the same jitter of the DSP's master clock.

#### Serial Clock Input (SCK)

The rising edge of SCK advances the conversion process and also udpates each bit in the SDO data stream. After CONV rises, the third rising edge of SCK starts clocking out the 12/14 data bits with the MSB sent first. A simple approach is to generate SCK to drive the LTC1403-1/LTC1403A-1 first and then buffer this signal with the appropriate number of inverters to drive the serial clock input of the processor serial port. Use the falling edge of the clock to latch data from the Serial Data Output (SDO)

into your processor serial port. The 14-bit Serial Data will be received right justified, in a 16-bit word with 16 or more clocks per frame sync. It is good practice to drive the LTC1403-1/LTC1403A-1 SCK input first to avoid digital noise interference during the internal bit comparison decision by the internal high speed comparator. Unlike the CONV input, the SCK input is not sensitive to jitter because the input signal is already sampled and held constant.

#### Serial Data Output (SDO)

Upon power-up, the SDO output is automatically reset to the high impedance state. The SDO output remains in high impedance until a new conversion is started. SDO sends out 12/14 bits in 2's complement format in the output data stream beginning at the third rising edge of SCK after the rising edge of CONV. SDO is always in high impedance mode when it is not sending out data bits. Please note the delay specification from SCK to a valid SDO. SDO is always guaranteed to be valid by the next rising edge of SCK. The 16-bit output data stream is compatible with the 16-bit or 32-bit serial port of most processors.

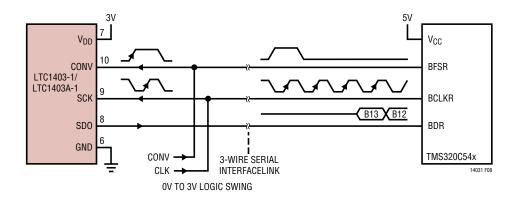

#### HARDWARE INTERFACE TO TMS320C54x

The LTC1403-1/LTC1403A-1 is a serial output ADC whose interface has been designed for high speed buffered serial ports in fast digital signal processors (DSPs). Figure 8 shows an example of this interface using a TMS320C54X.

The buffered serial port in the TMS320C54x has direct access to a 2kB segment of memory. The ADC's serial data can be collected in two alternating 1kB segments, in real time, at the full 2.8Msps conversion rate of the LTC1403-1/ LTC1403A-1. The DSP assembly code sets frame sync mode at the BFSR pin to accept an external positive going pulse and the serial clock at the BCLKR pin to accept an external positive edge clock. Buffers near the LTC1403-1/ LTC1403A-1 may be added to drive long tracks to the DSP to prevent corruption of the signal to LTC1403-1/ LTC1403A-1. This configuration is adequate to traverse a typical system board, but source resistors at the buffer outputs and termination resistors at the DSP, may be needed to match the characteristic impedance of very long transmission lines. If you need to terminate the SDO transmission line, buffer it first with one or two 74ACTxx gates. The TTL threshold inputs of the DSP port respond properly to the 3V swing from the SDO pin.

Figure 8. DSP Serial Interface to TMS320C54x

```

; 10-23-03 *********

; Files: 014SI.ASM -> 1403 bipolar Sine wave collection with Serial Port interface

bvectors.asm buffered mode.

s2k14ini.asm

2k buffer size.

; first element at 1024, last element at 1023, two middles at 2047 and 0000

; bipolar mode

; Works 16 or 64 clock frames.

; negative edge BCLKR

; negative BFSR pulse

; -0 data shifted

; 1' cable from counter to CONV at DUT

; 2' cable from counter to CLK at DUT

: *************

***********

.width

160

.length 110

.title "sineb0 BSP in auto buffer mode"

.mmreas

.setsect ".text", 0x500,0

.setsect "vectors", 0x180,0

;Set address of executable

;Set address of incoming 1403 data

.setsect "buffer", 0x800,0

.setsect "result", 0x1800,0

;Set address of BSP buffer for clearing

;Set address of result for clearing

.text

;.text marks start of code

start:

; this label seems necessary

; Make sure /PWRDWN is low at J1-9

; to turn off AC01 adc

tim=#0fh

prd=#0fh

tcr = #10h

; stop timer

; stop TDM serial port to AC01

tspc = #0h

; init stack pointer.

sp = #0700h

dp = #0

; data page

ar2 = #1800h

; pointer to computed receive buffer.

ar3 = #0800h

; pointer to Buffered Serial Port receive buffer

ar4 = #0h

; reset record counter

call sineinit

; Double clutch the initialization to insure a proper

sinepeek:

call sineinit

; reset. The external frame sync must occur 2.5 clocks

; or more after the port comes out of reset.

wait

goto wait

—Buffered Receive Interrupt Routine —

breceive:

ifr = #10h

; clear interrupt flags

TC = bitf(@BSPCE, #4000h); check which half (bspce(bit14)) of buffer

if (NTC) goto bufull

; if this still the first half get next half

bspce = #(2023h + 08000h); turn on halt for second half (bspce(bit15))

return_enable

---mask and shift input data ---

bufull:

b = *ar3 + << -0

; load acc b with BSP buffer and shift right -0

b = \#03FFFh \& b

; mask out the TRISTATE bits with #03FFFh

b = b ^ #2000h

; invert the MSB for bipolar operation

*ar2+ = data(#0bh)

; store B to out buffer and advance AR2 pointer

TC = (@ar2 == #02000h); output buffer is 2k starting at 1800h

if (TC) goto start

; restart if out buffer is at 1fffh

goto bufull

```

```

-dummy bsend return-

bsend return_enable

; this is also a dummy return to define bsend

; in vector table file BVECTORS.ASM

--- end ISR -

.copy "c:\dskplus\1403\s2k14ini.asm" ;initialize buffered serial port

.space 16*32

; clear a chunk at the end to mark the end

VECTORS

.sect "vectors"

;The vectors start here

.sect "buffer"

; Set address of BSP buffer for clearing

.space 16*0x800

.sect "result"

;Set address of result for clearing

.space 16*0x800

.end

************************

; File: BVECTORS.ASM -> Vector Table for the 'C54x DSKplus

BSP vectors and Debugger vectors

TDM vectors just return

; The vectors in this table can be configured for processing external and

; internal software interrupts. The DSKplus debugger uses four interrupt

; vectors. These are RESET, TRAP2, INT2, and HPIINT.

* DO NOT MODIFY THESE FOUR VECTORS IF YOU PLAN TO USE THE DEBUGGER *

; All other vector locations are free to use. When programming always be sure

; the HPIINT bit is unmasked (IMR=200h) to allow the communications kernel and

; host PC interact. INT2 should normally be masked (IMR(bit 2) = 0) so that the

; DSP will not interrupt itself during a HINT. HINT is tied to INT2 externally.

;

.title "Vector Table"

.mmreas

goto #80h

;00; RESET * DO NOT MODIFY IF USING DEBUGGER *

nop

nop

return_enable

;04; non-maskable external interrupt

nmi

nop

nop

trap2

goto #88h

;08; trap2 * DO NOT MODIFY IF USING DEBUGGER *

nop

nop

.space 52*16

;0C-3F: vectors for software interrupts 18-30

int.0

return_enable

;40; external interrupt int0

nop

nop

int1

return_enable ;44; external interrupt int1

nop

nop

```

```

int2

;48; external interrupt int2

return_enable

nop

nop

nop

tint

;4C; internal timer interrupt

return_enable

nop

nop

nop

brint

goto breceive

;50; BSP receive interrupt

nop

nop

bxint

goto bsend

;54; BSP transmit interrupt

nop

nop

nop

trint

return_enable

;58; TDM receive interrupt

nop

nop

txint

return_enable

;5C; TDM transmit interrupt

nop

nop

int3

return_enable

;60; external interrupt int3

nop

nop

hpiint

dgoto #0e4h

;64; HPIint * DO NOT MODIFY IF USING DEBUGGER *

nop

.space 24*16

;68-7F; reserved area

(C) COPYRIGHT TEXAS INSTRUMENTS, INC. 1996

******************

* File: s2k14ini.ASM BSP initialization code for the 'C54x DSKplus *

for use with 1403 in buffered mode

BSPC and SPC are the same in the 'C542

BSPCE and SPCE seem the same in the 'C542

.title "Buffered Serial Port Initialization Routine"

ON

.set 1

OFF

.set !ON

YES

.set 1

.set !YES

NO

BIT_8

.set 2

BIT_10

.set 1

BIT_12

.set 3

BIT_16

.set 0

.set 0x80

*********************

* This is an example of how to initialize the Buffered Serial Port (BSP).

* The BSP is initialized to require an external CLK and FSX for

^{\star} operation. The data format is 16-bits, burst mode, with autobuffering

* enabled.

```

```

******************

*LTC1403 timing from board with 10MHz crystal.

*10MHz, divided from 40MHz, forced to CLKIN by 1403 board.

*Horizontal scale is 25ns/chr or 100ns period at BCLKR

*Timing measured at DSP pins. Jxx pin labels for jumper cable.

*BFSR Pin J1-20 ~~\

*BDR Pin J1-26 _-_-<B13-B12-B11-B10-B09-B08-B07-B06-B05-B04-B03-B02-B01-B00>-_-<B13-B12*

*CLKIN Pin J5-09 ~~~~\_

/~~~~~\ /~~~~~\ /~~~~~\

/~~~~~

*C542 read

0 B13 B12 B11 B10 B09 B08 B07 B06 B05 B04 B03 B02 B01 B00 0 0 B13 B12*

* negative edge BCLKR

* negative BFSR pulse

* no data shifted

* 1' cable from counter to CONV at DUT

* 2' cable from counter to CLK at DUT

*No right shift is needed to right justify the input data in the main program

*the two msbs should also be masked

*************************

NO

;(digital looback mode?)

DLB bit

Loopback

BIT_16

FO bit

Format

.set

;(Data format? 16,12,10,8)

NO

;(internal Frame syncs generated?) TXM bit

Int.Svnc

.set

IntCLK

.set

NO

;(internal clks generated?)

BurstMode

YES

.set

;(if BurstMode=NO, then Continuous) FSM bit

;(3=default value, 1/4 CLOCKOUT)

CLKDIV

.set

3

.set

PCM_Mode

NO

; (Turn on PCM mode?)

;(change polarity)YES=^^^\_/^^^, NO=___

FS_polarity

YES

.set

;(change polarity)for BCLKR YES=_/^, NO=~\_

CLK_polarity

.set

NO

Frame_ignore

!YES

;(inverted !YES -ignores frame)

.set

XMTautobuf

NO

;(transmit autobuffering)

.set

RCVautobuf

YES

.set

; (receive autobuffering)

XMThalt

NO

;(transmit buff halt if XMT buff is full)

set

RCVhalt

.set

NO

; (receive buff halt if RCV buff is full)

XMTbufAddr

0x800

; (address of transmit buffer)

.set

;(length of transmit buffer)

0 \times 0 \times 0 = 0

XMTbufSize

.set

RCVbufAddr

0x800

; (address of receive buffer)

.set

RCVbufSize

0x800

;(length of receive buffer)works up to 800

.set

* See notes in the 'C54x CPU and Peripherals Reference Guide on setting up

valid buffer start and length values. Page 9-44

*******************

.eval ((Loopback >> 1)|((Format & 2)<<1)|(BurstMode <<3)|(IntCLK <<4)|(IntSync <<5)) ,SPCval

.eval ((CLKDIV)|(FS_polarity <<5)|(CLK_polarity<<6)|((Format &</pre>

1)<<7) | (Frame_ignore<<8) | (PCM_Mode<<9)), SPCEval

.eval (SPCEval (XMTautobuf <<10) | (XMThalt <<12) | (RCVautobuf <<13) | (RCVhalt <<15)), SPCEval</pre>

sineinit:

bspc = #SPCval

; places buffered serial port in reset

ifr = #10h

; clear interrupt flags

; Enable HPINT, enable BRINTO

imr = #210h

intm = 0

; all unmasked interrupts are enabled.

bspce = #SPCEval

; programs BSPCE and ABU

axr = #XMTbufAddr

; initializes transmit buffer start address

bkx = #XMTbufSize

; initializes transmit buffer size

arr = #RCVbufAddr

; initializes receive buffer start address

; initializes receive buffer size

bkr = #RCVbufSize

bspc = #(SPCval | GO)

; bring buffered serial port out of reset

return

; for transmit and receive because GO=0xCO

```

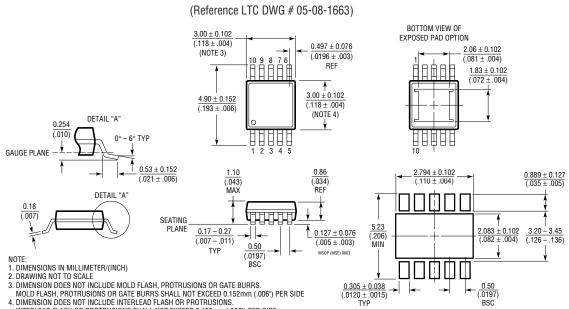

## PACKAGE DESCRIPTION

#### MSE Package 10-Lead Plastic MSOP

RECOMMENDED SOLDER PAD LAYOUT

## **RELATED PARTS**

INTERLEAD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.152mm (.006') PER SIDE 5. LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.102mm (.004') MAX

| PART NUMBER                    | DESCRIPTION                                   | COMMENTS                                                        |  |  |

|--------------------------------|-----------------------------------------------|-----------------------------------------------------------------|--|--|

| ADCs                           |                                               |                                                                 |  |  |

| LTC1608                        | 16-Bit, 500ksps Parallel ADC                  | ±5V Supply, ±2.5V Span, 90dB SINAD                              |  |  |

| LTC1604                        | 16-Bit, 333ksps Parallel ADC                  | ±5V Supply, ±2.5V Span, 90dB SINAD                              |  |  |

| LTC1609                        | 16-Bit, 250ksps Serial ADC                    | 5V, Configurable Bipolar/Unipolar Inputs                        |  |  |

| LTC1411                        | 14-Bit, 2.5Msps Parallel ADC                  | 5V, Selectable Spans, 80dB SINAD                                |  |  |

| LTC1414                        | 14-Bit, 2.2Msps Parallel ADC                  | ±5V Supply, ±2.5V Span, 78dB SINAD                              |  |  |

| LTC1403/LTC1403A               | 12-/14-Bit, 2.8Msps Serial ADC                | 3V, 15mW Unipolar Inputs, MSOP Package                          |  |  |

| LTC1407/LTC1407A               | 12-/14-Bit, 3Msps Simultaneous Sampling ADC   | 3V, 2-Channel Differential, Unipolar Inputs, 14mW, MSOP Package |  |  |

| LTC1407-1/LTC1407A-1           | 12-/14-Bit, 3Msps Simultaneous Sampling ADC   | 3V, 2-Channel Differential, Bipolar Inputs, 14mW, MSOP Package  |  |  |

| LTC1420                        | 12-Bit, 10Msps Parallel ADC                   | 5V, Selectable Spans, 72dB SINAD                                |  |  |

| LTC1405                        | 12-Bit, 5Msps Parallel ADC                    | 5V, Selectable Spans, 115mW                                     |  |  |

| LTC1412                        | 12-Bit, 3Msps Parallel ADC                    | ±5V Supply, ±2.5V Span, 72dB SINAD                              |  |  |

| LTC1402                        | 12-Bit, 2.2Msps Serial ADC                    | 5V or ±5V Supply, 4.096V or ±2.5V Span                          |  |  |

| LTC1864/LTC1865                | 16-Bit, 250ksps Serial ADC                    | 5V Supply, 1 and 2 Channel, 4.3mW, MSOP Package                 |  |  |

| DACs                           |                                               |                                                                 |  |  |

| LTC1666/LTC1667/LTC1668        | 12-/14-/16-Bit, 50Msps DACs                   | 87dB SFDR, 20ns Settling Time                                   |  |  |

| LTC1592                        | 16-Bit, Serial SoftSpan™ I <sub>OUT</sub> DAC | ±1LSB INL/DNL, Software Selectable Spans                        |  |  |

| References                     |                                               |                                                                 |  |  |

| LT1790-2.5                     | Micropower Series Reference in SOT-23         | 0.05% Initial Accuracy, 10ppm Drift                             |  |  |

| LT1461-2.5                     | Precision Voltage Reference                   | 0.04% Initial Accuracy, 3ppm Drift                              |  |  |

| LT1460-2.5                     | Micropower Series Voltage Reference           | 0.1% Initial Accuracy, 10ppm Drift                              |  |  |

| SoftSnan is a trademark of Lin | pear Technology Cornoration                   | 1                                                               |  |  |

SoftSpan is a trademark of Linear Technology Corporation.