|                                                                        |         |   |    |      |           |          |             |            |      |          | R            | EVI      | SIOI                                                                                                     | <b>VS</b> |    |           |          |       |          |               |       |              |      |      |      |   |

|------------------------------------------------------------------------|---------|---|----|------|-----------|----------|-------------|------------|------|----------|--------------|----------|----------------------------------------------------------------------------------------------------------|-----------|----|-----------|----------|-------|----------|---------------|-------|--------------|------|------|------|---|

| LTR                                                                    |         |   | _  |      |           |          |             | DES        | SCRI | PTIO     | N            |          |                                                                                                          |           |    |           |          |       | D/       | TE (Y         | 'R-MC | )-DA)        |      | APPI | ROVE | D |

|                                                                        |         |   |    |      |           |          |             |            |      |          |              |          |                                                                                                          |           |    |           |          |       |          |               |       |              |      |      |      |   |

| REV                                                                    | $\perp$ | _ |    |      |           |          |             |            |      |          |              |          |                                                                                                          |           |    |           |          |       |          |               |       |              |      |      |      |   |

| SHEET                                                                  | 4       | 4 |    | _    | _         |          |             | <u> </u>   |      | L        | $oxed{oxed}$ |          |                                                                                                          |           | L  |           |          |       |          |               |       |              |      |      |      |   |

| REV                                                                    | ┿       | 4 | _  |      | -         | <u> </u> | _           |            | L    | <u> </u> | _            | ļ_       |                                                                                                          |           | ↓_ | _         | <u> </u> | _     | <u> </u> |               |       |              |      |      |      |   |

| SHEET                                                                  |         | ᆛ | _  |      |           | <u> </u> |             |            |      | _        | <u> </u>     | <u> </u> |                                                                                                          | L.,       | ↓_ | <u> </u>  | _        |       |          |               |       |              |      |      |      |   |

| REV STATU                                                              |         | ┝ | RE |      |           | ļ. —     | Ļ           | <u> </u>   |      | Ŀ        | <u> </u>     | _        |                                                                                                          |           | _  | <u> </u>  |          |       |          |               |       |              |      |      | Щ    |   |

| PMIC N/A                                                               | ΔPI     |   |    | EET  | $\exists$ | PRE      | PARE<br>CKE | 3<br>ED BY | 4    | 5        | 6<br>20      | 7<br>04  | 8                                                                                                        | 9         | L_ | DEF       | ENSI     | E ELI | ECTR     | ONIC<br>(, OH | S SI  | UPPL<br>5444 | Y CE | ENTE | R    |   |

| MILITARY DRAWING  THIS DRAWING IS AVAILABLE FOR USE BY ALL DEPARTMENTS |         |   |    |      | APT<br>DH | WING     | APP         | ROV        | AL D |          | 1            |          | MICROCIRCUITS, DIGITAL, BIPOLAR, ADVANCE SCHOTTKY TTL, 2-INPUT NOR GATES, MONOLI SILICON  SIZE CAGE CODE |           |    |           |          | LITH  | 10       |               |       |              |      |      |      |   |

| AND AGENCIES OF THE                                                    |         |   |    | AUGI |           | 198      | 8           |            |      | -        | SHEET 1 OF 9 |          |                                                                                                          |           |    | <b>88</b> | 70<br>—  | 9     |          |               |       |              |      |      |      |   |

DESC FORM 193 SEP 87

$\circ$  U.S. GOVERNMENT PRINTING OFFICE: 1987 — 748-129/60911  $5962\!-\!E984\!-\!2$

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444                                                                                                                                                                                                                              |                                              |          | REVISION LEVEL                                                   |                                       | SHEET 2                                                  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|----------|------------------------------------------------------------------|---------------------------------------|----------------------------------------------------------|--|--|

| MILITARY DRAWING                                                                                                                                                                                                                                                                  | <u> </u>                                     | L        |                                                                  |                                       | 5962-88709                                               |  |  |

| STANDARDIZED                                                                                                                                                                                                                                                                      | SIZE                                         |          |                                                                  |                                       |                                                          |  |  |

| Maximum power dissipation is defined as $V_{CC}$ x $I_{CC},$ and must withstand the added $P_D$ due to short circuit test, eg. $I_{OS}.$                                                                                                                                          |                                              |          |                                                                  |                                       |                                                          |  |  |

| Supply voltage range ( $V_{CC}$ ) Minimum high level input voltage ( $V_{I}$ Maximum low level input voltage ( $V_{IL}$ Input clamp current ( $I_{IC}$ ) High level output current ( $I_{OH}$ ) Low level output current ( $I_{OL}$ ) Case operating temperature range ( $I_{CC}$ | ) · · · · · · · · · · · · · · ·              | <br><br> | - 0.8 V<br>18 mA<br>1.0 mA                                       |                                       | .5 V maximum.                                            |  |  |

| Voltage applied to any output in the Current into any output in the low s Storage temperature range Maximum power dissipation (PD) 1/ - Lead temperature (soldering, 10 secon thermal resistance, junction-to-case Junction temperature (TJ)                                      | state<br><br>onds)<br>e (θ <sub>1C</sub> ) - | <br><br> | - 40 mA<br>65 °C to 4<br>- 71.5 mW<br>- +300 °C<br>- See MIL -M- | ·150°C                                | pendix C                                                 |  |  |

| Supply voltage range Input voltage range Input current range                                                                                                                                                                                                                      |                                              | <br>     | 1.2 V at<br>30 mA to                                             | -18 mA to                             | o +7.0 V dc maximum<br>+7.0 V                            |  |  |

| 1.3 Absolute maximum ratings.                                                                                                                                                                                                                                                     | <b>54.11</b>                                 | , puc    | · uge                                                            |                                       |                                                          |  |  |

| C<br>D<br>2                                                                                                                                                                                                                                                                       | D-1 (14-<br>F-2 (14-<br>C-2 (20-<br>carrie   | - termi  | nal, "358" X "                                                   | x .200"),<br>x .085"),<br>358" x .100 | dual-in-line package<br>flat package<br>O"), square chip |  |  |

| Outline letter                                                                                                                                                                                                                                                                    |                                              |          | Case out                                                         | line                                  |                                                          |  |  |

| 1.2.2 <u>Case outlines</u> . The case outline as follows:                                                                                                                                                                                                                         | s shall be                                   |          |                                                                  | _                                     |                                                          |  |  |

| 01 5 <b>4</b> F36                                                                                                                                                                                                                                                                 | <del></del>                                  |          | Quadruple 2-in                                                   |                                       | tes                                                      |  |  |

| Device type Generic nu                                                                                                                                                                                                                                                            |                                              |          | Circuit functi                                                   |                                       | ollows:                                                  |  |  |

| (1.2.1 <u>Device type</u> . The device type sh                                                                                                                                                                                                                                    | •                                            | 1.2)     | 2) þ                                                             | IIL-M-38510                           | )                                                        |  |  |

| Drawing number Device                                                                                                                                                                                                                                                             | type                                         | Case o   | utline Lea                                                       | id finish p                           | ner                                                      |  |  |

| 5962-88709 01                                                                                                                                                                                                                                                                     | _                                            |          | <u>.                                    </u>                     | <del>X</del>                          |                                                          |  |  |

| 1.2 Part number. The complete part nu                                                                                                                                                                                                                                             | umber shal                                   | 1 be a   | s shown in the                                                   | following                             | g example:                                               |  |  |

| 1.1 Scope. This drawing describes dewith 1.2.1 of MIL-STD-883, "Provisions for non-JAN devices".                                                                                                                                                                                  | or the use                                   | OI M     | 1-210-883 1N (                                                   | conjunction                           | n with compliant                                         |  |  |

|                                                                                                                                                                                                                                                                                   |                                              |          |                                                                  |                                       |                                                          |  |  |

#### 2. APPLICABLE DOCUMENTS

2.1 Government specification and standard. Unless otherwise specified, the following specification and standard, of the issue listed in that issue of the Department of Defense Index of Specifications and Standards specified in the solicitation, form a part of this drawing to the extent specified herein.

**SPECIFICATION**

MILITARY

MIL-M-38510

- Microcircuits, General Specification for.

STANDARD

MILITARY

MIL-STD-883

- Test Methods and Procedures for Microelectronics.

(Copies of the specification and standard required by manufacturers in connection with specific acquisition functions should be obtained from the contracting activity or as directed by the contracting activity.)

- 2.2 Order of precedence. In the event of a conflict between the text of this drawing and the references cited herein, the text of this drawing shall take precedence.

- 3. REQUIREMENTS

- 3.1 Item requirements. The individual item requirements shall be in accordance with 1.2.1 of MIL-STD-883, "Provisions for the use of MIL-STD-883 in conjunction with compliant non-JAN devices" and as specified herein.

- $3.2\,$  Design, construction, and physical dimensions. The design, construction, and physical dimensions shall be as specified in MIL-M-38510 and herein.

- 3.2.1 Terminal connections. The terminal connections shall be as specified on figure 1.

- 3.2.2 Truth table. The truth table shall be as specified on figure 2.

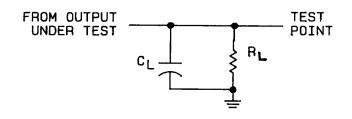

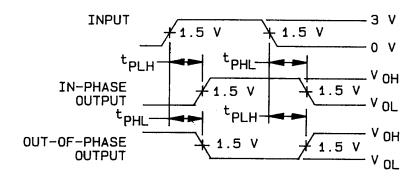

- 3.2.3 Test circuit and switching waveform. The test circuit and switching waveform shall be as specified on figure 3.

- 3.2.4 Case outlines. The case outlines shall be in accordance with 1.2.2 herein.

- 3.3 Electrical performance characteristics. Unless otherwise specified, the electrical performance characteristics are as specified in table I and apply over the full case operating temperature range.

- 3.4 Marking. Marking shall be in accordance with MIL-STD-883 (see 3.1 herein). The part shall be marked with the part number listed in 1.2 herein. In addition, the manufacturer's part number may also be marked as listed in 6.4 herein.

- 3.5 <u>Certificate of compliance</u>. A certificate of compliance shall be required from a manufacturer in order to be listed as an approved source of supply in 6.4. The certificate of compliance submitted to DESC-ECS prior to listing as an approved source of supply shall state that the manufacturer's product meets the requirements of MIL-STD-883 (see 3.1 herein) and the requirements herein.

| STANDARDIZED MILITARY DRAWING                           | SIZE<br><b>A</b> |            |      | 5962-88709 |  |

|---------------------------------------------------------|------------------|------------|------|------------|--|

| DEFENSE ELECTRONICS SUPPLY CENTER<br>DAYTON, OHIO 45444 |                  | REVISION L | EVEL | SHEET 3    |  |

DESC FORM 193A SEP 87

| TAE                                                |                   | Т                                                                                    |                                             | <del></del>               | <del></del> -                                    |      |              |

|----------------------------------------------------|-------------------|--------------------------------------------------------------------------------------|---------------------------------------------|---------------------------|--------------------------------------------------|------|--------------|

| Test                                               | Symbol            | -55°C < Tr                                                                           | ons <u>1</u> /<br>< +125°C<br>Tse specified | <br> Group A<br> subgroup | <br>  Li<br> s <br>  Min                         | Uni  |              |

| High level output voltage                          | V <sub>OH</sub>   | V <sub>CC</sub> = 4.5 V<br>  V <sub>IL</sub> = 0.8 V                                 | $I_{OH} = -1.0 \text{ mA}$                  | 1, 2, 3                   | -                                                | -    | <br> <br>  V |

| Low level output voltage                           | I V <sub>OL</sub> | V <sub>CC</sub> = 4.5 V<br>  V <sub>IL</sub> = 0.8 V<br>  V <sub>IH</sub> = 2.0 V 2/ | OL = 20 mA                                  | 1, 2, 3                   | <del> </del>                                     | 0.5  | <br>  v      |

| Input clamp voltage                                | VIC               | V <sub>CC</sub> = 4.5 V                                                              | IN = -18 mA                                 | 1, 2, 3                   | <del> </del>                                     | -1.2 | ļ<br>Į V     |

| Low level input current                            | IIL               | V <sub>CC</sub> = 5.5 V<br>V <sub>IN</sub> = 0.5 V<br>Unused inputs =                | 4.5 Y                                       | 1, 2, 3                   |                                                  | -0.6 | m,A          |

| High level input current                           | F                 | V <sub>CC</sub> = 5.5 V<br>V <sub>IN</sub> = 2.7 V<br>Unused inputs =                | 0.0 Y                                       | 1, 2, 3                   | <del>                                     </del> | 20   | μА           |

|                                                    | 1                 | V <sub>CC</sub> = 5.5 V<br>V <sub>IN</sub> = 7.0 V<br>Unused inputs = 0              | 0.0 V                                       | 1, 2, 3                   | <br> <br> <br>                                   | 0.1  | mA           |

| Short circuit output current                       | Ios               | V <sub>CC</sub> = 5.5 V<br>V <sub>OUT</sub> = 0.0 V                                  | <u>5</u> /                                  | 1, 2, 3                   | -60                                              | -150 | mA           |

| Supply current                                     | I <sub>CCH</sub>  | V <sub>CC</sub> = 5.5 V<br>V <sub>IN</sub> = 0.0 V (all                              | inputs)                                     | 1, 2, 3                   |                                                  | 5.6  | mΑ           |

|                                                    | ICCL              | V <sub>CC</sub> = 5.5 V<br>One input per gat<br>all others groun                     | e at 4.5 V and<br>ded.                      | 1, 2, 3                   |                                                  | 13   | mA           |

| unctional tests                                    | <br>              | See 4.3.1c <u>6</u> /                                                                |                                             | 7, 8                      |                                                  |      |              |

| ropagation delay time,<br>A or B to Y              | i ii              | $V_{CC} = 4.5 \text{ V to 5.}$ $C_{L} = 50 \text{ pF}$ $C_{L} = 500\Omega$           | 9, 10, 11                                   | 1.7                       | 7.5                                              | ns   |              |

|                                                    | t <sub>PHL</sub>  | See figure 3                                                                         |                                             | 9,10,11                   | 1                                                | 6.5  | ns           |

| ee footnotes on next page.                         |                   |                                                                                      |                                             | ·                         | !                                                |      |              |

| STANDARDIZED<br>MILITARY DRAWIN                    | G                 | SIZE<br>A                                                                            |                                             | 5962                      | 2-88709                                          | )    |              |

| DEFENSE ELECTRONICS SUPPLY (<br>DAYTON, OHIO 45444 | CENTER            |                                                                                      | REVISION LEVEL                              | s                         | HEET                                             |      |              |

DESC FORM 193A SEP 87

- 1/ Unused inputs that do not directly control the pin under test must be  $\geq 2.5$  V or  $\leq 0.5$  V, and shall not exceed 5.5 V or go less than 0.0 V. No inputs shall be floated.

- $^{2/}$  All outputs must be tested. In the case where only one input at V<sub>IL</sub> maximum or V<sub>IH</sub> minimum produces the proper output state, the test must be performed with each input being selected as the V<sub>IL</sub> maximum or V<sub>IH</sub> minimum input.

- 3/ One input to gate under test = 0.8 V, other inputs < 0.8 V.

- 4/ One input to gate under test = 2.0 V, other inputs < 0.8 V.

- 5/ Not more than one output shall be shorted at one time and the duration of the test condition shall not exceed one second.

- 6/ Functional tests shall be conducted at input test conditions of GND  $\leq$  V<sub>IL</sub>  $\leq$  V<sub>OL</sub> and V<sub>OH</sub>  $\leq$  V<sub>IH</sub>  $\leq$  V<sub>CC</sub>.

- 7/ Propagation delay limits are based on single output switching. Unused inputs = 0.0 V or 3.0 V.

- 3.6 Certificate of conformance. A certificate of conformance as required in MIL-STD-883 (see 3.1 herein) shall be provided with each lot of microcircuits delivered to this drawing.

- 3.7 Notification of change. Notification of change to DESC-ECS shall be required in accordance with MIL-STD-883 (see 3.1 herein).

- 3.8 Verification and review. DESC, DESC's agent, and the acquiring activity retain the option to review the manufacturer's facility and applicable required documentation. Offshore documentation shall be made available onshore at the option of the reviewer.

- 4. QUALITY ASSURANCE PROVISIONS

- 4.1 Sampling and inspection. Sampling and inspection procedures shall be in accordance with section 4 of MIL-M-38510 to the extent specified in MIL-STD-883 (see 3.1 herein).

- 4.2 <u>Screening.</u> Screening shall be in accordance with method 5004 of MIL-STD-883, and shall be conducted on all devices prior to quality conformance inspection. The following additional criteria shall apply:

- a. Burn-in test, method 1015 of MIL-STD-883.

- Test condition A or D using the circuit submitted with the certificate of compliance (see 3.5 herein).

- (2)  $T_A = +125$ °C, minimum.

- b. Interim and final electrical test parameters shall be as specified in table II herein, except interim electrical parameter tests prior to burn-in are optional at the discretion of the manufacturer.

- 4.3 Quality conformance inspection. Quality conformance inspection shall be in accordance with method 5005 of MIL-STD-883 including groups A, B, C, and D inspections. The following additional criteria shall apply.

- 4.3.1 Group A inspection.

- a. Tests shall be as specified in table II herein.

- b. Subgroups 4, 5, and 6 in table I, method 5005 of MIL-STD-883 shall be omitted.

- c. Subgroups 7 and 8 tests shall verify the truth table as specified on figure 2 herein.

| STANDARDIZED MILITARY DRAWING                        | SIZE<br>A |                | 5962-88709 |  |  |

|------------------------------------------------------|-----------|----------------|------------|--|--|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL | SHEET 5    |  |  |

| Case outlines                                                           | C and D                                     | 2                                                                                     |  |  |  |  |

|-------------------------------------------------------------------------|---------------------------------------------|---------------------------------------------------------------------------------------|--|--|--|--|

| Terminal<br>  number                                                    | Terminal<br>  symbol                        |                                                                                       |  |  |  |  |

| 1 1 2 3 4 4 5 5 1 6 6 7 7 8 9 1 10 11 11 12 13 14 15 16 17 18 19 1 20 1 | 1A 1B 1Y 2A 2B 2Y GND 3Y 3A 3B 4Y 4A 4B VCC | NC   1A   1B   1Y   1   NC   NC |  |  |  |  |

NC = No connection

FIGURE 1. Terminal connections.

| T | Inp         | uts             | <br>  Output |

|---|-------------|-----------------|--------------|

| i | A           | <b>B</b>        | Y            |

| T | H<br>X<br>L | X  <br>H  <br>L | L<br>L<br>H  |

H = High level voltage

L = Low level voltage

X = Irrelevant

FIGURE 2. Truth table.

**STANDARDIZED** SIZE Α 5962-88709 **MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER** REVISION LEVEL SHEET DAYTON, OHIO 45444 6

DESC FORM 193A SEP 87

☆ U.S. GOVERNMENT PRINTING OFFICE: 1987-549-096

## PROPAGATION DELAY TIMES

## NOTES:

- 1. CL includes probe and jig capacitance.

- 2. All input pulses have the following characteristics: PRR  $\leq$  10 MHz,  $t_r$  =  $t_f$  = 2.5 ns, duty cycle = 50%.

- 3. The outputs are measured one at a time with one transition per measurement.

- 4.  $C_L = 50 \text{ pF}$ ,  $R_L = 500 \Omega$ .

FIGURE 3. Test circuit and switching waveforms.

# STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 SIZE A 5962-88709 REVISION LEVEL SHEET 7

DESC FORM 193A SEP 87

☆ U.S. GOVERNMENT PRINTING OFFICE: 1987--549-096

# TABLE II. Electrical test requirements.

| MIL-STD-883 test requirements                                      | Subgroups<br>(per method<br>5005, table I) |

|--------------------------------------------------------------------|--------------------------------------------|

| Interim electrical parameters<br>  (method 5004)                   |                                            |

| Final electrical test parameters (method 5004)                     | 1*,2,3,7,8,9,<br>10,11                     |

| Group A test requirements (method 5005)                            | 1,2,3,7,8,9,<br>10,11                      |

| Groups C and D end-point<br>electrical parameters<br>(method 5005) | 1,2,3                                      |

<sup>\*</sup> PDA applies to subgroup 1.

## 4.3.2 Groups C and D inspections.

- a. End-point electrical parameters shall be as specified in table II herein.

- b. Steady-state life test conditions, method 1005 of MIL-STD-883.

- (1) Test condition A or D using the circuit submitted with the certificate of compliance (see  $3.5\ \text{herein}$ ).

- (2)  $T_A = +125$ °C, minimum.

- (3) Test duration: 1,000 hours, except as permitted by method 1005 of MIL-STD-883.

### 5. PACKAGING

$5.1\,$  Packaging requirements. The requirements for packaging shall be in accordance with MIL-M-38510.

## 6. NOTES

- 6.1 Intended use. Microcircuits conforming to this drawing are intended for use when military specifications do not exist and qualified military devices that will perform the required function are not available for OEM application. When a military specification exists and the product covered by this drawing has been qualified for listing on QPL-38510, the device specified herein will be inactivated and will not be used for new design. The QPL-38510 product shall be the preferred item for all applications.

- 6.2 Replaceability. Microcircuits covered by this drawing will replace the same generic device covered by a contractor-prepared specification or drawing.

- 6.3 Comments. Comments on this drawing should be directed to DESC-ECS, Dayton, Ohio 45444, or telephone 513-296-5375.

STANDARDIZED

MILITARY DRAWING

DEFENSE ELECTRONICS SUPPLY CENTER

DAYTON, OHIO 45444

SIZE

A

5962-88709

REVISION LEVEL

SHEET

8

DESC FORM 193A

SEP 87

6.4 Approved source of supply. An approved source of supply is listed herein. Additional sources will be added as they become available. The vendor listed herein has agreed to this drawing and a certificate of compliance (see 3.5 herein) has been submitted to DESC-ECS.

| Military drawing<br>part number | Vendor<br>  CAGE<br>  number | Vendor<br>similar part<br>number <u>1</u> / |

|---------------------------------|------------------------------|---------------------------------------------|

| 5962-8870901CX                  | 01295                        | SNJ 54F36J                                  |

| 5962-3870901DX                  | 01295                        | SNJ54F36W                                   |

| 5962-88709012X                  | 01295                        | SNJ 54F36FK                                 |

1/ Caution. So not use this number for item acquisition. Items acquired to this number may not satisfy the performance requirements of this drawing.

Vendor CAGE number

01295

Vendor name and address

Texas Instruments, Incorporated P.O. Box 6448 Midland, TX 79711

STANDARDIZED

MILITARY DRAWING

DEFENSE ELECTRONICS SUPPLY CENTER

DAYTON, OHIO 45444

SIZE A

5962-88709

REVISION LEVEL

SHEET

9