|                                                               |        |       |    |              |                 |          |        | RJ | EVISI       | IONS     |                      |       |      |          |        |             |      |      |      |    |

|---------------------------------------------------------------|--------|-------|----|--------------|-----------------|----------|--------|----|-------------|----------|----------------------|-------|------|----------|--------|-------------|------|------|------|----|

| LTR                                                           |        |       |    |              | D               | ESCR     | IPTI(  | ON |             |          |                      |       | L    | ATE      | (YR-MC | DA)         |      | APPR | OVED |    |

|                                                               |        |       |    |              |                 |          |        |    |             |          |                      |       |      |          |        |             |      |      |      |    |

| REV                                                           |        |       |    |              |                 |          |        |    |             | <u> </u> |                      |       |      | <u> </u> | [      |             |      |      |      |    |

| SHEET                                                         |        |       |    |              |                 |          |        |    | i           |          |                      |       |      |          |        |             |      |      |      |    |

| REV                                                           |        |       |    |              |                 |          |        |    | <u> </u>    |          |                      |       |      |          |        |             |      |      |      |    |

| SHEET                                                         | 15     | 16    | 17 | 18           | 19              | 20       | 21     | 22 |             |          |                      |       |      |          |        |             |      |      |      |    |

| REV STATE                                                     |        |       |    | RE           | ٧               |          |        |    |             | <u> </u> |                      |       |      |          |        |             |      |      |      |    |

| OF SHEETS                                                     |        |       |    | SH           | EET             |          | î      | 2  | 3           | 4        | 5                    | 6     | 7    | 8        | 9      | 10          | 11   | 12   | 13   | 14 |

| PMIC N/A                                                      | _      |       | -  |              | ARED E<br>L. Gr |          |        |    |             | ומ       | efen:                | SE EL |      |          |        | PPLY<br>454 |      | rer  |      |    |

| STA<br>MICRO                                                  | CIRC   | UIT   |    | CHEC<br>Jeff | KED BY<br>Bowli | í<br>ing |        |    |             |          |                      |       |      |          |        |             |      |      |      |    |

| DRAWING  THIS DRAWING IS AVAILABLE FOR USE BY ALL DEPARTMENTS |        | BLE   |    | OVED E       | 3Y<br>Johns     | son      |        |    | ELI         | ECTR     | IRCU<br>ICAI<br>IOMI | LLY   | ERA  | SABI     | EP     | ROGE        | MMAS | ABLE | :    |    |

| AND AGEN<br>DEPARTMEN                                         | CIES O | F THE |    | DRAW<br>95-0 |                 | PROVA    | L DATE |    |             |          |                      |       |      |          |        |             | ••   |      |      |    |

| AMSC N/A                                                      |        |       |    | REVI         | SION L          | .EVEL    |        |    | <del></del> | SIZ<br>A | E                    | I     | E CO |          |        | 59          | 62-  | 9552 | 25   |    |

|                                                               |        |       |    |              |                 |          |        |    |             | SHI      | EET                  | 1     |      |          | OF     | 2           | 2    |      |      |    |

DESC FORM 193

JUL 94

<u>DISTRIBUTION STATEMENT A</u>. Approved for public release; distribution is unlimited.

5962-E040-95

#### 1. SCOPE

- 1.1 <u>Scope</u>. This drawing forms a part of a one part one part number documentation system (see 6.6 herein). Two product assurance classes consisting of military high reliability (device classes Q and M) and space application (device class V), and a choice of case outlines and lead finishes are available and are reflected in the Part or Identifying Number (PIN). Device class M microcircuits represent non-JAN class B microcircuits in accordance with 1.2.1 of MIL-STD-883, "Provisions for the use of MIL-STD-883 in conjunction with compliant non-JAN devices". When available, a choice of Radiation Hardness Assurance (RHA) levels are reflected in the PIN.

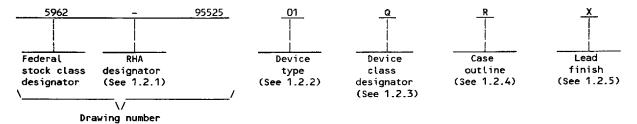

- 1.2 PIN. The PIN shall be as shown in the following example:

- 1.2.1 <u>RHA designator</u>. Device class M RHA marked devices shall meet the MIL-I-38535 appendix A specified RHA levels and shall be marked with the appropriate RHA designator. Device classes Q and V RHA marked devices shall meet the MIL-I-38535 specified RHA levels and shall be marked with the appropriate RHA designator. A dash (-) indicates a non-RHA device.

- 1.2.2 Device type(s). The device type(s) shall identify the circuit function as follows:

|             |                   |                         | Potentio | meter Or | Endurance (writes |       |               |

|-------------|-------------------|-------------------------|----------|----------|-------------------|-------|---------------|

| Device type | Generic number 1/ | <u>Circuit function</u> | Pot 0    | Pot 1    | Pot 2             | Pot 3 | per register) |

| 01          | 9241Y             | Quad EEPOT              | 2.0K     | 2.0K     | 2.0K              | 2.0K  | 100,000 .     |

| 02          | 9241W             | Quad EEPOT              | 10K      | 10K      | 10K               | 10K   | 100,000       |

| 03          | 92 <b>4</b> 1U    | Quad EEPOT              | 50K      | 50K      | 50K               | 50K   | 100,000       |

| 04          | 9241M             | Quad EEPOT              | 2.0K     | 10K      | 10K               | 50K   | 100,000       |

1.2.3 <u>Device class designator</u>. The device class designator shall be a single letter identifying the product assurance level as follows:

Device class

### Device requirements documentation

M

Vendor self-certification to the requirements for non-JAN class B microcircuits in accordance with 1.2.1 of MIL-STD-883

Q or V

Certification and qualification to MIL-I-38535

1.2.4 <u>Case outline(s)</u>. The case outline(s) shall be as designated in MIL-STD-1835 and as follows:

| Outline letter | Descriptive designator | <u>Terminals</u> | Package style |

|----------------|------------------------|------------------|---------------|

| R              | GD IP1-T20             | 20               | Dual-in-line  |

1.2.5 <u>Lead finish</u>. The lead finish shall be as specified in MIL-STD-883 (see 3.1 herein) for class M or MIL-I-38535 for classes Q and V. finish letter "X" shall not be marked on the microcircuit or its packaging. The "X" designation is for use in specifications when lead finishes A, B, and C are considered acceptable and interchangeable without preference.

1/ Generic numbers are also listed in the Standard Microcircuit Drawing Source Approval Bulletin and in MIL-BUL-103.

| STANDARD MICROCIRCUIT DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                | 5962-95525 |

|-----------------------------------------------------------------|-----------|----------------|------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL | SHEET 2    |

DESC FORM 193A JUL 94

🖿 9004708 0009765 OST 🖿

| 1.3 Absolute maximum ratings. 2/                                                                                                                                                                                                                                                                   |                                     |                            |                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|----------------------------|------------------|

| Supply voltage range with respect to ground ( $V_{CC}$ ). Voltage on SCL, SDA, or AO – A3 with respect to ground Voltage on any $V_H$ or $V_L$ pin referenced to ground . Diferential voltage ( $\Delta V = V_H - V_L$ ) Storage temperature range ( $T_{stg}$ )                                   | Line R)                             | ±8.0 V dc                  | r, minimum       |

| 1.4 Recommended operating conditions.                                                                                                                                                                                                                                                              |                                     |                            |                  |

| Supply voltage range $(V_{CC})$ Case operating temperature range $(T_C)$ Low level input voltage range $(V_{IL})$ High level input voltage range $(V_{IH})$                                                                                                                                        |                                     | -1,0 1 46 60 10.0 1 40     | lc               |

| 1.5 <u>Digital logic testing for device classes Q and V</u> .                                                                                                                                                                                                                                      |                                     |                            |                  |

| Fault coverage measurement of manufacturing<br>logic tests (MIL-STD-883, test method 5012)                                                                                                                                                                                                         |                                     | XX percent 4/              |                  |

| 2. APPLICABLE DOCUMENTS                                                                                                                                                                                                                                                                            |                                     |                            |                  |

| 2.1 <u>Government specification, standards, bulletin, and handbook of the issof Specifications and Standards specified in the solicitations.</u>                                                                                                                                                   | sue listed in the                   | at issue of the Department | Of Defense Index |

| SPECIFICATION                                                                                                                                                                                                                                                                                      |                                     |                            |                  |

| MILITARY                                                                                                                                                                                                                                                                                           |                                     |                            |                  |

| MIL-I-38535 - Integrated Circuits, Manufacturing,                                                                                                                                                                                                                                                  | General Specifi                     | cation for.                |                  |

| STANDARDS                                                                                                                                                                                                                                                                                          |                                     |                            |                  |

| MILITARY                                                                                                                                                                                                                                                                                           |                                     |                            |                  |

| MIL-STD-883 - Test Methods and Procedures for Mic<br>MIL-STD-973 - Configuration Management.<br>MIL-STD-1835 - Microcircuit Case Outlines.                                                                                                                                                         | rcelectronics.                      |                            |                  |

| BULLETIN                                                                                                                                                                                                                                                                                           |                                     |                            |                  |

| MILITARY                                                                                                                                                                                                                                                                                           |                                     |                            |                  |

| MIL-BUL-103 - List of Standard Microcircuit Drawi                                                                                                                                                                                                                                                  | ngs (SMD's).                        |                            |                  |

| 2/ Stresses above the absolute maximum rating may cause possinum levels may degrade performance and affect relia 3/ Maximum junction temperature shall not be exceeded exceeded conditions in accordance with method 5004 of MIL-STD-84 4/ When a Qualified Manufacturers' List (QML) source exist | ability.<br>ept for allowabl<br>83. | e short duration burn-in s |                  |

| STANDARD MICROCIRCUIT DRAWING DEFENSE ELECTRONICS SUPPLY CENTER                                                                                                                                                                                                                                    | SIZE                                |                            | 5962-95525       |

|                                                                                                                                                                                                                                                                                                    | A                                   |                            |                  |

📟 9004708 0009766 T96 📟

#### HANDBOOK

#### MILITARY

MIL-HDBK-780 - Standardized Military Drawings.

(Copies of the specification, standards, bulletin, and handbook required by manufacturers in connection with specific acquisition functions should be obtained from the contracting activity or as directed by the contracting activity.)

2.2 <u>Non-Government publications</u>. The following documents form a part of this document to the extent specified herein. Unless otherwise specified, the issues of the documents which are DoD adopted are those listed in the issue of the DODISS cited in the solicitation. Unless otherwise specified, the issues of documents not listed in the DODISS are the issues of the documents cited in the solicitation.

#### ELECTRONICS INDUSTRIES ASSOCIATION (EIA)

JEDEC Standard No. 17 - A Standardized Test Procedure for the Characterization of LATCH-UP in CMOS Integrated Circuits.

(Applications for copies should be addressed to the Electronic Industries Association, 2001 Pennsylvania Avenue, N.W., Washington, DC 20006.)

AMERICAN SOCIETY FOR TESTING AND MATERIALS (ASTM)

ASTM Standard F1192-88 - Standard Guide for the Measurement of Single Event Phenomena from Heavy Ion Irradiation of Semicondustor Devices.

(Applications for copies of ASTM publications should be addressed to the American Society for Testing and Materials, 1916 Race Street, Philadelphia, Pennsylvania 19103).

(Non-Government standards and other publications are normally available from the organizations that prepare or distribute the documents. These documents also may be available in or through libraries or other informational services.)

2.3 <u>Order of precedence</u>. In the event of a conflict between the text of this drawing and the references cited herein, the text of this drawing shall take precedence.

# 3. REQUIREMENTS

- 3.1 <u>Item requirements</u>. The individual item requirements for device class M shall be in accordance with 1.2.1 of MIL-STD-883, "Provisions for the use of MIL-STD-883 in conjunction with compliant non-JAN devices" and as specified herein. The individual item requirements for device classes Q and V shall be in accordance with MIL-I-38535, the device manufacturer's Quality Management (QM) plan, and as specified herein.

- 3.2 <u>Design, construction, and physical dimensions</u>. The design, construction, and physical dimensions shall be as specified in MIL-STD-883 (see 3.1 herein) for device class N and MIL-I-38535 for device classes Q and V and herein.

- 3.2.1 <u>Case outline</u>. The case outline shall be in accordance with 1.2.4 herein.

- 3.2.2 <u>Terminal connections</u>. The terminal connections shall be as specified on figure 1.

- 3.2.3 <u>Truth table</u>. The truth table shall be as specified on figure 2.

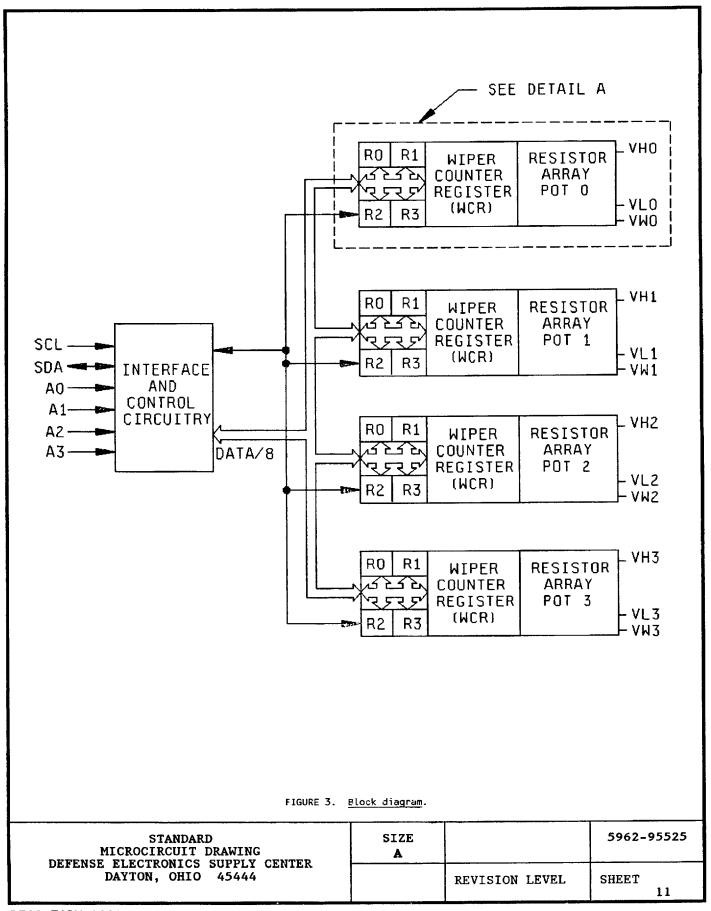

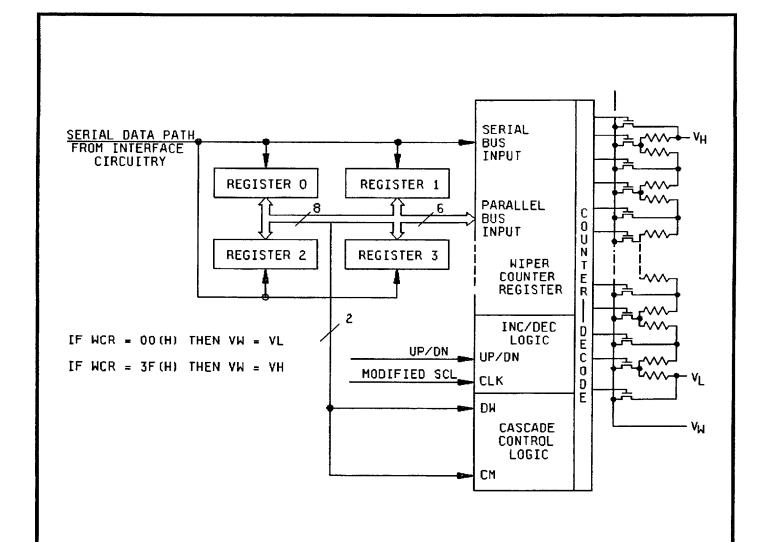

- 3.2.4 Block diagram. The block diagram shall be as specified on figure 3.

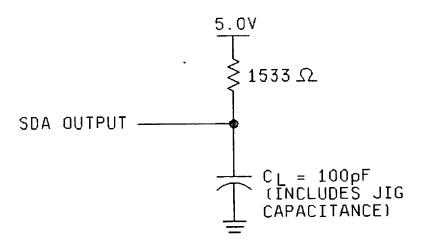

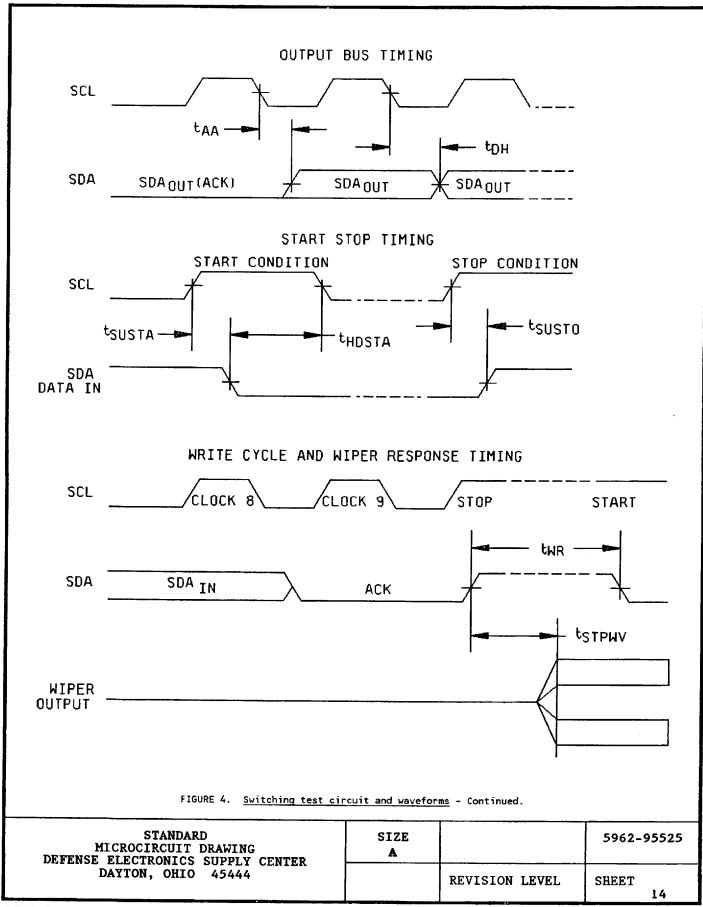

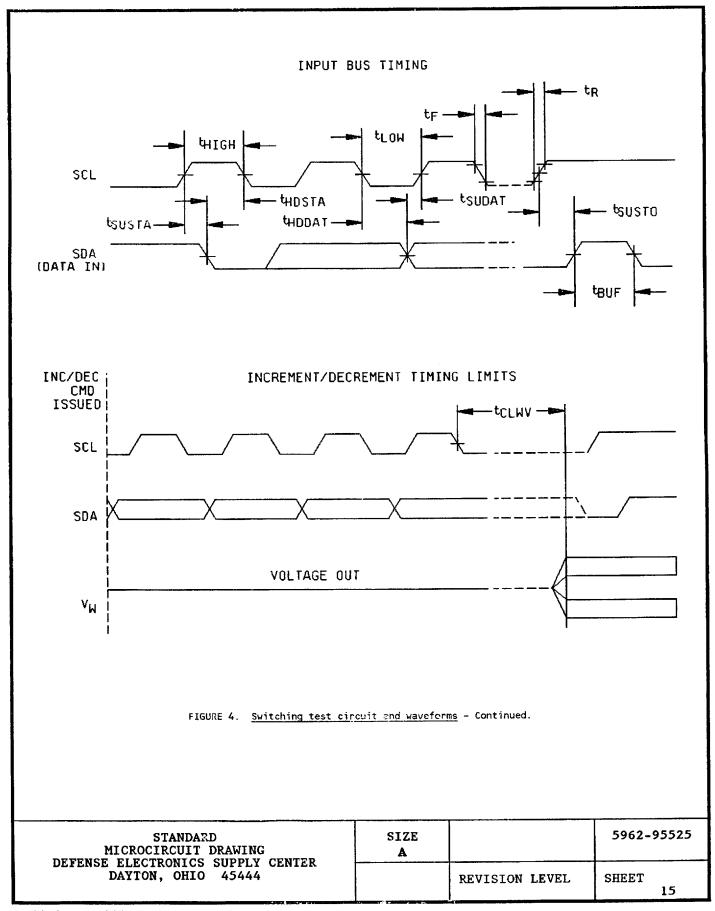

- 3.2.5 <u>Switching test circuits and waveforms</u>. The switching test circuits and waveforms shall be as specified on figure 4.

- 3.2.5.1 <u>Unprogrammed devices</u>. The truth table for unprogrammed devices for contracts involving no altered item drawing shall be as specified on figure 2 herein. When required, in screening (see 4.2 herein), or quality conformance inspection groups A, B, C, or D (see 4.4 herein), the devices shall be programmed by the manufacturer prior to test in a checkerboard or similar pattern (a minimum of 50 percent of the total number of bits programmed).

| STANDARD MICROCIRCUIT DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                | 5962-95525 |

|-----------------------------------------------------------------|-----------|----------------|------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL | SHEET 4    |

DESC FORM 193A JUL 94

9004708 0009767 922

- 3.2.5.2 Programmed devices. The requirements for supplying programmed devices are not part of this document.

- 3.3 <u>Electrical performance characteristics and postirradiation parameter limits</u>. Unless otherwise specified herein, the electrical performance characteristics and postirradiation parameter limits are as specified in table I and shall apply over the full case operating temperature range.

- 3.4 <u>Electrical test requirements</u>. The electrical test requirements shall be the subgroups specified in table IIA. The electrical tests for each subgroup are defined in table I.

- 3.5 Marking. The part shall be marked with the PIN listed in 1.2 herein. Marking for device class M shall be in accordance with MIL-STD-883 (see 3.1 herein). In addition, the manufacturer's PIN may also be marked as listed in MIL-BUL-103. Marking for device classes Q and V shall be in accordance with MIL-I-38535.

- 3.5.1 <u>Certification/compliance mark</u>. The compliance mark for device class M shall be a "C" as required in MIL-STD-883 (see 3.1 herein). The certification mark for device classes Q and V shall be a "QML" or "Q" as required in MIL-I-38535.

- 3.6 <u>Certificate of compliance</u>. For device class M, a certificate of compliance shall be required from a manufacturer in order to be listed as an approved source of supply in MIL-BUL-103 (see 6.7.2 herein). For device classes Q and V, a certificate of compliance shall be required from a QML-38535 listed manufacturer in order to supply to the requirements of this drawing (see 6.7.1 herein). The certificate of compliance submitted to DESC-EC prior to listing as an approved source of supply for this drawing shall affirm that the manufacturer's product meets, for device class M the requirements of MIL-STD-883 (see 3.1 herein), or for device classes Q and V, the requirements of MIL-I-38535 and the requirements herein.

- 3.7 <u>Certificate of conformance</u>. A certificate of conformance as required for device class M in MIL-STD-883 (see 3.1 herein) or for device classes Q and V in MIL-I-38535 shall be provided with each lot of microcircuits delivered to this drawing.

- 3.8 <u>Notification of change for device class M</u>. For device class M, notification to DESC-EC of change of product (see 6.2 herein) involving devices acquired to this drawing is required for any change as defined in MIL-STD-973.

- 3.9 <u>Verification and review for device class M</u>. For device class M, DESC, DESC's agent, and the acquiring activity retain the option to review the manufacturer's facility and applicable required documentation. Offshore documentation shall be made available onshore at the option of the reviewer.

- 3.10 <u>Microcircuit group assignment for device class M</u>. Device class M devices covered by this drawing shall be in microcircuit group number 42 (see MIL-1-38535, appendix A).

- 3.11 <u>Processing of EEPOTs</u>. All testing requirements and quality assurance provisions herein shall be satisfied by the manufacturer prior to delivery.

- 3.11.1 <u>Conditions of the supplied devices</u>. Devices will be supplied in an unprogrammed or clear state. No provision will be made for supplying programmed devices.

- 3.11.2 <u>Erasure of EEPOTs</u>. When specified, devices shall be erased in accordance with procedures and characteristics specified in 4.5.1.

- 3.11.3 <u>Programming of EEPOTs</u>. When specified, devices shall be programmed in accordance with procedures and characteristics specified in 4.5.2.

- 3.11.4 <u>Verification of state of EEPROMs</u>. When specified, devices shall be verified as either written to the specified pattern or cleared. As a minimum, verification shall consist of performing a read of the entire memory array to verify that all bits are in the proper state. Any bit that does not verify to be in the proper state shall constitute a device failure and the device shall be removed from the lot or sample.

| STANDARD<br>MICROCIRCUIT DRAWING                     | SIZE<br>A |                | 5962-95525 |

|------------------------------------------------------|-----------|----------------|------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL | SHEET<br>5 |

9004708 0009768 869

TABLE I. <u>Electrical performance characteristics</u>.

| Test                                                   | Symbol            | Conditions $-55^{\circ}C \leq T_{C} \leq +125^{\circ}C$                                          | Group A<br>subgroups | Device<br>type | Lir             | imits                | Unit             |

|--------------------------------------------------------|-------------------|--------------------------------------------------------------------------------------------------|----------------------|----------------|-----------------|----------------------|------------------|

|                                                        |                   | -55°C ≤ T <sub>C</sub> ≤ +125°C<br>4.5 V ≤ V <sub>CC</sub> ≤ 5.5 V<br>unless otherwise specified |                      |                | Min             | Max                  |                  |

| V <sub>CC</sub> supply current, active                 | Icc               | f <sub>SCL</sub> = 100 KHz, SDA = open,<br>all other inputs = GND                                | 1, 2, 3              | All            |                 | 3.0                  | mA               |

| V <sub>CC</sub> supply current,<br>standby             | ISB               | SCL = SDA = V <sub>CC</sub> , AO - A3 = GND                                                      | 1, 2, 3              | ALL            |                 | 500                  | μA               |

| Input leakage<br>current                               | ILI               | V <sub>IN</sub> = GND to V <sub>CC</sub>                                                         | 1, 2, 3              | ALL            |                 | 10                   | μА               |

| Output leakage<br>current                              | I <sub>LO</sub>   | V <sub>OUT</sub> = GND to V <sub>CC</sub>                                                        | 1, 2, 3              | ALL            |                 | 10                   | μА               |

| High level input<br>voltage                            | v <sub>IH</sub>   |                                                                                                  | 1, 2, 3              | ALL            | 2.0             | ν <sub>ς</sub> ς+1.0 | V                |

| Low level input<br>voltage                             | V <sub>IL</sub>   |                                                                                                  | 1, 2, 3              | ALL            | -1.0 <u>1</u> / | 0.8                  | V                |

| Low level output<br>voltage                            | V <sub>OL</sub>   | I <sub>OL</sub> = 3.0 mA                                                                         | 1, 2, 3              | ALL            |                 | 0.4                  | ٧                |

| Input/output<br>capacitance (SDA)                      | C1/0              | V <sub>I/O</sub> = 0 V, T <sub>A</sub> = +25°C,<br>see 4.4.1b                                    | 4                    | All            |                 | 8.0                  | pF               |

| Input capacitance                                      | CIN               | V <sub>IN</sub> = 0 V, T <sub>A</sub> = +25°C,<br>see 4.4.1b                                     | 4                    | ALL            |                 | 6.0                  | pF               |

| End to end<br>resistance<br>tolerance                  | R <sub>E-E</sub>  |                                                                                                  | 4, 5, 6              | ALL            | -20             | +20                  | 1%               |

| Power rating, each potentiometer <u>2</u> /            | PIN               | T <sub>A</sub> = +25°C                                                                           | 4                    | ALL            |                 | 50                   | m₩               |

| Wiper current                                          | Iw                |                                                                                                  | 4, 5, 6              | All            | -1.0            | +1.0                 | mA               |

| Wiper resistance                                       | R <sub>W</sub>    | I <sub>W</sub> = ±1.0 mA                                                                         | 4, 5, 6              | All            |                 | 100                  | Ω                |

| Voltage on any V <sub>H</sub><br>or V <sub>L</sub> pin | V <sub>TERM</sub> |                                                                                                  | 4, 5, 6              | ALL            | -5.0            | +5.0                 | V                |

| Noise figure <u>3</u> /                                | NF                | V <sub>REF</sub> = 1.0 V                                                                         | 4, 5, 6              | ALL            |                 | ≤120                 | dB/<br>√Hz       |

| Resolution 1/                                          | RES               | Individual array resolution                                                                      | 4, 5, 6              | All            |                 | 1.6                  | %                |

|                                                        |                   | All four arrays cascaded together                                                                |                      |                |                 | 0.4                  |                  |

| Absolute linearity,<br>each potentiometer<br>4/        | AL                | VW(n)(actual) -<br>VW(n)(expected)                                                               | 4, 5, 6              | All            | -1.0            | +1.0                 | MI<br><u>5</u> / |

| Relative linearity, each potentiometer 6/              | RL                | VW(n + 1) - [VW(n) + MI] 5/                                                                      | 4, 5, 6              | All            | -0.2            | +0.2                 | MI<br><u>5</u> / |

See footnotes at end of table.

| STANDARD MICROCIRCUIT DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 | SIZE<br>A |                | 5962-95525 |

|------------------------------------------------------------------------------------|-----------|----------------|------------|

| DAYTON, OHIO 45444                                                                 |           | REVISION LEVEL | SHEET<br>6 |

DESC FORM 193A JUL 94

# ■ 9004708 0009769 7T5 ■

$\label{eq:table I.} \textbf{Electrical performance characteristics} \ \textbf{--} \ \textbf{continued}.$

| Test                                                                 | Symbol             | Conditions<br>-55°C < T < +125°C                                                 | Group A<br>subgroups | Device<br>type | Limits |      | Units      |

|----------------------------------------------------------------------|--------------------|----------------------------------------------------------------------------------|----------------------|----------------|--------|------|------------|

|                                                                      |                    | -55°C ≤ $T_C$ ≤ +125°C<br>4.5 V ≤ $V_{CC}$ ≤ 5.5 V<br>unless otherwise specified | Subgi Sups           |                | Min    | Max  |            |

| Temperature coefficient of resistance 3/                             | TC <sub>R</sub>    |                                                                                  | 4, 5, 6              | ALL            |        | ±300 | °C<br>ppm/ |

| Functional tests                                                     |                    | see 4.4.1c                                                                       | 7, 8A, 8B            | ALL            |        |      | <u> </u>   |

| Power-up to initiation of read operation 3/7/                        | <sup>t</sup> PUR   | C <sub>L</sub> = 100 pF, see figure 4                                            | 9, 10, 11            | All            |        | 1.0  | ms         |

| Power-up to initiation of write operation 3/7/                       | <sup>t</sup> PUW   |                                                                                  | 9, 10, 11            | All            |        | 5.0  | ms         |

| SCL clock frequency                                                  | f <sub>SCL</sub>   |                                                                                  | 9, 10, 11            | ALL            | 0 1/   | 100  | KHz        |

| Noise suppression time constant (glitch filter) 1/                   | <sup>t</sup> nstc  | C <sub>L</sub> = 100 pF, see figure 4                                            | 9, 10, 11            | ALL            |        | 100  | ns         |

| Clock low period                                                     | t <sub>LOW</sub>   |                                                                                  | 9, 10, 11            | ALL            | 4700   |      | ns         |

| Clock high period                                                    | <sup>t</sup> HIGH  |                                                                                  | 9, 10, 11            | ALL            | 4000   |      | ns         |

| SCL and SDA rise<br>time <u>1</u> /                                  | t <sub>R</sub>     |                                                                                  | 9, 10, 11            | All            |        | 1000 | ns         |

| SCL and SDA fall time <u>1</u> /                                     | t <sub>F</sub>     |                                                                                  | 9, 10, 11            | ALL            |        | 300  | ns         |

| Start condition<br>setup time (for a<br>repeated start<br>condition) | <sup>t</sup> susta |                                                                                  | 9, 10, 11            | All            | 4700   |      | ns         |

| Start condition hold time                                            | t <sub>HDSTA</sub> |                                                                                  | 9, 10, 11            | All            | 4000   |      | ns         |

| Data in setup time                                                   | <sup>t</sup> SUDAT |                                                                                  | 9, 10, 11            | ALL            | 250    |      | ns         |

| Data in hold time                                                    | t <sub>HDDAT</sub> |                                                                                  | 9, 10, 11            | ALL            | 0      |      | ns         |

| SCL low to SDA data out valid 1/                                     | t <sub>AA</sub>    |                                                                                  | 9, 10, 11            | ALL            | 300    | 3500 | ns         |

| Data out hold time                                                   | t <sub>DH</sub>    | ]                                                                                | 9, 10, 11            | ALL            | 300    |      | ns         |

| Stop condition setup time                                            | <sup>t</sup> susto |                                                                                  | 9, 10, 11            | All            | 4700   |      | ns         |

| Bus free time prior to new transmission 1/                           | t <sub>BUF</sub>   |                                                                                  | 9, 10, 11            | All            | 4700   |      | ns         |

| Write cycle time<br>(nonvolatile write<br>operation)                 | <sup>t</sup> WR    |                                                                                  | 9, 10, 11            | All            |        | 10   | ms         |

See footnotes at end of table.

| STANDARD<br>MICROCIRCUIT DRAWING                     | SIZE<br>A |                | 5962-95525 |

|------------------------------------------------------|-----------|----------------|------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL | SHEET<br>7 |

DESC FORM 193A JUL 94

**■** 9004708 0009770 417 **■**

### TABLE I. <u>Electrical performance characteristics</u> - continued.

| Test                                           | Symbol             | Conditions<br>-55°C ≤ T <sub>C</sub> ≤ +125°C                                                                        | Group A<br>subgroups | Device<br>type | Limits |     | Units |

|------------------------------------------------|--------------------|----------------------------------------------------------------------------------------------------------------------|----------------------|----------------|--------|-----|-------|

|                                                |                    | -55°C $\leq$ T <sub>C</sub> $\leq$ +125°C<br>4.5 V $\leq$ V <sub>CC</sub> $\leq$ 5.5 V<br>unless otherwise specified |                      |                | Min    | Max |       |

| Wiper response time<br>from stop<br>generation | <sup>t</sup> stpwv | C <sub>L</sub> = 100 pF, see figure 4                                                                                | 9, 10, 11            | All            |        | 500 | μs    |

| Wiper response from<br>clock low               | <sup>t</sup> CLWV  |                                                                                                                      | 9, 10, 11            | All            |        | 1   | ms    |

- $1/V_{\text{IL}}$  (min),  $V_{\text{IH}}$  (max), RES,  $f_{\text{SCL}}$  (min),  $t_{\text{NSTC}}$ ,  $t_{\text{R}}$ ,  $t_{\text{F}}$ ,  $t_{\text{AA}}$  (min), and  $t_{\text{BUF}}$ , are for reference only and are not tested.

- $\underline{2}/$  If not tested, shall be guaranteed to the limits specified in table I.

- $\overline{\underline{3}}$ / Parameters shall be tested as part of device initial characterization and after design and process change. Parameters shall be guaranteed to the limits of table I for all lots not specifically tested.

- 4/ Absolute linearity is utilized to determine actual wiper voltage versus expected voltage as determined by wiper position when used as a potentiometer.

- $\frac{5}{6}$ / MI = R<sub>TOT</sub>/63 or  $(V_H V_L)/63$ , single pot. 6/ Relative linearity is utilized to determine the actual change in voltage between two successive tap positions when used as a potentiometer. It is a measure of the error in step size.

- 7' t<sub>PUR</sub> and t<sub>PUW</sub> are the delays required from the time  $v_{CC}$  is stable until the specified operation can be initiated.

| STANDARD MICROCIRCUIT DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 | SIZE<br>A |                | 5962-95525 |

|------------------------------------------------------------------------------------|-----------|----------------|------------|

|                                                                                    |           | REVISION LEVEL | SHEET<br>8 |

DESC FORM 193A JUL 94

9004708 0009771 353

| Device type     | ALL                                                                     |

|-----------------|-------------------------------------------------------------------------|

| Case outline    | R                                                                       |

| Terminal number | Terminal symbol                                                         |

| 1               | V <sub>UO</sub> VLO VHO AO A2 VW1 VH1 SDA VSS VH2 VL2 VW2 SCL A3 A1 VH3 |

| 18<br>19<br>20  | V <sub>L3</sub><br>V <sub>W3</sub><br>Vcc                               |

FIGURE 1. Terminal connections.

| STANDARD MICROCIRCUIT DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                | 5962-95525 |

|-----------------------------------------------------------------|-----------|----------------|------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL | SHEET<br>9 |

- 9004708 0009772 29T 🖚

| 1                                  |    |                |                | Instruc        | tion fo        | rmat |                |     |                                                                                                                        |

|------------------------------------|----|----------------|----------------|----------------|----------------|------|----------------|-----|------------------------------------------------------------------------------------------------------------------------|

| Instruction                        | 13 | I <sub>2</sub> | I <sub>1</sub> | I <sub>O</sub> | P <sub>1</sub> | PO   | R <sub>1</sub> | RO  | Operation                                                                                                              |

| Read WCR                           | 1  | 0              | 0              | 1              | 1/0            | 1/0  | N/A            | N/A | Read the contents of the wiper counter register pointed to by P <sub>1</sub> - P <sub>0</sub>                          |

| Write WCR                          | 1  | 0              | 1              | 0              | 1/0            | 1/0  | N/A            | N/A | Write new value to the wiper counter register pointed to by P <sub>1</sub> - P <sub>0</sub>                            |

| Read data register                 | 1  | 0              | 1              | 1              | 1/0            | 1/0  | 1/0            | 1/0 | Read the contents of the register pointed to by $P_1$ - $P_0$ and $R_1$ - $R_0$                                        |

| Write data register                | 1  | 1              | 0              | 0              | 1/0            | 1/0  | 1/0            | 1/0 | Write new value to the register pointed to by $P_1$ - $P_0$ and $R_1$ - $R_0$                                          |

| XFR data register to WCR           | 1  | 1              | 0              | 1              | 1/0            | 1/0  | 1/0            | 1/0 | Transfer the contents of the WCR pointed to by $P_1$ - $P_0$ and $R_1$ - $R_0$ to it's associated WCR                  |

| XFR WCR to data<br>register        | 1  | 1              | 1              | 0              | 1/0            | 1/0  | 1/0            | 1/0 | Transfer the contents of the WCR pointed to by $P_1$ - $P_0$ to the register pointed to by $R_1$ - $R_0$               |

| Global XFR data<br>register to WCR | 0  | 0              | 0              | 1              | N/A            | N/A  | 1/0            | 1/0 | Transfer the contents of all four data registers pointed to by R <sub>1</sub> - R <sub>0</sub> to their respective WCR |

| Global XFR WCR to data<br>register | 1  | 0              | 0              | 0              | N/A            | N/A  | 1/0            | 1/0 | Transfer the contents of all WCR's to their respective data registers pointed to by R <sub>1</sub> - R <sub>0</sub>    |

| Increment/decrement<br>wiper       | 0  | 0              | 1              | 0              | 1/0            | 1/0  | N/A            | N/A | Enable increment/decrement of the WCR pointed to by P1 - P0                                                            |

FIGURE 2. <u>Truth table</u>.

| STANDARD<br>MICROCIRCUIT DRAWING<br>DEFENSE ELECTRONICS SUPPLY CENTER<br>DAYTON, OHIO 45444 | SIZE<br>A |                | 5962-95525  |

|---------------------------------------------------------------------------------------------|-----------|----------------|-------------|

|                                                                                             |           | REVISION LEVEL | SHEET<br>10 |

9004708 0009773 126 🖿

<sup>=</sup> Logic "1" voltage level = Logic "0" voltage level

<sup>1/0 =</sup> Logic "1" or logic "0" voltage level

N/A = Not applicable or don't care; that is, a data register is not involved in the operation and need not be addressed

**■ 9004708 0009774 062 ■**

DETAIL A

DETAILED POTENTIOMETER BLOCK DIAGRAM

1 OF 4 POTENTIOMETERS SHOWN

FIGURE 3. Block diagram - continued.

| STANDARD MICROCIRCUIT DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                | 5962-95525  |

|-----------------------------------------------------------------|-----------|----------------|-------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL | SHEET<br>12 |

# 9004708 0009775 TT9 **388**

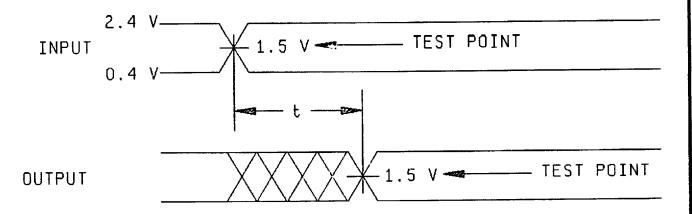

# SWITCHING TEST CIRCUIT (OR EQUIVALENT)

# INPUT/OUTPUT TIMING LEVELS

AC testing: Inputs are driven at 2.4 V for a logic "1" and 0.4 V for a logic "0". Input pulse rise and fall times are  $\leq$  10 ns.

FIGURE 4. Switching test circuit and waveforms.

| STANDARD<br>MICROCIRCUIT DRAWING                     | SIZE<br>A |                | 5962-95525  |

|------------------------------------------------------|-----------|----------------|-------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL | SHEET<br>13 |

DESC FORM 193A JUL 94

# 💌 9004708 0009776 935 **==**

9004708 0009777 871

- 3.12 <u>Endurance</u>. A reprogrammability test shall be completed as part of the vendor's reliability monitors. This reprogrammability test shall be done for initial characterization and after any design or process changes which may affect the reprogrammability of the device. The methods and procedures may be vendor specific, but shall guarantee the number of program/erase endurance cycles listed in section 1.3 herein over the full military temperature range. The vendor's procedure shall be kept under document control and shall be made available upon request of the acquiring or preparing activity, along with test data.

- 3.13 <u>Data retention</u>. A data retention stress test shall be completed as part of the vendor's reliability monitors. This test shall be done for initial characterization and after any design or process change which may affect data retention. The methods and procedures may be vendor specific, but shall guarantee the number of years listed in section 1.3 herein over the full military temperature range. The vendor's procedure shall be kept under document control and shall be made available upon request of the acquiring or preparing activity, along with test data.

- 4. QUALITY ASSURANCE PROVISIONS

- 4.1 <u>Sampling and inspection</u>. For device class M, sampling and inspection procedures shall be in accordance with MIL-STD-883 (see 3.1 herein). For device classes Q and V, sampling and inspection procedures shall be in accordance with MIL-I-38535 and the device manufacturer's QM plan.

- 4.2 <u>Screening</u>. For device class M, screening shall be in accordance with method 5004 of MIL-STD-883, and shall be conducted on all devices prior to quality conformance inspection. For device classes Q and V, screening shall be in accordance with MIL-I-38535, and shall be conducted on all devices prior to qualification and technology conformance inspection.

- 4.2.1 Additional criteria for device class M.

- a. Delete the sequence specified as initial (preburn-in) electrical parameters through interim (postburn-in) electrical parameters of method 5004 and substitute lines 1 through 6 of table IIA herein.

- b. Prior to burn-in, the devices shall be programmed (see 4.5.2 herein) with a checkerboard pattern or equivalent (manufacturers at their option may employ an equivalent pattern provided it is a topologically true alternating bit pattern). The pattern shall be read before and after burn-in. Devices having bits not in the proper state after burn-in shall constitute a device failure and shall be included in the PDA calculation and shall be removed from the lot.

- c. The test circuit shall be maintained by the manufacturer under document revision level control and shall be made available to the preparing or acquiring activity upon request. The test circuit shall specify the inputs, outputs, biases, and power dissipation, as applicable, in accordance with the intent specified in test method 1015.

- (1) Dynamic burn-in (method 1015 of MIL-STD-883, test condition D) using the circuit referenced (see 4.2.1c herein).

- d. Interim and final electrical parameters shall be as specified in table IIA herein.

- e. After the completion of all screening, the device shall be erased and verified prior to delivery.

| STANDARD<br>MICROCIRCUIT DRAWING<br>DEFENSE ELECTRONICS SUPPLY CENTER<br>DAYTON, OHIO 45444 | SIZE<br>A |                | 5962-95525  |

|---------------------------------------------------------------------------------------------|-----------|----------------|-------------|

|                                                                                             |           | REVISION LEVEL | SHEET<br>16 |

9004708 0009779 644 📟

# 4.2.2 Additional criteria for device classes Q and V.

- a. The burn-in test duration, test condition and test temperature, or approved alternatives shall be as specified in the device manufacturer's QM plan in accordance with MIL-I-38535. The burn-in test circuit shall be maintained under document revision level control of the device manufacturer's Technology Review Board (TRB) in accordance with MIL-I-38535 and shall be made available to the acquiring or preparing activity upon request. The test circuit shall specify the inputs, outputs, biases, and power dissipation, as applicable, in accordance with the intent specified in test method 1015.

- b. Interim and final electrical test parameters shall be as specified in table IIA herein.

- c. Additional screening for device class V beyond the requirements of device class Q shall be as specified in appendix B of MIL-I-38535 and as detailed in table IIA herein.

- 4.3 Qualification inspection for device classes Q and V. Qualification inspection for device classes Q and V shall be in accordance with MIL-I-38535. Inspections to be performed shall be those specified in MIL-I-38535 and herein for groups A, B, C, D, and E inspections (see 4.4.1 through 4.4.4).

- 4.4 <u>Conformance inspection</u>. Quality conformance inspection for device class M shall be in accordance with MIL-STD-883 (see 3.1 herein) and as specified herein. Inspections to be performed for device class M shall be those specified in method 5005 of MIL-STD-883 and herein for groups A, B, C, D, and E inspections (see 4.4.1 through 4.4.4). Technology conformance inspection for classes Q and V shall be in accordance with MIL-I-38535 including groups A, B, C, D, and E inspections and as specified herein except where option 2 of MIL-I-38535 permits alternate in-line control testing.

### 4.4.1 Group A inspection.

- a. Tests shall be as specified in table IIA herein.

- b. Subgroup 4 (C<sub>IN</sub> and C<sub>I/O</sub> measurements) shall be measured only for initial qualification and after any process or design changes which may affect input or output capacitance. Capacitance shall be measured between the designated terminal and GND at a frequency of 1 MHz. Sample size is 15 devices with no failures and all input and output terminals tested.

- c. For device class M, subgroups 7 and 8 tests shall be sufficient to verify the truth table. For device classes Q and V, subgroups 7 and 8 shall include verifying the functionality of the device; these tests shall have been fault graded in accordance with MIL-STD-883, test method 5012 (see 1.5 herein).

- d. O/V (latch-up) tests shall be measured only for initial qualification and after any design or process changes which may affect the performance of the device. For device class M, procedures and circuits shall be maintained under document revision level control by the manufacturer and shall be made available to the preparing activity or acquiring activity upon request. For device classes Q and V, performance of O/V (latch-up) testing shall be as specified in the manufacturer's QM plan, the procedures and circuits shall be under the control of the device manufacturer's TRB in accordance with MIL-I-38535 and shall be made available to the preparing activity or acquiring activity upon request. Testing shall be on all pins, on five devices with zero failures. Latch-up test shall be considered destructive. Information contained in JEDEC Standard number 17 may be used for reference.

- e. All devices selected for testing shall be programmed with a checkerboard pattern or equivalent. After completion of all testing, the devices shall be erased and verified, (except devices submitted for groups C and D testing and devices to be archived, i.e., devices not to be sold).

- 4.4.2 <u>Group C inspection</u>. The group C inspection end-point electrical parameters shall be as specified in table IIA herein. Delta limits shall apply only to subgroup 1 of group C and shall consist of test specified in table IIB herein.

| STANDARD MICROCIRCUIT DRAWING                        | SIZE<br>A |                | 5962-95525  |

|------------------------------------------------------|-----------|----------------|-------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL | SHEET<br>17 |

DESC FORM 193A JUL 94

**9004708 0009780 366**

TABLE IIA. Electrical test requirements. 1/2/3/4/5/6/7/

| · · ·       |                                               | T                                             | <u> </u>                          |                                   |

|-------------|-----------------------------------------------|-----------------------------------------------|-----------------------------------|-----------------------------------|

| Line<br>no. | Test<br>requirements                          | Subgroups<br>(per method<br>5005, table<br>I) | (per MIL                          | roups<br>-I-38535,<br>- III)      |

|             |                                               | Device<br>class<br>M                          | Device<br>class<br>Q              | Device<br>class<br>V              |

| 1           | Interim electrical<br>parameters<br>(see 4.2) |                                               |                                   | 1,7,9                             |

| 2           | Static burn-in I<br>method 1015               | Not<br>required                               | Not<br>required                   | Not<br>required                   |

| 3           | Same as line 1                                |                                               |                                   | 1*,7* ∆                           |

| 4           | Dynamic burn-in<br>(method 1015)              | Required                                      | Required                          | Required                          |

| 5           | Same as line 1                                |                                               |                                   | 1*,7* ∆                           |

| 6           | Final electrical parameters                   | 1*,2,3,7*,<br>8A,8B,9,10,<br>11               | 1*,2,3,7*,<br>8A,8B,9,10,<br>11   | 1*,2,3,7*,<br>8A,8B,9,10,<br>11   |

| 7           | Group A test<br>requirements                  | 1,2,3,4**,7,<br>8A,8B,9,10,<br>11             | 1,2,3,4**,7,<br>8A,8B,9,10,<br>11 | 1,2,3,4**,7,<br>8A,8B,9,10,<br>11 |

| 8           | Group C end-point<br>electrical<br>parameters | 2,3,7,<br>8A,8B                               | 1,2,3,7,<br>8A,8B                 | 1,2,3,7,<br>8A,8B,9,10,<br>11 Δ   |

| 9           | Group D end-point<br>electrical<br>parameters | 2,3,8A,8B                                     | 2,3,8A,8B                         | 2,3,8A,8B                         |

| 10          | Group E end-point<br>electrical<br>parameters | 1,7,9                                         | 1,7,9                             | 1,7,9                             |

- 1/ Blank spaces indicate test are not applicable.

- 2/ Any or all subgroups may be combined when using high-speed testers.

3/ Subgroups 7, 8A, and 8B functional tests shall verify the truth table.

- 4/ \* Indicates PDA applies to subgroups 1 and 7. 5/ \*\* See 4.4.1b.

- $\frac{6}{6}$ /  $\Delta$  Indicates delta limit (see table IIB) shall be required where specified, and the delta values shall be computed with reference to the previous interim electrical parameters (see line 1). For device class V, performance of delta tests and limits shall be as specified in the manufacturer's QM plan. 7/ See 4.4.1d.

| STANDARD MICROCIRCUIT DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 | SIZE<br>A |                | 5962-95525  |

|------------------------------------------------------------------------------------|-----------|----------------|-------------|

|                                                                                    |           | REVISION LEVEL | SHEET<br>18 |

9004708 0009781 2T2 **=**

### 4.4.2.1 Additional criteria for device class M.

- a. Steady-state life test conditions, method 1005 of MIL-STD-883:

- (1) The device selected for testing shall be programmed with a checkerboard pattern or equivalent.

- (2) Test condition D. The test circuit shall be maintained by the manufacturer under document revision level control and shall be made available to the preparing or acquiring activity upon request. The test circuit shall specify the inputs, outputs, biases, and power dissipation, as applicable, in accordance with the intent specified in test method 1005.

- (3)  $T_A = +125$ °C, minimum.

- (4) Test duration: 1,000 hours, except as specified in method 1005 of MIL-STD-883.

- b. All devices requiring end-point electrical testing shall be programmed with a checkerboard or equivalent alternating bit pattern.

- c. After the completion of all testing, the devices shall be cleared and verified prior to delivery (except devices submitted for group D testing and devices to be archived, i.e., devices not to be sold).

- 4.4.2.2 Additional criteria for device classes Q and V. The steady-state life test duration, test condition and test temperature, or approved alternatives shall be as specified in the device manufacturer's QM plan in accordance with MIL-I-38535. The test circuit shall be maintained under document revision level control by the device manufacturer's TRB, in accordance with MIL-I-38535, and shall be made available to the acquiring or preparing activity upon request. The test circuit shall specify the inputs, outputs, biases, and power dissipation, as applicable, in accordance with the intent specified in test method 1005.

- 4.4.3 <u>Group D inspection</u>. The group D inspection end-point electrical parameters shall be as specified in table IIA herein. The devices selected for testing shall be programmed with a checkerboard pattern or equivalent. After completion of all testing, the devices shall be erased and verified (except devices to be archived, i.e., devices not to be sold).

- 4.4.4 <u>Group E inspection</u>. Group E inspection is required only for parts intended to be marked as radiation hardness assured (see 3.5 herein). RHA levels for device classes Q and V shall be M, D, L, R, F, G, and H and for device class M shall be M and D.

- a. End-point electrical parameters shall be as specified in table IIA herein.

- b. For device class M, the devices shall be subjected to radiation hardness assured tests as specified in MIL-I-38535, appendix A, for the RHA level being tested. For device classes Q and V, the devices or test vehicle shall be subjected to radiation hardness assured tests as specified in MIL-I-38535 for the RHA level being tested. All device classes must meet the postirradiation end-point electrical parameter limits as defined in table I at T<sub>A</sub> = +25°C ±5°C, after exposure, to the subgroups specified in table IIA herein.

- c. When specified in the purchase order or contract, a copy of the RHA delta limits shall be supplied.

TABLE IIB. Delta limits at 25°C.

| Test <u>1</u> / | All device types                           |

|-----------------|--------------------------------------------|

| I <sub>SB</sub> | ±10 percent of specified value in table I. |

| ILI             | ±10 percent of specified value in table I. |

| I <sub>LO</sub> | ±10 percent of specified value in table I. |

1/ The above parameter shall be recorded before and after the required burn-in and life tests to determine delta.

| STANDARD MICROCIRCUIT DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 | SIZE<br>A |                | 5962-95525 |

|------------------------------------------------------------------------------------|-----------|----------------|------------|

|                                                                                    |           | REVISION LEVEL | SHEET      |

DESC FORM 193A JUL 94

**9**004708 0009782 1399 **=**

- 4.5 <u>Methods of inspection</u>. Methods of inspection shall be as specified in the appropriate figures and tables herein.

- 4.5.1 <u>Erasing procedures</u>. The erasing procedures shall be as specified by the device manufacturer and shall be available upon request.

- 4.5.2 <u>Programming procedure</u>. The programming procedures shall be as specified by the device manufacturer and shall be made available upon request.

- 4.6 <u>Delta measurements for device class V</u>. Delta measurements, as specified in table IIA, shall be made and recorded before and after the required burn-in screens and steady-state life tests to determine delta compliance. The electrical parameters to be measured, with associated delta limits are listed in table IIB. The device manufacturer may, at his option, either perform delta measurements or within 24 hours after burn-in perform final electrical parameter tests, subgroups 1, 7, and 9.

- PACKAGING

- 5.1 <u>Packaging requirements</u>. The requirements for packaging shall be in accordance with MIL-STD-883 (see 3.1 herein) for device class M and MIL-I-38535 for device classes Q and V.

- 6. NOTES

(This section contains information of a general or explanatory nature that may be helpful, but is not mandatory.)

- 6.1 <u>Intended use</u>. Microcircuits conforming to this drawing are intended for use for Government microcircuit applications (original equipment), design applications, and logistics purposes.

- 6.1.1 <u>Replaceability</u>. Microcircuits covered by this drawing will replace the same generic device covered by a contractor-prepared specification or drawing.

- 6.1.2 <u>Substitutability</u>. Device class Q devices will replace device class M devices.

- 6.2 <u>Configuration control of SMD's</u>. All proposed changes to existing SMD's will be coordinated with the users of record for the individual documents. This coordination will be accomplished in accordance with MIL-STD-973 using DD Form 1692, Engineering Change Proposal.

- 6.3 Record of users. Military and industrial users shall inform Defense Electronics Supply Center when a system application requires configuration control and which SMD's are applicable to that system. DESC will maintain a record of users and this list will be used for coordination and distribution of changes to the drawings. Users of drawings covering microelectronic devices (FSC 5962) should contact DESC-EC, telephone (513) 296-6047.

- 6.4 <u>Comments</u>. Comments on this drawing should be directed to DESC-EC, Dayton, Ohio 45444, or telephone (513) 296-5377.

- 6.5 <u>Abbreviations, symbols, and definitions</u>. The abbreviations, symbols, and definitions used herein are defined in MIL-I-38535 and MIL-STD-1331.

AL . . . . . . . . . Absolute linearity, C<sub>IN</sub> . . . . . . . . . Input capacitance  $c_{1/0}^{\text{in}}$  . . . . . . . . Input/output capacitance each potentiometer . . . . . . . . . Load capacitance f<sub>SCL</sub> ---- SCL clock frequency V<sub>CC</sub> supply current, active . . . . . . . Input leakage current I<sub>LI</sub> .  $\mathbf{I}_{\mathsf{LO}}$ . . . . . . . . Output leakage current Low level output current V<sub>CC</sub> supply current, standby Wiper current Noise figure P<sub>IN</sub> . . . . . . . . . . . . . . . . Power rating, each potentiometer End to end resistance tolerance . . . . . . . . . . . Resolution Relative linearity, each potentiometer  $R_{\underline{U}}$  . . . . . . . . . . Wiper resistance

| STANDARD MICROCIRCUIT DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 | SIZE<br>A |                | 5962-95525 |

|------------------------------------------------------------------------------------|-----------|----------------|------------|

|                                                                                    |           | REVISION LEVEL | SHEET 20   |

DESC FORM 193A JUL 94

**3** 9004708 0009783 075 🗯

6.5 Abbreviations, symbols, and definitions - continued. . . . . . . . . Ambient temperature  $\mathsf{t}_{\mathsf{AA}}^{\circ}$  . . . . . . . . . . . . . SCL low to SDA data out valid BUF ..... Bus free time prior to new transmission T<sub>C</sub> . . . . . . . . . . Case temperature  $t_{\text{CLWV}}$  . . . . . . . . Wiper response from clock low  $TC_R$  . . . . . . Temperature coefficient of resistance t<sub>DH</sub> . . . . . . . . . . Data out hold time SCL and SDA fall time t<sub>HDDAT</sub> . . . . . . . . Data in hold time t<sub>HDSTA</sub> . . . . . . . . . Start condition hold time t<sub>HIGH</sub> . . . . . . . . . . Clock high period t<sub>LOW</sub> . . . . . . . . . . Clock low period Noise suppression time constant (glitch filter) t<sub>NSTC</sub> · · TPUR ..... Power-up to initiation of read operation Power-up to initiation of write operation t<sub>PUW</sub> ... SCL and SDA rise time Storage temperature T<sub>stg</sub> · · · · · Wiper response time from stop generation Data in setup time t<sub>SUDAT</sub> · · · Start condition setup time (for a repeated start condition) <sup>t</sup>susta Stop condition setup time <sup>t</sup>susto Write cycle time (nonvolatile write operation) τwr · . . . .  $\mathbf{V}_{\mathsf{CC}}$  supply voltage  $\nu_{cc}$  . .  $v_{H'}^{r}$ ,  $v_{L}$  ...... Equivalent to the terminal connections on either end of a mechanical potentiometer High level input voltage ν... Low level input voltage V<sub>1N</sub> . . . . Input voltage V<sub>1/0</sub> . . . . . . . . . . . . . Input/output voltage Low level output voltage V<sub>OL</sub> . . . . Reference voltage REF  $\rm V_{SS}$  supply voltage Voltage on any  $\rm V_H$  or  $\rm V_L$  pin Equivalent to the wiper output of a mechanical potentiometer v<sub>ss</sub> . . . . . . . . . Differential voltage

6.5.1 <u>Timing limits</u>. The table of timing values shows either a minimum or a maximum limit for each parameter. Input requirements are specified from the external system point of view. Thus, address setup time is shown as a minimum since the system must supply at least that much time (even though most devices do not require it). On the other hand, responses from the memory are specified from the device point of view. Thus, the access time is shown as a maximum since the device never provides data later than that time.

| STANDARD MICROCIRCUIT DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 | SIZE<br>A |                | 5962-95525 |

|------------------------------------------------------------------------------------|-----------|----------------|------------|

|                                                                                    |           | REVISION LEVEL | SHEET 21   |

DESC FORM 193A JUL 94

■ 9004708 0009784 TO1 **■**

### 6.5.2 Waveforms.

| WAVEFORM<br>SYMBOL | INPUT                                 | OUTPUT                     |  |

|--------------------|---------------------------------------|----------------------------|--|

|                    | MUST BE<br>VALID                      | WILL BE<br>VALID           |  |

|                    | CHANGE FROM<br>H TO L                 | WIIL CHANGE FROM<br>H TO L |  |

| _/////             | CHANGE FROM<br>L TO H                 | WILL CHANGE FROM<br>L TO H |  |

| XXXXXX             | DON'T CARE<br>ANY CHANGE<br>PERMITTED | CHANGING<br>STATE UNKNOWN  |  |

|                    |                                       | HIGH<br>IMPEDANCE          |  |

6.6 One part — one part number system. The one part — one part number system described below has been developed to allow for transitions between identical generic devices covered by the three major microcircuit requirements documents (MIL—H—38534, MIL—I—38535, and 1.2.1 of MIL—STD—883) without the necessity for the generation of unique PIN's. The three military requirements documents represent different class levels, and previously when a device manufacturer upgraded military product from one class level to another, the benefits of the upgraded product were unavailable to the Original Equipment Manufacturer (OEM), that was contractually locked into the original unique PIN. By establishing a one part number system covering all three documents, the OEM can acquire to the highest class level available for a given generic device to meet system needs without modifying the original contract parts selection criteria.

| Military documentation format                              | Example PIN under new system | Manufacturing source listing | Document<br><u>Listing</u> |

|------------------------------------------------------------|------------------------------|------------------------------|----------------------------|

| New MIL-H-38534 Standard Microcircuit<br>Drawings          | 5962-XXXXXZZ(H or K)YY       | QML-38534                    | MIL-BUL-103                |

| New MIL-I-38535 Standard Microcircuit<br>Drawings          | 5962-XXXXXZZ(Q or V)YY       | QML-38535                    | MIL-BUL-103                |

| New 1.2.1 of MIL-STD-883 Standard<br>Microcircuit Drawings | 5962-XXXXXZZ(M)YY            | MIL-BUL-103                  | MIL-BUL-103                |

## 6.7 Sources of supply.

- 6.7.1 <u>Sources of supply for device classes Q and V</u>. Sources of supply for device classes Q and V are listed in QML-38535. The vendors listed in QML-38535 have submitted a certificate of compliance (see 3.6 herein) to DESC-EC and have agreed to this drawing.

- 6.7.2 <u>Approved sources of supply for device class M</u>. Approved sources of supply for class M are listed in MIL-BUL-103. The vendors listed in MIL-BUL-103 have agreed to this drawing and a certificate of compliance (see 3.6 herein) has been submitted to and accepted by DESC-EC.

| STANDARD<br>MICROCIRCUIT DRAWING<br>DEFENSE ELECTRONICS SUPPLY CENTER<br>DAYTON, OHIO 45444 | SIZE<br>A |                | 5962-95525 |

|---------------------------------------------------------------------------------------------|-----------|----------------|------------|

|                                                                                             |           | REVISION LEVEL | SHEET 22   |

DESC FORM 193A JUL 94

**9**004708 0009785 948 **9**

46646