### 1.0 Key Features

- Can be used in designs presently using the SYM20C15

- Single-chip, half-duplex 1200 bits per second FSK modem

- Bell 202 shift frequencies of 1200Hz and 2200Hz

- 3.3V 5.0V power supply

- · Transmit-signal wave shaping

- · Receive band-pass filter

- · Low power: optimal for intrinsically safe applications

- · CMOS compatible

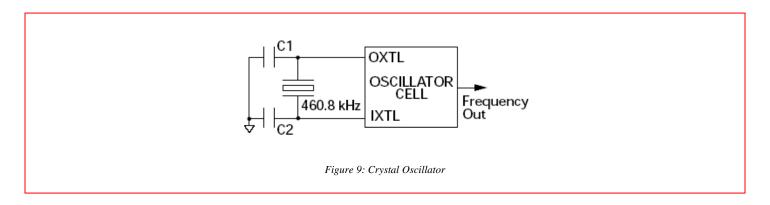

- Internal oscillator requires 460.8kHz crystal or ceramic resonator

- · Meets HART physical layer requirements

- Industrial temperature range of -40°C to +85°C

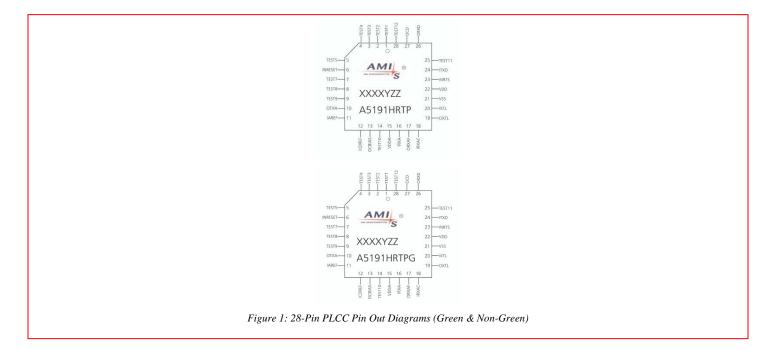

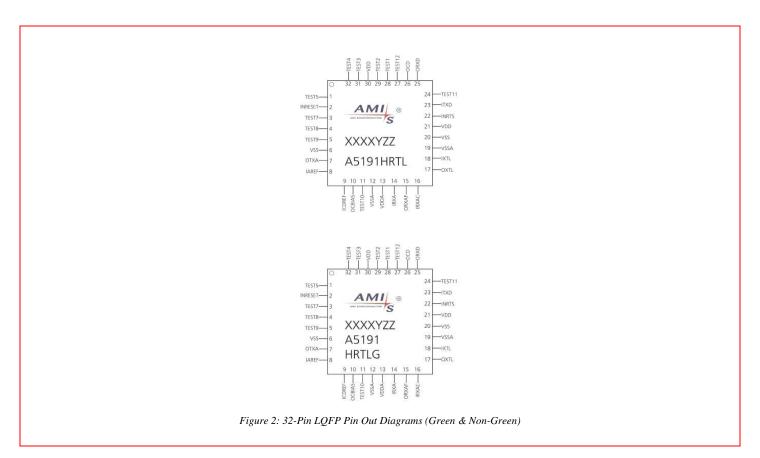

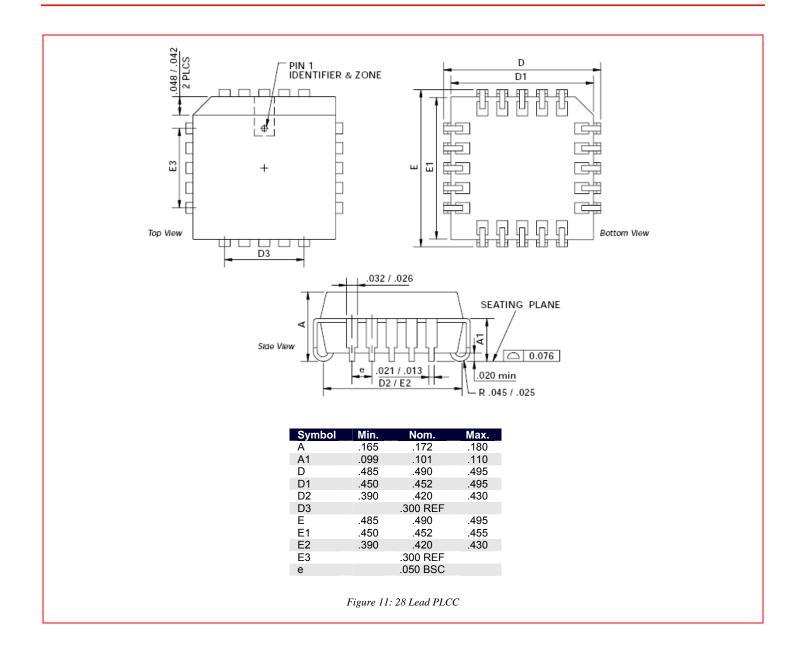

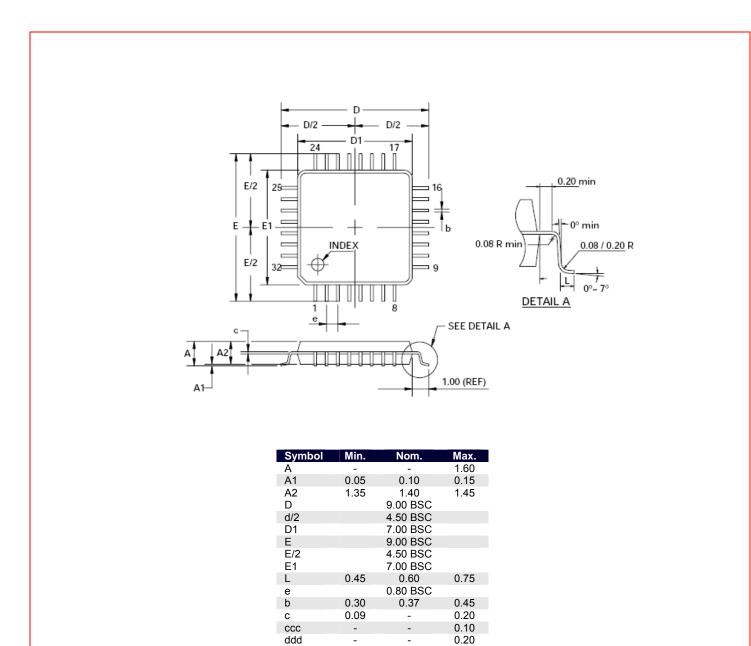

- Available in 28-pin PLCC and 32-pin LQFP packages

### 2.0 Description

The A5191HRT is a single-chip, CMOS modem for use in highway addressable remote transducer (HART) field instruments and masters. The modem and a few external passive components provide all of the functions needed to satisfy HART physical layer requirements including modulation, demodulation, receive filtering, carrier detect, and transmit-signal shaping. The A5191HRT is pincompatible with the SYM20C15. See the Pin Description and Functional Description sections for details on pin compatibility with the SYM20C15.

The A5191HRT uses phase continuous frequency shift keying (FSK) at 1200 bits per second. To conserve power the receive circuits are disabled during transmit operations and vice versa. This provides the half-duplex operation used in HART communications.

Table 1: Pin Out Summary 28-Pin PLCC, A5191HRTP/Pg (12197-504/508)

| Pin No. | Signal Name | Type   | Pin Description                                                                             |  |  |  |

|---------|-------------|--------|---------------------------------------------------------------------------------------------|--|--|--|

| 1       | TEST1       | Input  | Connect to VSS                                                                              |  |  |  |

| 2       | TEST2       | -      | No connect                                                                                  |  |  |  |

| 3       | TEST3       | -      | No connect                                                                                  |  |  |  |

| 4       | TEST4       | -      | No connect                                                                                  |  |  |  |

| 5       | TEST5       | Input  | Connect to VSS                                                                              |  |  |  |

| 6       | INRESET     | Input  | Reset all digital logic when low                                                            |  |  |  |

| 7       | TEST7       | Input  | Connect to VSS                                                                              |  |  |  |

| 8       | TEST8       | Input  | Connect to VSS                                                                              |  |  |  |

| 9       | TEST9       | Input  | Connect to VSS                                                                              |  |  |  |

| 10      | OTXA        | Output | Output transmit analog, FSK modulated HART transmit signal to 4-20mA loop interface circuit |  |  |  |

| 11      | IAREF       | Input  | Analog reference voltage                                                                    |  |  |  |

| 12      | ICDREF      | Input  | Carrier detect reference voltage                                                            |  |  |  |

| 13      | OCBIAS      | Output | Comparator bias current                                                                     |  |  |  |

| 14      | TEST10      | Input  | Connect to VSS                                                                              |  |  |  |

| 15      | VDDA        | Power  | Analog supply voltage                                                                       |  |  |  |

| 16      | IRXA        | Input  | FSK modulated HART receive signal from 4-20mA loop interface circuit                        |  |  |  |

| 17      | ORXAF       | Output | Analog receive filter output                                                                |  |  |  |

| 18      | IRXAC       | Input  | Analog receive comparator input                                                             |  |  |  |

| 19      | OXTL        | Output | Crystal oscillator output                                                                   |  |  |  |

| 20      | IXTL        | Input  | Crystal oscillator input                                                                    |  |  |  |

| 21      | VSS         | Ground | Ground                                                                                      |  |  |  |

| 22      | VDD         | Power  | Digital supply voltage                                                                      |  |  |  |

| 23      | INRTS       | Input  | Request to send                                                                             |  |  |  |

| 24      | ITXD        | Input  | Input transmit date, transmitted HART data stream from UART                                 |  |  |  |

| 25      | TEST11      | -      | No connect                                                                                  |  |  |  |

| 26      | ORXD        | Output | Received demodulated HART data to UART                                                      |  |  |  |

| 27      | OCD         | Output | Carrier detect output                                                                       |  |  |  |

| 28      | TEST12      | -      | No connect                                                                                  |  |  |  |

Table 2: Pin Out Summary 32-Pin LQFP, A5191HRTI/Lg (12197-503/507)

| Table 2.1 III | Out Sulfilliary 32- |        | 3191111(11/Lg (12197-303/307)                                                               |  |  |  |

|---------------|---------------------|--------|---------------------------------------------------------------------------------------------|--|--|--|

| Pin No.       | Signal Name         | Туре   | Pin Description                                                                             |  |  |  |

| 1             | TEST5               | Input  | Connect to VSS                                                                              |  |  |  |

| 2             | INRESET             | Input  | Reset all logic when low, connect to VDD for normal operation                               |  |  |  |

| 3             | TEST7               | Input  | Connect to VSS                                                                              |  |  |  |

| 4             | TEST8               | Input  | Connect to VSS                                                                              |  |  |  |

| 5             | TEST9               | Input  | Connect to VSS                                                                              |  |  |  |

| 6             | VSS                 | Ground | Digital ground                                                                              |  |  |  |

| 7             | OTXA                | Output | Output transmit analog, FSK modulated HART transmit signal to 4-20mA loop interface circuit |  |  |  |

| 8             | IAREF               | Input  | Analog reference voltage                                                                    |  |  |  |

| 9             | ICDREF              | Input  | Carrier detect reference voltage                                                            |  |  |  |

| 10            | OCBIAS              | Output | Comparator bias current                                                                     |  |  |  |

| 11            | TEST10              | Input  | Connect to VSS                                                                              |  |  |  |

| 12            | VSSA                | Ground | Analog ground                                                                               |  |  |  |

| 13            | VDDA                | Power  | Analog supply voltage                                                                       |  |  |  |

| 14            | IRXA                | Input  | FS modulated HART receive signal from 4-20mA loop interface circuit                         |  |  |  |

| 15            | ORXAF               | Output | Analog receive filter input                                                                 |  |  |  |

| 16            | IRXAC               | Input  | Analog receive comparator input                                                             |  |  |  |

| 17            | OXTL                | Output | Crystal oscillator output                                                                   |  |  |  |

| 18            | IXTL                | Input  | Crystal oscillator input                                                                    |  |  |  |

| 19            | VSSA                | Ground | Analog ground                                                                               |  |  |  |

| 20            | VSS                 | Ground | Digital ground                                                                              |  |  |  |

| 21            | VDD                 | Power  | Digital supply voltage                                                                      |  |  |  |

| 22            | INRTS               | Input  | Request to send                                                                             |  |  |  |

| 23            | ITXD                | Input  | Input transmit data, transmit HART data stream from UART                                    |  |  |  |

| 24            | TEST11              | -      | No connect                                                                                  |  |  |  |

| 25            | ORXD                | Output | Received demodulated HART data to UART                                                      |  |  |  |

| 26            | OCD                 | Output | Carrier detect output                                                                       |  |  |  |

| 27            | TEST12              | -      | No connect                                                                                  |  |  |  |

| 28            | TEST1               | Input  | Connect to VSS                                                                              |  |  |  |

| 29            | TEST2               | -      | No connect                                                                                  |  |  |  |

| 30            | VDD                 | Power  | Digital supply voltage                                                                      |  |  |  |

| 31            | TEST3               | -      | No connect                                                                                  |  |  |  |

| 32            | TEST4               | -      | No connect                                                                                  |  |  |  |

|               |                     |        |                                                                                             |  |  |  |

## 3.0 Pin Descriptions

Table 3: Pin Descriptions

| Symbol                      | Pin Name                         | Description                                                                                                                                                                                                                                                                         |

|-----------------------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IAREF                       | Analog reference voltage         | Analog input sets the dc operating point of the operational amplifiers and comparators and is usually selected to split the dc potential between VDD and VSS. See Table 5.                                                                                                          |

| ICDREF                      | Carrier detect reference voltage | Analog input controls at which level the carrier detect (OCD) becomes active. This is determined by the dc voltage difference between ICDREF and IAREF. Selecting ICDREF - IAREF equal to $0.08~V_{\text{DC}}$ will set the carrier detect to a nominal $100~\text{mV}_{\text{PP}}$ |

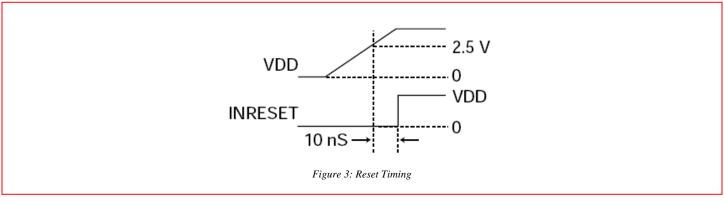

| INRESET Reset digital logic |                                  | When at logic low ( $V_{SS}$ ) this input holds all the digital logic in reset. During normal operation INRESET should be at $V_{DD}$ . INRESET should be held low for a minimum of 10nS after $V_{DD}$ = 2.5V as shown in Table 3.                                                 |

| INRTS                       | Request to send                  | Active-low input selects the operation of the modulator. OTXA is enabled when this signal is low. This signal must be held high during power-up.                                                                                                                                    |

| IRXA                        | Analog receive input             | Input accepts the 1200/2200Hz signals from the external filter.                                                                                                                                                                                                                     |

| IRXAC                       | Analog receive comparator input  | Positive input of the carrier detect comparator and the receiver filter comparator.                                                                                                                                                                                                 |

| ITXD                        | Digital transmit input (CMOS)    | Input to the modulator accepts digital data in NRZ form. When ITXD is low, the modulator output frequency is 2200Hz. When ITXD is high, the modulator output frequency is 1200Hz.                                                                                                   |

| IXTL                        | Oscillator input                 | Input to the internal oscillator must be connected to a parallel mode 460.8kHz ceramic resonator when using the internal oscillator or grounded when using an external 460.8kHz clock signal.                                                                                       |

| OCBIAS                      | Comparator bias current          | The current through this output controls the operating parameters of the internal operational amplifiers and comparators. For normal operation, OCBIAS current is set to 2.54A.                                                                                                     |

| OCD        | Carrier detect output         | Output goes high when a valid input is recognized on IRXA. If the received signal is greater than the threshold specified on ICDREF for four cycles of the IRXA signal, the valid input is recognized.                                  |

|------------|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ORXAF      | Analog receive filter output  | Signal is the square wave output of the receiver high-pass filter.                                                                                                                                                                      |

| ORXD       | Digital receive output (CMOS) | Signal outputs the digital receive data. When the received signal (IRXA) is 1200Hz, ORXD outputs logic high. When the received signal (IRXA) is 2200Hz, ORXD outputs logic low. ORXD is qualified internally with OCD.                  |

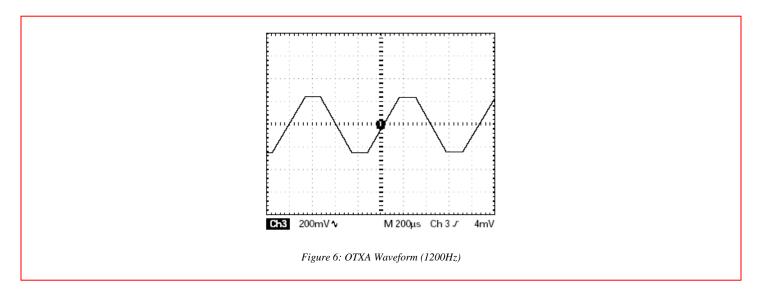

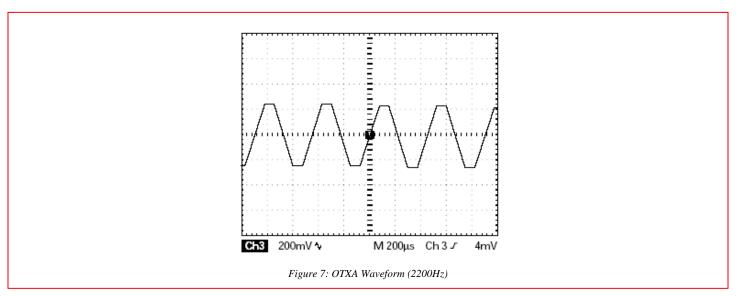

| OTXA       | Analog transmit output        | Output provides the trapezoidal signal controlled by ITXD. When ITXD is low, the output frequency is 2200Hz. When ITXD is high, the output frequency is 1200Hz. This output is active when INRTS is low and 0.5 Vpc when INRTS is high. |

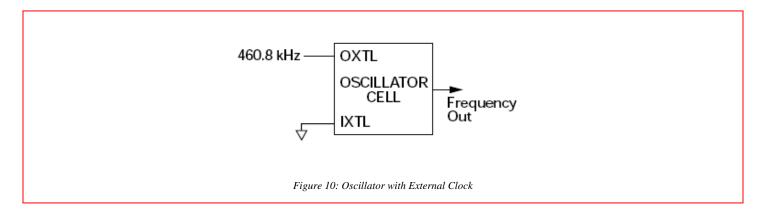

| OXTL       | Oscillator output             | Output from the internal oscillator must be connected to an external 460.8kHz clock signal or to a parallel mode 460.8kHz ceramic resonator when using the internal oscillator.                                                         |

| TEST(12:1) | Factory test                  | Factory test pins; for normal operation, tie these signals as per Table 1 and Table 2                                                                                                                                                   |

| VDD        | Digital power                 | Power for the digital modem circuitry                                                                                                                                                                                                   |

| VDDA       | Analog supply voltage         | Power for the analog modem circuitry                                                                                                                                                                                                    |

| VSS        | Ground                        | Analog and digital ground                                                                                                                                                                                                               |

| VSSA       | Analog ground                 |                                                                                                                                                                                                                                         |

#### Note:

This signal is also present on the LSI 20C15. It is labeled as Test6. The 20C15 data sheet mentions the reset function of this pin but does not emphasize its use to reset the chip. Reliable operation of the modem requires a hardware reset as shown in Figure 3. This is true for the AMIS 12197-503 and 12197-504 as well as the LSI 20C15.

## **4.0 Functional Description**

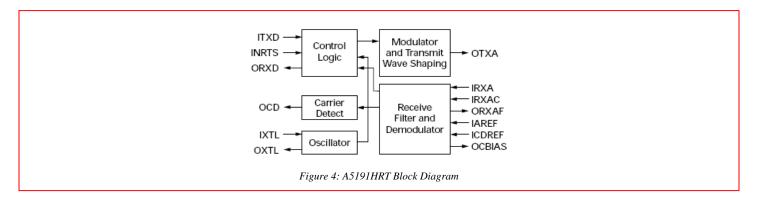

The A5191HRT is a functional equivalent of the SYM20C15 HART Modem. It contains a transmit data modulator and signal shaper, carrier detect circuitry, analog receiver and demodulator circuitry and an oscillator, as shown in Figure 4.

The internal HART modem modulates the transmit-signal and demodulates the receive signal. The transmit-signal shaper enables the A5191HRT to transmit a HART compliant signal. The carrier is detected by comparing the receiver filter output with the difference between two external voltage references. The analog receive circuitry band-pass filters the received signal for input to the modem and the carrier detect circuitry. The oscillator provides the modem with a stable time base using either a simple external resonator or an external clock source.

#### **4.1 A5191HRT Logic**

The modem consists of a modulator and demodulator. The modem uses shift frequencies of nominally 1200Hz (for a 1) and 220Hz (for a 0). The bit rate is 1200 bits/second.

#### 4.1.1. Modulator

The modulator accepts digital data in NRZ form at the ITXD input and generates the FSK modulated signal at the OTXA output. INRTS must be a logic low for the modulator to be active.

#### 4.1.2. Demodulator

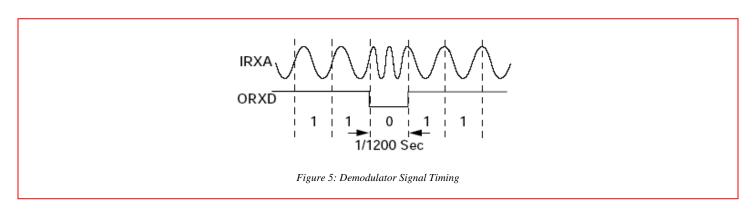

The demodulator accepts an FSK signal at the IRXA input and reproduces the original modulating signal at the ORXD output. The nominal bit rate is 1200 bits per second. Figure 5 illustrates the demodulation process.

The output of the demodulator is qualified with the carrier detect signal (OCD), therefore, only IRXA signals large enough to be detected (100mV<sub>PP</sub> typically) by the carrier detect circuit produce received serial data at ORXD.

Maximum demodulator jitter is 12 percent of one bit given input frequencies within HART specifications, a clock frequency of 460.8kHz (±1.0 percent) and zero input (IRXA) asymmetry.

#### 4.2 Transmit-Signal Shaper

The transmit-signal shaper generates a HART compliant FSK modulated signal at OTXA. Figure 6 and Figure 7 show the transmit-signal forms of the A5191HRT.

For IAREF = 1.235  $V_{DC}$ , OTXA will have a voltage swing from approximately 0.25 to 0.75  $V_{DC}$ .

#### 4.3 Carrier Detect Circuitry

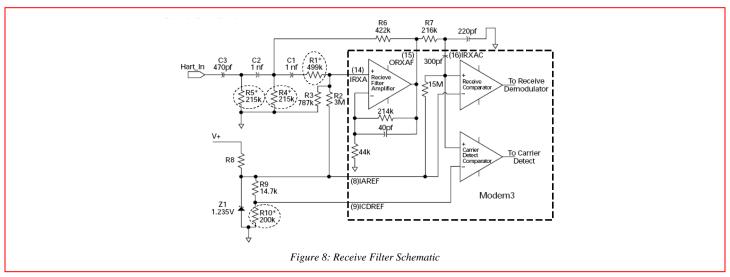

The carrier detect comparator shown in Figure 8 generates logic low output if the IRXAC voltage is below ICDREF. The comparator output is fed into a carrier detect block (see Figure 4). The carrier detect block drives the carrier detect output pin OCD high if INRTS is high and four consecutive pulses out of the comparator have arrived. OCD stays high as long as INRTS is high and the next comparator pulse is received in less than 2.5ms. Once OCD goes inactive, it takes four consecutive pulses out of the comparator to

assert OCD again. Four consecutive pulses amount to 3.33ms when the received signal is 1200Hz and to 1.82ms when the received signal is 2200Hz.

#### 4.4 Analog Receiver Circuitry

#### 4.4.1. Voltage References

The A5191HRT requires two voltage references, IAREF and ICDREF.

IAREF sets the dc operating point of the internal operational amplifiers and comparators. A 1.235  $V_{DC}$  reference (Analog Devices AD589) is suitable as IAREF.

The level at which OCD (carrier detect) becomes active is determined by the dc voltage difference (ICDREF - IAREF). Selecting a voltage difference of 0.08  $V_{DC}$  will set the carrier detect to a nominal 100 mV<sub>PP</sub>.

#### 4.4.2. Bias Current Resistor

The A5191HRT requires a bias current resistor to be connected between OCBIAS and V<sub>ss</sub>. The bias current controls the operating parameters of the internal operational amplifiers and comparators.

The value of the bias current resistor is determined by the reference voltage IAREF and the following formula:

$$R_{BIAS} = \left(\frac{IAREF}{2.5 \,\mu A}\right)$$

The recommended bias current resistor is 500KW when IAREF is equal to 1.235 Vpc.

In Figure 8 all external capacitor values have a tolerance of  $\pm 5$  percent and the resistors have a tolerance of  $\pm 1$  percent, except the 3MW which has a tolerance of  $\pm 5$  percent. External to the A5191HRT, the filter exhibits a three-pole, high-pass filter at 624Hz and a one-pole, low-pass filter at 2500Hz. Internally, the A5191HRT has a high-pass pole at 35Hz and a low-pass pole at 90kHz. The low-pass pole can vary as much as  $\pm 30$  percent. The input impedance of the entire filter is greater than 150MW at frequencies below 50kHz.

#### 4.5 Oscillator

The A5191HRT requires a 460.8kHz clock signal on OXTL. This can be provided by an external clock or external components may be connected to the A5191HRT internal oscillator.

#### 4.5.1. Internal Oscillator Option

The oscillator cell will function with either a 460.8kHz crystal or ceramic resonator. A parallel resonant ceramic resonator can be connected between OXTL and IXTL. Figure 9 illustrates the crystal option for clock generation using a 460.8kHz (±I percent tolerance) parallel resonant crystal and two tuning capacitors. The actual values of the capacitors may depend on the recommendations of the manufacturer of the resonator. Typically, capacitors in the range of 100pF to 470pF are used.

#### 4.5.2. External Clock Option

It may be desirable to use an external 460.8kHz clock as shown in Figure 10 rather than the internal oscillator because of the high cost and low availability of ceramic resonators. In addition, the A5191HRT consumes less current when an external clock is used. Minimum current consumption occurs with the clock connected to OXTL and IXTL connected to  $V_{\rm ss}$ .

### **5.0 Ordering Information**

The A5191HRT is available in a 28-pin plastic leaded chip carrier (PLCC) and 32-pin low-profile quad flat pack (LQFP). Use the following part number when ordering. Contact your local sales representative for more information: www.onsemi.com.

| Part Number    | Package                             | Shipping Configuration | Temperature Range           |

|----------------|-------------------------------------|------------------------|-----------------------------|

| A5191HRTLG-XTD | 32-pin LQFP<br>Green/RoHS compliant | Tube/Tray              | -40°C to +85°C (Industrial) |

| A5191HRTLG-XTP | 32-pin LQFP<br>Green/RoHS compliant | Tape & Reel            | -40°C to +85°C (Industrial) |

| A5191HRTPG-XTD | 28-pin PLCC<br>Green/RoHS compliant | Tube/Tray              | -40°C to +85°C (Industrial) |

| A5191HRTPG-XTP | 28-pin PLCC<br>Green/RoHS compliant | Tape & Reel            | -40°C to +85°C (Industrial) |

### **6.0 Electrical Specifications**

Table 4: Absolute Maximums

| Symbol            | Parameter              | Min. | Max.                     | Units |

|-------------------|------------------------|------|--------------------------|-------|

| T <sub>A</sub>    | Ambient                | -40  | +85                      | °C    |

| Ts                | Storage temperature    | -55  | 150                      | °C    |

| $V_{DD}$          | Supply voltage         | -0.3 | 6.0                      | V     |

| $V_{IN}, V_{OUT}$ | DC input, output       | -0.3 | VDD + 0.3                | V     |

| TL                | Re-flow solder profile |      | Per IPC/JEDEC J-STD-020C | °C    |

#### Cautions:

Table 5: DC Characteristics

$V_{DD}$  = 3.0V to 5.5V,  $V_{SS}$  = 0V  $T_A$  = -40°C to +85°C

| Symbol  | Parameter                                                | VDD        | Min.                  | Typ.             | Max.                  | Units |

|---------|----------------------------------------------------------|------------|-----------------------|------------------|-----------------------|-------|

| VIL     | Input voltage, low                                       | 3.0 - 5.5  |                       |                  | 0.3 * V <sub>DD</sub> | V     |

| VIH     | Input voltage                                            | 3.0 - 5.5  | 0.7 * V <sub>DD</sub> |                  |                       | V     |

| VOL     | Output voltage, low ( $I_{OL} = 0.67 \text{mA}$ )        | 3.0 - 5.5  |                       |                  | 0.4                   | V     |

| VOH     | Output voltage, high (I <sub>OH</sub> = -0.67mA)         | 3.0 - 5.5  | 2.4                   |                  |                       | V     |

| CIN     | Input capacitance Analog input IRXA Digital input        |            |                       | 2.9<br>25<br>3.5 |                       | pF    |

| IIL/IH  | Input leakage current                                    |            |                       |                  | ± 500                 | nA    |

| IOLL    | Output leakage current                                   |            |                       |                  | ± 10                  | μA    |

| IDO     | Power supply current (RBIAS = 500kΩ, IAREF = 1.235V)     | 3.3<br>5.0 |                       | 330<br>300       | 450<br>600            | μA    |

| IAREF   | Analog reference                                         | 3.3<br>5.0 | 1.2                   | 1.235<br>2.5     | 2.6                   | V     |

| ICDREF* | Carrier detect reference (IAREF – 0.08V)                 |            |                       | 1.15             |                       | V     |

| OCBIAS  | Comparator bias current (RBIAS = 500 kΩ, IAREF = 1.235V) |            |                       | 2.5              |                       | μA    |

<sup>\*</sup>The HART specification requires carrier detect (OCD) to be active between 80 and 120 mVp-p. Setting ICDREF at IAREF - 0.08 VDC will set the carrier detect to a nominal 100 mVp-p.

<sup>1.</sup> CMOS devices are damaged by high-energy electrostatic discharge. Devices must be stored in conductive foam or with all pins shunted. Precautions should be taken to avoid application of voltages higher than the maximum rating. Stresses above absolute maximum ratings may result in damage to the device.

<sup>2.</sup> Remove power before insertion or removal of this device.

Table 6: AC Characteristics

$V_{DD}$  = 3.0V to 5.5V,  $V_{SS}$  = 0V,  $T_A$  = -40°C to +85°C

| Pin Name | Description                                                                                                                    | Min.         | Тур.                            | Max.                 | Units                           |

|----------|--------------------------------------------------------------------------------------------------------------------------------|--------------|---------------------------------|----------------------|---------------------------------|

| IRXA     | Receive analog input Leakage current Frequency – mark (logic 1) Frequency – space (logic 0)                                    | 1190<br>2180 | 1200<br>2200                    | ±150<br>1210<br>2220 | nA<br>Hz<br>Hz                  |

| ORXAF    | Output of the high-pass filter<br>Slew rate<br>Gain bandwidth (GBW)<br>Voltage range                                           | 150<br>0.15  | 0.025                           | VDD – 0.15           | V/µs<br>kHz<br>V/µs             |

| IRXAC    | Carrier detect and receive filter input<br>Leakage current                                                                     |              |                                 | ±500                 | nA                              |

| ОТХА     | Modulator output Frequency – mark (logic 1) Frequency – mark (logic 0) Amplitude (IAREF 1.235V) Slope Loading (IAREF = 1.235V) | 30           | 1196.9<br>2194.3<br>500<br>2.79 |                      | Hz<br>Hz<br>mVDD<br>mV/μs<br>kΩ |

| ORXD     | Receive digital output Rise/fall time                                                                                          | 20           |                                 |                      | ns                              |

| OCD      | Carrier detect output Rise/fall time                                                                                           | 20           |                                 |                      | ns                              |

The modular output frequencies are proportional to the input clock frequency (460.8kHz).

Table 7: Modem Characteristics  $V_{DD}$  = 3.0V to 5.5V,  $V_{SS}$  = 0V,  $T_A$  = -40°C to +85°C

| Parameter                                           | Min. | Тур. | Max. | Units      |

|-----------------------------------------------------|------|------|------|------------|

| Demodulator jitter                                  |      |      |      |            |

| Conditions                                          |      |      | 12   | % of 1 bit |

| 1. Input frequencies at 1200Hz ±10Hz, 2200Hz ± 20Hz |      |      |      |            |

| 2. Clock frequency of 460.8kHz ± 0.1%               |      |      |      |            |

| 3. Input (HLXA) asymmetry, 0                        |      |      |      |            |

# Table 8: Ceramic Resonator - External Clock Specifications $V_{\text{DD}}$ = 3.0V to 5.5V, $V_{\text{SS}}$ = 0V, $T_{\text{A}}$ = -40°C to +85°C

| Parameter       | Min.  | Тур.      | Max.  | Units |

|-----------------|-------|-----------|-------|-------|

| Resonator       |       |           |       |       |

| Tolerance       |       |           | 1.0   | %     |

| Frequency       | 460.8 |           |       | kHz   |

| External        |       |           |       |       |

| Clock frequency | 456.2 | 460.8     |       | kHz   |

| Duty cycle      | 40    | 50        | 465.4 | %     |

| Amplitude       |       | VOH - VOL | 60    | V     |

## 7.0 Mechanical Specifications

Figure 12: 32 Lead LQFP

### 8.0 Revision History

| Revision | Date       | Modification                            |

|----------|------------|-----------------------------------------|

| 2        | March 2005 |                                         |

| 3        | May 2008   | Update to new ON Semiconductor template |

ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada

Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910 Janan Customer Focus Center

Japan Customer Focus Center Phone: 81-3-5773-3850 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative