# 13-Bit Monolithic A/D Converter

AD7550

**FEATURES**

Resolution: 13 Bits, 2's Complement

Relative Accuracy: ±1/2 LSB "Quad Slope" Precision Gain Drift: 1ppm/°C Offset Drift: 1ppm/°C

Microprocessor Compatible Ratiometric Overrange Flag **Very Low Power Dissipation** TTL/CMOS Compatible **CMOS Monolithic Construction**

#### GENERAL DESCRIPTION

The AD7550 is a 13-bit (2's complement) monolithic CMOS analog-to-digital converter on a 118 x 125 mil die packaged in a 40-pin ceramic DIP. Outstanding accuracy and stability (1ppm/°C) is obtained due to its revolutionary integrating technique, called "Quad Slope" (Analog Devices patent No. 3872466). This conversion consists of four slopes of integration as opposed to the traditional dual slope and provides much higher precision.

The AD7550 parallel output data lines have three-state logic and are microprocessor compatible through the use of two enable lines which control the lower eight LSB's (low byte enable) and the five MBS's (high byte enable). An overrange flag is also available which together with the BUSY and BUSY flags can be interrogated through the STATUS ENABLE providing easy microprocessor interface.

The AD7550 conversion time is about 40ms with a 1MHz clock. Clock can be externally controlled or internally generated by simply connecting a capacitor to the clock pin. A positive start pulse can be self-generated by having a capacitor on the start pin or can be externally applied.

#### PACKAGE IDENTIFICATION<sup>1</sup>

Suffix "D" - Ceramic DIP (D40A)

1 See Section 19 for package outline information.

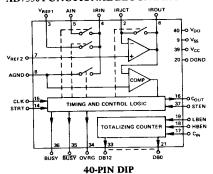

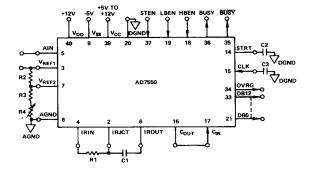

#### AD7550 FUNCTIONAL BLOCK DIAGRAM

For most applications, the AD7550 needs only three resistors, one capacitor, and a reference voltage since the integrating amplifier, comparator, switches and digital logic are all on the CMOS chip.

A wide range of power supply voltages (±5V to ±12V) with minuscule current requirements make the AD7550 ideal for low power and/or battery operated applications. Selection of the logic (V<sub>CC</sub>) supply voltage (+5V to V<sub>DD</sub>) provides direct TTL or CMOS interface on the digital input/output

The AD7550 uses a high density CMOS process featuring double layer metal and silicon nitride passivation to ensure high reliability and long-term stability.

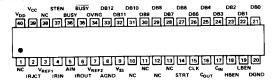

#### PIN CONFIGURATION

TOP VIEW

ANALOG-TO-DIGITAL CONVERTERS VOL. 1, 10-119

## **SPECIFICATIONS** (V<sub>DD</sub> = +12V, V<sub>SS</sub> = -5V, V<sub>CC</sub> = +5V, V<sub>REF</sub> = +4.25V unless otherwise noted)<sup>1</sup>

| PARAMETER                                                                                                                          | TA = +25°C                                                                                                                                 | OVER SPECIFIED TEMPERATURE RANGE                  | TEST CONDITIONS                                                                                                                                                                                                   |

|------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ACCURACY Resolution Relative Accuracy Gain Error Gain Error Drift Offset Error Offset Error Drift                                  | ±1LSB max<br>±1LSB max<br>1ppm/°C typ<br>±0.5LSB max<br>1ppm/°C typ                                                                        | 13 Bits 2's Comp min<br>±1 LSB max                | $f_{CLK} = 500 \text{kHz}, R_1 = 1 \text{M}\Omega,$<br>$C_1 = 0.01 \mu\text{F}, \text{IRJCT Voltage}$<br>Adjusted to $\frac{\text{VREF1}}{2} \pm 0.6\%$                                                           |

| ANALOG INPUTS  AIN Input Resistance <sup>2</sup> V <sub>REF1</sub> Input Resistance <sup>2</sup> V <sub>REF2</sub> Leakage Current | R1MΩ min<br>R1MΩ min<br>10pA typ                                                                                                           |                                                   |                                                                                                                                                                                                                   |

| DIGITAL INPUTS CIN, LBEN, HBEN, STEN VINL VINH VINL VINH VINH VINL VINH VINL                                                       | +0.8V max<br>+2.4V min<br>+1.2V max<br>+10.8V min<br>5nA typ                                                                               | +0.8V max<br>+2.4V min<br>+1.2V max<br>+10.8V min | V <sub>CC</sub> = +5V<br>V <sub>CC</sub> = +12V                                                                                                                                                                   |

| START VINL VINH INL INH                                                                                                            | +0.8V max<br>+3.0V min<br>-1µA typ<br>+150µA typ                                                                                           | +0.8V max<br>+3.0V min                            | $V_{CC}$ = +5V to $V_{DD}$<br>$V_{CC}$ = +5V to $V_{DD}$ , BUSY = Low<br>$V_{CC}$ = +5V to $V_{DD}$ , BUSY = High                                                                                                 |

| CLOCK VINL VINH VINH VINL VINH INH INH                                                                                             | +0.8V max<br>+3V min<br>+1.2V max<br>+10.8V min<br>-100µA typ<br>+100µA typ                                                                | +0.8V max<br>+3V min<br>+1.2V max<br>+10.8V min   | $V_{CC} = +5V$ $V_{CC} = +12V$ $V_{IN} = V_{INL}; V_{CC} = +5V \text{ to } +12V$ $V_{IN} = V_{INH}; V_{CC} = +5V \text{ to } +12V$                                                                                |

| DIGITAL OUTPUTS  VOUTL VOUTH VOUTL VOUTH Capacitance (Floating State)                                                              | +0.5V max<br>+2.4V min<br>+1.2V max<br>+10.8V min<br>5pF typ                                                                               | +0.8V max<br>+2.4V min<br>+1.2V max<br>+10.8V min | V <sub>CC</sub> = +5V, I <sub>SINK</sub> = 1.6mA<br>V <sub>CC</sub> = +5V, I <sub>SOURCE</sub> = 40µA<br>V <sub>CC</sub> = +12V, I <sub>SINK</sub> = 1.6mA<br>V <sub>CC</sub> = +12V, I <sub>SOURCE</sub> = 0.6mA |

| (OVRG, BUSY, BUSY,<br>and DB0-DB12<br>I <sub>LKG</sub> (Floating State)<br>(OVRG, BUSY, BUSY,<br>and DB0-DB12)                     | ±5nA typ                                                                                                                                   |                                                   | $V_{CC}$ = +5V to +12V<br>$V_{OUT}$ = 0V and $V_{CC}$                                                                                                                                                             |

| DYNAMIC PERFORMANCE  Conversion Time                                                                                               | 90ms typ                                                                                                                                   |                                                   | V <sub>IN(CLK)</sub> = 0 to +3V,<br>f <sub>CLK</sub> = 500kHz<br>V <sub>IN(CLK)</sub> = 0 to +3V,<br>f <sub>CLK</sub> = 1MHz                                                                                      |

| STEN, HBEN, LBEN<br>Propagation<br>Delay t <sub>ON</sub> , t <sub>OFF</sub>                                                        | 250ns typ, 500ns max                                                                                                                       |                                                   | V <sub>IN</sub> (STEN, HBEN, LBEN)<br>0 to +3V                                                                                                                                                                    |

| External STRT Pulse Duration                                                                                                       | 800ns min                                                                                                                                  |                                                   | $V_{IN(STRT)} = 0 \text{ to } +3V$                                                                                                                                                                                |

| POWER SUPPLIES  V <sub>DD</sub> Range V <sub>SS</sub> Range V <sub>CC</sub> Range l'DD l <sub>SS</sub> l <sub>CC</sub>             | +10V min, +12V max<br>-5V min, -12V max<br>+5V min, V <sub>DD</sub> max<br>0.6mA typ, 2mA max<br>0.3mA typ, 2mA max<br>0.06mA typ, 2mA max |                                                   | f <sub>CLK</sub> = 1MHz                                                                                                                                                                                           |

NOTES

#### VOL. I, 10-120 ANALOG-TO-DIGITAL CONVERTERS

$<sup>^{1}</sup>$  Full Scale Voltage =  $\pm V_{REF1} \div$  2.125. For  $V_{REF1}$  = +4.25V, FS voltage is  $\pm 2.000V_{\odot}$

<sup>&</sup>lt;sup>3</sup> The equivalent input circuit is the integrator resistor R<sub>1</sub> (1MΩ min, 10MΩ max) in series with a voltage source  $\frac{V_{REF1}}{2}$ , (see Figure 1). Specifications subject to change without notice.

#### ORDERING INFORMATION

| Model    | Temperature Range | Package |

|----------|-------------------|---------|

| AD7550BD | -25°C to +85°C    | Ceramic |

#### CAUTION:

- The digital control inputs are zener protected; however, permanent damage may occur on unconnected units under high energy electrostatic fields. Keep unused units in conductive foam at all times. Prior to pulling the devices from the conductive foam, ground the foam to deplete any accumulated charge.

- 2.  $V_{CC}$  should never exceed  $V_{DD}$  by more than 0.4V, especially during power ON or OFF sequencing.

| ABSOLUTE MAXIMUM RATINGS                                                                |

|-----------------------------------------------------------------------------------------|

| V <sub>DD</sub> to AGND                                                                 |

| V <sub>DD</sub> to DGND                                                                 |

| V <sub>SS</sub> to AGND                                                                 |

| V <sub>SS</sub> to DGND                                                                 |

| AGND to DGND                                                                            |

| V <sub>CC</sub> to DGND                                                                 |

| V <sub>REF1</sub> V <sub>SS</sub> , V <sub>DD</sub>                                     |

| V <sub>REF2</sub> AGND, V <sub>DD</sub>                                                 |

| AIN                                                                                     |

| IRIN                                                                                    |

| IRJCTAGND, V <sub>DD</sub>                                                              |

| IROUT V <sub>SS</sub> , V <sub>DD</sub>                                                 |

| Digital Input Voltage                                                                   |

| HBEN, LBEN, STEN, $C_{1N}$ DGND, (DGND +27V)                                            |

| CLK, STARTDGND, V <sub>DD</sub>                                                         |

| Digital Output Voltage                                                                  |

| DB0-DB12, OVRG, BUSY, $\overline{\text{BUSY}}$ , $C_{\text{OUT}}$ DGND, $V_{\text{CC}}$ |

| Power Dissipation (Package)                                                             |

| Up to +50°C                                                                             |

| Derates above +50°C by                                                                  |

| Storage Temperature65°C to +150°C                                                       |

Operating Temperature. . . . . . . . . . . . . . . . -25°C to +85°C

ANALOG-TO-DIGITAL CONVERTERS VOL. I, 10-121

#### PIN FUNCTION DESCRIPTION PIN MNEMONIC DESCRIPTION 1 NC No Connection 2 IRJCT IntegratoR JunCTion. Summing junction (negative input) of integrating amplifier. 3 $V_{REF1}$ Voltage REFerence Input 4 IRIN IntegratoR INput. External integrator input R is connected between IRJCT and IRIN. 5 AIN Analog INput. Unknown analog input voltage to be measured. Fullscale AIN equals V<sub>REF</sub>/2.125. 6 IROUT IntegratoR OUTput. External integrating capacitor C1 is connected between IROUT and IRJCT. 7 VREF2 Voltage REFerence ÷ 2 Input 8 AGND Analog GrouND 9 $v_{ss}$ Negative Supply (-5V to -12V) 10 NC No Connection 11 NC No Connection 12 NC No Connection 13 NC No Connection STRT 14 STaRT Conversion. When STRT goes to a Logic "1," the AD7550's digital logic is set up and BUSY is latched "high." When STRT returns "low," conversion begins in synchronization with CLK. Reinitiating STRT during conversion causes a conversion restart. STRT can be driven from an external logic source or can be programmed for continuous conversion by connecting an external capacitor between STRT and DGND. An externally applied STRT command must be a positive pulse of at least 800 nanoseconds to ensure proper set-up of the AD7550 logic. 15 CLK CLock Input. The CLK can be driven from external logic, or can be programmed for internal oscillation by connecting an external capacitor between CLK and DGND. 16 COUT Count OUT provides a number (N) of gated clock pulses given by: $N = \left[ \frac{AIN}{V_{REF1}} \quad 2.125 + 1 \right] \quad 4096$ 17 $C_{IN}$ Count IN is the input to the output counter. 2's complement binary data appears on the DBO through DB12 output lines (if the HBEN and LBEN enable lines are "high") if COUT is con-18 HBEN High Byte ENable is the three-state logic enable input for the DB8-DB12 data outputs. When HBEN is low, the DB8-DB12 outputs are floating. When HBEN is "high," digital data appears on the data lines. 19 LBEN Low Byte ENable is the three-state logic enable for DB0-DB7. When LBEN is "low," DB0-DB7 are floating. When "high," digital data appears on the data lines. 20 DGND Digital GrouND is the ground return for all digital logic and the comparator. 21 DBO Data Bit 0 (least significant bit) 22 DR1 23 DB2 24 DB3 25 DB4 26 DB5 27 DB6 CODE: 2's Complement 28' DB7 29 DB8 30 DB9 31 **DB10** 32 DB11 33 DB12 Data Bit 12 (most significant bit) OVRG OVerRange indicates a Logic "1" if AIN exceeds plus or minus full scale by at least 1/2 LSB. 34 OVRG is a three-state output and floats until STEN is addressed with a Logic "1". 35 BUSY Not BUSY. BUSY indicates whether conversion is complete or in progress. BUSY is a three-

state output which floats until STEN is addressed with a Logic "1." When addressed, BUSY will indicate either a "1" (conversion complete) or a "0" (conversion in progress). 36 BUSY BUSY indicates conversion status. BUSY is a three-state output which floats until STEN is addressed with a Logic "1." When addressed, BUSY indicates a "0" (conversion complete) or a "1" (conversion in progress). 37 STEN STatus ENable is the three-state control input for BUSY, BUSY, and OVRG.

38 NC

39 Logic Supply. Digital inputs and outputs are TTL compatible if V<sub>CC</sub> = +5V, CMOS compatible  $v_{cc}$ for  $V_{CC} = +10V$  to  $V_{DD}$ .

$V_{DD}$ Positive Supply +10V to +12V.

VOL. I, 10-122 ANALOG-TO-DIGITAL CONVERTERS

#### PRINCIPLES OF OPERATION

#### BASIC OPERATION

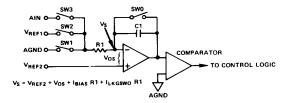

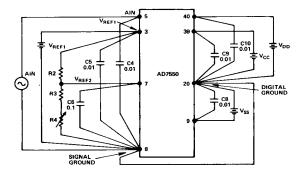

The essence of the quad slope technique is best explained through Figures 1 and 2.

Figure 1. Quad Slope Integrator Circuit

The inputs AGND (analog ground),  $V_{REF1}$  and AlN (analog input) are applied in sequence to an integrator (Figure 1), creating four slopes (phases 1 through 4, Figure 2) at the integrator output. Voltage  $V_{\rm S}$  is ideally equal to  $\frac{V_{REF1}}{2}$ , but if not, will create an error count "n" that will be minimized by the "quad-slope" conversion process.  $V_{REF1}$  and  $V_{REF2}$  must be positive voltages.

The equivalent integrator input voltages and their integration times are shown in Table I.

TABLE I.

INTEGRATOR EQUIVALENT INPUT VOLTAGES

AND INTEGRATION TIMES

| Phase | Input Voltage                     | Integration Time                  |

|-------|-----------------------------------|-----------------------------------|

| 1     | AGND-V <sub>S</sub>               | t <sub>1</sub> = K <sub>1</sub> t |

| 2     | V <sub>REF1</sub> -V <sub>S</sub> | $t_2 = (K_1 + n)t$                |

| 3     | AIN-V <sub>S</sub>                | $t_3 = (2K_1 - n)t$               |

| 4     | V <sub>REF1</sub> -V <sub>S</sub> | $t_4 = (K_3 - 2K_1 + n - 2N)t$    |

NOTE: Ideally VS = VREF2 = 1/2 VREF1

where:

t = The CLK period

n = System error count

$K_1 = A$  fixed count equal to 4352 counts

$K_2 = A$  fixed count equal to 17408 counts ( $K_2 = 4K_1$ )

$K_3 = A$  fixed count equal to 25600 counts

N = Digital output count corresponding to the analog input voltage, AIN

#### PHASE 0

After the start pulse is applied, switch SW2 is closed (all other switches open) and the integrator output is ramped to comparator zero crossing. Phase 0 can be considered the reset phase of the converter, and always has a duration  $t_0 = R_1C_1$  (integrator time constant). Upon zero crossing, counters  $K_1$  and  $K_2$  are started, switch SW2 is opened and SW1 is closed.

#### PHASE :

Phase 1 integrates (AGND  $-V_S$ ) for a fixed period of time (by counter  $K_1$ ) equal to  $t_1 = K_1t$ . At the end of phase 1, switch SW1 is opened and SW2 is closed.

#### PHASE 2

The integrator input is switched to  $(V_{REF1} - V_S)$  and the output ramps down until zero crossing is achieved. The integration time  $t_2 = (K_1 + n)t$  includes the error count "n" due to offsets, etc. At the end of phase 2, switch SW2 is opened, SW3 is closed, and a third counter  $(K_3)$  is started.

#### PHASE 3

Phase 3 integrates the analog input (AIN - V<sub>S</sub>) until counter K<sub>2</sub> counts  $4K_1t$ . At this time SW3 is opened and SW2 is closed again.

#### PHASE 4

Phase 4 integrates (V<sub>REF1</sub> - V<sub>S</sub>) and the comparator output ramps down until zero crossing once again is achieved. Since the comparator always approaches zero crossing from the same slope, propagation delay is constant and hysteresis effect is eliminated.

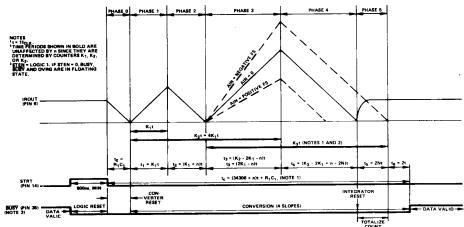

Figure 2. Quad Slope Timing Diagram

ANALOG-TO-DIGITAL CONVERTERS VOL. I, 10-123

The time t5 between the phase 4 zero crossing and the termination of counter K3 is considered equal to 2N counts. N, the number of counts at the C<sub>OUT</sub> terminal, is obtained by a divide-by-two counter stage. This reduces "jitter" effect. Barring third (and higher) order effects, it can be proven that:

$$N = \left(\frac{AIN}{V_{REF1}} - 1\right) \cdot 2K_1 + \frac{K_3}{2} + \left(\frac{AIN}{V_{REF1}} - 1\right) \cdot \left[\frac{AGND}{V_{REF1}} (1 + 2\alpha) - \alpha^2\right] \cdot 2K_1$$

ideal transfer function error term

where:

$$\alpha = \frac{2V_S - V_{REF1}}{V_{REF1}}$$

The ideal case assumes:

AGND = 0V

$$V_S = \frac{V_{REF1}}{2}$$

, therefore  $\alpha = 0$

Then (EQN 1) simplifies to:

$$N = \frac{AIN}{V_{REF1}} \cdot 8704 + 4096$$

(EQN 2)

$$N = \frac{AIN}{V_{FS}} \cdot 4096 + 4096$$

(EQN 3)

where:

$$V_{FS}$$

= full scale input voltage =  $\frac{V_{REF1}}{2.125}$

The parallel output (DB0-DB12) of the AD7550 represents the number N in binary 2's complement coding when the  $C_{OUT}$  pin is connected to the  $C_{IN}$  pin (see Table II).

TABLE II

OUTPUT CODING (Bipolar 2's Complement)

| Analog Input<br>(Note 1)   | N<br>(Note 2) |      | llel Digital Output<br>(Note 3) |                |

|----------------------------|---------------|------|---------------------------------|----------------|

|                            |               | OVRG | DB12                            | DBO            |

| +Overrange                 | -             | 1    | 0                               | 111111111111   |

| +VFS (1-2 <sup>-12</sup> ) | 8191          | 0    | 0                               | 111111111111   |

| +VFS (2 <sup>-12</sup> )   | 4097          | 0    | 0                               | 0000 0000 0001 |

| 0                          | 4096          | 0    | 0                               | 0000 0000 0000 |

| -VFS (2 <sup>-12</sup> )   | 4095          | 0    | 1                               | 111111111111   |

| -VFS                       | 0             | 0    | 1                               | 0000 0000 0000 |

| -Overrange                 | -             | 1    | 1                               | 0000 0000 0000 |

Notes Vans

$V_{FS} = \frac{1}{2.125}$

2 N = number of counts at COUT pin

3 COUT strapped to CIN; LBEN, HBEN and STEN = Logic 1

#### **ERROR ANALYSIS**

Equation 1 shows that only  $\alpha$  and AGND generate error terms. Their impact can be analyzed as follows:

Case 1: AGND =

$$0, \alpha \neq 0$$

Error sources such as capacitor-leakage (I<sub>L</sub>) and op amp offset (e) cause  $\alpha$  to be different from zero.

#### VOL. I, 10-124 ANALOG-TO-DIGITAL CONVERTERS

Under this condition,

$$\alpha = \frac{2 (e + I_L R_1)}{V_{REF1}}$$

where  $I_L R_{\rm I}$  is the equivalent error voltage generated by leakage  $I_L$  .

The evaluation of this error term is best demonstrated through the following example:

Assume:

e = 5mV,

$$I_L$$

= 5nA,  $R_1$  = 1M $\Omega$  and  $V_{REF1}$  = 4.25V.

Then:

$$\alpha = 4.7 \times 10^{-3}$$

and:

$$N = \left[\frac{A1N}{V_{REF1}} - 1\right] \times 8704 + 12800 - \left[\frac{A1N}{V_{REF1}} - 1\right] \times 22.1 \times 10^{-6} \times 8704$$

error term N<sub>E</sub>

Therefore, the error count Ne is as follows:

For AIN =

$$-V_{FS}$$

:  $N_{\epsilon}$  = 0.28 counts = 0.28LSB

AIN = 0:  $N_{\epsilon}$  = 0.19 counts = 0.19LSB

AIN =  $+V_{FS}$ :  $N_{\epsilon}$  = 0.09 counts = 0.09LSB

The above example shows the strong reduction of the circuit errors because of the  $\alpha^2$  term in (EQN 1). Another consequence of this effect is that  $N_{\epsilon}$  is always positive, regardless of the polarity of the circuit errors.

Case 2: AGND

$$\neq 0$$

,  $\alpha = 0$

When AGND is different from the signal ground, then this error will come through on a first-order basis. Indeed:

$$N = \begin{bmatrix} AIN \\ V_{REF1} \end{bmatrix} - 1 \cdot 8704 + 12800 + \begin{bmatrix} AIN \\ V_{REF1} \end{bmatrix} - 1 \cdot \frac{AGND}{V_{REF1}}$$

error term N<sub>E</sub>

The following example demonstrates the impact of AGND.

Let AGND =

$$1 \text{mV}$$

and  $V_{REF1} = 4.25 \text{V}$ .

For AIN =

$$-V_{FS}$$

, then  $N_{\epsilon}$  = 3.01 counts

AIN = 0, then  $N_{\epsilon}$  = 2.05 counts

AIN = +  $V_{FS}$ , then  $N_{\epsilon}$  = 1.08 counts

Therefore, ground loops should be minimized because a  $330\mu V$  difference between AGND and signal ground will cause 1 count (1 LSB) of error when the analog input is at minus full scale. An optimized ground system is shown in Figure 7.

#### **OPERATING GUIDELINES**

The following steps, in conjunction with Figure 3, explain the calculations of the component values required for proper operation.

#### 1. DETERMINATION OF VREF1

When the full scale voltage requirement (VFS) has been ascertained, the reference voltage can be calculated by:

$$V_{REF1} = 2.125 (V_{FS})$$

V<sub>REF1</sub> must be positive for proper operation.

#### 2. SELECTION OF C3 (INTERNAL CLOCK OPERATION)

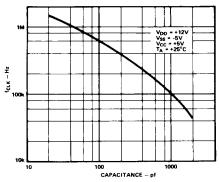

For internal clock operation, connect capacitor  $C_3$  to the clock pin as shown in Figure 3. The clock frequency versus capacitor  $C_3$  is shown in Figure 4.

The clock frequency must be limited to 1.3MHz for proper operation.

### 3. SELECTION OF INTEGRATOR COMPONENTS ( $R_1$ AND $C_1$ )

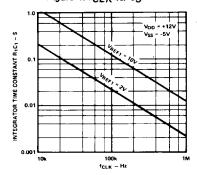

To ensure that the integrator's output doesn't saturate to its bound  $(V_{DD})$  during the phase (3) integration cycle, the integrator time constant  $(R_1C_1)$  should be approximately equal to:

$$\pi = R_1 C_1 = \frac{V_{REF1} (9 \times 10^3)}{f_{CLK} (V_{DD} - 4V)}$$

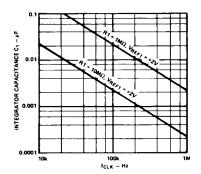

The integrator components  $R_1$  and  $C_1$  can be selected by referring to Figure 5 and/or Figure 6. Figure 5 plots the time constant ( $R_1C_1$ ) versus clock frequency for different reference voltages. Figure 6 is a direct plot of the required  $C_1$  versus  $f_{CLK}$  for  $R_1$  values of  $1M\Omega$  and  $10M\Omega$ .

$R_1$  can be a standard 10% resistor, but must be selected between  $1M\Omega$  to  $10M\Omega.$

The integrating capacitor "C<sub>1</sub>" must be a low leakage, low dielectric absorption type such as teflon, polystyrene or polypropylene. To minimize noise, the outside foil of C<sub>1</sub> must be connected to IR<sub>OUT</sub>.

#### 4. CONVERSION TIME

As shown in Figure 2, the conversion time is independent of the analog input voltage AIN, and is given by:

$$t_{convert} = t_{STRT} + \frac{34306}{f_{CLK}} + R_1C_1$$

where:

t<sub>STRT</sub> = STRT pulse duration R<sub>1</sub>C<sub>1</sub> = Integrator Time Constant f<sub>CLK</sub> = CLK Frequency

For example, if  $V_{EEF1} = 4.25V$ ,  $R_1 = 1M\Omega$ ,  $C_1 = 4,000pF$  and CLK = 1MHz, the conversion time (not including  $t_{STRT}$ , which is normally only microseconds in duration) is approximately 40 milliseconds.

#### 5. EXTERNAL OR AUTO STRT OPERATION

The STRT pin can be driven externally, or with the addition of C2, made to self-start.

The size of C2 determines the length of time from end of conversion until a new conversion is initiated. This is the "data valid" time and is given by:

$$t_{DAV} \approx (1.7 \times 10^6 \Omega) C_2 + 20 \mu s$$

When first applying power to the AD7550, a 0V to  $V_{DD}$  positive pulse (power up restart) is required at the STRT terminal to initiate auto STRT operation.

#### 6. INITIAL CALIBRATION

Trim  $R_4$  (Figure 3) so that pin 2 (IRJCT) equals 1/2  $V_{REF1}$   $\pm 0.6\%$ . When measuring the voltage on IRJCT, apply a Logic "1" to the STRT terminal.

Figure 3. Operation Diagram

ANALOG-TO-DIGITAL CONVERTERS VOL. I, 10-125

Figure 4. fCLK vs. C3

Figure 5. Integrator Time Constant (R<sub>1</sub>C<sub>1</sub>) vs. f<sub>CLK</sub> for Different Reference Voltages

Figure 6. Integrator Capacitance (C<sub>1</sub>) vs. f<sub>CLK</sub> for Different Integrator Resistances (R<sub>1</sub>)

#### APPLICATION HINTS

When operating at f<sub>CLK</sub> greater than 500kHz, the following steps are recommended to minimize errors due to noise coupling (see Figure 7).

- Decouple AIN (pin 5), V<sub>REF1</sub> (pin 3) and V<sub>REF2</sub> (pin 7) through 0.01µF to signal ground.

- 2. Signal ground must be located as close to pin 8 (AGND) as possible.

- 3. Keep the lead lengths of R<sub>1</sub> and C<sub>1</sub> toward pin 2 (IRJCT) as short as possible. In addition, both components should lie over the analog ground plane. If C<sub>1</sub> has an outside foil, connect it to pin 6 (IROUT), not pin 2.

- 4. Hold the data bit enables (HBEN, LBEN) in the 0 state during conversion. This is easily accomplished by tying STEN to the 1 state and driving HBEN and LBEN with BUSY. This prevents the DB0 through DB12 outputs from coupling noise into the integrator during the phase 1-4 active integration periods.

Figure 7. Ground System

#### VOL. I, 10-126 ANALOG-TO-DIGITAL CONVERTERS