Rev: 032609

# DS34S101, DS34S102, DS34S104, DS34S108 Single/Dual/Quad/Octal TDM-over-Packet Chip

# **General Description**

**Features**

These IETF PWE3 SAToP/CESoPSN/TDMoIP/HDLC compliant devices allow up to eight E1, T1 or serial streams or one high-speed E3, T3, STS-1 or serial stream to be transported transparently over IP, MPLS or Ethernet networks. Jitter and wander of recovered clocks conform to G.823/G.824, G.8261, and TDM specifications. TDM data is transported in up to 64 individually configurable bundles. All standards-based TDM-over-packet mapping methods are supported except AAL2. Frame-based serial HDLC data flows are also supported. The high level of integration available with the DS34S10x devices minimizes cost, board space, and time to market.

# **Applications**

TDM Circuit Extension Over PSN

- Leased-Line Services Over PSN

- TDM Over GPON/EPON

- TDM Over Cable

- o TDM Over Wireless

Cellular Backhaul Over PSN Multiservice Over Unified PSN HDLC-Based Traffic Transport Over PSN

- Transport of E1, T1, E3, T3 or STS-1 TDM or CBR Serial Signals Over Packet Networks

- Full Support for These Mapping Methods: SATOP, CESOPSN, TDMoIP (AAL1), HDLC, Unstructured, Structured, Structured with CAS

- Adaptive Clock Recovery, Common Clock, External Clock and Loopback Timing Modes

- On-Chip TDM Clock Recovery Machines, One Per Port, Independently Configurable

- Clock Recovery Algorithm Handles Network PDV, Packet Loss, Constant Delay Changes, Frequency Changes and Other Impairments

- ♦ 64 Independent Bundles/Connections

- Multiprotocol Encapsulation Supports IPv4, IPv6, UDP, RTP, L2TPv3, MPLS, Metro Ethernet

- VLAN Support According to 802.1p and 802.1Q

- ◆ 10/100 Ethernet MAC Supports MII/RMII/SSMII

- ♦ Selectable 32-Bit, 16-Bit or SPI Processor Bus

- Operates from Only Two Clock Signals, One for Clock Recovery and One for Packet Processing

- Glueless SDRAM Buffer Management

- ♦ Low-Power 1.8V Core, 3.3V I/O

See detailed feature list in Section 5.

# Functional Diagram

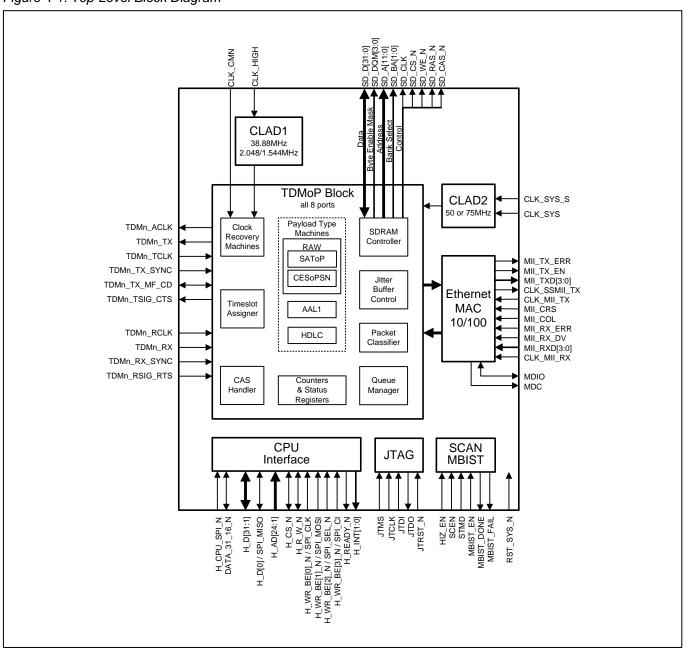

# DS34S108 Circuit Emulation Engine MAC SDRAM Clock Inputs Interface

# Ordering Information

| PART               | PORTS | TEMP RANGE     | PIN-PACKAGE |

|--------------------|-------|----------------|-------------|

| <b>DS34S101</b> GN | 1     | -40°C to +85°C | 256 TECSBGA |

| DS34S101GN+        | 1     | -40°C to +85°C | 256 TECSBGA |

| <b>DS34S102</b> GN | 2     | -40°C to +85°C | 256 TECSBGA |

| DS34S102GN+        | 2     | -40°C to +85°C | 256 TECSBGA |

| <b>DS34S104</b> GN | 4     | -40°C to +85°C | 256 TECSBGA |

| DS34S104GN+        | 4     | -40°C to +85°C | 256 TECSBGA |

| <b>DS34S108</b> GN | 8     | -40°C to +85°C | 484 HSBGA   |

| DS34S108GN+        | 8     | -40°C to +85°C | 484 HSBGA   |

+Denotes lead(Pb)-free/RoHS-compliant package (explanation).

NIXIN

Maxim Integrated Products

1

# 1 Applicable Standards

Table 1-1. Applicable Standards

| SPECIFICATION | SPECIFICATION TITLE                                                                                                        |  |  |

|---------------|----------------------------------------------------------------------------------------------------------------------------|--|--|

| IEEE          |                                                                                                                            |  |  |

| IEEE 802.3    | Carrier Sense Multiple Access with Collision Detection (CSMA/CD) Access Method and Physical Layer Specifications (2005)    |  |  |

| IEEE 1149.1   | Standard Test Access Port and Boundary-Scan Architecture, 1990                                                             |  |  |

| IETF          |                                                                                                                            |  |  |

| RFC 4553      | Structure-Agnostic Time Division Multiplexing (TDM) over Packet (SAToP) (06/2006)                                          |  |  |

| RFC 4618      | Encapsulation Methods for Transport of PPP/High-Level Data Link Control (HDLC) over MPLS Networks (09/2006)                |  |  |

| RFC 5086      | Structure-Aware Time Division Multiplexed (TDM) Circuit Emulation Service over Packet Switched Network (CESoPSN) (12/2007) |  |  |

| RFC 5087      | Time Division Multiplexing over IP (TDMoIP) (12/2007)                                                                      |  |  |

| ITU-T         |                                                                                                                            |  |  |

| G.823         | The Control of Jitter and Wander within Digital Networks which are Based on the 2048kbps Hierarchy (03/2000)               |  |  |

| G.824         | The Control of Jitter and Wander within Digital Networks which are Based on the 1544kbps Hierarchy (03/2000)               |  |  |

| G.8261/Y.1361 | Timing and Synchronization Aspects in Packet Networks (05/2006)                                                            |  |  |

| 1.363.1       | B-ISDN ATM Adaptation Layer Specification: Type 1 AAL (08/1996)                                                            |  |  |

| 1.363.2       | B-ISDN ATM Adaptation Layer Specification: Type 2 AAL (11/2000)                                                            |  |  |

| 1.366.2       | AAL Type 2 Service Specific Convergence Sublayer for Narrow-Band Services (11/2000)                                        |  |  |

| O.151         | Error Performance Measuring Equipment Operating at the Primary Rate and Above (1992)                                       |  |  |

| O.161         | In-Service Code Violation Monitors for Digital Systems (1993)                                                              |  |  |

| Y.1413        | TDM-MPLS Network Interworking – User Plane Interworking (03/2004)                                                          |  |  |

| Y.1414        | Voice Services–MPLS Network Interworking (07/2004)                                                                         |  |  |

| Y.1452        | Voice Trunking over IP Networks (03/2006)                                                                                  |  |  |

| Y.1453        | TDM-IP Interworking – User Plane Networking (03/2006)                                                                      |  |  |

| MEF           |                                                                                                                            |  |  |

| MEF 8         | Implementation Agreement for the Emulation of PDH Circuits over Metro Ethernet Networks (10/2004)                          |  |  |

| MFA           |                                                                                                                            |  |  |

| MFA 4.0       | TDM Transport over MPLS Using AAL1 (06/2003)                                                                               |  |  |

| MFA 5.0.0     | I.366.2 Voice Trunking Format over MPLS Implementation Agreement (08/2003)                                                 |  |  |

| MFA 8.0.0     | Emulation of TDM Circuits over MPLS Using Raw Encapsulation – Implementation Agreement (11/2004)                           |  |  |

Rev: 032609 2 of 13

DS34S101, DS34S102, DS34S104, DS34S108

# 2 Detailed Description

The DS34S108 is an 8-port TDM-over-Packet (TDMoP) IC. The DS34S104, DS34S102 and DS34S101 have the same functionality as the DS34S108, except they have only 4, 2 or 1 ports, respectively. These sophisticated devices can map and demap multiple E1/T1 data streams or a single E3/T3/STS-1 data stream to and from IP, MPLS or Ethernet networks. A built-in MAC supports connectivity to a single 10/100 Mbps PHY over an MII, RMII or SSMII interface. The DS34S10x devices are controlled through a 16 or 32-bit parallel bus interface or a high-speed SPI serial interface.

The TDM-over-Packet (TDMoP) core is the enabling block for circuit emulation and other network applications. It performs transparent transport of legacy TDM traffic over Packet Switched-Networks (PSN). The TDMoP core implements payload mapping methods such as AAL1 for circuit emulation, HDLC method, structure-agnostic SAToP method, and the structure-aware CESoPSN method.

The AAL1 payload-type machine maps and demaps E1, T1, E3, T3, STS-1 and other serial data flows into and out of IP, MPLS or Ethernet packets, according to the methods described in ITU-T Y.1413, Y.1453, MEF 8, MFA 4.1 and IETF RFC 5087 (TDMoIP). It supports E1/T1 structured mode with or without CAS, using a timeslot size of 8 bits, or unstructured mode (carrying serial interfaces, unframed E1/T1 or E3/T3/STS-1 traffic).

The HDLC payload-type machine maps and demaps HDLC dataflows into and out of IP/MPLS packets according to IETF RFC 4618 (excluding clause 5.3 - PPP) and IETF RFC 5087 (TDMoIP). It supports 2-, 7- and 8-bit timeslot resolution (i.e. 16, 56, and 64 kbps respectively), as well as N × 64 kbps bundles (n=1 to 32). Supported applications of this machine include trunking of HDLC-based traffic (such as Frame Relay) implementing Dynamic Bandwidth Allocation over IP/MPLS networks and HDLC-based signaling interpretation (such as ISDN D-channel signaling termination – BRI or PRI, V5.1/2, or GR-303).

The SAToP payload-type machine maps and demaps unframed E1, T1, E3 or T3 data flows into and out of IP, MPLS or Ethernet packets according to ITU-T Y.1413, Y.1453, MEF 8, MFA 8.0.0 and IETF RFC 4553. It supports E1/T1/E3/T3 with no regard for the TDM structure. If TDM structure exists it is ignored, allowing this to be the simplest mapping/demapping method. The size of the payload is programmable for different services. This emulation suits applications where the provider edges have no need to interpret TDM data or to participate in the TDM signaling. The PSN network must have almost no packet loss and very low packet delay variation (PDV) for this method.

The CESoPSN payload-type machine maps and demaps structured E1, T1, E3 or T3 data flows into and out of IP, MPLS or Ethernet packets with static assignment of timeslots inside a bundle according to ITU-T Y.1413, Y.1453, MEF 8, MFA 8.0.0 and the IETF RFC 5086 (CESoPSN). It supports E1/T1/E3/T3 while taking into account the TDM structure. The level of structure must be chosen for proper payload conversion such as the framing type (i.e. frame or multiframe). This method is less sensitive to PSN impairments but lost packets could still cause service interruption.

Rev: 032609 3 of 13

# 3 Application Examples

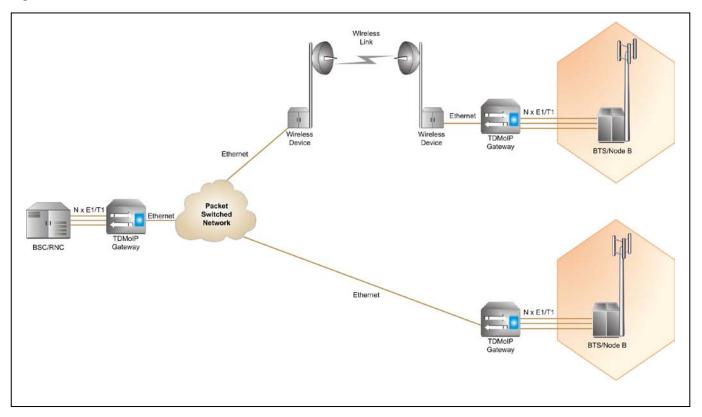

In Figure 3-1, a DS34S10x device is used in each TDMoP gateway to map TDM services into a packet-switched metropolitan network. TDMoP data is carried over various media: fiber, wireless, G/EPON, coax, etc.

Fixed Wireless Connection Wireless Central Office Packet Switched Network G/E PON PSTN TDMoIP ONU with TDMoIP Function LAN Fiber Route TDMoIP E1/T1 LAN

Figure 3-1. TDMoP in a Metropolitan Packet Switched Network

Rev: 032609 4 of 13

Figure 3-2. TDMoP in Cellular Backhaul

## Other Possible Applications

### Point-to-Multipoint TDM Connectivity over IP/Ethernet

The DS34S10x devices support NxDS0 TDMoP connections (known as bundles) with or without CAS (Channel Associated Signaling). There is no need for an external TDM cross-connect, since the packet domain can be used as a virtual cross-connect. Any bundle of timeslots can be directed to another remote location on the packet domain.

### HDLC Transport over IP/MPLS

TDM traffic streams often contain HDLC-based control channels and data traffic. These data streams, when transported over a packet domain, should be treated differently than the time-sensitive TDM payload. DS34S10x devices can terminate HDLC channels in the TDM streams and optionally map them into IP/MPLS/Ethernet for transport. All HDLC-based control protocols (ISDN BRI and PRI, SS7 etc.) and all HDLC data traffic can be managed and transported.

### Using a Packet Backplane for Multiservice Concentrators

A communications device with all the above-mentioned capabilities can use a packet-based backplane instead of the more expensive TDM bus option. This enables a cost-effective and future-proof design of communication platforms with full support for both legacy and next-generation services.

Rev: 032609 5 of 13

# 4 Block Diagram

Figure 4-1. Top-Level Block Diagram

Rev: 032609 6 of 13

### 5 Features

### Global Features

- TDMoP Interfaces

- DS34S101: 1 E1/T1/serial TDM interface

- o DS34S102: 2 E1/T1/serial TDM interfaces

- o DS34S104: 4 E1/T1/serial TDM interfaces

- DS34S108: 8 E1/T1/serial TDM interfaces

- All four devices: optionally 1 high-speed E3/DS3/STS-1 TDM interface

- o All four devices: each interface optionally configurable for serial operation for V.35 and RS530

- Ethernet Interface

- o One 10/100 Mbps port configurable for MII, RMII or SSMII interface format

- Half or full duplex operation

- VLAN support according to 802.1p and 802.1Q including stacked tags

- o Fully compatible with IEEE 802.3 standard

- End-to-end TDM synchronization through the IP/MPLS domain by on-chip, per-port TDM clock recovery

- 64 independent bundles/connections, each with its own:

- o Transmit and receive queues

- o Configurable jitter-buffer depth

- o Connection-level redundancy, with traffic duplication option

- · Packet loss compensation and handling of misordered packets

- Glueless SDRAM interface

- Complies with MPLS-Frame Relay Alliance Implementation Agreements 4.1, 5.1 and 8.0

- Complies with ITU-T standards Y.1413 and Y.1414.

- Complies with Metro Ethernet Forum 3 and 8

- Complies with IETF RFC 4553 (SAToP), RFC 5086 (CESoPSN) and RFC 5087 (TDMoIP)

- IEEE 1146.1 JTAG boundary scan

- 1.8V and 3.3V Operation with 5.0V tolerant I/O

### Clock Synthesizers

- Clocks to operate the TDMoP clock recovery machines can synthesized from a single clock input (10MHz, 19.44MHz, 38.88MHz or 77.76MHz on the CLK\_HIGH pin)

- Clock to operate TDMoP logic and SDRAM interface (50MHz or 75MHz) can be synthesized from a single 25MHz clock on the CLK\_SYS pin

### TDM-over-Packet Block

- Enables transport of TDM services (E1, T1, E3, T3, STS-1) or serial data over packet-switched networks

- SAToP payload-type machine maps/demaps unframed E1/T1/E3/T3/STS-1 or serial data flows to/from IP, MPLS or Ethernet packets according to ITU-T Y.1413, Y.1453, MEF 8, MFA 8.0.0 and IETF RFC 4553.

- CESoPSN payload-type machine maps/demaps structured E1/T1 data flows to/from IP, MPLS or Ethernet packets with static assignment of timeslots inside a bundle according to ITU-T Y.1413, Y.1453, MEF 8, MFA 8.0.0 and IETF RFC 5086.

- AAL1 payload-type machine maps/demaps E1/T1/E3/T3/STS-1 or serial data flows to/from IP, MPLS or Ethernet packets according to ITU-T Y.1413, MEF 8, MFA 4.1 and IETF RFC 5087. For E1/T1 it supports structured mode with/without CAS using 8-bit timeslot resolution, while implementing static timeslot allocation. For E1/T1, E3/T3/STS-1 or serial interface it supports unstructured mode.

- HDLC payload-type machine maps/demaps HDLC-based E1/T1/serial flow to/from IP, MPLS or Ethernet packets. It supports 2-, 7- and 8-bit timeslot resolution (i.e. 16, 56, and 64 kbps respectively), as well as N x 64 kbps bundles. This is useful in applications where HDLC-based signaling interpretation is required (such as ISDN D channel signaling termination, V.51/2, or GR-303), or for trunking packet-based applications (such as Frame Relay), according to IETF RFC 4618.

Rev: 032609 7 of 13

### DS34S101, DS34S102, DS34S104, DS34S108

### TDMoP TDM Interfaces

- Supports single high-speed E3, T3 or STS-1 interface on port 1 or one (DS34S101), two (DS34S102), four (DS34S104) or eight (DS34S108) E1, T1 or serial interfaces

- For single high-speed E3, T3 or STS-1 interface, AAL1 or SAToP payload type is used

- For E1 or T1 interfaces, the following modes are available:

- Unframed E1/T1 pass-through mode (AAL1, SAToP or HDLC payload type)

- Structured fractional E1/T1 support (all payloads)

- Structured with CAS fractional E1/T1 with CAS support (CESoPSN or AAL1 payload type)

- For serial interfaces, the following modes are available:

- Arbitrary continuous bit stream (using AAL1 or SAToP payload type)

- Single-interface high-speed mode on port 1 up to STS-1 rate (51.84 Mbps) using a single bundle/connection.

- Low-speed mode with each interface operating at N x 64 kbps (N = 1 to 63) with an aggregate rate of 18.6Mbps

- o HDLC-based traffic (such as Frame Relay) at N x 64 kbps (N = 1 to 63) with an aggregate rate of 18.6Mbps).

- All serial interface modes are capable of working with a gapped clock.

### **TDMoP Bundles**

- 64 independent bundles, each can be assigned to any TDM interface

- Each bundle carries a data stream from one TDM interface over IP/MPLS/Ethernet PSN from TDMoP source device to TDMoP destination device

- Each bundle may be for N x 64kbps, an entire E1, T1, E3, T3 or STS-1, or an arbitrary serial data stream

- Each bundle is uni-directional (but frequently coupled with opposite-direction bundle for bidirectional communication)

- Multiple bundles can be transported between TDMoP devices

- Multiple bundles can be assigned to the same TDM interface

- Each bundle is independently configured with its own:

- Transmit and receive queues

- Configurable receive-buffer depth

- o Optional connection-level redundancy (SAToP, AAL1, CESoPSN only).

- Each bundle can be assigned to one of the payload-type machines or to the CPU

- For E1/T1 the device provides internal bundle cross-connect functionality, with DS0 resolution

### TDMoP Clock Recovery

- Sophisticated TDM clock recovery machines, one for each TDM interface, allow end-to-end TDM clock synchronization, despite the packet delay variation of the IP/MPLS/Ethernet network

- The following clock recovery modes are supported:

- o Adaptive clock recovery

- Common clock (using RTP)

- o External clock

- o Loopback clock

- The clock recovery machines provide both fast frequency acquisition and highly accurate phase tracking:

- Jitter and wander of the recovered clock are maintained at levels that conform to G.823/G.824 traffic or synchronization interfaces. (For adaptive clock recovery, the recovered clock performance depends on packet network characteristics.)

- Short-term frequency accuracy (1 second) is better than 16 ppb (using OCXO reference), or 100 ppb (using TCXO reference)

8 of 13

- Capture range is ±90 ppm

- o Internal synthesizer frequency resolution of 0.5 ppb

- High resilience to packet loss and misordering, up to 2% without degradation of clock recovery performance

- Robust to sudden significant constant delay changes

Rev: 032609

DS34S101, DS34S102, DS34S104, DS34S108

Automatic transition to holdover when link break is detected

### TDMoP Delay Variation Compensation

- Configurable jitter buffers compensate for delay variation introduce by the IP/MPLS/Ethernet network

- Large maximum jitter buffer depths:

- E1: up to 256 ms

- o T1 unframed: up to 340 ms

- o T1 framed: up to 256 ms

- T1 framed with CAS: up to 192 ms

- o E3: up to 60 ms

- o T3: up to 45 ms

- o STS-1: up to 40 ms.

- Packet reordering is performed for SAToP and CESoPSN bundles within the range of the jitter buffer

- Packet loss is compensated by inserting either a pre-configured conditioning value or the last received value.

### TDMoP CAS Support

- On-chip CAS handler terminates E1/T1 CAS when using AAL1/CESoPSN in structured-with-CAS mode.

- CPU intervention is not required for CAS handling.

# Test and Diagnostics

- IEEE 1149.1 JTAG support

- MBIST (memory built-in self test)

### CPU Interface

- 32 or 16-bit parallel interface or optional SPI serial interface

- Byte write enable pins for single-byte write resolution

- Hardware reset pin

- Software reset supported

- Software access to device ID and silicon revision

- On-chip SDRAM controller provides access to SDRAM for both the chip and the CPU

- CPU can access transmit and receive buffers in SDRAM used for packets to/from the CPU (ARP, SNMP, etc.)

# 6 Overview of Major Operational Modes

Globally, the resources of the device can be committed to either one high-speed E3, T3 or STS-1 TDM stream (high-speed mode) or one or more E1, T1 or serial streams (normal low-speed mode). In high-speed mode, the TDM signal is carried using an unstructured AAL1 or SAToP mapping. High-speed mode is enabled by setting General\_cfg\_reg0.High\_speed=1.

In normal, low-speed mode, each port can be configured for E1, T1 or serial (e.g. V.35) operation. Ports configured for E1 or T1 can be further configured for unframed, framed, or multiframed interface. In addition, each port can be configured to have the transmit and receive directions clocked by independent clocks (two-clock mode) or to have both directions clocked by the transmit clock (one-clock mode). All of this configuration is specified in the per-port Port[n]\_cfg\_reg register.

Rev: 032609 9 of 13

# 7 Pin Descriptions

# 7.1 Short Pin Descriptions

| PIN NAME                  | TYPE        | PIN DESCRIPTION                                                                 |

|---------------------------|-------------|---------------------------------------------------------------------------------|

| TDM Interface             | <u> </u>    | ,                                                                               |

| TDMn_ACLK                 | 0           | TDMoP Recovered Clock Output                                                    |

| TDMn_TCLK                 | lpu         | TDMoP Transmit Clock Input (here transmit means "away from Ethernet MII")       |

| TDMn_TX                   | 0           | TDMoP Transmit Data Output                                                      |

| TDMn_TX_SYNC              | Ipd         | TDMoP Transmit Frame Sync Input                                                 |

| TDMn_TX_MF_CD             | IOpd        | TDMoP Transmit Multiframe Sync Input or Carrier Detect Output                   |

| TDMn_TSIG_CTS             | 0           | TDMoP Transmit Signaling Output or Clear to Send Output                         |

| TDMn_RCLK                 | lpu         | TDMoP Receive Clock Input (here receive means "toward Ethernet MII")            |

| TDMn RX                   | Ipu         | TDMoP Receive Data Input                                                        |

| TDMn_RX_SYNC              | Ipd         | TDMoP Receive Frame/Multiframe Sync Input                                       |

| TDMn_RSIG_RTS             | Ipu         | TDMoP Receive Signaling Input or Request To Send Input                          |

| SDRAM Interface           | 1 .pu       | 12 mon 11000110 digitaling input of 110 quote 10 dona input                     |

| SD_CLK                    | 0           | SDRAM Clock                                                                     |

| SD_D[31:0]                | 10          | SDRAM Data Bus                                                                  |

| SD_D[31.0]<br>SD_DQM[3:0] | 0           | SDRAM Byte Enable Mask                                                          |

| SD_A[11:0]                | 0           | SDRAM Address Bus                                                               |

| SD_A[11:0]<br>SD_BA[1:0]  | 0           | SDRAM Bank Select Outputs                                                       |

| SD_CS_N                   | 0           | SDRAM Chip Select (Active Low)                                                  |

| SD_WE_N                   | 0           | SDRAM Write Enable (Active Low)                                                 |

| SD RAS N                  | 0           | SDRAM Row Address Strobe (Active Low)                                           |

| SD_CAS_N                  | 0           | SDRAM Column Address Strobe (Active Low)                                        |

| <del></del>               |             |                                                                                 |

| Ethernet PHY Interface (  | MII/RMII/SS |                                                                                 |

| CLK_MII_TX                | <u> </u>    | MII Transmit Clock Input                                                        |

| CLK_SSMII_TX              | 0           | SSMII Transmit Clock Output                                                     |

| MII_TXD[3:0]              | 0           | MII Transmit Data Outputs                                                       |

| MII_TX_EN                 | 0           | MII Transmit Enable Output                                                      |

| MII_TX_ERR                | 0           | MII Transmit Error Output                                                       |

| CLK_MII_RX                | !           | MII Receive Clock Input                                                         |

| MII_RXD[3:0]              | l l         | MII Receive Data Inputs                                                         |

| MII_RX_DV                 | !           | MII Receive Data Valid Input                                                    |

| MII_RX_ERR                | l l         | MII Receive Error Input                                                         |

| MII_COL                   | l l         | MII Collision Input                                                             |

| MII_CRS                   | 1           | MII Carrier Sense Input                                                         |

| MDC                       | 0           | PHY Management Clock Output                                                     |

| MDIO                      | lOpu        | PHY Management Data Input/Output                                                |

| Global Clocks             |             | <del>,</del>                                                                    |

| CLK_SYS_S                 | I           | System Clock Selection Input                                                    |

| CLK_SYS                   | I           | System Clock Input: 25, 50 or 75MHz                                             |

| CLK_CMN                   | I           | Common Clock Input (for common clock mode also known as differential mode)      |

| CLK_HIGH                  | I           | Clock High Input (for adaptive clock recovery machines and E1/T1 master clocks) |

| CPU Interface             |             |                                                                                 |

| H_CPU_SPI_N               | lpu         | Host Bus Interface (1=Parallel Bus, 0=SPI Bus)                                  |

| DAT_32_16_N               | lpu         | Data Bus Width (1=32-bit, 0=16-bit)                                             |

| H_D[31:1]                 | io          | Host Data Bus                                                                   |

| H_D[0] / SPI_MISO         | IO          | Host Data LSb or SPI Data Output                                                |

| H_AD[24:1]                | I           | Host Address Bus                                                                |

| H_CS_N                    | I           | Host Chip Select (Active Low)                                                   |

| H_R_W_N / SPI_CP          | I           | Host Read/Write Control or SPI Clock Phase                                      |

| H_WR_BE0_N / SPI_CLK      | I           | Host Write Enable Byte 0 (Active Low) or SPI Clock                              |

| H_WR_BE1_N / SPI_MOSI     |             | Host Write Enable Byte 1 (Active Low) or SPI Data Input                         |

Rev: 032609 10 of 13

### DS34S101, DS34S102, DS34S104, DS34S108

| PIN NAME                   | TYPE | PIN DESCRIPTION                                               |

|----------------------------|------|---------------------------------------------------------------|

| H_WR_BE2_N / SPI_SEL_N     | I    | Host Write Enable Byte 2 or SPI Chip Select (Active Low)      |

| H_WR_BE3_N / SPI_CI        |      | Host Write Enable Byte 3 (Active Low) or SPI Clock Invert     |

| H_READY_N                  | Oz   | Host Ready Output (Active Low)                                |

| H_INT                      | 0    | Host Interrupt Output.                                        |

| JTAG Interface             |      |                                                               |

| JTRST_N                    | lpu  | JTAG Test Reset                                               |

| JTCLK                      | lpd  | JTAG Test Clock                                               |

| JTMS                       | lpu  | JTAG Test Mode Select                                         |

| JTDI                       | lpu  | JTAG Test Data Input                                          |

| JTDO                       | Oz   | JTAG Test Data Output                                         |

| Reset and Factory Test Pir | าร   |                                                               |

| RST_SYS_N                  | lpu  | System Reset (Active Low)                                     |

| HIZ_N                      | I    | High Impedance Enable (Active Low)                            |

| SCEN                       | lpd  | Used for factory tests.                                       |

| STMD                       | lpd  | Used for factory tests.                                       |

| MBIST_EN                   | I    | Used for factory tests.                                       |

| MBIST_DONE                 | 0    | Used for factory tests.                                       |

| MBIST_FAIL                 | 0    | Used for factory tests                                        |

| TEST_CLK                   | 0    | Used for factory tests.                                       |

| TST_CLD                    | I    | Used for factory tests. DS34S104 only.                        |

| Power and Ground           |      |                                                               |

| DVDDC                      | Р    | 1.8V Core Voltage for TDM-over-Packet Digital logic (17 pins) |

| DVDDIO                     | Р    | 3.3V for I/O Pins (16 pins)                                   |

| DVSS                       | Р    | Ground for TDM-over-Packet logic and I/O Pins (31 pins)       |

| ACVDD1, ACVDD2             | Р    | 1.8V for CLAD Analog Circuits                                 |

| ACVSS1, ACVSS2             | Р    | Ground for CLAD Analog Circuits                               |

Note 1: In pin names, the suffix "n" stands for port number: n=1 to 8 for DS34S108; n=1 to 4 for DS34S104; n=2 for DS34S102; n=1 for DS34S101. All pin names ending in "\_N" are active low.

Note 2: All pins, except power and analog pins, are CMOS/TTL unless otherwise specified in the pin description. PIN TYPES

I = input pin

$I_{PD}$  = input pin with internal  $50k\Omega$  pulldown to DVSS

$I_{PU}$  = input pin with internal  $50k\Omega$  pullup to DVDDIO

IO = input/output pin

$\mathsf{IO}_{\mathsf{PD}}$  = input/output pin with internal  $\mathsf{50k}\Omega$  pulldown to DVSS

$IO_{PU}$  = input/output pin with internal  $50k\Omega$  pullup to DVDDIO

O = output pin

$O_Z$  = output pin that can be placed in a high-impedance state

P = power-supply or ground pin

Rev: 032609 11 of 13

\_ DS34S101, DS34S102, DS34S104, DS34S108

# 8 Package Information

For the latest package outline information and land patterns, go to www.maxim-ic.com/packages.

DS34S101, DS34S102 and DS34S108 have a 256-lead thermally enhanced chip-scale ball grid array (TECSBGA) package. The TECSBGA package dimensions are shown in Maxim document 21-0353.

DS34S108 has a 484-lead thermally enhanced ball grid array (TEBGA) package. The TEBGA package dimensions are shown in Maxim document 21-0365.

### 9 Thermal Information

| Parameter                          | TECSBGA-256<br>DS34S101<br>DS34S102<br>DS34S104 | TEBGA-484<br>DS34S108 |

|------------------------------------|-------------------------------------------------|-----------------------|

| Target Ambient Temperature Range   | -40 to 85°C                                     | -40 to 85°C           |

| Die Junction Temperature Range     | -40 to 125°C                                    | -40 to 125°C          |

| Theta Jc (junction to top of case) | 3.7 °C/W                                        | 4.2 °C/W              |

| Theta Jb (junction to bottom pins) | 13.1 °C/W                                       | 7.1 °C/W              |

| Theta Ja, Still Air (Note 1)       | 26.2 °C/W                                       | 16.1 °C/W             |

Note 1: These numbers are estimates using JEDEC standard PCB and enclosure dimensions.

Rev: 032609 12 of 13

# 10 Document Revision History

| REVISION DATE | DESCRIPTION                                                                                                                                                                                        |              |  |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--|

| 091407        | Preliminary release.                                                                                                                                                                               |              |  |

|               | Initial data sheet release. See below for changes made to the data sheet since the 091407 preliminary release version.                                                                             |              |  |

|               | Removed future status from DS34S104 in the Ordering Information table.                                                                                                                             | 1            |  |

|               | Updated status of IETF PWE3 standards for CESoPSN and TDMoIP.                                                                                                                                      | 1, 6, 10, 15 |  |

|               | In Table 9-1 and Table 9-2, corrected the pin type (from Ipd to I) and changed pin description to tell users to connect inputs SCEN and STMD to DVSS. These inputs do not have internal pulldowns. | 25, 33       |  |

| 040108        | In Section 7.1: Global Features, clarified product and package type relationships for the TEBGA and TECSBGA packages.                                                                              | 14           |  |

|               | In Table 9-2, clarified the pin description for input CLK_HIGH, added information for the unused input MCLK.                                                                                       | 30           |  |

|               | In Table 9-2, changed the output type for H_READY_N to three-stateable (from Opu to Oz). This output does not have an internal pullup.                                                             | 32           |  |

|               | In Table 9-2, simplified the pin descriptions for signals only used in factory (TEST_CLK, SCEN, STMD).                                                                                             | 33           |  |

|               | In Section 16: Thermal Information, updated the thermal Information for the TEBGA package. Added Theta-JA values for TEBGA deployments with forced air flow.                                       | 68           |  |

| 052908        | Removed future status from DS34S108 in the Ordering Information table.                                                                                                                             | 1            |  |

| 071808        | Completely revised and simplified. All content derived from the 071108 revision of the full data sheet.                                                                                            | All          |  |

| 101708        | Removed all references to AAL2 mode. Corrected some spelling errors and other minor typos.                                                                                                         | All          |  |

| 032609        | Removed future status for the DS34S101 and DS34S102 devices in the <i>Ordering Information</i> table.                                                                                              | 1            |  |

Rev: 032609 13 of 13

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.