## Section 18 Electrical Specifications

## 18.1 Absolute Maximum Ratings

Table 18-1 lists the absolute maximum ratings.

Table 18-1 Absolute Maximum Ratings

| Item                          | Symbol | Rating                                | Unit |

|-------------------------------|--------|---------------------------------------|------|

| Supply voltage                | Vcc    | -0.3 to +0.7                          | ٧    |

| Programming voltage           | VPP    | -0.3 to +13.5                         | ٧    |

| Input voltage (except port 6) | Vin    | -0.3 to Vcc + 0.3                     | ٧    |

| Input voltage (port 6)        | Vìn    | -0.3 to AVcc + 0.3                    | ٧    |

| Analog supply voltage         | AVcc   | -0.3 to +7.0                          | ٧    |

| Analog input voltage          | Van    | -0.3 to AVcc + 0.3                    | ٧    |

| Operating temperature         | Topr   | Regular specifications: -20 to +75    | .c   |

|                               |        | Wide-range specifications: -40 to +85 | .c   |

| Storage temperature           | Tstg   | -55 to +125                           | .c   |

Note: Permanent damage to the chip may result if the absolute maximum ratings shown in table 18-1 are exceeded.

#### 18.2 Electrical Characteristics

#### 18.2.1 DC Characteristics

Table 18-2 lists the DC characteristics.

Table 18-2 DC Characteristics

Conditions:  $Vcc = AVcc = 5.0 \text{ V} \pm 10\%^{*1}$ , Vss = AVss = 0 V,

$T_a = -20$  to 75°C (Regular specifications)

$T_a = -40$  to 85°C (Wide-range specifications)

|                       | •                                 |           |              |     |            |          | Test              |

|-----------------------|-----------------------------------|-----------|--------------|-----|------------|----------|-------------------|

| Item                  |                                   | Symbol    | min          | typ | max        | Unit     | Conditions        |

| Input high voltage    | RES, MD <sub>2</sub> ,            | Vін       | Vcc - 0.7    |     | Vcc + 0.3  | V        |                   |

|                       | MD <sub>1</sub> , MD <sub>0</sub> |           |              |     |            |          |                   |

|                       | EXTAL                             |           | Vcc × 0.7    |     | Vcc + 0.3  | <u>v</u> |                   |

|                       | Port 6                            |           | 2.2          |     | AVcc + 0.3 |          |                   |

|                       | Other input pins                  |           | 2.2          | _   | Vcc + 0.3  | ٧        |                   |

|                       | (except port 5)                   |           |              |     |            |          |                   |

| Input low voltage     | RES, MD2,                         | VIL       | -0.3         | _   | 0.5        | ٧        |                   |

|                       | MD <sub>1</sub> , MD <sub>0</sub> |           |              |     |            |          |                   |

|                       | Other input pins                  |           | -0.3         | _   | 8.0        |          |                   |

|                       | (except port 5)                   |           |              |     |            |          |                   |

| Schmitt trigger       | Port 5                            | VT-       | 1.0          |     | 2.5        |          |                   |

| input voltage         |                                   | VT+       | 2.0          |     | 3.5        | V        |                   |

|                       |                                   | VT+ – VT- | 0.4          |     |            | ٧        |                   |

| Input leakage current | RES                               | lin       |              |     | 10.0       | μА       | $V_{in} = 0.5 to$ |

|                       | NMI, MD2,                         |           |              |     | 1.0        | μА       | Vcc - 0.5 V       |

|                       | MD1, MD0,                         |           |              |     |            |          |                   |

|                       | Port 6                            |           | _            | _   | 1.0        | μΑ       | $V_{in} = 0.5 to$ |

|                       |                                   |           |              |     |            |          | AVcc - 0.5 V      |

| Leakage current       | Port 7,                           | Itsi      | _            | _   | 1.0        | μΑ       | $V_{in} = 0.5 to$ |

| in 3-state            | ports 5 to 1                      |           |              |     |            |          | Vcc - 0.5 V       |

| (off state)           |                                   |           |              |     |            |          |                   |

| Input pull-up         | Ports 3 and 4                     | -IP       | 50           | _   | 200        | μА       | Vin = 0 V         |

| MOS current           |                                   |           |              |     |            |          |                   |

| Output high voltage   | All output pins                   | Vон       | Vcc - 0.5    |     | _          | ٧        | Iон = −200 μA     |

|                       |                                   |           | 3.5          |     | _          | ٧        | loн = -1 mA       |

| Output low voltage    | All output pins                   | Vol       |              | _   | 0.4        | ٧        | loL = 1.6 mA      |

| •                     | (except RES)                      |           |              |     |            |          |                   |

|                       | Port 3                            |           | _            | _   | 1.0        | ٧        | lot = 8 mA        |

|                       |                                   |           | _            |     | 1.2        | ٧        | lot = 10 mA       |

|                       | RES                               |           | _            |     | 0.4        | V        | lot = 2.6 mA      |

| Input capacitance     | RES                               | Cin       | <del>_</del> |     | 60         | pF       | Vin = 0 V         |

| . It - :              | NMI                               | -         |              | _   | 30         | pF       | f = 1 MHz         |

|                       | All input pins                    |           | _            |     | 15         | pF       | Ta = 25°C         |

|                       | except RES                        |           |              |     |            | •        |                   |

Table 18-2 DC Characteristics (cont)

|                      |                  |        |     |      |     |      | Test       |

|----------------------|------------------|--------|-----|------|-----|------|------------|

| Item                 |                  | Symbol | min | typ  | max | Unit | Conditions |

| Current dissipation* | Normal operation | lcc    |     | 20   | 30  | mA   | f = 6 MHz  |

|                      |                  |        |     | 25   | 40  | mA   | f = 8 MHz  |

|                      |                  |        |     | 30   | 50  | mA   | f = 10 MHz |

|                      |                  |        |     | 12   | 20  | mA   | f = 6 MHz  |

|                      | Sleep mode       |        |     | 16   | 25  | mA   | f = 8 MHz  |

|                      |                  |        | _   | 20   | 30  | mA   | f = 10 MHz |

|                      | Standby          |        | _   | 0.01 | 5.0 | μА   |            |

| Analog supply        | During A/D       | Alcc   | _   | 0.6  | 2.0 | mA   |            |

| current              | conversion       |        |     |      |     |      |            |

|                      | While waiting    | •      | _   | 0.01 | 5.0 | μА   |            |

| RAM standby voltage  |                  | VRAM   | 2.0 | _    | _   | ٧    |            |

Note: AVcc must be connected to a power supply even when the A/D converter is not used.

Table 18-3 Allowable Output Current Sink Values

Conditions:  $VCC = AVCC = 5.0 \text{ V} \pm 10\%$ , Vss = AVss = 0 V,

$T_a = -20$  to 75°C (Regular specifications)

$T_a = -40$  to 85°C (Wide-range specifications)

| Item                   |                         | Symbol | min | typ | max | Unit |

|------------------------|-------------------------|--------|-----|-----|-----|------|

| Allowable output low   | Port 3                  | loL    |     | _   | 10  | mA   |

| current sink (per pin) | RES                     |        |     |     | 2.6 | mA   |

|                        | Other output pins       |        | _   | _   | 2.0 | mA   |

| Allowable output low   | Port 3, total of 8 pins | ∑ lor  | _   | _   | 40  | mA   |

| current sink (total)   | Total of all other      |        | _   | _   | 80  | mA   |

|                        | output pins             |        |     |     |     |      |

| Allowable output high  | All output pins         | -Іон   | _   | _   | 2.0 | mA   |

| current sink (per pin) |                         |        |     |     |     |      |

| Allowable output high  | Total of all output     | ∑ –Юн  | _   | _   | 40  | mA   |

| current sink (total)   | pins                    |        |     |     |     |      |

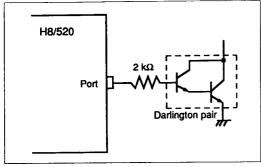

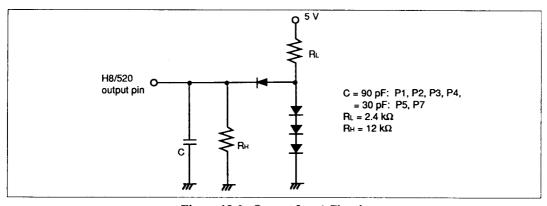

Note: To avoid degrading the reliability of the chip, be careful not to exceed the output current sink values in table 18-3. In particular, when driving a Darlington transistor pair or LED directly, be sure to insert a current-limiting resistor in the output path. See figures 18-1 and 18-2.

<sup>\*</sup> Current dissipation values assume that V<sub>IH</sub> min = V<sub>CC</sub> − 0.5 V, V<sub>IL</sub> max = 0.5 V, all output pins are in the no-load state, and all MOS input pull-ups are off.

H8/520 Vcc 600 Ω

Figure 18-1 Example of Circuit for Driving a Darlington Transistor Pair

Figure 18-2 Example of Circuit for Driving an LED

#### 18.2.2 AC Characteristics

The AC characteristics of the H8/520 chip are listed in three tables. Bus timing parameters are given in table 18-4, control signal timing parameters in table 18-5, and timing parameters of the on-chip supporting modules in table 18-6. See figure 18-3 for the output load circuit.

#### Table 18-4 Bus Timing

Conditions:

$Vcc = 5.0 \text{ V} \pm 10\%$ ,  $\emptyset = 0.5 \text{ to } 10 \text{ MHz}$ , Vss = 0 V

$T_a = -20$  to 75°C (Regular specifications)

$T_a = -40$  to 85°C (Wide-range specifications)

|                               |             | 6 N   | lHz _ | 8 1 | MHz  | 10  | MHz  |      | Test            |

|-------------------------------|-------------|-------|-------|-----|------|-----|------|------|-----------------|

| ltem                          | Symbol      | min   | max   | min | max  | min | max  | Unit | Conditions      |

| Clock cycle time              | toyc        | 166.7 | 2000  | 125 | 2000 | 100 | 2000 | ns   | See figure 18-4 |

| Clock pulse width low         | tcL         | 65    |       | 45  |      | 35  |      | ns   | _               |

| Clock pulse width high        | tсн         | 65    |       | 45  |      | 35  |      | ns   | _               |

| Clock rise time               | <b>t</b> Cr | -     | 15    |     | 15   |     | 15   | ns   |                 |

| Clock fall time               | tor         |       | 15    |     | 15   |     | 15   | ns   | -               |

| Address delay time            | tad         |       | 70    |     | 60   | _   | 55   | ns   | _               |

| Address hold time             | tah         | 30    |       | 25  |      | 20  |      | ns   | _               |

| RD delay time 1               | tRDD1       |       | 70    |     | 60   |     | 40   | ns   | _               |

| RD delay time 2               | tRDD2       | _     | 70    |     | 60   |     | 50   | ns   | _               |

| WR delay time 1               | twnD1       | _     | 70    |     | 60   |     | 50   | ns   | _               |

| WR delay time 2               | twRD2       |       | 70    |     | 60   |     | 50   | ns   | _               |

| Write data strobe pulse width | tosww       | 200   |       | 150 |      | 120 | _    | ns   | _               |

| Address setup time 1          | tası        | 25    |       | 20  |      | 15  |      | ns   |                 |

| Address setup time 2          | tas2        | 105   |       | 80  |      | 65  | -    | ns   | See figure 18-4 |

| Read data setup time          | tros        | 60    |       | 50  |      | 40  | _    | ns   |                 |

Table 18-4 Bus Timing (cont)

|                       |        | 6 1 | 6 MHz |     | 8 MHz |     | 10 MHz |      | Test            |  |

|-----------------------|--------|-----|-------|-----|-------|-----|--------|------|-----------------|--|

| Item                  | Symbol | min | max   | min | max   | min | max    | Unit | Conditions      |  |

| Read data hold time   | troh   | 0   | _     | 0   | _     | 0   | _      | ns   | See figure 18-4 |  |

| Read data access time | tacc   |     | 280   | _   | 190   | _   | 160    | ns   | _               |  |

| Write data delay time | twoo   |     | 70    |     | 60    |     | 60     | ns   | _               |  |

| Write data setup time | twos   | 30  |       | 15  | _     | 10  | _      | ns   | -               |  |

| Write data hold time  | twoH   | 30  |       | 25  | _     | 20  | _      | ns   |                 |  |

| Wait setup time       | twrs   | 40  |       | 40  |       | 40  |        | ns   | See figure 18-5 |  |

| Wait hold time        | twrH   | 10  |       | 10  |       | 10  |        | ns   |                 |  |

**Table 18-5 Control Signal Timing**

Conditions:  $Vcc = 5.0 \text{ V} \pm 10\%$ ,  $\emptyset = 0.5 \text{ to } 10 \text{ MHz}$ , Vss = 0 V

$T_a = -20$  to 75°C (Regular specifications)  $T_a = -40$  to 85°C (Wide-range specifications)

|                                                                 |        | 6 N | ИHz  | 8 1 | ЛНZ | 10  | 10 MHz |      | Test             |

|-----------------------------------------------------------------|--------|-----|------|-----|-----|-----|--------|------|------------------|

| Item                                                            | Symbol | min | max  | min | max | min | max    | Unit | Conditions       |

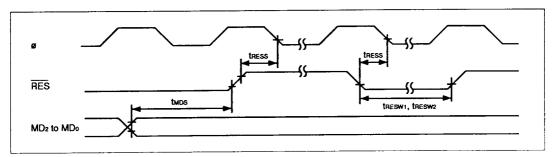

| RES setup time                                                  | tress  | 200 | **** | 200 | _   | 200 | _      | ns   | See figure 18-6  |

| RES pulse width 1*                                              | tresw1 | 6.0 | _    | 6.0 |     | 6.0 |        | toyo |                  |

| RES pulse width 2*                                              | tRESW2 | 520 |      | 520 | _   | 520 | _      | tcyc |                  |

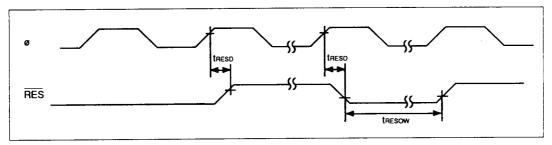

| RES output delay time                                           | tresd  | _   | 100  | _   | 100 | _   | 100    | ns   | See figure 18-7  |

| RES output pulse width                                          | tresow | 132 | _    | 132 |     | 132 |        | tcyc |                  |

| Mode programming setup time                                     | tMDS   | 4.0 | _    | 4.0 | _   | 4.0 |        | toyo | See figure 18-6  |

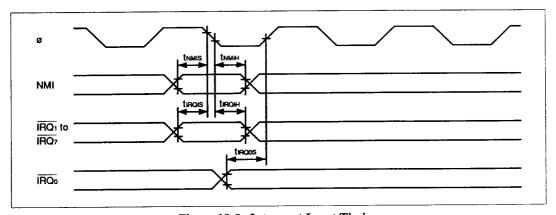

| NMI setup time                                                  | tnmis  | 150 |      | 150 | _   | 150 | -      | ns   | See figure 18-8  |

| NMI hold time                                                   | tnmih  | 10  |      | 10  | _   | 10  | _      | ns   | _                |

| IRQo setup time                                                 | tirqos | 50  |      | 50  |     | 50  | _      | ns   | -                |

| IRQ1 to IRQ7 setup time                                         | tiRQ1S | 50  |      | 50  |     | 50  |        | ns   |                  |

| IRQ1 to IRQ7 hold time                                          | tiRQ1H | 10  |      | 10  |     | 10  |        | ns   |                  |

| NMI pulse width<br>(for recovery from<br>software standby mode) | tnmiw  | 200 | _    | 200 | _   | 200 |        | ns   |                  |

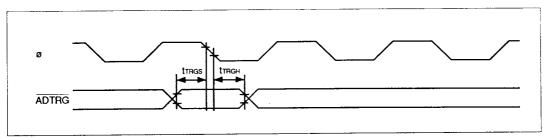

| A/D trigger setup time                                          | trrgs  | 50  |      | 50  |     | 50  |        | ns   | See figure 18-18 |

| A/D trigger hold time                                           | tтrgн  | 10  |      | 10  |     | 10  | -      | ns   |                  |

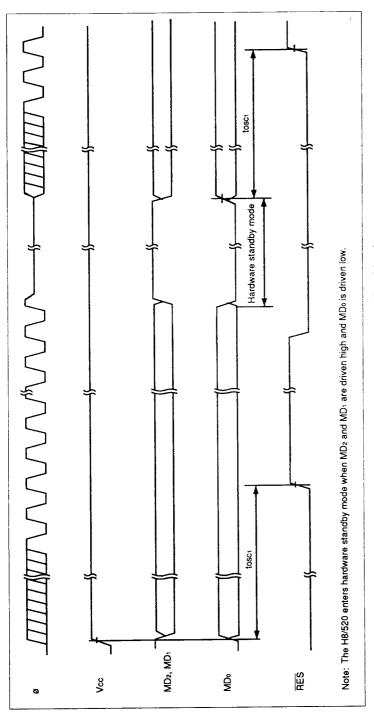

| Crystal oscillator settling time (reset)                        | toscı  | 20  |      | 20  |     | 20  | _      | ms   | See figure 18-9  |

| Crystal oscillator settling time (software standby)             | tosc2  | 10  |      | 10  |     | 10  |        | ms   | See figure 17-1  |

Note: \* tresw2 applies when the RSTOE bit in the reset control/status register (RSTCR) is set to 1. tresw1 applies when RSTOE is cleared to 0. tresw1 also applies at power-up.

Table 18-6 Timing Conditions of On-Chip Supporting Modules

Conditions:  $Vcc = 5.0 \text{ V} \pm 10\%$ ,  $\emptyset = 0.5 \text{ to } 10 \text{ MHz}$ , Vss = 0 V

$T_a = -20$  to 75°C (Regular specifications)  $T_a = -40$  to 85°C (Wide-range specifications)

|       |                             |         |               | 6 N | AHZ | 8 1 | VIHz | 10 / | MHz |       | Test             |

|-------|-----------------------------|---------|---------------|-----|-----|-----|------|------|-----|-------|------------------|

| Item  |                             |         | Symbol        | min | max | min | max  | min  | max | Unit  | Conditions       |

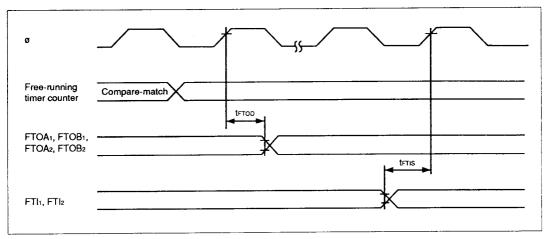

| FRT   | Timer output delay time     |         | <b>t</b> FTOD |     | 100 |     | 100  | _    | 100 | ns    | See figure 18-11 |

|       | Timer input setup time      |         | <b>t</b> FTIS | 50  | _   | 50  | _    | 50   | _   | ns    |                  |

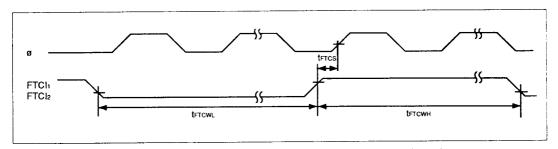

|       | Timer clock input setup tin | ne      | trtcs         | 50  |     | 50  | _    | 50   | _   | ns    | See figure 18-12 |

|       | Timer clock pulse width     |         | trtcw         | 1.5 | _   | 1.5 | _    | 1.5  |     | tcyc  | -                |

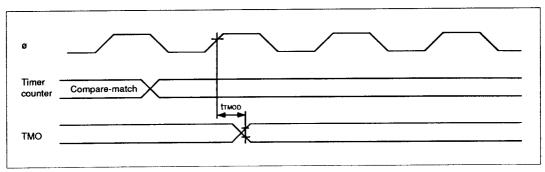

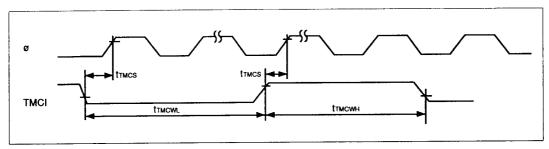

| TMR   | Timer output delay time     |         | TTMOD         |     | 100 | _   | 100  | _    | 100 | ns    | See figure 18-13 |

|       | Timer clock input setup tin | ne      | trucs         | 50  |     | 50  | _    | 50   | _   | ns    | See figure 18-14 |

|       | Timer clock pulse width     |         | trucw         | 1.5 | _   | 1.5 | _    | 1.5  | _   | tcyc  | -                |

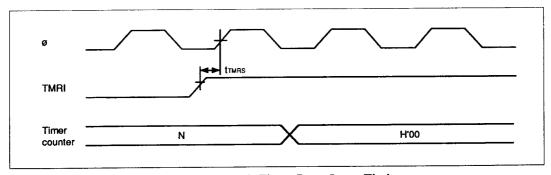

|       | Timer reset input setup tin | пе      | TTMRS         | 50  | _   | 50  | _    | 50   | _   | ns    | See figure 18-15 |

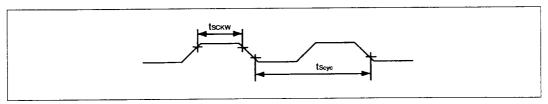

| SCI   | Input clock cycle           | (Async) | tScyc         | 2   | _   | 2   | _    | 2    | _   | tcyc  | See figure 18-16 |

|       |                             | (Sync)  |               | 4   | _   | 4   | _    | 4    | -   | tcyc  |                  |

|       | Input clock pulse width     |         | tsckw         | 0.4 | 0.6 | 0.4 | 0.6  | 0.4  | 0.6 | tscyc | -                |

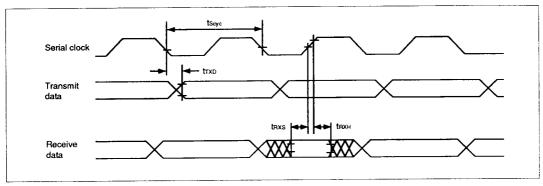

|       | Transmit data delay time    | (Sync)  | ttxD          | _   | 100 | _   | 100  | _    | 100 | ns    | See figure 18-17 |

|       | Receive data setup time     | (Sync)  | trxs          | 100 |     | 100 | _    | 100  | _   | ns    | _                |

|       | Receive data hold time      | (Sync)  | taxh          | _   | 100 | _   | 100  | _    | 100 | ns    | -                |

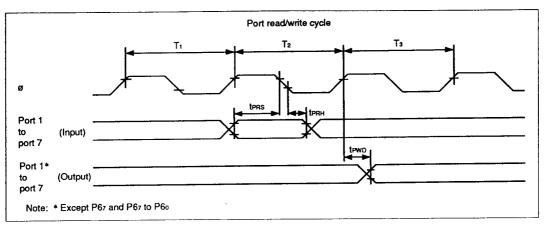

| Ports | Output data delay time      |         | tpwD          | _   | 100 |     | 100  | _    | 100 | ns    | See figure 18-10 |

|       | Input data setup time       |         | tprs          | 50  | _   | 50  | _    | 50   |     | ns    | -                |

|       | Input data hold time        |         | tркн          | 50  | _   | 50  |      | 50   |     | ns    | •                |

#### • Measurement Conditions for AC Characteristics

Figure 18-3 Output Load Circuit

#### 18.2.3 A/D Converter Characteristics

Table 18-7 lists the characteristics of the on-chip A/D converter.

Table 18-7 (1) A/D Converter Characteristics

Conditions:  $Vcc = AVcc = 5.0 \text{ V} \pm 10\%$ , Vss = AVss = 0 V,

$T_a = -40$  to 85°C (Wide-range specifications)

|                                   | 6 MHz |     |      | 8 MHz |     |       | 10 MHz |     |      |      |

|-----------------------------------|-------|-----|------|-------|-----|-------|--------|-----|------|------|

| Item                              | min   | typ | max  | min   | typ | max   | min    | typ | max  | Unit |

| Resolution                        | 10    | 10  | 10   | 10    | 10  | 10    | 10     | 10  | 10   | Bits |

| Conversion time                   | _     |     | 23.0 |       | _   | 17.25 |        |     | 13.8 | μs   |

| Analog input capacitance          |       |     | 20   |       |     | 20    |        |     | 20   | pF   |

| Allowable signal-source impedance | _     | -   | 10   |       |     | 10    |        | _   | 10   | kΩ   |

| Nonlinearity error                |       | _   | ±2.0 |       | _   | ±2.0  |        |     | ±2.0 | LSB  |

| Offset error                      |       |     | ±2.0 | _     | _   | ±2.0  | _      | _   | ±2.0 | LSB  |

| Full-scale error                  | _     | _   | ±2.0 |       |     | ±2.0  |        | _   | ±2.0 | LSB  |

| Quantizing error                  | _     | _   | ±0.5 | _     |     | ±0.5  |        | _   | ±0.5 | LSB  |

| Absolute accuracy                 | _     | _   | ±2.5 | _     |     | ±2.5  | _      |     | ±2.5 | LSB  |

Table 18-7 (2) A/D Converter Characteristics

Conditions:  $Vcc = AVcc = 5.0 V \pm 10\%$ , Vss = AVss = 0 V,

$T_a = -20$  to 75°C (Regular specifications)

|                                   |     | 6 MH | z    |     | 8 MH | z     |     | 10 MF | lz   |      |

|-----------------------------------|-----|------|------|-----|------|-------|-----|-------|------|------|

| Item                              | min | typ  | max  | min | typ  | max   | min | typ   | max  | Unit |

| Resolution                        | 10  | 10   | 10   | 10  | 10   | 10    | 10  | 10    | 10   | Bits |

| Conversion time                   | _   | _    | 23.0 |     | _    | 17.25 | -   |       | 13.8 | μs   |

| Analog input capacitance          |     | _    | 20   |     |      | 20    |     |       | 20   | pF   |

| Allowable signal-source impedance | _   | _    | 10   |     |      | 10    |     |       | 10   | kΩ   |

| Nonlinearity error                | _   | _    | ±3.5 |     |      | ±3.5  | _   | _     | ±3.5 | LSB  |

| Offset error                      | _   |      | ±3.5 |     |      | ±3.5  | _   | _     | ±3.5 | LSB  |

| Full-scale error                  | _   |      | ±3.5 |     |      | ±3.5  | _   |       | ±3.5 | LSB  |

| Quantizing error                  | _   | _    | ±0.5 |     | _    | ±0.5  |     | _     | ±0.5 | LSB  |

| Absolute accuracy                 | _   | _    | ±4.0 |     |      | ±4.0  |     | _     | ±4.0 | LSB  |

## 18.3 MCU Operational Timing

This section provides the following timing charts:

| 18.3.1 Bus timing                       | Figures 18-4 and 18-5   |

|-----------------------------------------|-------------------------|

| 18.3.2 Control Signal Timing            | Figures 18-6 to 18-8    |

| 18.3.3 Clock Timing                     | Figure 18-9             |

| 18.3.4 I/O Port Timing                  | Figure 18-10            |

| 18.3.5 16-Bit Free-Running Timer Timing | Figures 18-11 and 18-12 |

| 18.3.6 8-Bit Timer Timing               | Figures 18-13 to 18-15  |

| 18.3.7 SCI Timing                       | Figures 18-16 and 18-17 |

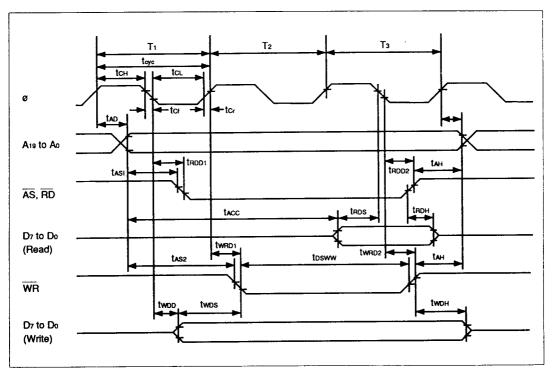

#### 18.3.1 Bus Timing

#### 1. Basic Bus Cycle (without Wait States) in Expanded Modes

Figure 18-4 Basic Bus Cycle (without Wait States) in Expanded Modes

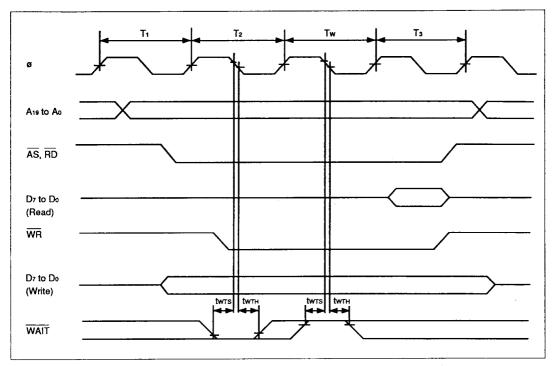

### 2. Basic Bus Cycle (with 1 Wait State) in Expanded Modes

Figure 18-5 Basic Bus Cycle (with 1 Wait State) in Expanded Modes

### 18.3.2 Control Signal Timing

### 1. Reset Input Timing

Figure 18-6 Reset Input Timing

### 2. Reset Output Timing

Figure 18-7 Reset Output Timing

### 3. Interrupt Input Timing

Figure 18-8 Interrupt Input Timing

Figure 18-9 Clock Oscillator Stabilization

## 18.3.4 I/O Port Timing

Figure 18-10 I/O Port Input/Output Timing

### 18.3.5 16-Bit Free-Running Timer Timing

#### 1. Free-Running Timer Input/Output Timing

Figure 18-11 Free-Running Timer Input/Output Timing

## 2. External Clock Input Timing for Free-Running Timers

Figure 18-12 External Clock Input Timing for Free-Running Timers

### 18.3.6 8-Bit Timer Timing

### 1. 8-Bit Timer Output Timing

Figure 18-13 8-Bit Timer Output Timing

### 2. 8-Bit Timer Clock Input Timing

Figure 18-14 8-Bit Timer Clock Input Timing

#### 3. 8-Bit Timer Reset Input Timing

Figure 18-15 8-Bit Timer Reset Input Timing

## 18.3.7 Serial Communication Interface Timing

Figure 18-16 SCI Input Clock Timing

Figure 18-17 SCI Input/Output Timing (Synchronous Mode)

## 18.3.8 A/D External Trigger Input Timing

Figure 18-18 A/D External Trigger Input Timing

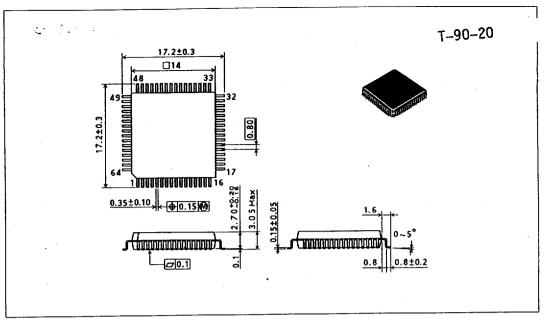

7-90-20

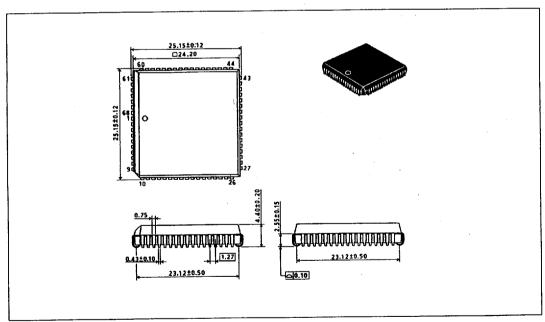

# Appendix F Package Dimensions

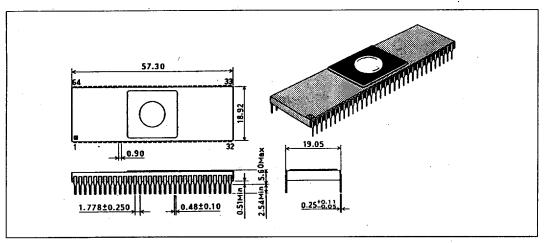

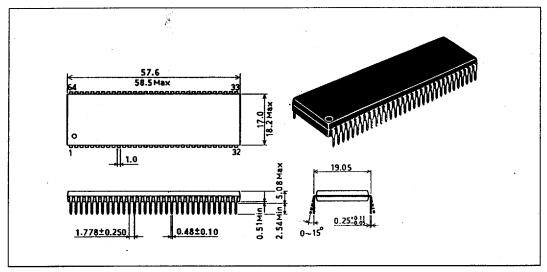

Figure F-1 shows the dimensions of the DC-64S package. Figure F-2 shows the dimensions of the DP-64S package. Figure F-3 shows the dimensions of the FP-64A package. Figure F-4 shows the dimensions of the CP-68 package.

Figure F-1 Package Dimensions (DC-64S)

Figure F-2 Package Dimensions (DP-64S)

Figure F-3 Package Dimensions (FP-64A)

Figure F-4 Package Dimensions (CP-68)