# Single Micropower, Chopper Stabilized, RRIO **Operational Amplifier**

### ISL28133

The ISL28133 is a single micropower, chopper stabilized operational amplifier that is optimized for single supply operation from 1.65V to 5.5V. Its low supply current of 18µA and wide input range enable the ISL28133 to be an excellent general purpose op amp for a range of applications. The ISL28133 is ideal for handheld devices that operates off 2 AA or single Li-ion batteries.

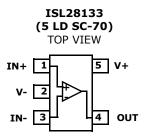

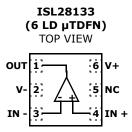

The ISL28133 is available in the 5 Ld SOT-23, the 5 Ld SC70 and the 6 Ld 1.6mmx1.6mm µTDFN packages. All devices operates over the extended temperature range of -40°C to +125°C.

### **Features**

| • Low Input Offset Voltage 8μV, Max.                          |

|---------------------------------------------------------------|

| • Low Offset TC 0.075μV/°C, Max                               |

| • Input Bias Current 300pA, Max.                              |

| • Quiescent Current 18µA, Typ.                                |

| • Wide Supply Range 1.65V to 5.5V                             |

| • Low Noise (0.01Hz to 10Hz)1.1 $\mu$ V <sub>P-P</sub> , Typ. |

| <ul> <li>Rail-to-Rail Inputs and Output</li> </ul>            |

| • Operating Temperature Range40°C to +125°C                   |

# Applications\*(see page 17)

- Bidirectional Current Sense

- Temperature Measurement

- Medical Equipment

- Electronic Weigh Scales

### **Related Literature**

- AN1480 "ISL28133ISENS-EV1Z Evaluation Board Users Guide"

- AN1499 "ISL28133EVAL1Z High Gain Evaluation Board User's Guide"

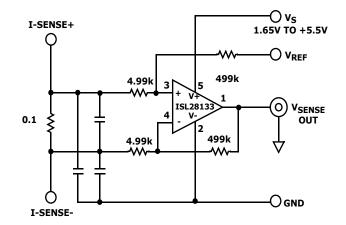

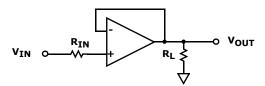

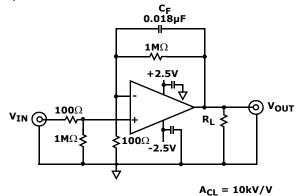

# **Typical Application**

#### **BIDIRECTIONAL CURRENT SENSE AMPLIFIER**

1

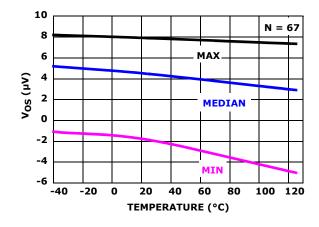

# **VOS vs Temperature**

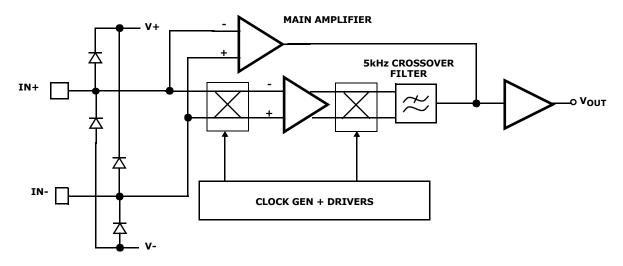

### **Block Diagram**

### **Ordering Information**

| PART<br>NUMBER               | PART MARKING     | PACKAGE<br>(Pb-Free) | PKG.<br>DWG. # |  |  |

|------------------------------|------------------|----------------------|----------------|--|--|

| ISL28133FHZ-T7 (Notes 1, 2)  | BCFA             | 5 Ld SOT-23          | MDP0038        |  |  |

| ISL28133FEZ-T7 (Notes 1, 2)  | ВНА              | 5 Ld SC70            | P5.049         |  |  |

| ISL28133FRUZ-T7 (Notes 1, 3) | T8               | 6 Ld μTDFN           | L6.1.6x1.6     |  |  |

| ISL28133ISENS-EV1Z           | Evaluation Board |                      |                |  |  |

| ISL28133EVAL1Z               | Evaluation Board |                      |                |  |  |

#### NOTES:

- 1. Please refer to  $\underline{\mathsf{TB347}}$  for details on reel specifications.

- 2. These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

- 3. These Intersil Pb-free plastic packaged products employ special Pb-free material sets; molding compounds/die attach materials and NiPdAu plate e4 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

- 4. For Moisture Sensitivity Level (MSL), please see device information page for <u>ISL28133</u>. For more information on MSL please see techbrief <u>TB363</u>.

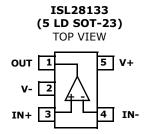

# **Pin Configuration**

# **Pin Descriptions**

| ISL28133<br>(5 Ld SOT23) | ISL28133<br>(5 Ld SC70) | ISL28133<br>(6 Ld µTDFN) | PIN<br>NAME | FUNCTION            | EQUIVALENT CIRCUIT                                 |

|--------------------------|-------------------------|--------------------------|-------------|---------------------|----------------------------------------------------|

| 3                        | 1                       | 4                        | IN+         | Non-inverting input | IN- CLOCK GEN + DRIVERS                            |

|                          |                         |                          |             |                     | Circuit 1                                          |

| 2                        | 2                       | 2                        | V-          | Negative supply     |                                                    |

| 4                        | 3                       | 3                        | IN-         | Inverting input     | (See Circuit 1)                                    |

| 1                        | 4                       | 1                        | OUT         | Output              | V+ OUT Circuit 2                                   |

| 5                        | 5                       | 6                        | V+          | Positive supply     |                                                    |

|                          |                         | 5                        | NC          | Not Connected -     | This pin is not electrically connected internally. |

### **Absolute Maximum Ratings**

| Max Supply Voltage V+ to V6.5V      |

|-------------------------------------|

| Max Voltage VIN to GND0.5V to 6.5V  |

| Max Input Differential Voltage 6.5V |

| Max Input Current 20mA              |

| Max Voltage VOUT to GND (10s) 6.5V  |

| ESD Rating                          |

| Human Body Model                    |

| Machine Model                       |

| Charged Device Model                |

### **Thermal Information**

| Thermal Resistance (Typical)                 | $\theta_{JA}$ (°C/W) |

|----------------------------------------------|----------------------|

| 5 Ld SOT-23 (Notes 5)                        | 225                  |

| 5 Ld SC70 (Notes 5)                          | 206                  |

| 6 Ld μTDFN (Notes 5)                         | 240                  |

| Maximum Storage Temperature Range65°0        | C to +150°C          |

| Pb-Free Reflow Profile se                    | e link below         |

| http://www.intersil.com/pbfree/Pb-FreeReflov | v.asp                |

|                                              |                      |

### **Operating Conditions**

| Temperature Range            | -40°C to +125°C |

|------------------------------|-----------------|

| Maximum Junction Temperature | 140°C           |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTE

5.  $\theta_{JA}$  is measured with the component mounted on a high effective thermal conductivity test board in free air. See Tech Brief TB379 for details.

# Electrical Specifications $V_+ = 5V$ , $V_- = 0V$ , VCM = 2.5V, $T_A = +25$ °C, $R_L = Open$ , unless otherwise specified. Boldface limits apply over the operating temperature range, -40°C to +125°C.

| PARAMETER                          | DESCRIPTION                                     | CONDITIONS                                                                                                                     | MIN<br>(Note 6) | TYP   | MAX<br>(Note 6) | UNIT              |

|------------------------------------|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-----------------|-------|-----------------|-------------------|

| DC SPECIFICATION                   | NS .                                            |                                                                                                                                | J.              |       |                 |                   |

| V <sub>OS</sub>                    | Input Offset Voltage                            |                                                                                                                                | -8              | ±2    | 8               | μV                |

|                                    |                                                 |                                                                                                                                | -15.5           |       | 15.5            | μV                |

| TCV <sub>OS</sub>                  | Input Offset Voltage Temperature<br>Coefficient |                                                                                                                                |                 | 0.02  | 0.075           | μV/°C             |

| I <sub>OS</sub>                    | Input Offset Current                            |                                                                                                                                |                 | -60   |                 | pA                |

| I <sub>B</sub>                     | Input Bias Current                              |                                                                                                                                | -300            | ±30   | 300             | pA                |

|                                    |                                                 |                                                                                                                                | -600            |       | 600             | pA                |

| Common Mode Input<br>Voltage Range |                                                 | V+ = 5.0V, V- = GND                                                                                                            | -0.1            |       | 5.1             | V                 |

| CMRR                               | Common Mode Rejection Ratio                     | VCM = -0.1V to 5.0V                                                                                                            | 118             | 125   |                 | dB                |

|                                    |                                                 |                                                                                                                                | 115             |       |                 | dB                |

| PSRR                               | Power Supply Rejection Ratio                    | Vs = 2V to 5.5V                                                                                                                | 110             | 138   |                 | dB                |

|                                    |                                                 |                                                                                                                                | 110             |       |                 | dB                |

| V <sub>OH</sub>                    | Output Voltage Swing, High                      | $R_L = 10k\Omega$                                                                                                              | 4.965           | 4.981 |                 | V                 |

| V <sub>OL</sub>                    | Output Voltage Swing, Low                       | $R_L = 10k\Omega$                                                                                                              |                 | 18    | 35              | mV                |

| A <sub>OL</sub>                    | Open Loop Gain                                  | $R_L = 1M\Omega$                                                                                                               |                 | 174   |                 | dB                |

| V <sub>+</sub>                     | Supply Voltage                                  | (Note 7)                                                                                                                       | 1.65            |       | 5.5             | V                 |

| I <sub>S</sub>                     | Supply Current                                  | R <sub>L</sub> = OPEN                                                                                                          |                 | 18    | 25              | μΑ                |

|                                    |                                                 |                                                                                                                                |                 |       | 35              | μΑ                |

| I <sub>SC+</sub>                   | Output Source Short Circuit Current             | R <sub>L</sub> = Short to ground or V+                                                                                         | 13              | 17    | 26              | mA                |

| I <sub>SC-</sub>                   | Output Sink Short Circuit Current               |                                                                                                                                | -26             | -19   | -13             | mA                |

| AC SPECIFICATION                   | NS                                              |                                                                                                                                | I               |       |                 |                   |

| GBWP                               | Gain Bandwidth Product<br>f = 50kHz             | $\begin{aligned} &A_{V} = 100,  R_{F} = 100 k \Omega, \\ &R_{G} = 1 k \Omega,  R_{L} = 10 k \Omega  to   V_{CM} \end{aligned}$ |                 | 400   |                 | kHz               |

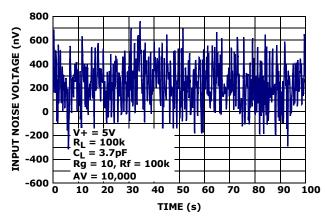

| e <sub>N</sub> V <sub>P-P</sub>    | Peak-to-Peak Input Noise Voltage                | f = 0.01Hz to 10Hz                                                                                                             |                 | 1.1   |                 | μV <sub>P-P</sub> |

FN6560.3 August 12, 2010

**Electrical Specifications**  $V_+ = 5V$ ,  $V_- = 0V$ , VCM = 2.5V,  $T_A = +25$ °C,  $R_L = Open$ , unless otherwise specified. **Boldface** limits apply over the operating temperature range, -40°C to +125°C. (Continued)

| PARAMETER                                      | DESCRIPTION                                   | CONDITIONS                                                 | MIN<br>(Note 6) | ТҮР  | MAX<br>(Note 6) | UNIT     |

|------------------------------------------------|-----------------------------------------------|------------------------------------------------------------|-----------------|------|-----------------|----------|

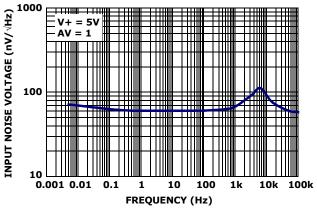

| e <sub>N</sub>                                 | Input Noise Voltage Density                   | f = 1kHz                                                   |                 | 65   |                 | nV/√(Hz) |

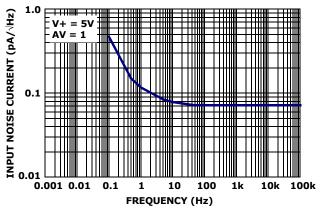

| i <sub>N</sub>                                 | Input Noise Current Density                   | f = 1kHz                                                   |                 | 72   |                 | fA/√(Hz) |

|                                                |                                               | f = 10Hz                                                   |                 | 79   |                 | fA/√(Hz) |

| C <sub>in</sub>                                | Differential Input Capacitance                | f = 1MHz                                                   |                 | 1.6  |                 | pF       |

|                                                | Common Mode Input Capacitance                 |                                                            |                 | 1.12 |                 | pF       |

| TRANSIENT RESP                                 | ONSE                                          |                                                            | 1               |      | •               |          |

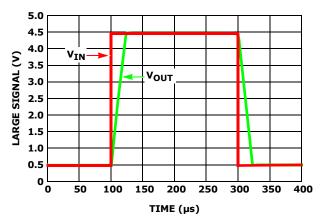

| SR                                             | Positive Slew Rate                            | $V_{OUT}$ = 1V to 4V, $R_L$ = 10k $\Omega$                 |                 | 0.2  |                 | V/µs     |

|                                                | Negative Slew Rate                            |                                                            |                 | 0.1  |                 | V/µs     |

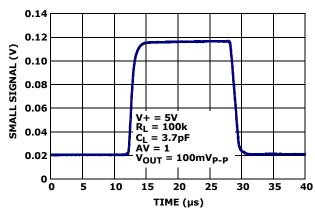

| t <sub>r</sub> , t <sub>f</sub> , Small Signal | Rise Time, t <sub>r</sub> 10% to 90%          | $A_V = +1$ , $V_{OUT} = 0.1V_{P-P}$ ,                      |                 | 1.1  |                 | μs       |

|                                                | Fall Time, t <sub>f</sub> 10% to 90%          | $R_F = 0\Omega, R_L = 10k\Omega,$<br>$C_L = 1.2pF$         |                 | 1.1  |                 | μs       |

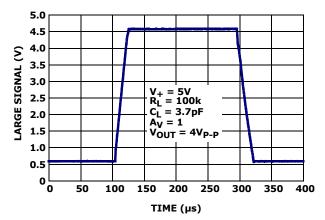

| t <sub>r</sub> , t <sub>f</sub> Large Signal   | Rise Time, t <sub>r</sub> 10% to 90%          | $A_V = +1, V_{OUT} = 2V_{P-P},$                            |                 | 8    |                 | μs       |

|                                                | Fall Time, t <sub>f</sub> 10% to 90%          | $R_F = 0\Omega, R_L = 10k\Omega,$<br>$C_L = 1.2pF$         |                 | 10   |                 | μs       |

| t <sub>s</sub>                                 | Settling Time to 0.1%, 2V <sub>P-P</sub> Step | $A_V = +1, R_F = 0\Omega, \\ R_L = 10k\Omega, C_L = 1.2pF$ |                 | 35   |                 | μs       |

#### NOTES:

- 6. Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Temperature limits established by characterization and are not production tested.

- 7. Parts are 100% tested with a minimum operating voltage of 1.65V to a VOS limit of  $\pm 15 \mu V$ .

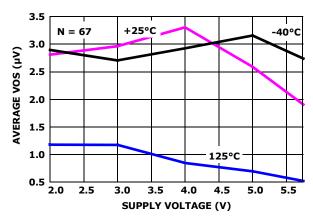

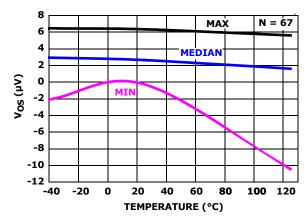

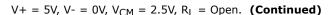

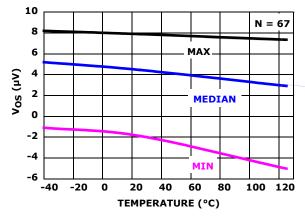

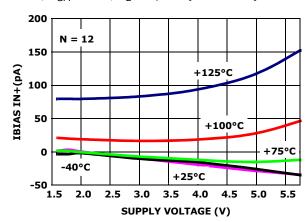

# **Typical Performance Curves** V+=5V, V-=0V, $V_{CM}=2.5V$ , $R_L=Open$ .

FIGURE 1. AVERAGE INPUT OFFSET VOLTAGE vs SUPPLY VOLTAGE

FIGURE 2.  $V_{OS}$  vs TEMPERATURE,  $V_S = \pm 1.0V$ ,  $V_{IN} = 0V$ ,  $R_L = INF$

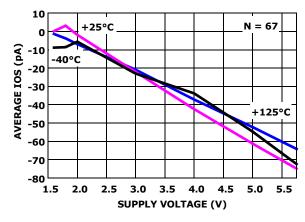

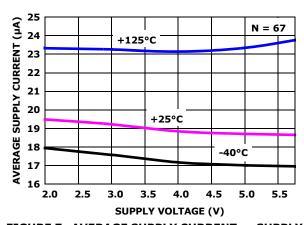

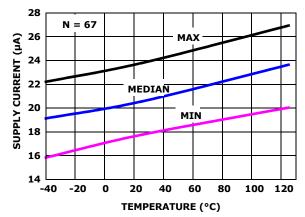

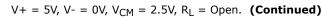

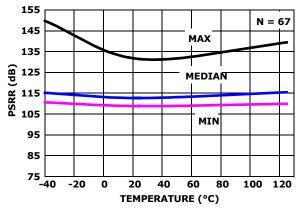

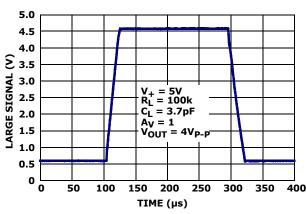

# **Typical Performance Curves** V+=5V, V-=0V, $V_{CM}=2.5V$ , $R_L=Open$ . (Continued)

FIGURE 3.  $V_{OS}$  vs TEMPERATURE,  $V_S = \pm 2.5V$ ,  $V_{IN} = 0V, R_L = INF$

FIGURE 4. IB+ vs SUPPLY VOLTAGE vs **TEMPERATURE**

FIGURE 5. IB- vs SUPPLY VOLTAGE vs TEMPERATURE

FIGURE 6. IOS vs SUPPLY VOLTAGE vs **TEMPERATURE**

FIGURE 7. AVERAGE SUPPLY CURRENT vs SUPPLY **VOLTAGE**

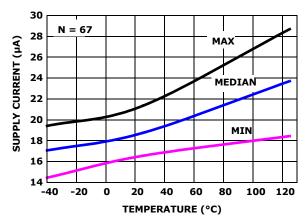

FIGURE 8. MIN/MAX SUPPLY CURRENT vs TEMPERATURE,  $V_S = \pm 0.8V, V_{IN} = 0V, R_L = INF$

FIGURE 9. MIN/MAX SUPPLY CURRENT vs TEMPERATURE,  $V_S = \pm 2.5V, V_{IN} = 0V, R_L = INF$

FIGURE 10. INPUT NOISE VOLTAGE 0.01Hz TO 10Hz

FIGURE 11. INPUT NOISE VOLTAGE DENSITY vs **FREQUENCY**

FIGURE 12. INPUT NOISE CURRENT DENSITY vs **FREQUENCY**

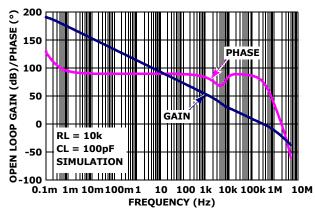

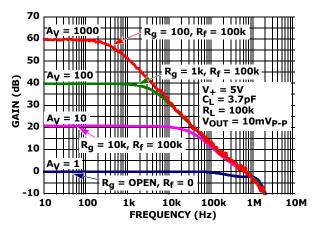

FIGURE 13. FREQUENCY RESPONSE vs OPEN LOOP  $GAIN, R_L = 10k$

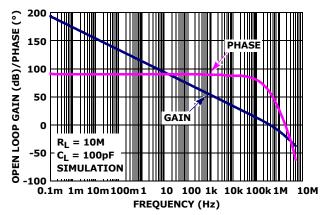

FIGURE 14. FREQUENCY RESPONSE vs OPEN LOOP  $GAIN, R_I = 10M$

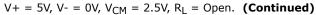

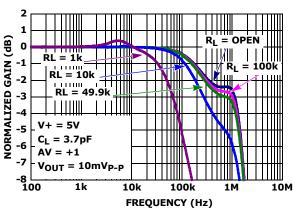

FIGURE 15. GAIN vs FREQUENCY vs  $R_{L_1}$   $V_S = 1.6V$

FIGURE 16. GAIN vs FREQUENCY vs  $R_L$ ,  $V_S = 5V$

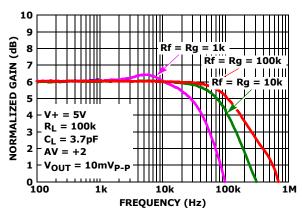

FIGURE 17. GAIN vs FREQUENCY vs FEEDBACK RESISTOR VALUES  $R_f/R_g$

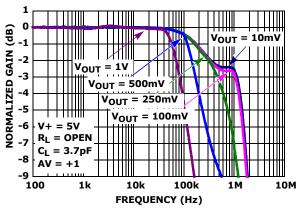

FIGURE 18. GAIN vs FREQUENCY vs V<sub>OUT</sub>, R<sub>L</sub> = OPEN

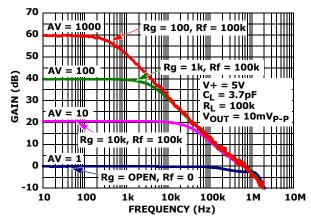

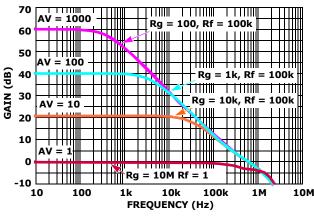

FIGURE 19. FREQUENCY RESPONSE vs CLOSED LOOP GAIN

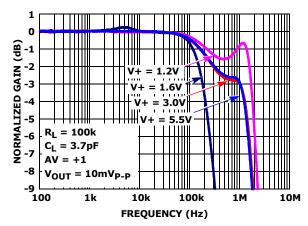

FIGURE 20. GAIN vs FREQUENCY vs SUPPLY VOLTAGE

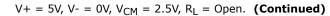

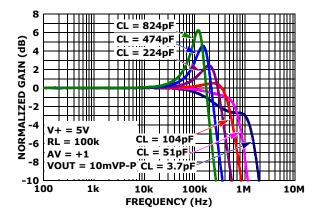

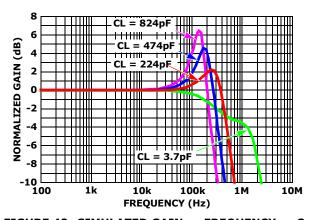

FIGURE 21. GAIN vs FREQUENCY vs CL

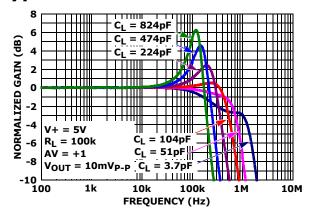

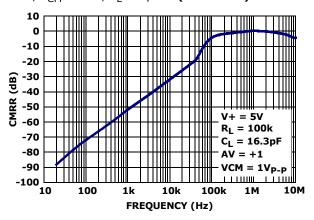

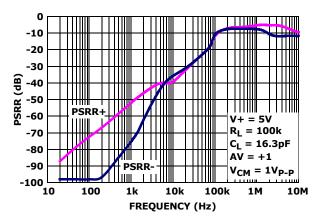

FIGURE 22. CMRR vs FREQUENCY,  $V_S = 5V$

FIGURE 23. PSRR vs FREQUENCY,  $V_S = 5V$

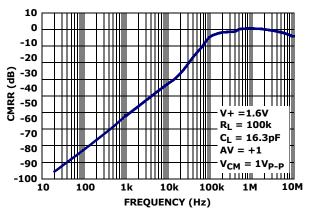

FIGURE 24. CMRR vs FREQUENCY,  $V_S = 1.6V$

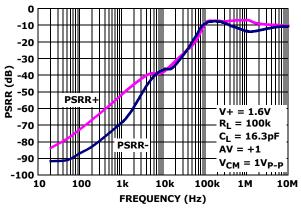

FIGURE 25. PSRR vs FREQUENCY,  $V_S = 1.6V$

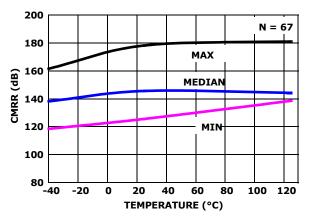

FIGURE 26. CMRR vs TEMPERATURE, VCM = -2.5V TO +2.5V, V+ =  $\pm 2.5V$

FIGURE 27. PSRR vs TEMPERATURE, V+ = 2V TO 5.5V

FIGURE 28. LARGE SIGNAL STEP RESPONSE (4V)

FIGURE 29. LARGE SIGNAL STEP RESPONSE (1V)

FIGURE 30. SMALL SIGNAL STEP RESPONSE (100mV)

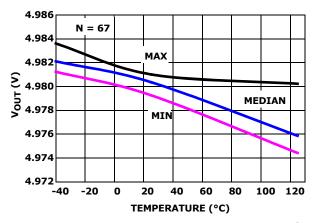

FIGURE 31.  $V_{OUT}$  HIGH vs TEMPERATURE,  $R_L$  = 10k,  $V_S$  +-2.5V

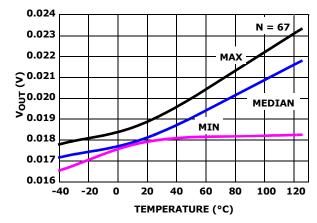

FIGURE 32.  $V_{OUT}$  LOW vs TEMPERATURE,  $R_L = 10k$ ,  $V_S +-2.5V$

# **Applications Information**

### **Functional Description**

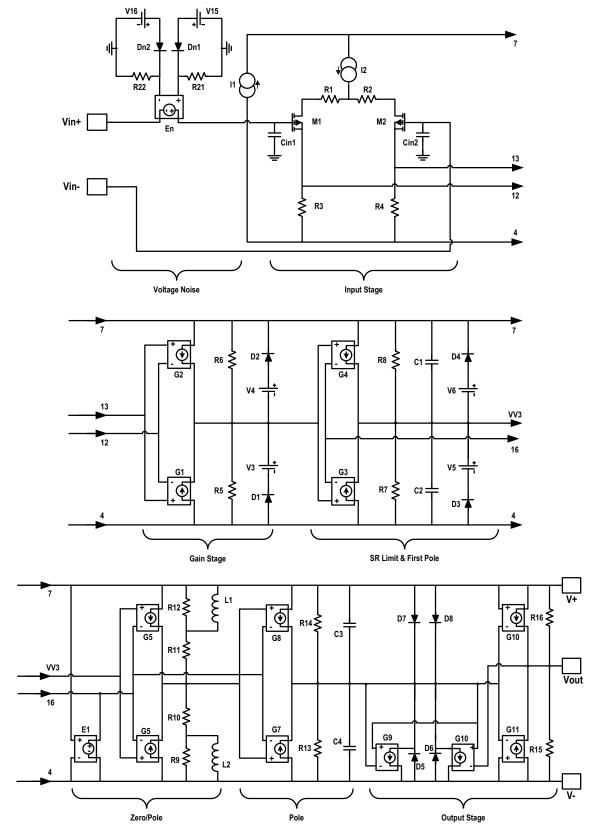

The ISL28133 uses a proprietary chopper-stabilized architecture shown in the "Block Diagram" on page 2. The ISL28133 combines a 400kHz main amplifier with a very high open loop gain (174dB) chopper stabilized amplifier to achieve very low offset voltage and drift (2 $\mu$ V, 0.02 $\mu$ V/°C typical) while consuming only 18 $\mu$ A of supply current per channel.

This multi-path amplifier architecture contains a time continuous main amplifier whose input DC offset is corrected by a parallel-connected, high gain chopper stabilized DC correction amplifier operating at 100kHz. From DC to ~5kHz, both amplifiers are active with DC offset correction and most of the low frequency gain is provided by the chopper amplifier. A 5kHz crossover filter cuts off the low frequency amplifier path leaving the main amplifier active out to the 400kHz gain-bandwidth product of the device.

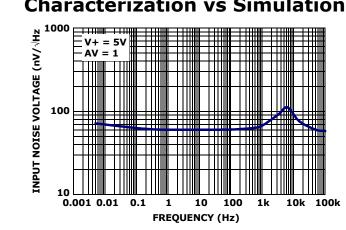

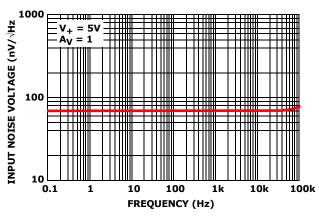

The key benefits of this architecture for precision applications are very high open loop gain, very low DC offset, and low 1/f noise. The noise is virtually flat across the frequency range from a few mHz out to 100kHz, except for the narrow noise peak at the amplifier crossover frequency (5kHz).

### Rail-to-rail Input and Output (RRIO)

The RRIO CMOS amplifier uses parallel input PMOS and NMOS that enable the inputs to swing 100mV beyond either supply rail. The inverting and non-inverting inputs do not have back-to-back input clamp diodes and are capable of maintaining high input impedance at high differential input voltages. This is effective in eliminating output distortion caused by high slew-rate input signals.

The output stage uses common source connected PMOS and NMOS devices to achieve rail-to-rail output drive capability with 17mA current limit and the capability to swing to within 20mV of either rail while driving a  $10k\Omega$  load.

#### **IN+ and IN- Protection**

All input terminals have internal ESD protection diodes to both positive and negative supply rails, limiting the input voltage to within one diode beyond the supply rails. For applications where either input is expected to exceed the rails by 0.5V, an external series resistor must be used to ensure the input currents never exceed 20mA (see Figure 33).

FIGURE 33. INPUT CURRENT LIMITING

11

# Layout Guidelines for High Impedance Inputs

To achieve the maximum performance of the high input impedance and low offset voltage of the ISL28133 amplifiers, care should be taken in the circuit board layout. The PC board surface must remain clean and free of moisture to avoid leakage currents between adjacent traces. Surface coating of the circuit board will reduce surface moisture and provide a humidity barrier, reducing parasitic resistance on the board.

### High Gain, Precision DC-Coupled Amplifier

The circuit in Figure 34 implements a single-stage, 10kV/V DC-coupled amplifier with an input DC sensitivity of under 100nV that is only possible using a low VOS amplifier with high open loop gain. This circuit is practical down to 1.8V due to it's rail-to-rail input and output capability. Standard high gain DC amplifiers operating from low voltage supplies are not practical at these high gains using typical low offset precision op amps because the input offset voltage and temperature coefficient consume most of the available output voltage swing. For example, a typical precision amplifier in a gain of 10kV/V with a ±100µV VOS and a temperature coefficient of  $0.5\mu V/^{\circ}C$  would produce a DC error at the output of >1V with an additional 5mV°C of temperature dependent error. At 3V, this DC error consumes > 30% of the total supply voltage, making it impractical to measure sub-microvolt low frequency signals.

The  $\pm 8\mu V$  max  $V_{OS}$  and  $0.075\mu V/^{\circ}C$  of the ISL28133 produces a temperature stable maximum DC output error of only  $\pm 80mV$  with a maximum temperature drift of  $0.75mV/^{\circ}C$ . The additional benefit of a very low 1/f noise corner frequency and some feedback filtering enables DC voltages and voltage fluctuations well below 100nV to be easily detected with a simple single stage amplifier.

FIGURE 34. HIGH GAIN, PRECISION DC-COUPLED

<u>intersil</u>

#### **ISL28133 SPICE Model**

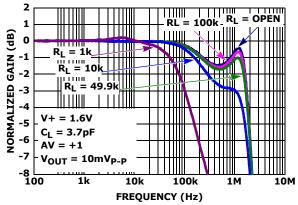

Figure 35 shows the SPICE model schematic and Figure 36 shows the net list for the ISL28133 SPICE model. The model is a simplified version of the actual device and simulates important parameters such as noise, **Slew Rate**, Gain and Phase. The model uses typical parameters from the ISL28133. The poles and zeros in the model were determined from the actual open and closed-loop gain and phase response. This enables the model to present an accurate AC representation of the actual device. The model is configured for ambient temperature of  $+25^{\circ}\text{C}$ .

Figures 37 through 44 show the characterization vs simulation results for the Noise Density, Frequency Response vs Close Loop Gain, Gain vs Frequency vs CL and Large Signal Step Response (4V).

FIGURE 35. SPICE CIRCUIT SCHEMATIC

#### ISL28133

```

* ISL28133 Macromodel

V_V6

18 VV3 0.7Vdc

* Revision B, April 2009

* AC characteristics, Voltage Noise

*Zero/Pole

* Connections:

+input

E E1

16 4 7 4 0.5

-input

G G5

4 VV4 VV3 16 0.000001

+Vsupply

G G6

7 VV4 VV3 16 0.000001

20 7 0.3H

-Vsupply

L L1

R R12

20 7 2.5meg

output

R R11

VV4 20 1meg

.subckt ISL28133

3

2

6

L_L2

4 19 0.3H

R_R9

4 19 2.5meg

*Voltage Noise

R R10

19 VV4 1meg

D DN1

102 101 DN

*Pole

D DN2

104 103 DN

G G7

4 VV5 VV4 16 0.000001

R R21

0 101 120k

G G8

7 VV5 VV4 16 0.000001

VV5 7 0.12p

R R22

0 103 120k

C C3

E_EN

8 3 101 103 1

C_C4

4 VV5 0.12p

V V15

102 0 0.1Vdc

R R13

4 VV5 1meg

VV5 7 1meg

V_V16

104 0 0.1Vdc

R_R14

*Input Stage

*Output Stage

C_Cin1

80 0.4p

G G9

21 4 6 VV5 0.0000125

C_Cin2

G_G10

20 2.0p

22 4 VV5 6 0.0000125

9 10 10

4 21 DY

R R1

D D5

R R2

10 11 10

D D6

4 22 DY

R R3

D D7

4 12 100

7 21 DX

R R4

4 13 100

D D8

7 22 DX

M M1

12899 pmosisil

R R15

46 8k

+ L=50u

R_R16

67 8k

+ W=50u

G G11

6 4 VV5 4 -0.000125

M M2

13 2 11 11 pmosisil

G_G12

7 6 7 VV5 -0.000125

+ L=50u

+ W=50u

.model pmosisil pmos (kp=16e-3 vto=10m)

.model DN D(KF=6.4E-16 AF=1)

1 11

4 7 DC 92uA

1_12

7 10 DC 100uA

.MODEL DX D(IS=1E-18 Rs=1)

.MODEL DY D(IS=1E-15 BV=50 Rs=1)

*Gain stage

.ends ISL28133

G G1

4 VV2 13 12 0.0002

G G2

7 VV2 13 12 0.0002

R R5

4 VV2 1.3Meg

R R6

VV2 7 1.3Meg

D D1

4 14 DX

D D2

15 7 DX

V V3

VV2 14 0.7Vdc

V_V4

15 VV2 0.7Vdc

*SR limit first pole

4 VV3 VV2 16 1

G G3

G G4

7 VV3 VV2 16 1

R R7

4 VV3 1meg

R R8

VV3 7 1meg

C C1

VV3 7 12u

C_C2

4 VV3 12u

D D3

4 17 DX

D D4

18 7 DX

VV3 17 0.7Vdc

V V5

```

FIGURE 36. SPICE NET LIST

### **Characterization vs Simulation Results**

FIGURE 37. CHARACTERIZED INPUT NOISE VOLTAGE **DENSITY vs FREQUENCY**

FIGURE 38. SIMULATED INPUT NOISE VOLTAGE **DENSITY vs FREQUENCY**

FIGURE 39. CHARACTERIZED FREOUENCY RESPONSE **vs CLOSED LOOP GAIN**

FIGURE 40. SIMULATED FREQUENCY RESPONSE vs **CLOSED LOOP GAIN**

FIGURE 41. CHARACTERIZED GAIN vs FREQUENCY vs  $C_L$

FIGURE 42. SIMULATED GAIN vs FREQUENCY vs C<sub>1</sub>

# **Characterization vs Simulation Results (Continued)**

FIGURE 43. CHARACTERIZED LARGE SIGNAL STEP RESPONSE (4V)

FIGURE 44. SIMULATED LARGE SIGNAL STEP RESPONSE (4V)

## **Revision History**

The revision history provided is for informational purposes only and is believed to be accurate, but not warranted. Please go to web to make sure you have the latest Rev.

| DATE     | REVISION | CHANGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5/3/10   | FN6560.3 | Title Page 1: Replaced "Zero-Drift" with "Chopper Stabilized" for title and part description On page 3: Pin Configuration: MTDFN -> uTDFN On page 7: Figure 10: Changed 0.1Hz to 0.01Hz in Figure caption On page 11: In "Functional Description"; Paragraph 1, 2nd sentence: Changed text from "open loop gain (200dB)" -to- "open loop gain (174dB)" Changed TYP for "Open Loop Gain" on page 4 from 200dB to 174dB. On page 11: In "High Gain, Precision DC-Coupled Amplifier"; Paragraph 2, 1st sentence: Changed text from "DC output error of only ±80mV with a maximum temperature drift of 0.75μV/°C." to " DC output error of only ±80mV with a maximum temperature drift of 0.75mV/C."                                                                                                |

| 2/24/10  |          | Removed "Coming Soon" from ISL28133EVAL1Z in the ordering information table on pg 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 09/24/09 | FN6560.2 | Converted to new Intersil template. Removed ISL28233 and ISL28433 from data sheet, added Applications, Related Literature, Typical Application Circuit, Performance Curve, updated ordering information by removing "coming soon" on SC70 and uTDFN packages and adding Eval board listed as "coming soon". Added Block Diagram, Changed in Abs Max Rating Voltage from "5.75V" to "6.5V". Removed Tjc from Thermal Information until provided by packaging scheduled for 9-11-09. Changed Low Offset "drift" to Low Offset "TC", added Max Junction Temp 140C, added SPICE model and simulation results, removed supply current graph at +-3V, re-ordered typical performance curves, removed guard ring information from application section. Added Revision History and Products Information |

| 05/29/09 | FN6560.1 | Page 4: Removed the RL = 100 Curve from Figures 3, 4 and 5. Page 1: Under Features, removed the word "Output" from "Low Output Noise"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 03/25/09 | FN6560.0 | Initial Release to WEB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

### **Products**

Intersil Corporation is a leader in the design and manufacture of high-performance analog semiconductors. The Company's products address some of the industry's fastest growing markets, such as, flat panel displays, cell phones, handheld products, and notebooks. Intersil's product families address power management and analog signal processing functions. Go to <a href="https://www.intersil.com/products">www.intersil.com/products</a> for a complete list of Intersil product families.

\*For a complete listing of Applications, Related Documentation and Related Parts, please see the respective device information page on intersil.com: <a href="ISL28133">ISL28133</a></a>

To report errors or suggestions for this data sheet, please go to www.intersil.com/askourstaff

FITs are available from our website at <a href="http://rel.intersil.com/reports/search.php">http://rel.intersil.com/reports/search.php</a>

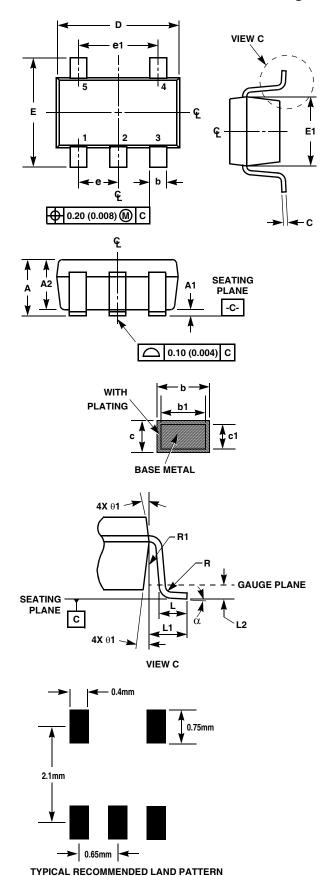

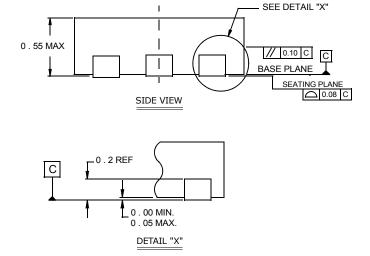

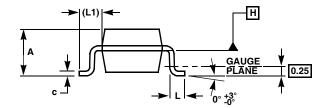

### Small Outline Transistor Plastic Packages (SC70-5)

P5.049 **5 LEAD SMALL OUTLINE TRANSISTOR PLASTIC PACKAGE**

|        | INC        | HES            | MILLIMETERS |                |       |

|--------|------------|----------------|-------------|----------------|-------|

| SYMBOL | MIN        | MAX            | MIN         | MAX            | NOTES |

| Α      | 0.031      | 0.043          | 0.80        | 1.10           | -     |

| A1     | 0.000      | 0.004          | 0.00        | 0.10           | -     |

| A2     | 0.031      | 0.039          | 0.80        | 1.00           | -     |

| b      | 0.006      | 0.012          | 0.15        | 0.30           | -     |

| b1     | 0.006      | 0.010          | 0.15        | 0.25           |       |

| С      | 0.003      | 0.009          | 0.08        | 0.22           | 6     |

| c1     | 0.003      | 0.009          | 0.08        | 0.20           | 6     |

| D      | 0.073      | 0.085          | 1.85        | 2.15           | 3     |

| Е      | 0.071      | 0.094          | 1.80        | 2.40           | -     |

| E1     | 0.045      | 0.053          | 1.15        | 1.35           | 3     |

| е      | 0.0256 Ref |                | 0.65        | Ref            | -     |

| e1     | 0.0512 Ref |                | 1.30        | Ref            | -     |

| L      | 0.010      | 0.018          | 0.26        | 0.46           | 4     |

| L1     | 0.017      | 0.017 Ref.     |             | Ref.           | -     |

| L2     | 0.006      | BSC            | 0.15        | BSC            |       |

| α      | 0°         | 8 <sup>0</sup> | 0°          | 8 <sup>0</sup> | -     |

| N      | 5          |                | į           | 5              | 5     |

| R      | 0.004      | -              | 0.10        | -              |       |

| R1     | 0.004      | 0.010          | 0.15        | 0.25           |       |

Rev. 3 7/07

### NOTES:

- 1. Dimensioning and tolerances per ASME Y14.5M-1994.

- 2. Package conforms to EIAJ SC70 and JEDEC MO-203AA.

- 3. Dimensions D and E1 are exclusive of mold flash, protrusions, or gate burrs.

- 4. Footlength L measured at reference to gauge plane.

- 5. "N" is the number of terminal positions.

- 6. These Dimensions apply to the flat section of the lead between 0.08mm and 0.15mm from the lead tip.

- 7. Controlling dimension: MILLIMETER. Converted inch dimensions are for reference only.

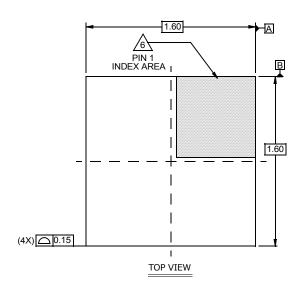

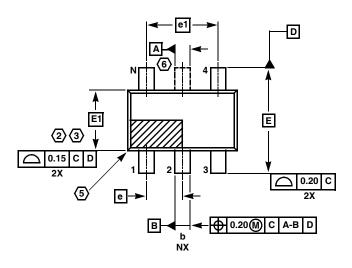

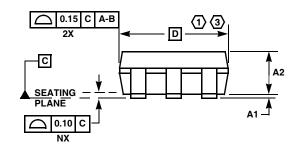

## **Package Outline Drawing**

### L6.1.6x1.6

### 6 LEAD ULTRA THIN DUAL FLAT NO-LEAD COL PLASTIC PACKAGE (UTDFN COL)

TYPICAL RECOMMENDED LAND PATTERN

#### NOTES:

- 1. Dimensions are in millimeters. Dimensions in ( ) for Reference Only.

- 2. Dimensioning and tolerancing conform to AMSE Y14.5m-1994.

- Unless otherwise specified, tolerance : Decimal  $\pm 0.05$

- 4. Dimension b applies to the metallized terminal and is measured between 0.15mm and 0.30mm from the terminal tip.

- 5. Tiebar shown (if present) is a non-functional feature.

- The configuration of the pin #1 identifier is optional, but must be located within the zone indicated. The pin #1 identifier may be either a mold or mark feature.

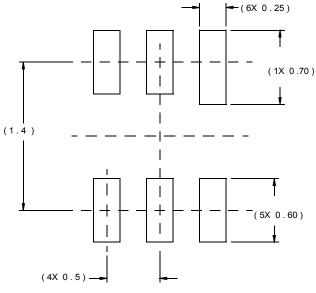

### SOT-23 Package Family

### MDP0038

#### **SOT-23 PACKAGE FAMILY**

|        | MILLIN  |         |           |

|--------|---------|---------|-----------|

| SYMBOL | SOT23-5 | SOT23-6 | TOLERANCE |

| Α      | 1.45    | 1.45    | MAX       |

| A1     | 0.10    | 0.10    | ±0.05     |

| A2     | 1.14    | 1.14    | ±0.15     |

| b      | 0.40    | 0.40    | ±0.05     |

| С      | 0.14    | 0.14    | ±0.06     |

| D      | 2.90    | 2.90    | Basic     |

| E      | 2.80    | 2.80    | Basic     |

| E1     | 1.60    | 1.60    | Basic     |

| е      | 0.95    | 0.95    | Basic     |

| e1     | 1.90    | 1.90    | Basic     |

| L      | 0.45    | 0.45    | ±0.10     |

| L1     | 0.60    | 0.60    | Reference |

| N      | 5       | 6       | Reference |

Rev. F 2/07

#### NOTES:

- 1. Plastic or metal protrusions of 0.25mm maximum per side are not included.

- 2. Plastic interlead protrusions of 0.25mm maximum per side are not included.

- 3. This dimension is measured at Datum Plane "H".

- 4. Dimensioning and tolerancing per ASME Y14.5M-1994.

- 5. Index area Pin #1 I.D. will be located within the indicated zone (SOT23-6 only).

- 6. SOT23-5 version has no center lead (shown as a dashed line).

For additional products, see www.intersil.com/product\_tree

Intersil products are manufactured, assembled and tested utilizing ISO9000 quality systems as noted in the quality certifications found at <a href="https://www.intersil.com/design/quality">www.intersil.com/design/quality</a>

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com