# BIPOLAR ANALOG INTEGRATED CIRCUIT UPC3223TB

# 5 V, SILICON MMIC MEDIUM OUTPUT POWER AMPLIFIER

#### DESCRIPTION

The  $\mu$ PC3223TB is a silicon monolithic IC designed as IF amplifier for DBS tuners. This IC is manufactured using our 30 GHz f<sub>max</sub> UHS0 (<u>U</u>Itra <u>High Speed</u> Process) silicon bipolar process.

#### FEATURES

- Wideband response : fu = 3.2 GHz TYP. @ 3 dB bandwidth

- Medium output power: Po (sat) = +12.0 dBm @ f = 1.0 GHz

- : Po (sat) = +9.0 dBm @ f = 2.2 GHz

- High linearity : Po(1 dB) = +6.5 dBm @ f = 1.0 GHz

- : Po (1 dB) = +5.0 dBm @ f = 2.2 GHz

- Power gain : G<sub>P</sub> = 23.0 dB TYP. @ f = 1.0 GHz

: G<sub>P</sub> = 23.0 dB TYP. @ f = 2.2 GHz

- Supply voltage : Vcc = 4.5 to 5.5 V

- Port impedance : input/output 50  $\Omega$

#### APPLICATION

• IF amplifiers in DBS converters etc.

#### **ORDERING INFORMATION (Solder Contains Lead)**

| Part Number  | Package              | Marking | Supplying Form                                                                                                               |

|--------------|----------------------|---------|------------------------------------------------------------------------------------------------------------------------------|

| μPC3223TB-E3 | 6-pin super minimold | СЗЈ     | <ul> <li>Embossed tape 8 mm wide</li> <li>1, 2, 3 pins face the perforation side of tape</li> <li>Qty 3 kpcs/reel</li> </ul> |

#### **ORDERING INFORMATION (Pb-Free)**

| Part Number    | Package              | Marking | Supplying Form                                                                                                               |

|----------------|----------------------|---------|------------------------------------------------------------------------------------------------------------------------------|

| μPC3223TB-E3-A | 6-pin super minimold | C3J     | <ul> <li>Embossed tape 8 mm wide</li> <li>1, 2, 3 pins face the perforation side of tape</li> <li>Qty 3 kpcs/reel</li> </ul> |

**Remark** To order evaluation samples, contact your nearby sales office. Part number for sample order: μPC3223TB-A

Caution: Observe precautions when handling because these devices are sensitive to electrostatic discharge

The information in this document is subject to change without notice. Before using this document, please confirm that this is the latest version.

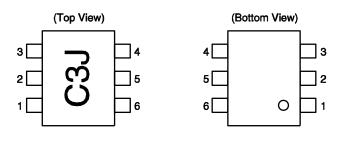

#### **PIN CONNECTIONS**

| Pin No. | Pin Name |

|---------|----------|

| 1       | INPUT    |

| 2       | GND      |

| 3       | GND      |

| 4       | OUTPUT   |

| 5       | GND      |

| 6       | Vcc      |

|         |          |

PRODUCT LINE-UP OF 5 V-BIAS SILICON MMIC MEDIUM OUTPUT AMPLIFIER (TA = +25°C, f = 1 GHz, Vcc = Vout = 5.0 V, Zs = ZL = 50  $\Omega$ )

| Part No.  | fu<br>(GHz) | Po <sub>(sat)</sub><br>(dBm) | G <sub>P</sub><br>(dB) | NF<br>(dB) | lcc<br>(mA) | Package              | Marking |

|-----------|-------------|------------------------------|------------------------|------------|-------------|----------------------|---------|

| μPC2708TB | 2.9         | +10.0                        | 15                     | 6.5        | 26          | 6-pin super minimold | C1D     |

| μPC2709TB | 2.3         | +11.5                        | 23                     | 5.0        | 25          |                      | C1E     |

| μPC2710TB | 1.0         | +13.5                        | 33                     | 3.5        | 22          |                      | C1F     |

| μPC2776TB | 2.7         | +8.5                         | 23                     | 6.0        | 25          |                      | C2L     |

| μPC3223TB | 3.2         | +12.0                        | 23                     | 4.5        | 19          |                      | C3J     |

Remark Typical performance. Please refer to ELECTRICAL CHARACTERISTICS in detail.

#### PIN EXPLANATIONS

| PIN<br>No.  | Pin Name | Applied<br>Voltage (V)                                       | Pin Voltage (V)<br>Note | Function and Applications                                                                                                                                                                                                                                                                            |

|-------------|----------|--------------------------------------------------------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1           | INPUT    | _                                                            | 0.96                    | Signal input pin.<br>A internal matching circuit, configured with resistors, enables 50 $\Omega$<br>connection over a wide band.<br>A multi-feedback circuits is designed to cancel the deviations of hFE and<br>resistance.<br>This pin must be coupled to signal source with capacitor for DC cut. |

| 4           | OUTPUT   | Voltage as<br>same as Vcc<br>through<br>external<br>inductor | _                       | Signal output pin.<br>The inductor must be attached between Vcc and output pins to supply<br>current to the internal output transistors.                                                                                                                                                             |

| 6           | Vcc      | 4.5 to 5.5                                                   | _                       | Power suplly pin.<br>Witch biases the internal input transistor. This pin should be externally<br>equipped with bypass capacitor to minimize its impedance.                                                                                                                                          |

| 2<br>3<br>5 | GND      | 0                                                            | _                       | Ground pin.<br>This pin should be connected to system ground with minimum inductance.<br>Ground pattern on the board should be formed as wide as possible.<br>All the ground pins must be connected together with wide ground pattern to<br>decrease impedance difference.                           |

~

Note Pin Voltage is measured at Vcc = 5.0 V

#### ABSOLUTE MAXIMUM RATINGS

| Parameter                     | Symbol | Conditions                          | Ratings     | Unit |

|-------------------------------|--------|-------------------------------------|-------------|------|

| Supply Voltage                | Vcc    | T <sub>A</sub> = +25°C, Pin 4 and 6 | 6.0         | V    |

| Total Circuit Current         | Icc    | T <sub>A</sub> = +25°C              | 40          | mA   |

| Power Dissipation             | PD     | T <sub>A</sub> = +85°C <b>Note</b>  | 270         | mW   |

| Operating Ambient Temperature | TA     |                                     | -40 to +85  | °C   |

| Storage Temperature           | Tstg   |                                     | -55 to +150 | °C   |

| Input Power                   | Pin    | T <sub>A</sub> = +25°C              | +10         | dBm  |

Note Mounted on double-sided copper-clad  $50 \times 50 \times 1.6$  mm epoxy glass PWB

#### RECOMMENDED OPERATING RANGE

| Parameter                     | Symbol | Conditions                                         | MIN. | TYP. | MAX. | Unit |

|-------------------------------|--------|----------------------------------------------------|------|------|------|------|

| Supply Voltage                | Vcc    | The same voltage should be applied to pin 4 and 6. | 4.5  | 5.0  | 5.5  | V    |

| Operating Ambient Temperature | TA     |                                                    | -40  | +25  | +85  | °C   |

# ELECTRICAL CHARACTERISTICS (TA = +25°C, Vcc = Vout = 5.0 V, Zs = ZL = 50 $\Omega$ )

| Parameter                       | Symbol    | Test Conditions                                 | MIN. | TYP.  | MAX. | Unit |

|---------------------------------|-----------|-------------------------------------------------|------|-------|------|------|

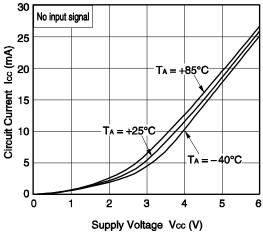

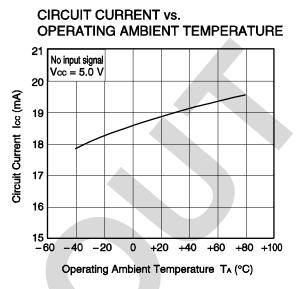

| Circuit Current                 | lcc       | No input signal                                 | 15.0 | 19.0  | 24.0 | mA   |

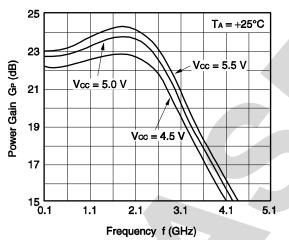

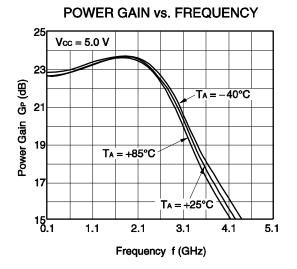

| Power Gain                      | Gp        | $f = 1.0 \text{ GHz}, P_{in} = -30 \text{ dBm}$ | 20.5 | 23.0  | 25.5 | dB   |

|                                 |           | $f = 2.2 \text{ GHz}, P_{in} = -30 \text{ dBm}$ | 20.0 | 23.0  | 26.0 |      |

| Saturated Output Power          | Po (sat)  | $f = 1.0 \text{ GHz}, P_{in} = -5 \text{ dBm}$  | +9.0 | +12.0 | -    | dBm  |

|                                 |           | f = 2.2 GHz, Pin = -5 dBm                       | +6.0 | +9.0  | -    |      |

| Gain 1 dB Compression Output    | PO (1 dB) | f = 1.0 GHz                                     | +4.5 | +6.5  | -    | dBm  |

| Power                           |           | f = 2.2 GHz                                     | +3.0 | +5.0  | -    |      |

| Noise Figure                    | NF        | f = 1.0 GHz                                     | —    | 4.5   | 6.0  | dB   |

|                                 |           | f = 2.2 GHz                                     | -    | 4.0   | 5.5  |      |

| Upper Limit Operating Frequency | fu        | 3 dB down below flat gain at f = 0.1 GHz        | 2.8  | 3.2   | I    | GHz  |

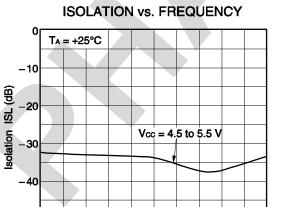

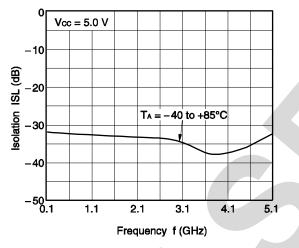

| Isolation                       | ISL       | f = 1.0 GHz, P <sub>in</sub> = -30 dBm          | 28.0 | 33.0  | -    | dB   |

|                                 |           | f = 2.2 GHz, P <sub>in</sub> = -30 dBm          | 28.0 | 33.0  | -    |      |

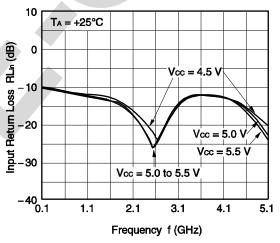

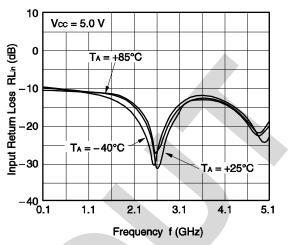

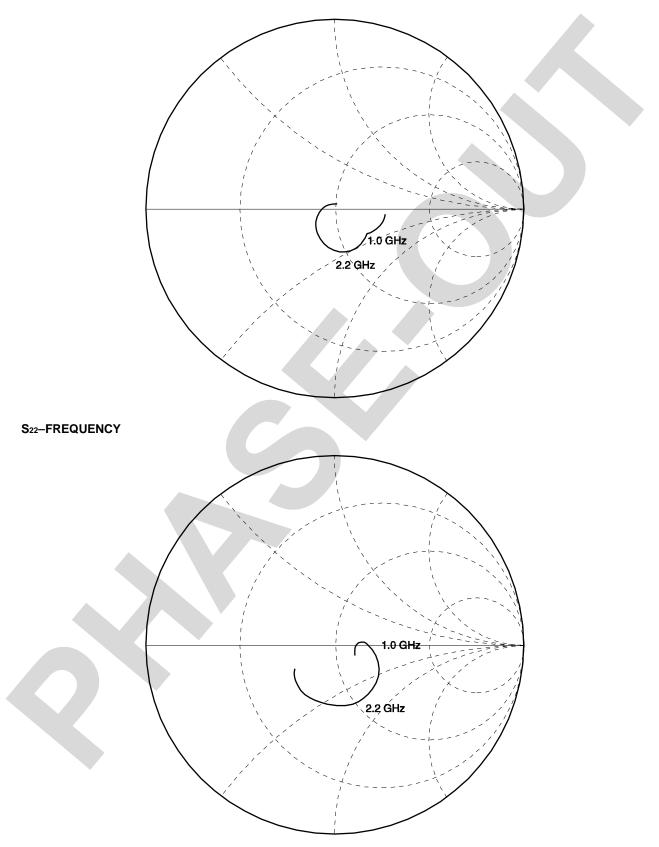

| Input Return Loss               | RLin      | f = 1.0 GHz, P <sub>in</sub> = -30 dBm          | 9.0  | 12.0  | -    | dB   |

|                                 |           | f = 2.2 GHz, P <sub>in</sub> = -30 dBm          | 12.0 | 17.5  | -    |      |

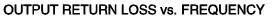

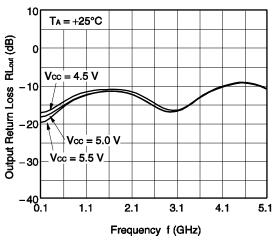

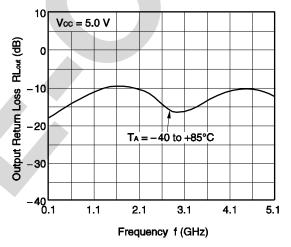

| Output Return Loss              | RLout     | f = 1.0 GHz, P <sub>in</sub> = -30 dBm          | 9.0  | 12.0  | -    | dB   |

|                                 |           | f = 2.2 GHz, P <sub>in</sub> = -30 dBm          | 9.0  | 12.0  | -    |      |

| Gain Flatness                   | ⊿Gp       | f = 0.1 to 2.2 GHz                              | _    | ±0.9  | -    | dB   |

# OTHER CHARACTERISTICS, FOR REFERENCE PURPOSES ONLY

(TA = +25°C, Vcc = Vout = 5.0 V, Zs = ZL = 50  $\Omega$ )

| Parameter              | Symbol | Test Conditions | Reference Value | Unit |

|------------------------|--------|-----------------|-----------------|------|

| Output Intercept Point | OIP₃   | f = 1.0 GHz     | +17.8           | dBm  |

|                        |        | f = 2.2 GHz     | +14.8           |      |

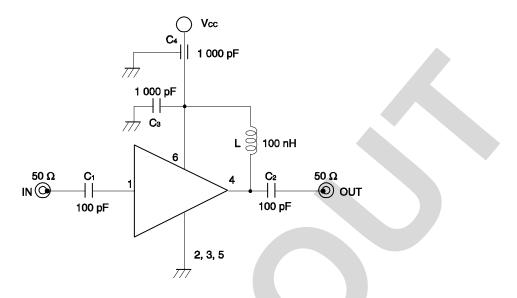

#### TEST CIRCUIT

The application circuits and their parameters are for reference only and are not intended for use in actual design-ins.

| MEASURING ELECTRICAL CHARACTERISTICS |                        |          |  |  |  |

|--------------------------------------|------------------------|----------|--|--|--|

|                                      | Туре                   | Value    |  |  |  |

| C1, C2                               | Chip Capacitor         | 100 pF   |  |  |  |

| C₃                                   | Chip Capacitor         | 1 000 pF |  |  |  |

| C4                                   | Feed-through Capacitor | 1 000 pF |  |  |  |

| L                                    | Chip Inductor          | 100 nH   |  |  |  |

#### COMPONENTS OF TEST CIRCUIT FOR MEASURING ELECTRICAL CHARACTERISTICS

#### INDUCTOR FOR THE OUTPUT PIN

The internal output transistor of this IC consumes 20 mA, to output medium power. To supply current for output transistor, connect an inductor between the Vcc pin (pin 6) and output pin (pin 4). Select large value inductance, as listed above.

The inductor has both DC and AC effects. In terms of DC, the inductor biases the output transistor with minimum voltage drop to output enable high level. In terms of AC, the inductor makes output-port impedance higher to get enough gain. In this case, large inductance and Q is suitable.

#### CAPACITORS FOR THE Vcc, INPUT AND OUTPUT PINS

Capacitors of 1000 pF are recommendable as the bypass capacitor for the Vcc pin and the coupling capacitors for the input and output pins.

The bypass capacitor connected to the Vcc pin is used to minimize ground impedance of Vcc pin. So, stable bias can be supplied against Vcc fluctuation.

The coupling capacitors, connected to the input and output pins, are used to cut the DC and minimize RF serial impedance. Their capacitances are therefore selected as lower impedance against a 50  $\Omega$  load. The capacitors thus perform as high pass filters, suppressing low frequencies to DC.

To obtain a flat gain from 100 MHz upwards, 1 000 pF capacitors are used in the test circuit. In the case of under 10 MHz operation, increase the value of coupling capacitor such as 10 000 pF. Because the coupling capacitors are determined by equation,  $C = 1/(2 \pi Rfc)$ .

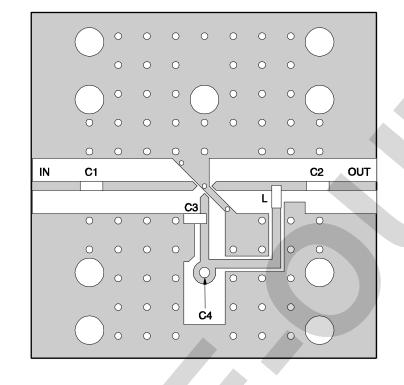

#### ILLUSTRATION OF THE TEST CIRCUIT ASSEMBLED ON EVALUATION BOARD

#### COMPONENT LIST

|        | Value    |  |

|--------|----------|--|

| C1, C2 | 100 pF   |  |

| C3, C4 | 1 000 pF |  |

| L      | 100 nH   |  |

#### Notes

- 1.  $30 \times 30 \times 0.4$  mm double sided copper clad polyimide board.

- 2. Back side: GND pattern

- 3. Solder plated on pattern

- 4. O: Through holes

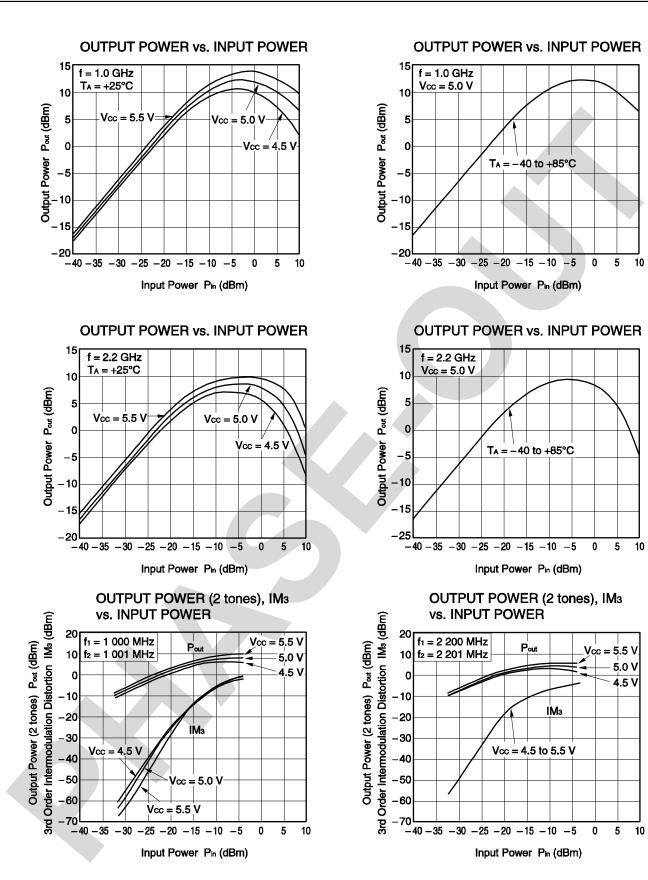

#### TYPICAL CHARACTERISTICS (TA = $+25^{\circ}C$ , unless otherwise specified)

**POWER GAIN vs. FREQUENCY**

Frequency f (GHz)

2.1

3.1

4.1

5.1

**INPUT RETURN LOSS vs. FREQUENCY**

-50L 0.1

1.1

**ISOLATION vs. FREQUENCY**

Remark The graphs indicate nominal characteristics.

**INPUT RETURN LOSS vs. FREQUENCY**

**OUTPUT RETURN LOSS vs. FREQUENCY**

Remark The graphs indicate nominal characteristics.

## S-PARAMETERS (TA = +25°C, Vcc = Vout = 5.0 V)

#### S11-FREQUENCY

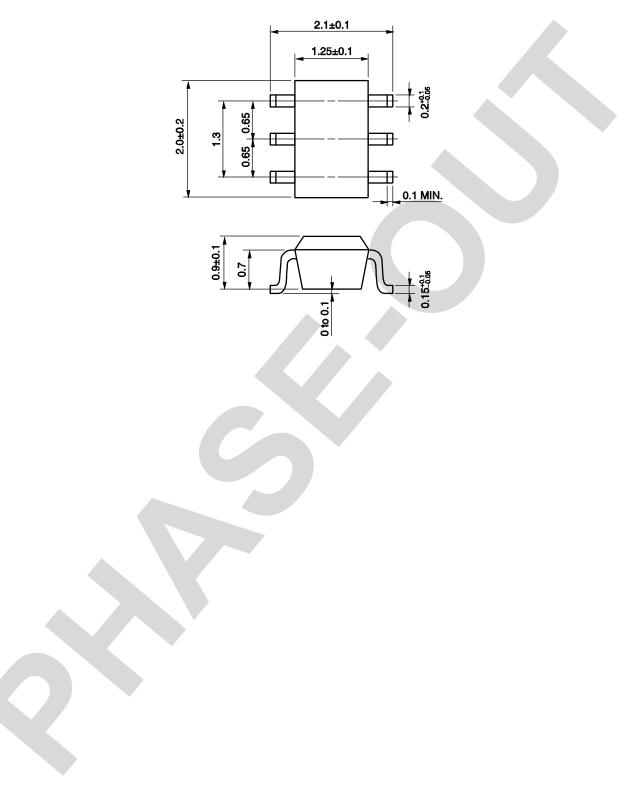

### PACKAGE DIMENSIONS

## 6-PIN SUPER MINIMOLD (UNIT: mm)

#### NOTES ON CORRECT USE

- (1) Observe precautions for handling because of electro-static sensitive devices.

- (2) Form a ground pattern as widely as possible to minimize ground impedance (to prevent undesired oscillation).

All the ground pins must be connected together with wide ground pattern to decrease impedance difference.

- (3) The bypass capacitor should be attached to Vcc line.

- (4) The inductor must be attached between Vcc and output pins. The inductance value should be determined in accordance with desired frequency.

- (5) The DC cut capacitor must be each attached to input and output pin.

#### **RECOMMENDED SOLDERING CONDITIONS**

This product should be soldered and mounted under the following recommended conditions. For soldering methods and conditions other than those recommended below, contact your nearby sales office.

| Soldering Method | Soldering Conditions                                                                                                                                                                                                                                                       |                                                                                                                          | Condition Symbol |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|------------------|

| Infrared Reflow  | Peak temperature (package surface temperature)<br>Time at peak temperature<br>Time at temperature of 220°C or higher<br>Preheating time at 120 to 180°C<br>Maximum number of reflow processes                                                                              | : 260°C or below<br>: 10 seconds or less<br>: 60 seconds or less<br>: 120±30 seconds<br>: 3 times                        | IR260            |

| Wave Soldering   | Maximum chlorine content of rosin flux (% mass)<br>Peak temperature (molten solder temperature)<br>Time at peak temperature<br>Preheating temperature (package surface temperature)<br>Maximum number of flow processes<br>Maximum chlorine content of rosin flux (% mass) | : 0.2%(Wt.) or below<br>: 260°C or below<br>: 10 seconds or less<br>: 120°C or below<br>: 1 time<br>: 0.2%(Wt.) or below | WS260            |

| Partial Heating  | Peak temperature (pin temperature)<br>Soldering time (per side of device)<br>Maximum chlorine content of rosin flux (% mass)                                                                                                                                               | : 350°C or below<br>: 3 seconds or less<br>: 0.2%(Wt.) or below                                                          | HS350            |

Caution Do not use different soldering methods together (except for partial heating).

#### NOTICE

- 1. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. California Eastern Laboratories and Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 2. California Eastern Laboratories has used reasonable care in preparing the information included in this document, but California Eastern Laboratories does not warrant that such information is error free. California Eastern Laboratories and Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 3. California Eastern Laboratories and Renesas Electronics do not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of California Eastern Laboratories or Renesas Electronics or others.

- 4. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part. California Eastern Laboratories and Renesas Electronics assume no responsibility for any losses incurred by you or third parties arising from such alteration, modification, copy or otherwise misappropriation of Renesas Electronics product.

- 5. Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots etc. "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; and safety equipment etc. Renesas Electronics products are neither intended nor authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems, surgical implantations etc.), or may cause serious property damages (nuclear reactor control systems, military equipment etc.). You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application for which it is not intended. California Eastern Laboratories and Renesas Electronics product for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for which the product is not intended by California Eastern Laboratories or Renesas Electronics.

- 6. You should use the Renesas Electronics products described in this document within the range specified by California Eastern Laboratories, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. California Eastern Laboratories shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 7. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or systems manufactured by you.

- 8. Please contact a California Eastern Laboratories sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. California Eastern Laboratories and Renesas Electronics assume no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 9. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You should not use Renesas Electronics products or technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. When exporting the Renesas Electronics products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations.

- 10. It is the responsibility of the buyer or distributor of California Eastern Laboratories, who distributes, disposes of, or otherwise places the Renesas Electronics product with a third party, to notify such third party in advance of the contents and conditions set forth in this document, California Eastern Laboratories and Renesas Electronics assume no responsibility for any losses incurred by you or third parties as a result of unauthorized use of Renesas Electronics products.

- This document may not be reproduced or duplicated in any form, in whole or in part, without prior written consent of California Eastern Laboratories.

Please contact a California Eastern Laboratories sales office if you have any questions regarding the information contained in this document or Renesas

- Electronics products, or if you have any other inquiries.

**NOTE 1:** "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries. **NOTE 2:** "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics. **NOTE 3:** Products and product information are subject to change without notice.

CEL Headquarters • 4590 Patrick Henry Drive, Santa Clara, CA 95054 • Phone (408) 919-2500 • www.cel.com

For a complete list of sales offices, representatives and distributors, Please visit our website: www.cel.com/contactus