# Analog Devices Welcomes Hittite Microwave Corporation

NO CONTENT ON THE ATTACHED DOCUMENT HAS CHANGED

# **HMC871\* Product Page Quick Links**

Last Content Update: 11/01/2016

# Comparable Parts

View a parametric search of comparable parts

# Evaluation Kits <a> □</a>

• HMC871LC5 Evaluation Board

# Documentation <a>□</a>

### **Data Sheet**

• HMC871 Data Sheet

# Reference Materials 🖵

### **Quality Documentation**

- Package/Assembly Qualification Test Report: LC5, LC5A (QTR: 2014-00384 REV: 01)

- Semiconductor Qualification Test Report: PHEMT-F (QTR: 2013-00269)

### **Technical Articles**

Powerful Optical Modulator Driver Family for Metro and Long Haul 40G/100G Applications

# Design Resources -

- HMC871 Material Declaration

- · PCN-PDN Information

- · Quality And Reliability

- · Symbols and Footprints

# Discussions <a>□</a>

View all HMC871 EngineerZone Discussions

# Sample and Buy 🖵

Visit the product page to see pricing options

# Technical Support <a> □</a>

Submit a technical question or find your regional support number

<sup>\*</sup> This page was dynamically generated by Analog Devices, Inc. and inserted into this data sheet. Note: Dynamic changes to the content on this page does not constitute a change to the revision number of the product data sheet. This content may be frequently modified.

### Typical Applications

The HMC871LC5 is ideal for:

- SONET OC-192 & SDH-STM-64 Transmission Systems

- 10 GbE Transmitters

- 10 Gbps VSR Modules

- Pre-driver for 40 Gbps DQPSK Modules

- Broadband Gain Block for Test & Measurement Equipment

### **Features**

Wide Supply Range from 5V to 8V

Adjustable Output Amplitude up to 4 Vp-p

Low Additive RMS Jitter, <300 fs

Low DC Power Consumption,

0.25W for Vout = 2.5 Vp-p at Vdd = 5V

Cross Point Adjustment

32 Lead 5x5mm SMT Package: 25mm<sup>2</sup>

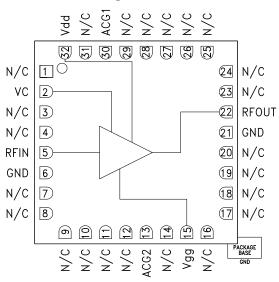

### **Functional Diagram**

### **General Description**

The HMC871LC5 is a GaAs MMIC PHEMT Distributed Driver Amplifier packaged in a leadless 5x5mm surface mount package. The amplifier operates between DC and 20 GHz and provides 15 dB of gain. The output swing cross point is adjustable and saturated output swing is 4Vp-p. Gain flatness is excellent at  $\pm 0.5$  dB as well as very low additive RMS jitter of 300 fs for 10 Gbps operation. The HMC871LC5 provides VSR and Gigabit Ethernet designers with scalable power dissipation for varying output drive requirements (<0.25W at Vout = 2.5 Vp-p and <0.6W at Vout = 4 Vp-p). The HMC871-LC5 has a very wide supply (Vdd) operating range from +5V to +8V and the I/Os are internally matched to 50 Ohms.

# Electrical Specifications, $T_{\Delta} = +25^{\circ}$ C, Vdd = 8V, VC = 0.5V, $Idd = 75mA^{*}$

| Parameter                       | Conditions                                                                 | Min.           | Тур.             | Max.          | Units          |

|---------------------------------|----------------------------------------------------------------------------|----------------|------------------|---------------|----------------|

| Gain                            | Frequency = 1 - 8 GHz<br>Frequency = 8 - 16 GHz<br>Frequency = 16 - 20 GHz | 13<br>12<br>10 | 16<br>15<br>13.5 |               | dB<br>dB<br>dB |

| Small Signal Bandwidth          | 3-dB cutoff                                                                |                | 17.5             |               | GHz            |

| Input Return Loss               | Frequency = 1 - 10 GHz<br>Frequency = 10 - 20 GHz                          |                | 20<br>10         |               | dB<br>dB       |

| Output Return Loss              | Frequency = 1 - 10 GHz<br>Frequency = 10 - 20 GHz                          |                | 15<br>10         |               | dB<br>dB       |

| Gain Variation Over Temperature | Frequency = 1 - 10 GHz<br>Frequency = 10 - 20 GHz                          |                | 0.016<br>0.025   | 0.022<br>0.36 | dB/°C<br>dB/°C |

| Group Delay Variation           | Frequency = 1 - 12 GHz                                                     |                | ±15              |               | ps             |

| Saturated Output Power (Psat)   | Frequency = 1 - 12 GHz<br>Frequency = 12 - 20 GHz                          |                | 18<br>16         |               | dBm<br>dBm     |

<sup>\*</sup> Adjust Vgg between -1V to 0V to achieve Idd = 75 mA typical.

# Electrical Specifications, $T_A = +25^{\circ}$ C, Vdd = 8V, VC = 0.5V, $Idd = 75mA^*$ Continued

| Parameter                                | Conditions                                        | Min.     | Тур.       | Max. | Units      |

|------------------------------------------|---------------------------------------------------|----------|------------|------|------------|

| Output Power for 1 dB Compression (P1dB) | Frequency = 1 - 12 GHz<br>Frequency = 12 - 20 GHz | 14<br>11 | 16.5<br>14 |      | dBm<br>dBm |

| Rise Time [1]                            | 20% - 80%                                         |          | 20         |      | ps         |

| Fall Time [1]                            | 20% - 80%                                         |          | 19         |      | ps         |

| Additive RMS Jitter [2]                  |                                                   |          |            | 300  | fs         |

| Supply Current (Idd) (Vgg = -0.7V Typ.)  |                                                   |          | 75         |      | mA         |

| Bias Current Adjust (Vgg)                |                                                   | -2       |            | 0    | V          |

| Output Voltage Adjust (VC)               |                                                   | 0        |            | 2    | V          |

<sup>[1]</sup> Data input = 22.5 Gbps NRZ PRBS  $2^{23}$ -1 pattern, 0.5 Vp-p.

# Electrical Specifications, $T_A = +25^{\circ}$ C, Vdd = 5V, VC = 0.5V, $Idd = 50mA^*$

| Parameter                                | Conditions                                                                 | Min.            | Тур.               | Max.           | Units          |

|------------------------------------------|----------------------------------------------------------------------------|-----------------|--------------------|----------------|----------------|

| Gain                                     | Frequency = 1 - 8 GHz<br>Frequency = 8 - 16 GHz<br>Frequency = 16 - 20 GHz | 11.5<br>11<br>8 | 14.5<br>14<br>11.5 |                | dB<br>dB<br>dB |

| Small Signal Bandwidth                   | 3-dB cutoff                                                                |                 | 18.5               |                | GHz            |

| Input Return Loss                        | Frequency = 1 - 10 GHz<br>Frequency = 10 - 20 GHz                          |                 | 15<br>10           |                | dB<br>dB       |

| Output Return Loss                       | Frequency = 1 - 10 GHz<br>Frequency = 10 - 20 GHz                          |                 | 10<br>10           |                | dB<br>dB       |

| Gain Variation Over Temperature          | Frequency = 1 - 10 GHz<br>Frequency = 10 - 20 GHz                          |                 | 0.017<br>0.024     | 0.024<br>0.034 | dB/°C<br>dB/°C |

| Group Delay Variation                    | Frequency = 1 - 12 GHz                                                     |                 | ±15                |                | deg            |

| Saturated Output Power (Psat)            | Frequency = 1 - 12 GHz<br>Frequency = 12 - 20 GHz                          |                 | 14<br>11           |                | dBm<br>dBm     |

| Output Power for 1 dB Compression (P1dB) | Frequency = 1 - 12 GHz<br>Frequency = 12 - 20 GHz                          | 8<br>4          | 11<br>8            |                | dBm<br>dBm     |

| Rise Time [1]                            | 20% - 80%                                                                  |                 | 20                 |                | ps             |

| Fall Time [1]                            | 20% - 80%                                                                  |                 | 20                 |                | ps             |

| Additive RMS Jitter [2]                  |                                                                            |                 |                    | 300            | fs             |

| Supply Current (Idd) (Vgg = -0.8V Typ.)  |                                                                            |                 | 50                 |                | mA             |

| Bias Current Adjust (Vgg)                |                                                                            | -2              |                    | 0              | ٧              |

| Output Voltage Adjust (VC)               |                                                                            | 0               |                    | 2              | V              |

<sup>[1]</sup> Data input = 22.5 Gbps NRZ PRBS  $2^{23}$ -1 pattern, 0.5 Vp-p.

<sup>[2]</sup> RMS jitter is calculated with 22.5 Gbps 10101... pattern.

<sup>\*</sup> Adjust Vgg between -1V to 0V to achieve Idd = 75mA typical.

<sup>[2]</sup> RMS jitter is calculated with 22.5 Gbps 10101... pattern.

<sup>\*</sup> Adjust Vgg between -1V to 0V to achieve Idd = 50mA typical.

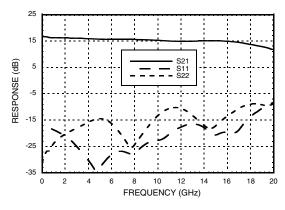

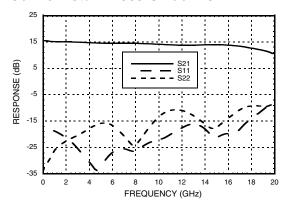

### Gain & Return Loss @ Vdd = 8V

### Gain & Return Loss @ Vdd = 5V

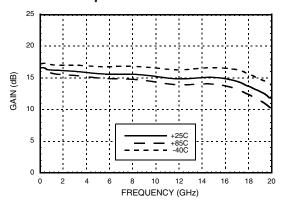

Gain vs. Temperature @ Vdd = 8V

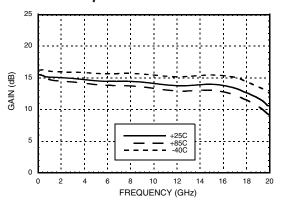

Gain vs. Temperature @ Vdd = 5V

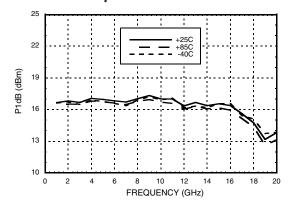

P1dB vs. Temperature @ Vdd = 8V

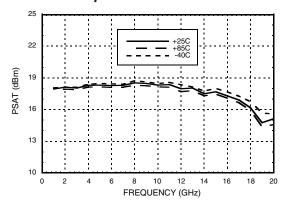

Psat vs. Temperature @ Vdd = 8V

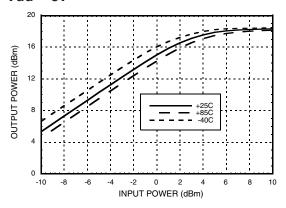

# Output Power vs. Input Power @ 10 GHz, Vdd = 8V

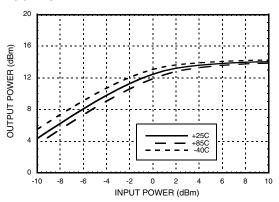

Output Power vs. Input Power @ 10 GHz, Vdd = 5V

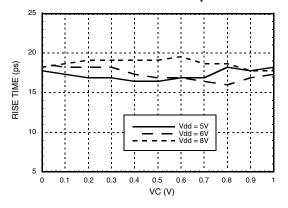

Rise Time vs. Vdd @ 22.5 Gbps [2]

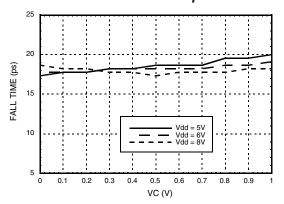

Fall Time vs. Vdd @ 22.5 Gbps [2]

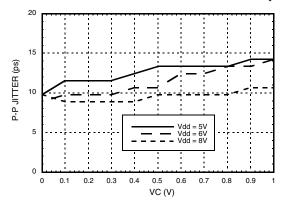

### Peak-to-Peak Jitter vs. Vdd @ 11.25 Gbps [1]

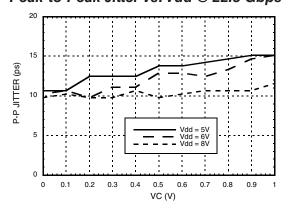

Peak-to-Peak Jitter vs. Vdd @ 22.5 Gbps [2]

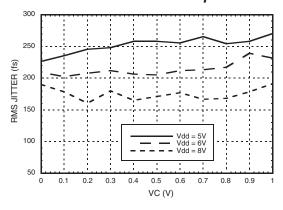

[1] Data input = 11.25 Gbps NRZ PRBS 2<sup>23</sup>-1 pattern, 0.5 Vp-p.

[2] Data input = 22.5 Gbps NRZ PRBS  $2^{23}$ -1 pattern, 0.5 Vp-p.

### RMS Jitter vs. Vdd @ 22.5 Gbps [4]

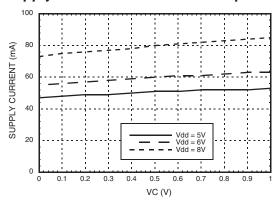

### Supply Current vs. Vdd @ 22.5 Gbps [3]

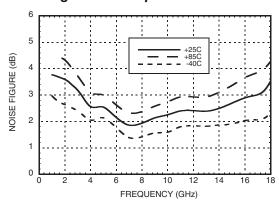

### Noise Figure vs. Temperature @ Vdd = 8V

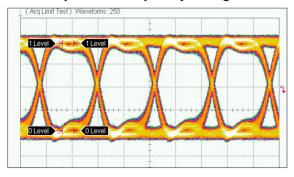

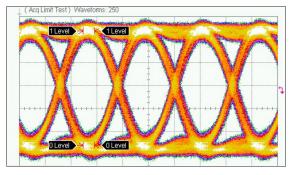

### 11.25 Gbps NRZ Output Eye Diagrams

|            | M               |         |         |       |

|------------|-----------------|---------|---------|-------|

|            | Current Min Max |         |         | Units |

| Jitter p-p | 9.78 ps         | 7.11 ps | 9.78 ps | V     |

| Rise Time  | 19.6 ps         | 18.7 ps | 19.6 ps | ps    |

| Fall Time  | 19.6 ps         | 18.7 ps | 19.6 ps | ps    |

| Eye Amp    | 3.03 V          | 3.03 V  | 3.03 V  | ps    |

Time scale: 40 ps/div Amplitude scale: 800 mV/div

Vdd = 8V, Vin: 11.25 Gbps NRZ PRBS 231-1, 0.5 Vp-p Vout: 3.03Vp-p

[1] Data input = 11.25 Gbps NRZ PRBS 2<sup>23</sup>-1 pattern, 0.5 Vp-p. [3] Data input 22.5 Gbps NRZ PRBS 2<sup>23</sup>-1 pattern, 0.5 Vp-p.

[2] Source jitter was not de-embedded

[4] RMS jitter is measured with 22.5 Gbps 10101...pattern

### 11.25 Gbps NRZ Output Eye Diagrams

|            | M               | Measurements |          |       |

|------------|-----------------|--------------|----------|-------|

|            | Current Min Max |              |          | Units |

| Jitter p-p | 11.56 ps        | 8.89 ps      | 11.56 ps | V     |

| Rise Time  | 16.9 ps         | 16.9 ps      | 16.9 ps  | ps    |

| Fall Time  | 16.9 ps         | 16.9 ps      | 17.8 ps  | ps    |

| Eye Amp    | 2.60 V          | 2.60 V       | 2.60 V   | ps    |

Time scale: 40 ps/div Amplitude scale: 600 V/div

Vdd = 5V, Vin: 11.25Gbps NRZ PRBS 2<sup>31</sup>-1, 0.5V p-p,

Vout: 2.60Vp-p

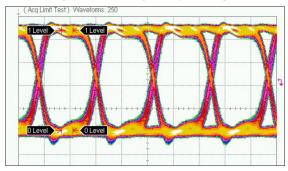

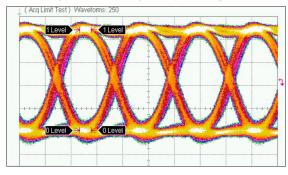

### 22.5 Gbps NRZ Output Eye Diagrams

|            | N               | Measurements |          |       |

|------------|-----------------|--------------|----------|-------|

|            | Current Min Max |              |          | Units |

| Jitter p-p | 9.333 ps        | 8.000 ps     | 9.333 ps | ٧     |

| Rise Time  | 17.78 ps        | 17.78 ps     | 18.67 ps | ps    |

| Fall Time  | 17.78 ps        | 17.33 ps     | 18.67 ps | ps    |

| Eye Amp    | 3.00 V          | 3.00 V       | 3.00 V   | ps    |

Time scale: 20 ps/div Amplitude scale: 800 mV/div

$Vdd = 8V, \ Vin: 22.5 \ Gbps \ NRZ \ PRBS \ 2^{31} - 1, \ 0.5 \ Vp - p$

Vout: 3.00Vp-p

### 22.5 Gbps NRZ Output Eye Diagrams

|            | M         | Measurements    |           |    |  |

|------------|-----------|-----------------|-----------|----|--|

|            | Current   | Current Min Max |           |    |  |

| Jitter p-p | 10.667 ps | 8.889 ps        | 11.556 ps | V  |  |

| Rise Time  | 16.00 ps  | 10.67 ps        | 16.00 ps  | ps |  |

| Fall Time  | 17.78 ps  | 16.89 ps        | 17.78 ps  | ps |  |

| Eye Amp    | 2.63 V    | 2.63 V          | 2.64 V    | ps |  |

Time scale: 20 ps/div Amplitude scale: 800 V/div

Vdd = 5V, Vin: 22.5Gbps NRZ PRBS 2<sup>31</sup>-1, 0.5V p-p,

Vout: 2.63Vp-p

### **Absolute Maximum Ratings**

| Drain Bias Voltage (Vdd)                                         | +9V                 |

|------------------------------------------------------------------|---------------------|

| Gate Bias Voltage (Vgg)                                          | -2 to 0V            |

| Control Bias Voltage (VC)                                        | (Vdd -8) to Vdd (V) |

| RF Input Power (RFIN)(Vdd = +8 Vdc)                              | +10 dBm             |

| Channel Temperature                                              | 175 °C              |

| Continuous Pdiss (T = 85 °C)<br>(derate 15.08 mW/°C above 85 °C) | 1.35 W              |

| Thermal Resistance (channel to ground paddle)                    | 66.31 °C/W          |

| Storage Temperature                                              | -65 to +150 °C      |

| Operating Temperature                                            | -40 to +85 °C       |

| ESD Sensitivity (HBM)                                            | Class 1A            |

### Typical Supply Current vs. Vdd

| Vdd (V) | Idd (mA)* | Power<br>Dissipation (W) |

|---------|-----------|--------------------------|

| +5      | 50        | 0.25                     |

| +6      | 60        | 0.36                     |

| +8      | 75        | 0.60                     |

<sup>\*</sup> Adjust Vgg between -1V and 0V to achieve Idd shown.

ELECTROSTATIC SENSITIVE DEVICE **OBSERVE HANDLING PRECAUTIONS**

### **Outline Drawing**

### **BOTTOM VIEW** 0.197±.005 PIN 32 .014 0.36 .009 0.24 013 [0.32] [5.00±.13] 32 25 REF σάσσσσοδ PIN 1 24 $\Box$ H871 0.197±.005 [5.00±.13] D D XXXX $\Box$ .022 [0.56] .017 [0.44] D D 8 17 16 138 [3.50] EXPOSED LOT NUMBER SQUARE GROUND 0.044 [1.12] .161 [4.10] PADDLE MAX NOTES: SEATING PLANE 1. PACKAGE BODY MATERIAL: ALUMINA -c-

- 2. LEAD AND GROUND PADDLE PLATING: 30-80 MICROINCHES GOLD OVER 50 MICROINCHES MINIMUM NICKEL.

- 3. DIMENSIONS ARE IN INCHES [MILLIMETERS].

- 4. LEAD SPACING TOLERANCE IS NON-CUMULATIVE.

- 5. PACKAGE WARP SHALL NOT EXCEED 0.05mm DATUM -C-

- 6. ALL GROUND LEADS AND GROUND PADDLE MUST BE SOLDERED TO PCB RF GROUND.

# Package Information

| Part N | umber | Package Body Material | Lead Finish      | MSL Rating | Package Marking [2] |

|--------|-------|-----------------------|------------------|------------|---------------------|

| HMC8   | 71LC5 | Alumina, White        | Gold over Nickel | MSL3 [1]   | H871<br>XXXX        |

<sup>[1]</sup> Max peak reflow temperature of 260 °C

<sup>[2] 4-</sup>Digit lot number XXXX

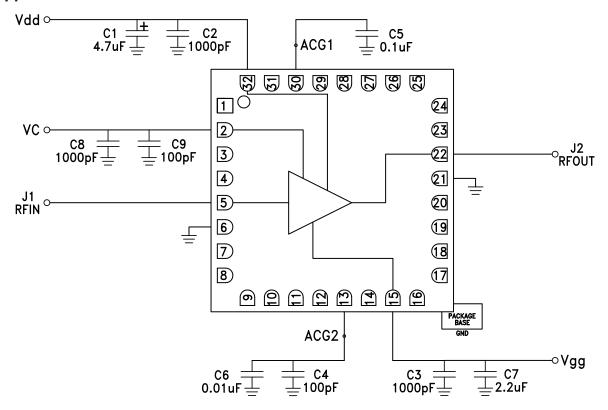

# **Pin Descriptions**

| Pin Number                                   | Function | Description                                                                                                                              | Interface Schematic |

|----------------------------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| 1, 3, 4, 7 - 12, 14,<br>16 - 20, 23 - 29, 31 | N/C      | The pins are not connected internally; however, all data shown herein was measured with these pins connected to RF/DC ground externally. |                     |

| 2                                            | VC       | Output voltage swing adjust. +0.5V should be applied for nominal operation.                                                              | vc o                |

| 5                                            | RFIN     | This pin is DC coupled and matched to 50 Ohms. DC blocking is required.                                                                  | RFIN ACG2           |

| 6, 21                                        | GND      | These pins and exposed package base must be connected to RF/DC ground.                                                                   | Ģ GND<br>—          |

| 13                                           | ACG2     | Low frequency termination. Attach bypass capacitor per application circuit herein.                                                       | RFIN ACG2           |

| 15                                           | Vgg      | Gate control for amplifier. Please follow "MMIC Amplifier Biasing Procedure" application note.                                           | Vggo                |

| 22                                           | RFOUT    | This pin is DC coupled<br>and matched to 50 Ohms.<br>DC blocking is required.                                                            | ACG1 RFOUT          |

| 30                                           | ACG1     | Low frequency termination. Attach bypass capacitor per application circuit herein.                                                       | ACG1 RFOUT          |

| 32                                           | Vdd      | Power supply for the amplifier. External bypass capacitors are required.                                                                 | Vdd 0~~~~           |

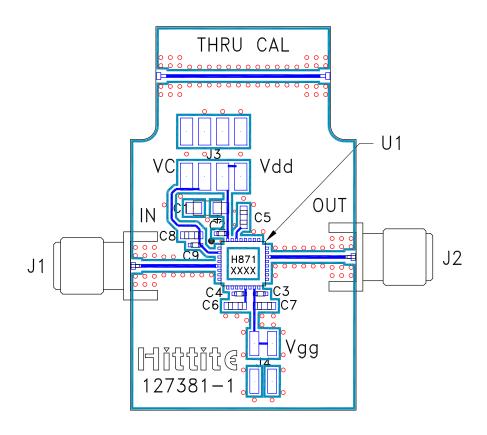

### **Evaluation PCB**

### List of Materials for Evaluation PCB 127517 [1]

| Item    | Description                  |  |

|---------|------------------------------|--|

| J1 - J2 | PCB Mount SMA Connector      |  |

| J3 - J4 | 2mm Molex Header             |  |

| C1      | 4.7 μF Capacitor, Tantalum   |  |

| C2, C3  | 1000 pF Capacitor, 0402 Pkg. |  |

| C4, C9  | 100 pF Capacitor, 0402 Pkg.  |  |

| C5      | 0.1 μF Capacitor, 0603 Pkg.  |  |

| C6      | 0.01 μF Capacitor, 0603 Pkg. |  |

| C7      | 2.2 μF Capacitor, 0603 Pkg.  |  |

| C8      | 1000 pF Capacitor, 0603 Pkg. |  |

| U1      | HMC871LC5, Modulator Driver  |  |

| PCB [2] | 127381 Evaluation PCB        |  |

[1] Reference this number when ordering complete evaluation PCB

[2] Circuit Board Material: Arlon 25FR or Rogers 4350

The circuit board used in the application should use RF circuit design techniques. Signal lines should have 50 Ohm impedance while the package ground leads and package bottom should be connected directly to the ground plane similar to that shown. A sufficient number of via holes should be used to connect the top and bottom ground planes. The evaluation board should be mounted to an appropriate heat sink. The evaluation circuit board shown is available from Hittite upon request.

### **Application Circuit**

### **Device Operation**

These devices are susceptible to damage from Electrostatic Discharge. Proper precautions should be observed during handling, assembly and test.

The input to this device should be AC-coupled. To provide the typical 4Vp-p output voltage swing, a 0.5Vp-p AC coupled input voltage swing is required.

### **Device Power Up Instructions**

- 1. Ground the device, no RF signal applied to device

- 2. Set Vgg to -2V (no drain current)

- 3. Set VC to +0.5V (no drain current)

- 4. Set Vdd to +5V or +8V (no drain current)

- 5. Adjust Vgg for Idd = 50mA (Vdd = 5V) or Idd = 75mA (Vdd = 8V)

- 6. Apply RF signal.

- Vgg may be varied between -1V and 0V to provide the desired eye crossing point percentage (i.e. 50% crosspoint) and a limited cross point control capability (±20%)

### **Device Power Down Instructions**

1. Reverse the sequence identified above in steps 1 through 6.