# High Performance 8-Bit Display Interface

AD9983A

### **FEATURES**

8-bit analog-to-digital converters

140 MSPS maximum conversion rate

Low PLL clock jitter at 140 MSPS

Automatic gain matching

Automated offset adjustment

2:1 input mux

Power-down via dedicated pin or serial register

4:4:4, 4:2:2, and DDR output format modes

Variable output drive strength

Odd/even field detection

External clock input

Regenerated Hsync output

Programmable output high impedance control

Hsyncs per Vsync counter

Pb-free package

### **APPLICATIONS**

Advanced TVs

Plasma display panels

LCDTV

HDTV

RGB graphics processing

LCD monitors and projectors

Scan converters

### **GENERAL DESCRIPTION**

The AD9983A is a complete 8-bit, 140 MSPS, monolithic analog interface optimized for capturing YPbPr video and RGB graphics signals. Its 140 MSPS encode rate capability and full power analog bandwidth of 300 MHz support all HDTV video modes up to 1080i and 720p as well as graphics resolutions up to SXGA ( $1280 \times 1024$  at 75 Hz).

The AD9983A includes a 140 MHz triple ADC with an internal reference, a PLL, and programmable gain, offset, and clamp control. The user provides only a 1.8 V power supply and an analog input. Three-state CMOS outputs can be powered from 1.8 V to 3.3 V.

The AD9983A on-chip PLL generates a sample clock from the tri-level sync (for YPbPr video) or the horizontal sync (for RGB graphics). Sample clock output frequencies range from 10 MHz to 140 MHz. With internal coast generation, the PLL maintains its output frequency in the absence of sync input. A 32-step

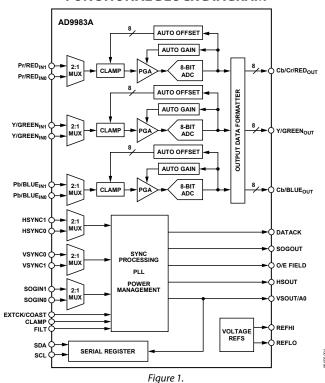

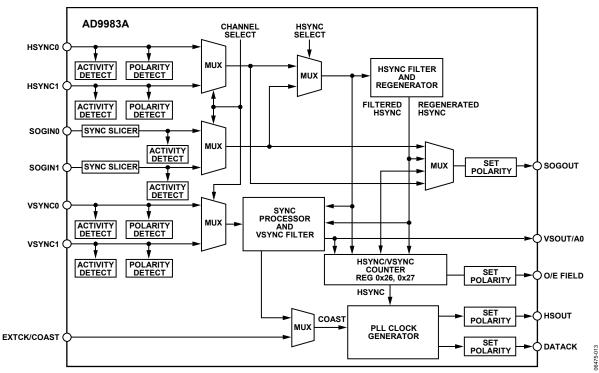

### **FUNCTIONAL BLOCK DIAGRAM**

sampling clock phase adjustment is provided. Output data, sync, and clock phase relationships are maintained.

The auto-offset feature can be enabled to automatically restore the signal reference levels and to automatically calibrate out any offset differences between the three channels. The auto channelto-channel gain matching feature can be enabled to minimize any gain mismatches between the three channels.

The AD9983A also offers full sync processing for composite sync and sync-on-green applications. A clamp signal is generated internally or may be provided by the user through the CLAMP input pin.

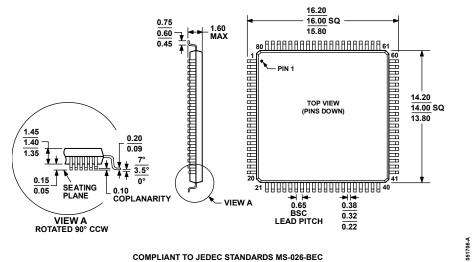

Fabricated in an advanced CMOS process, the AD9983A is provided in a space-saving 80-lead, Pb-free, LQFP surfacemount plastic package, and is specified over the  $0^{\circ}$ C to  $70^{\circ}$ C temperature range.

# **AD9983A\* Product Page Quick Links**

Last Content Update: 11/01/2016

# Comparable Parts

View a parametric search of comparable parts

# Evaluation Kits <a> □</a>

· AD9983A Evaluation Board

# Documentation <a>□</a>

# **Data Sheet**

AD9983A: High Performance 8-Bit Display Interface Data Sheet

# Reference Materials

### Informational

• Advantiv<sup>TM</sup> Advanced TV Solutions

# **Technical Articles**

• Analysis of Common Failures of HDMI CT

# Design Resources -

- · AD9983A Material Declaration

- · PCN-PDN Information

- Quality And Reliability

- · Symbols and Footprints

# Discussions <a>□</a>

View all AD9983A EngineerZone Discussions

# Sample and Buy 🖳

Visit the product page to see pricing options

# Technical Support <a> □</a>

Submit a technical question or find your regional support number

<sup>\*</sup> This page was dynamically generated by Analog Devices, Inc. and inserted into this data sheet. Note: Dynamic changes to the content on this page does not constitute a change to the revision number of the product data sheet. This content may be frequently modified.

# **TABLE OF CONTENTS**

| Features                                     | Output Formatter                   | 20 |

|----------------------------------------------|------------------------------------|----|

| Applications 1                               | 2-Wire Serial Control Port         | 21 |

| Functional Block Diagram1                    | Data Transfer via Serial Interface | 21 |

| General Description1                         | 2-Wire Serial Register Map         | 23 |

| Revision History2                            | 2-Wire Serial Control Registers    | 29 |

| Specifications                               | Chip Identification                | 29 |

| Analog Interface Characteristics             | PLL Divider Control                | 29 |

| Absolute Maximum Ratings5                    | Clock Generator Control            | 29 |

| Explanation of Test Levels5                  | Phase Adjust                       | 29 |

| Thermal Resistance                           | Input Gain                         | 30 |

| ESD Caution5                                 | Input Offset                       | 30 |

| Pin Configuration and Function Descriptions6 | Hsync Controls                     | 30 |

| Theory of Operation10                        | Vsync Controls                     | 31 |

| Digital Inputs10                             | Coast and Clamp Controls           | 32 |

| Analog Input Signal Handling10               | SOG Control                        |    |

| Hsync and Vsync Inputs10                     | Input and Power Control            | 34 |

| Serial Control Port10                        | Output Control                     | 35 |

| Output Signal Handling10                     | Sync Processing                    | 36 |

| Clamping 10                                  | Detection Status                   | 36 |

| Gain and Offset Control11                    | Polarity Status                    | 37 |

| Sync-on-Green                                | Hsync Count                        | 37 |

| Reference Bypassing12                        | Test Registers                     | 37 |

| Clock Generation                             | PCB Layout Recommendations         | 39 |

| Sync Processing                              | Analog Interface Inputs            | 39 |

| Power Management                             | Outputs (Both Data and Clocks)     | 40 |

| Timing Diagrams18                            | Digital Inputs                     | 40 |

| Hsync Timing19                               | Outline Dimensions                 | 41 |

| Coast Timing                                 | Ordering Guide                     | 41 |

# **REVISION HISTORY**

5/07—Revision 0: Initial Version

# **SPECIFICATIONS**

# **ANALOG INTERFACE CHARACTERISTICS**

$V_D = 1.8 \text{ V}, V_{DD} = 3.3 \text{ V}, PV_D = 1.8 \text{ V}, DAV_{DD} = 1.8 \text{ V}, ADC \text{ clock} = maximum conversion rate, full temperature range} = 0^{\circ}\text{C to } 70^{\circ}\text{C}.$

Table 1.

| Parameter                               | Temperature | Test Level <sup>1</sup> | Min            | Тур    | Max        | Unit                                  |

|-----------------------------------------|-------------|-------------------------|----------------|--------|------------|---------------------------------------|

| RESOLUTION                              |             |                         |                |        |            |                                       |

| Number of bits                          |             |                         |                | 8      |            | Bits                                  |

| LSB Size                                |             |                         |                | 0.391  |            | % of Full Scale                       |

| DC ACCURACY                             |             |                         |                |        |            |                                       |

| Differential Nonlinearity               | 25°C        | 1                       |                | ±0.25  | ±0.85      | LSB                                   |

| 2                                       | Full        | VI                      |                | ±0.3   | _0.00      | LSB                                   |

| Integral Nonlinearity                   | 25°C        | l i                     |                | ±0.75  | 1.45/-2.60 | LSB                                   |

| megrarivorimicanty                      | Full        | VI                      |                | ±1.0   | 1.13/ 2.00 | LSB                                   |

| No Missing Codes                        | Full        | VI                      |                | GNT    |            |                                       |

| ANALOG INPUT                            | Tun         | V1                      |                | GIVI   |            |                                       |

| Input Voltage Range                     |             |                         |                |        |            |                                       |

| Minimum                                 | Full        | VI                      |                |        | 0.5        | Vn n                                  |

| Maximum                                 | Full        | VI                      | 1.0            |        | 0.5        | V p-p                                 |

|                                         |             |                         | 1.0            | 125    |            | V p-p                                 |

| Gain Tempco                             | 25°C        | V                       |                | 125    | 1          | ppm/°C                                |

| Input Bias Current                      | 25°C        | IV                      |                |        | 1          | μΑ                                    |

|                                         | Full        | IV                      |                |        | 1          | μΑ                                    |

| Input Full-Scale Matching               | Full        | VI                      |                | 1      | 5          | % FS                                  |

| Offset Adjustment Range                 | Full        | VI                      |                | 50     |            | % FS                                  |

| SWITCHING PERFORMANCE                   |             |                         |                |        |            |                                       |

| Maximum Conversion Rate                 | Full        | VI                      | 140            |        |            | MSPS                                  |

| Minimum Conversion Rate                 | Full        | IV                      |                |        | 10         | MSPS                                  |

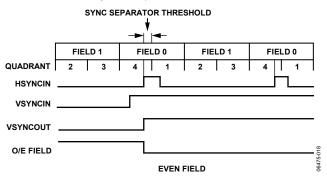

| Clock to Data Skew t <sub>SKEW</sub>    | Full        | IV                      | -0.5           |        | 2.0        | ns                                    |

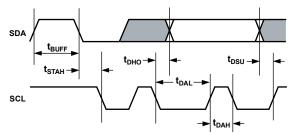

| t <sub>BUFF</sub>                       | Full        | VI                      | 4.7            |        |            | μs                                    |

| <b>t</b> stah                           | Full        | VI                      | 4.0            |        |            | μs                                    |

| t <sub>DHO</sub>                        | Full        | VI                      | 0              |        |            | μs                                    |

| t <sub>DAL</sub>                        | Full        | VI                      | 4.7            |        |            | μs                                    |

| t <sub>DAH</sub>                        | Full        | VI                      | 4.0            |        |            | μs                                    |

| t <sub>DSU</sub>                        | Full        | VI                      | 250            |        |            | ns                                    |

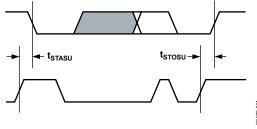

| <b>t</b> stasu                          | Full        | VI                      | 4.7            |        |            | μs                                    |

| t <sub>stosu</sub>                      | Full        | VI                      | 4.0            |        |            | μs                                    |

| Maximum PLL Clock Rate                  | Full        | VI                      | 140            |        |            | MHz                                   |

| Minimum PLL Clock Rate                  | Full        | IV                      |                |        | 10         | MHz                                   |

| Jitter <sup>2</sup>                     | 25°C        | IV                      |                |        | . •        | pS p-p                                |

| sitter                                  | Full        | IV                      |                |        |            | pS p-p                                |

| Campling Phase Tomps                    |             |                         |                | 15     |            |                                       |

| Sampling Phase Tempco                   | Full        | IV                      |                | 15     |            | pS/°C                                 |

| DIGITAL INPUTS                          | FP          | ,,                      | 1.0            |        |            | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |

| Input Voltage, High (V <sub>IH</sub> )  | Full        | VI                      | 1.0            |        |            | V                                     |

| Input Voltage, Low (V <sub>IL</sub> )   | Full        | VI                      |                |        | 0.8        | V                                     |

| Input Current, High (I <sub>IH</sub> )  | Full        | V                       |                |        | -1.0       | μΑ                                    |

| Input Current, Low (I <sub>IL</sub> )   | Full        | V                       |                |        | 1.0        | μΑ                                    |

| Input Capacitance                       | 25°C        | V                       |                | 2      |            | pF                                    |

| DIGITAL OUTPUTS                         |             |                         |                |        |            |                                       |

| Output Voltage, High (V <sub>OH</sub> ) | Full        | VI                      | $V_{DD} - 0.1$ |        |            | V                                     |

| Output Voltage, Low (Vol)               | Full        | VI                      |                |        | 0.1        | V                                     |

| Duty Cycle, DATACK                      | Full        | IV                      | 45             | 50     | 55         | %                                     |

| Output Coding                           |             |                         |                | Binary |            |                                       |

| Parameter                                              | Temperature | Test Level <sup>1</sup> | Min | Тур | Max  | Unit |

|--------------------------------------------------------|-------------|-------------------------|-----|-----|------|------|

| POWER SUPPLY                                           |             |                         |     |     |      |      |

| V <sub>D</sub> Supply Voltage                          | Full        | IV                      | 1.7 | 1.8 | 1.9  | V    |

| V <sub>DD</sub> Supply Voltage                         | Full        | IV                      | 1.7 | 3.3 | 3.47 | V    |

| PV <sub>D</sub> Supply Voltage                         | Full        | IV                      | 1.7 | 1.8 | 1.9  | V    |

| DA <sub>VDD</sub> Supply Voltage                       | Full        | IV                      | 1.7 | 1.8 | 1.9  | V    |

| V <sub>D</sub> Supply Current (I <sub>D</sub> )        | 25°C        | V                       |     | 250 |      | mA   |

| V <sub>DD</sub> Supply Current (I <sub>DD</sub> )      | 25°C        | V                       |     | 31  |      | mA   |

| PV <sub>D</sub> Supply Current (IPV <sub>D</sub> )     | 25°C        | V                       |     | 9   |      | mA   |

| DAV <sub>DD</sub> Supply Current (IDAV <sub>DD</sub> ) | 25°C        | V                       |     | 16  |      | mA   |

| Total Power Dissipation                                | Full        | VI                      |     |     | 800  | mW   |

| Power-Down Supply Current                              | Full        | VI                      |     | 10  |      | mA   |

| Power-Down Dissipation                                 | Full        | VI                      |     | 18  |      | mW   |

| DYNAMIC PERFORMANCE                                    |             |                         |     |     |      |      |

| Analog Bandwidth, Full Power                           | 25°C        | V                       |     | 300 |      | MHz  |

| Crosstalk                                              | Full        | V                       |     | 60  |      | dBc  |

$<sup>^{\</sup>rm 1}$  See the Explanation of Test Levels section.  $^{\rm 2}$  Jitter measurements taken at SXGA with recommended PLL settings.

# **ABSOLUTE MAXIMUM RATINGS**

Table 2.

| 14016 2.                     |                  |  |  |  |  |

|------------------------------|------------------|--|--|--|--|

| Parameter                    | Rating           |  |  |  |  |

| $V_D$                        | 1.98 V           |  |  |  |  |

| $V_{DD}$                     | 3.6 V            |  |  |  |  |

| $PV_D$                       | 1.98 V           |  |  |  |  |

| $DAV_{DD}$                   | 1.98 V           |  |  |  |  |

| Analog Inputs                | $V_D$ to $0.0V$  |  |  |  |  |

| REFHI                        | $V_D$ to $0.0V$  |  |  |  |  |

| REFLO                        | $V_D$ to $0.0V$  |  |  |  |  |

| Digital Inputs               | 5 V to 0.0 V     |  |  |  |  |

| Digital Output Current       | 20 mA            |  |  |  |  |

| Operating Temperature        | −25°C to + 85°C  |  |  |  |  |

| Storage Temperature          | −65°C to + 150°C |  |  |  |  |

| Maximum Junction Temperature | 150°C            |  |  |  |  |

| Maximum Case Temperature     | 150°C            |  |  |  |  |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **EXPLANATION OF TEST LEVELS**

- I. 100% production tested.

- II. 100% production tested at 25°C and sample tested at specified temperatures.

- III. Sample tested only.

- IV. Parameter is guaranteed by design and characterization testing.

- V. Parameter is a typical value only.

- VI. 100% production tested at 25°C; guaranteed by design and characterization testing.

#### THERMAL RESISTANCE

$\theta_{JA}$  is specified for the worst-case conditions, that is, a device soldered in a circuit board for surface-mount packages.

**Table 3. Thermal Resistance**

| Package Type | θ <sub>JA</sub> | θις | Unit |

|--------------|-----------------|-----|------|

| 80-lead LQFP | 35              | 16  | °C/W |

### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 2. 80-Lead LQFP Pin Configuration

**Table 4. Complete Pinout List**

| Pin Type | Pin Number      | Mnemonic          | Function                               | Value          |

|----------|-----------------|-------------------|----------------------------------------|----------------|

| Inputs   | 14              | R <sub>AIN0</sub> | Channel 0 Analog Input for Converter R | 0.0 V to 1.0 V |

|          | 16              | R <sub>AIN1</sub> | Channel 1 Analog Input for Converter R | 0.0 V to 1.0 V |

|          | 6               | G <sub>AINO</sub> | Channel 0 Analog Input for Converter G | 0.0 V to 1.0 V |

|          | 10              | G <sub>AIN1</sub> | Channel 1 Analog Input for Converter G | 0.0 V to 1.0 V |

|          | 2               | B <sub>AIN0</sub> | Channel 0 Analog Input for Converter B | 0.0 V to 1.0 V |

|          | 4               | B <sub>AIN1</sub> | Channel 1 Analog Input for Converter B | 0.0 V to 1.0 V |

|          | 70              | HSYNC0            | Horizontal Sync Input for Channel 0    | 3.3 V CMOS     |

|          | 68              | HSYNC1            | Horizontal Sync Input for Channel 1    | 3.3 V CMOS     |

|          | 71              | VSYNC0            | Vertical Sync Input for Channel 0      | 3.3 V CMOS     |

|          | 69              | VSYNC1            | Vertical Sync Input for Channel 1      | 3.3 V CMOS     |

|          | 8               | SOGIN0            | Input for Sync-on-Green Channel 0      | 0.0 V to 1.0 V |

|          | 12              | SOGIN1            | Input for Sync-on-Green Channel 1      | 0.0 V to 1.0 V |

|          | 72 <sup>1</sup> | EXTCK             | External Clock Input                   | 3.3 V CMOS     |

|          | 73              | CLAMP             | External Clamp Input Signal            | 3.3 V CMOS     |

|          | 72 <sup>1</sup> | COAST             | External PLL Coast Signal Input        | 3.3 V CMOS     |

|          | 17              | PWRDN             | Power-Down Control                     | 3.3 V CMOS     |

| Pin Type     | Pin Number                               | Mnemonic               | Function                                                   | Value          |

|--------------|------------------------------------------|------------------------|------------------------------------------------------------|----------------|

| Outputs      | 28 to 35                                 | RED [7:0]              | Outputs of Converter R, Bit 9 is the MSB                   | 3.3 V CMOS     |

|              | 42 to 49                                 | GREEN [7:0]            | Outputs of Converter G, Bit 9 is the MSB                   | 3.3 V CMOS     |

|              | 54 to 61                                 | BLUE [7:0]             | Outputs of Converter B, Bit 9 is the MSB                   | 3.3 V CMOS     |

|              | 25                                       | DATACK                 | Data Output Clock                                          | 3.3 V CMOS     |

|              | 23                                       | HSOUT                  | Hsync Output Clock (Phase-Aligned with DATACK)             | 3.3 V CMOS     |

|              | 22 <sup>2</sup>                          | VSOUT                  | Vsync Output Clock                                         | 3.3 V CMOS     |

|              | 24                                       | SOGOUT                 | Sync-on-Green Slicer Output                                | 3.3 V CMOS     |

|              | 21                                       | O/E FIELD              | Odd/Even Field Output                                      | 3.3 V CMOS     |

| References   | 78                                       | FILT                   | Connection for External Filter Components for Internal PLL |                |

|              | 18                                       | REFLO                  | Connection for External Capacitor for Input Amplifier      |                |

|              | 20                                       | REFHI                  | Connection for External Capacitor for Input Amplifier      |                |

| Power Supply | 1, 5, 9, 13                              | <b>V</b> <sub>D</sub>  | Analog Power Supply                                        | 1.8 V          |

|              | 26, 38, 52, 64                           | $V_{DD}$               | Output Power Supply                                        | 1.8 V or 3.3 V |

|              | 74, 76, 79                               | <b>PV</b> <sub>D</sub> | PLL Power Supply                                           | 1.8 V          |

|              | 41                                       | DAV <sub>DD</sub>      | Digital Logic Power Supply                                 | 1.8 V          |

|              | 3, 7, 11, 15, 39, 40, 53, 65, 75, 77, 80 | GND                    | Ground                                                     | 0 V            |

| Control      | 66                                       | SDA                    | Serial Port Data I/O                                       | 3.3 V CMOS     |

|              | 67                                       | SCL                    | Serial Port Data Clock (100 kHz maximum)                   | 3.3 V CMOS     |

|              | 22 <sup>2</sup>                          | A0                     | Serial Port Address Input                                  | 3.3 V CMOS     |

$<sup>^{\</sup>rm 1}$  EXTCK and COAST share the same pin.  $^{\rm 2}$  VSOUT and A0 share the same pin.

**Table 5. Pin Function Descriptions**

| Mnemonic          | Function                                     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R <sub>AINO</sub> | Analog Input for the Red<br>Channel 0        | These are high impedance inputs that accept the red, green, and blue channel graphics signals, respectively. The three channels are identical and can be used for any colors, but solors are assigned for convenient reference. They accommodate input signals.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| G <sub>AINO</sub> | Analog Input for the Green<br>Channel 0      | but colors are assigned for convenient reference. They accommodate input signals ranging from 0.5 V to 1.0 V full scale. Signals should be ac-coupled to these pins to support clamp operation. See Figure 4 and Figure 5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| BAINO             | Analog Input for the Blue<br>Channel 0       | support clamp operation. See rigure 4 and rigure 3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| R <sub>AIN1</sub> | Analog Input for the Red<br>Channel 1        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| G <sub>AIN1</sub> | Analog Input for the Green<br>Channel 1      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| B <sub>AIN1</sub> | Analog Input for the Blue<br>Channel 1       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| HSYNC0            | Horizontal Sync Input<br>Channel 0           | These inputs receive a logic signal that establishes the horizontal timing reference and provides the frequency reference for pixel clock generation. The logic sense of this pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| HSYNC1            | Horizontal Sync Input<br>Channel 1           | can be automatically determined by the chip or manually controlled by Serial Register 0x12, Bits[5:4] (Hsync polarity). Only the leading edge of Hsync is used by the PLL; the trailing edge is used in clamp timing. When Hsync polarity = 0, the falling edge of Hsync is used. When Hsync polarity = 1, the rising edge is active. The input includes a Schmitt trigger for noise immunity.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

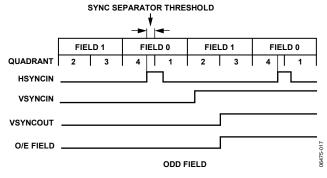

| VSYNC0            | Vertical Sync Input Channel 0                | These are the inputs for vertical sync and provide timing information for generation of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| VSYNC1            | Vertical Sync Input Channel 1                | the field (odd/even) and internal Coast generation. The logic sense of this pin can be automatically determined by the chip or manually controlled by Serial Register 0x14, Bits[5:4] (Vsync polarity).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SOGIN0            | Sync-on-Green Input<br>Channel 0             | These inputs process signals with embedded sync, typically on the green channel. The pin is connected to a high speed comparator with an internally generated threshold.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| SOGIN1            | Sync-on-Green Input<br>Channel 1             | The threshold level can be programmed in 8 mV steps to any voltage between 8 mV and 256 mV above the negative peak of the input signal. The default voltage threshold is 128 mV. When connected to an ac-coupled graphics signal with embedded sync, it produces a noninverting digital output on SOGOUT. This is usually a composite sync signal, containing both vertical and horizontal sync information that must be separated before passing the horizontal sync signal for Hsync processing. When not used, this input should be left unconnected. For more details on this function and how it should be configured, refer to the Sync-on-Green section.                                                                                                                                                                 |

| CLAMP             | External Clamp Input<br>(Optional)           | This logic input can be used to define the time during which the input signal is clamped to ground or midscale. It should be exercised when the reference dc level is known to be present on the analog input channels, typically during the back porch of the graphics signal. The CLAMP pin is enabled by setting the control bit clamp function to 1, (Register 0x18, Bit 4; default is 0). When disabled, this pin is ignored and the clamp timing is determined internally by counting a delay and duration from the trailing edge of the Hsync input. The logic sense of this pin can be automatically determined by the chip or controlled by clamp polarity Register 0x1B, Bits[7:6]. When not used, this pin may be left unconnected (there is an internal pull-down resistor) and the clamp function programmed to 0. |

| EXTCK/COAST       | External Clock                               | EXTCK allows the insertion of an external clock source rather than the internally generated, PLL locked clock. EXTCK is enabled by programming Register 0x03, Bit 2 to 1. This pin is shared with the Coast function, which does not affect EXTCK functionality.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                   | Coast Input to Clock<br>Generator (Optional) | COAST can be used to cause the pixel clock generator to stop synchronizing with Hsync and continue producing a clock at its current frequency and phase. This is useful when processing signals from sources that fail to produce Hsync pulses during the vertical interval. The coast signal is generally <i>not</i> required for PC-generated signals. The logic sense of this pin can be determined automatically or controlled by Coast polarity (Register 0x18, Bits[7:6]). When not used and EXTCK not used, this pin may be grounded and Coast polarity programmed to 1. Input Coast polarity defaults to 1 at power-up. This pin is shared with the EXTCK function, which does not affect coast functionality. For more details on EXTCK, see the description in this section.                                          |

| PWRDN             | Power-Down Control                           | This pin can be used along with Register 0x1E, Bit 3 for manual power-down control. If manual power-down control is selected (Register 0x1E, Bit 4) and this pin is not used, it is recommended to set the pin polarity (Register 0x1E, Bit 2) to active high and hardwire this pin to ground with a 10 k $\Omega$ resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Mnemonic                                         | Function                                                                            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------------------------------------------------|-------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

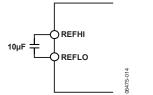

| REFLO, REFHI                                     | Input Amplifier Reference                                                           | REFLO and REFHI are connected together through a 10 $\mu$ F capacitor. These are used for stability in the input ADC circuitry. See Figure 6.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

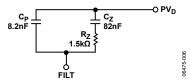

| FILT                                             | External Filter Connection                                                          | For proper operation, the pixel clock generator PLL requires an external filter. Connect the filter shown in Figure 6 to this pin. For optimal performance, minimize noise and parasitics on this node. For more information, see the PCB Layout Recommendations section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

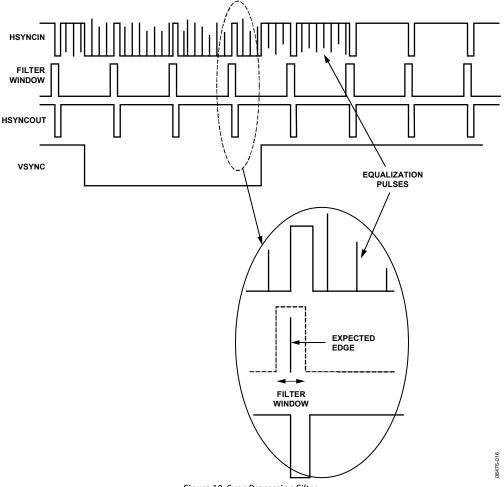

| HSOUT                                            | Horizontal Sync Output                                                              | A reconstructed and phase-aligned version of the Hsync input. Both the polarity and duration of this output can be programmed via serial bus registers. By maintaining alignment with DATACK and Data, data timing with respect to Hsync can always be determined.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| VSOUT/A0                                         | Vertical Sync Output                                                                | Pin shared with A0, serial port address. This can be either a separated Vsync from a composite signal or a direct pass through of the Vsync signal. The polarity of this output can be controlled via a serial bus bit. The placement and duration in all modes can be set by the graphics transmitter or the duration can be set by Register 0x14 and Register 0x15. This pin is shared with the A0 function, which does not affect Vsync Output functionality. For more details on A0, see the description in the Serial Control Port section.                                                                                                                                                                                                                                                                                 |

|                                                  | Serial Port Address Input 0                                                         | Pin shared with VSOUT. This pin selects the LSB of the serial port device address, allowing two Analog Devices parts to be on the same serial bus. A high impedance external pull-up resistor enables this pin to be read at power-up as 1, or a high impedance, external pull-down resistor enables this pin to be read at power-up as a 0 and not interfere with the VSOUT functionality.                                                                                                                                                                                                                                                                                                                                                                                                                                      |

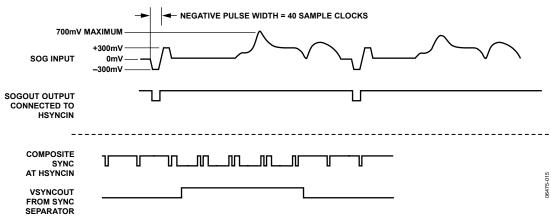

| SOGOUT                                           | Sync-On-Green Slicer<br>Output                                                      | This pin outputs one of four possible signals (controlled by Register 0x1D, Bits[1:0]): raw SOG, raw Hsync, regenerated Hsync from the filter, or the filtered Hsync. See Figure 8 to view how this pin is connected. Other than slicing off SOG, the output from this pin gets no additional processing on the AD9983A. Vsync separation is performed via the sync separator.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| O/E FIELD                                        | Odd/Even Field Bit for<br>Interlaced Video                                          | This output will identify whether the current field (in an interlaced signal) is odd or even.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| SDA                                              | Serial Port Data I/O                                                                | Data I/O for the I <sup>2</sup> C® serial port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| SCL                                              | Serial Port Data Clock                                                              | Clock for the I <sup>2</sup> C serial port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

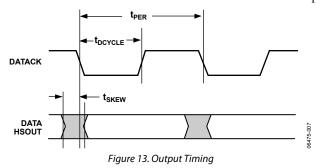

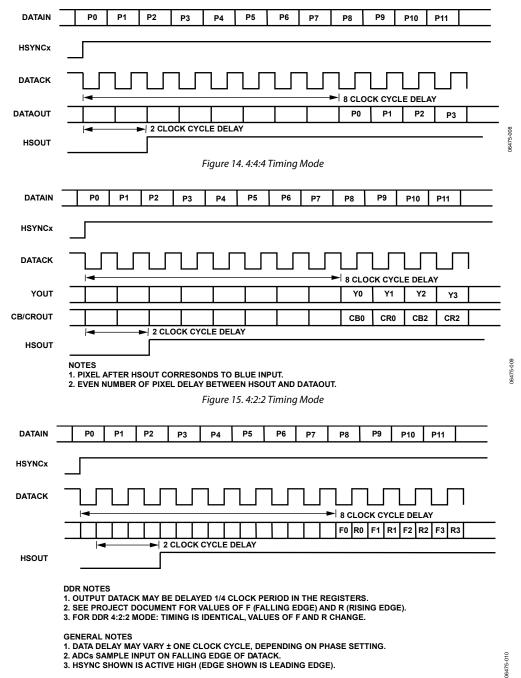

| RED [7:0]<br>GREEN [7:0]<br>BLUE [7:0]           | Data Output, Red Channel<br>Data Output, Green Channel<br>Data Output, Blue Channel | The main data outputs. Bit 9 is the MSB. The delay from pixel sampling time to output is fixed. When the sampling time is changed by adjusting the phase register, the output timing is shifted as well. The DATACK and HSOUT outputs are also moved, so the timing relationship among the signals is maintained.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| DATACK                                           | Data Clock Output                                                                   | This is the main clock output signal used to strobe the output data and HSOUT into external logic. Four possible output clocks can be selected with Register 0x20, Bits[7:6]. Three of these are related to the pixel clock (pixel clock, 90° phase-shifted pixel clock and 2× frequency pixel clock). They are produced either by the internal PLL clock generator or EXTCK and are synchronous with the pixel sampling clock. The fourth option for the data clock output is an internally generated 1/2x pixel clock. The sampling time of the internal pixel clock can be changed by adjusting the phase register (Register 0x04). When this is changed, the pixel related DATACK timing is also shifted. The data, DATACK, and HSOUT outputs are all moved so that the timing relationship among the signals is maintained. |

| V <sub>D</sub> (1.8 V)                           | Main Power Supply                                                                   | These pins supply power to the main elements of the circuit. They should be as quiet and filtered as possible.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| $V_{\text{DD}}(1.8\text{V}\text{to}3.3\text{V})$ | Digital Output Power Supply                                                         | A large number of output pins (up to 29) switching at high speed (up to 140 MHz) generates a lot of power supply transients (noise). These supply pins are identified separately from the V <sub>D</sub> pins, so special care can be taken to minimize output noise transferred into the sensitive analog circuitry. If the AD9983A is interfacing with lower voltage logic, V <sub>DD</sub> can be connected to a lower supply voltage (as low as 1.8 V) for compatibility.                                                                                                                                                                                                                                                                                                                                                    |

| PV <sub>D</sub> (1.8 V)                          | Clock Generator Power<br>Supply                                                     | The most sensitive portion of the AD9983A is the clock generation circuitry. These pins provide power to the clock PLL and help the user design for optimal performance. The designer should provide quiet, noise-free power to these pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| DAV <sub>DD</sub> (1.8 V)                        | Digital Input Power Supply                                                          | This supplies power to the digital logic.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| GND                                              | Ground                                                                              | The ground return for all circuitry on-chip. It is recommended that the AD9983A be assembled on a single solid ground plane, with careful attention to ground current paths.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

# THEORY OF OPERATION

The AD9983A is a fully integrated solution for capturing analog RGB or YPbPr signals and digitizing them for display on advanced TVs, flat panel monitors, projectors, and other types of digital displays. Implemented in a high performance CMOS process, the interface can capture signals with pixel rates of up to 140 MHz.

The AD9983A includes all necessary input buffering, signal dc restoration (clamping), offset and gain (brightness and contrast) adjustment, pixel clock generation, sampling phase control, and output data formatting. All controls are programmable via a 2-wire serial interface (I<sup>2</sup>C). Full integration of these sensitive analog functions makes system design straightforward and less sensitive to the physical and electrical environment.

With a typical power dissipation of less than 800 mW and an operating temperature range of 0°C to 70°C, the device requires no special environmental considerations.

## **DIGITAL INPUTS**

All digital inputs on the AD9983A operate to 3.3 V CMOS levels. The following digital inputs are 5 V tolerant (that is, applying 5 V to them does not cause any damage.): HSYNC0, HSYNC1, VSYNC1, SOGIN0, SOGIN1, SDA, SCL and CLAMP.

### **ANALOG INPUT SIGNAL HANDLING**

The AD9983A has six high impedance analog input pins for the red, green, and blue channels. They accommodate signals ranging from 0.5 V to 1.0 V p-p.

Signals are typically brought onto the interface board with a DVI-I connector, a 15-pin D connector, or RCA connectors. The AD9983A should be located as close as possible to the input connector. Signals should be routed using matchedimpedance traces (normally 75  $\Omega$ ) to the IC input pins.

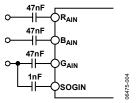

At the input pins the signal should be resistively terminated (75  $\Omega$  to the signal ground return) and capacitively coupled to the AD9983A inputs through 47 nF capacitors. These capacitors form part of the dc restoration circuit.

In an ideal world of perfectly matched impedances, the best performance can be obtained with the widest possible signal bandwidth. The wide bandwidth inputs of the AD9983A (300 MHz) can track the input signal continuously as it moves from one pixel level to the next and can digitize the pixel during a long, flat pixel time. In many systems, however, there are mismatches, reflections, and noise, which can result in excessive ringing and distortion of the input waveform. This makes it more difficult to establish a sampling phase that provides good image quality. A small inductor in series with the input is effective in rolling off the input bandwidth slightly and providing a high quality signal over a wider range of conditions. Using a Fair-Rite #2508051217Z0-High Speed, Signal Chip Bead Inductor in the circuit shown in Figure 3 provides good results in most applications.

Figure 3. Analog Input Interface Circuit

### **HSYNC AND VSYNC INPUTS**

The interface also accepts Hsync and Vsync signals, which are used to generate the pixel clock, clamp timing, coast and field information. These can be either a sync signal directly from the graphics source, or a preprocessed TTL- or CMOS-level signal.

The Hsync input includes a Schmitt trigger buffer for immunity to noise and signals with long rise times. In typical PC-based graphic systems, the sync signals are simply TTL-level drivers feeding unshielded wires in the monitor cable. As such, no termination is required.

### **SERIAL CONTROL PORT**

The serial control port is designed for 3.3 V logic; however, it is tolerant of 5 V logic signals. Refer to the 2-Wire Serial Control Port section.

### **OUTPUT SIGNAL HANDLING**

The digital outputs operate from 1.8 V to 3.3 V (V<sub>DD</sub>).

### **CLAMPING**

### **RGB Clamping**

To properly digitize the incoming signal, the dc offset of the input must be adjusted to fit the range of the on-board ADCs.

Most graphics systems produce RGB signals with black at ground and white at approximately 0.75 V. However, if sync signals are embedded in the graphics, the sync tip is often at ground, black is at 300 mV, and white is at approximately 1.0 V. Some common RGB line amplifier boxes use emitter-follower buffers to split signals and increase drive capability. This introduces a 700 mV dc offset to the signal, which must be removed for proper capture by the AD9983A.

The key to clamping is to identify a portion (time) of the signal when the graphic system is known to be producing black. An offset is then introduced that results in the ADC producing a black output (Code 0x00) when the known black input is present. The offset then remains in place when other signal levels are processed, and the entire signal is shifted to eliminate offset errors.

In most PC graphics systems, black is transmitted between active video lines. With CRT displays, when the electron beam has completed writing a horizontal line on the screen (at the right side), the beam is deflected quickly to the left side of the screen (called horizontal retrace) and a black signal is provided to prevent the beam from disturbing the image.

In systems with embedded sync, a blacker-than-black signal (Hsync) is produced briefly to signal the CRT that it is time to begin a retrace. Because the input is not at black level at this time, it is important to avoid clamping during Hsync. Fortunately, there is usually a period following Hsync, called the back porch, where a good black reference is provided. This is the time when clamping should be done.

The clamp timing can be established by simply exercising the CLAMP pin at the appropriate time with clamp source (Register 0x18, Bit 4) = 1. The polarity of this signal is set by the clamp polarity bit, (Register 0x1B, Bits[7:6]).

A simpler method of clamp timing employs the AD9983A internal clamp timing generator. The clamp placement register (Register 0x19) is programmed with the number of pixel periods that should pass after the trailing edge of Hsync before clamping starts. A second register, clamp duration, (Register 0x1A) sets the duration of the clamp. These are both 8-bit values, providing considerable flexibility in clamp generation. The clamp timing is referenced to the trailing edge of Hsync because, though Hsync duration can vary widely, the back porch (black reference) always follows Hsync. A good starting point for establishing clamping is to set the clamp placement to 0x04 (providing 4 pixel periods for the graphics signal to stabilize after sync) and set the clamp duration to 0x28 (giving the clamp 40 pixel periods to reestablish the black reference).

Clamping is accomplished by placing an appropriate charge on the external input coupling capacitor. The value of this capacitor affects the performance of the clamp. If it is too small, there will be a significant amplitude change during a horizontal line time (between clamping intervals). If the capacitor is too large, it will take too long for the clamp to recover from a large change in incoming signal offset. The recommended value (47 nF) results in recovering from a step error of 100 mV to within 1 LSB in 30 lines with a clamp duration of 20 pixel periods on a 85 Hz XGA signal.

# YPbPr Clamping

YPbPr graphic signals are slightly different from RGB signals in that the dc reference level (black level in RGB signals) of color difference signals is at the midpoint of the video signal rather than at the bottom. The three inputs are composed of luminance (Y) and color difference (Pb and Pr) signals. For color difference signals, it is necessary to clamp to the midscale range of the ADC range (512) rather than to the bottom of the ADC range (0), while the Y channel is clamped to ground.

Clamping to midscale rather than ground can be accomplished by setting the clamp select bits in the serial bus register. Each of the three converters has its own selection bit so that they can be clamped to either midscale or ground independently. These bits are located in Register 0x18, Bits[3:1]. The midscale reference voltage is internally generated for each converter.

### **GAIN AND OFFSET CONTROL**

The AD9983A contains three PGAs, one for each of the three analog inputs. The range of the PGA is sufficient to accommodate input signals with inputs ranging from 0.5 V to 1.0 V full scale. The gain is set in three 7-bit registers (red gain [0x05], green gain [0x07], blue gain [0x09]). For each register, a gain setting of 0 corresponds to the highest gain, while a gain setting of 127 corresponds to the lowest gain. Note that increasing the gain setting results in an image with less contrast.

The offset control shifts the analog input, resulting in a change in brightness. Three 9-bit registers red offset [Register 0x0B and Register 0x0C], green offset [Register 0x0D and Register 0x0E], and blue offset [Register 0x0F and Register 0x10] provide independent settings for each channel. Note that the function of the offset register depends on whether auto-offset is enabled (Register 0x1B, Bit 5).

If manual offset is used, seven bits of the offset registers (for the red channel Register 0x0B, Bits[6:0]) control the absolute offset added to the channel. The offset control provides  $\pm 63$  LSBs of adjustment range, with 1 LSB of offset corresponding to 1 LSB of output code.

### **Automatic Offset**

In addition to the manual offset adjustment mode, the AD9983A also includes circuitry to automatically calibrate the offset for each channel. By monitoring the output of each ADC during the back porch of the input signals, the AD9983A can self-adjust to eliminate any offset errors in its own ADC channels and any offset errors present on the incoming graphics or video signals.

To activate the auto-offset mode, set Register 0x1B, Bit 5 to 1. Next, the target code registers (Register 0x0B through Register 0x10) must be programmed. The values programmed into the target code registers should be the output code desired from the AD9983A ADCs, which are generated during the back porch reference time. For example, for RGB signals, all three registers are normally programmed to Code 2, while for YPbPr signals the green (Y) channel is normally programmed to Code 2 and the blue and red channels (Pb and Pr) are normally set to 128. The target code registers have nine bits per channel and are in twos complement format. This allows any value between -256 and +255 to be programmed. Although any value in this range can be programmed, the AD9983A offset range may not be able to reach every value. Intended target code values range from (but are not limited to) -40 to -1 and 1 to 40 when ground clamping and 88 to 168 when midscale clamping. Note that a target code of 0 is not valid.

Negative target codes are included in order to duplicate a feature that is present with manual offset adjustment. The benefit that is being mimicked is the ability to easily adjust brightness on a display. By setting the target code to a value that does not correspond to the ideal ADC range, the end result is an image that is either brighter or darker. A target code higher than ideal results in a brighter image. A target code lower than ideal results in a darker image.

The ability to program a target code gives a large degree of freedom and flexibility. In most cases all channels are set to either 1 or 128, but the flexibility to select other values allows for the possibility of inserting intentional skews between channels. It also allows the ADC range to be skewed so that voltages outside of the normal range can be digitized. For example, setting the target code to 40 allows the sync tip, which is normally below black level, to be digitized and evaluated.

The internal logic for the auto-offset circuit requires 16 data clock cycles to perform its function. This operation is executed immediately after the clamping pulse. Therefore, it is important to end the clamping pulse signal at least 16 data clock cycles before active video. This is true whether using the AD9983A internal clamp circuit or an external clamp signal. The auto-offset function can be programmed to run continuously or on a one-time basis (see auto-offset hold, Register 0x2C, Bit 4). In continuous mode, the update frequency can be programmed (Register 0x1B, Bits[4:3]). Continuous operation with updates every 64 Hsyncs is recommended.

A guideline for basic auto-offset operation is shown in Table 6 and Table 7.

Table 6. RGB Auto-Offset Register Settings

| Register        | Value | Comments                                           |

|-----------------|-------|----------------------------------------------------|

| 0x0B            | 0x02  | Sets red target to 4                               |

| 0x0C            | 0x00  | Must be written                                    |

| 0x0D            | 0x02  | Sets green target to 4                             |

| 0x0E            | 0x00  | Must be written                                    |

| 0x0F            | 0x02  | Sets blue target to 4                              |

| 0x10            | 0x00  | Must be written                                    |

| 0x18, Bits[3:1] | 000   | Sets red, green, and blue channels to ground clamp |

| 0x1B, Bits[5:3] | 110   | Selects update rate and enables auto-offset.       |

Table 7. PbPr Auto-Offset Register Settings

| Register        | Value | Comments                                               |

|-----------------|-------|--------------------------------------------------------|

| 0x0B            | 0x40  | Sets Pr (red) target to 128                            |

| 0x0C            | 0x00  | Must be written                                        |

| 0x0D            | 0x02  | Sets Y (green) target to 4                             |

| 0x0E            | 0x00  | Must be written                                        |

| 0x0F            | 0x40  | Sets Pb (blue) target to 128                           |

| 0x10            | 0x00  | Must be written                                        |

| 0x18 Bits[3:1]  | 101   | Sets Pb, Pr to midscale clamp<br>and Y to ground clamp |

| 0x1B, Bits[5:3] | 110   | Selects update rate and enables auto-offset            |

### **Automatic Gain Matching**

The AD9983A includes circuitry to match the gains between the three channels to within 1% of each other. Matching the gains of each channel is necessary in order to achieve good color balance on a display. On products without this feature, gain matching is achieved by writing software that evaluates the output of each channel, calculates gain mismatches, then writes values to the gain registers of each channel to compensate. With the auto gain matching function, this software routine is no longer needed. To activate auto gain matching, set Register 0x3C, Bit 2 to Bit 1.

Auto gain matching has similar timing requirements to auto offset. It requires 16 data clock cycles to perform its function, starting immediately after the end of the clamp pulse. Unlike auto offset it does not require that these 16 clock cycles occur during the back porch reference time, although that is what is recommended. During auto gain matching operation, the data outputs of the AD9983A are frozen (held at the value they had just prior to operation). The auto gain matching function can be programmed to run continuously or on a one-time basis (see the 0x3C—Bit[3] Auto Gain Matching Hold section).

### **SYNC-ON-GREEN**

The sync-on-green inputs (SOGIN0, SOGIN1) operate in two steps. First, they set a baseline clamp level off of the incoming video signal with a negative peak detector. Second, they set the sync trigger level to a programmable (Register 0x1D, Bits[7:3]) level (typically 128 mV) above the negative peak. The sync-ongreen inputs must be ac-coupled to the green analog input through their own capacitors. The value of the capacitors must be 1 nF  $\pm$ 20%. If sync-on-green is not used, this connection is not required. The sync-on-green signal always has negative polarity.

Figure 4. Typical Input Configuration

### **REFERENCE BYPASSING**

REFLO and REFHI are connected to each other by a 10  $\mu F$  capacitor. These references are used by the input ADC circuitry.

Figure 5. Input Amplifier Reference Capacitors

### **CLOCK GENERATION**

A PLL is used to generate the pixel clock. The Hsync input provides a reference frequency to the PLL. A voltage controlled oscillator (VCO) generates a much higher pixel clock frequency. The pixel clock is divided by the PLL divide value (Register 0x01 and Register 0x02) and phase-compared with the Hsync input. Any error is used to shift the VCO frequency and maintain lock between the two signals.

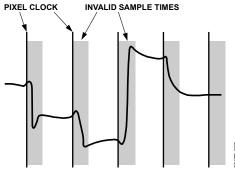

The stability of this clock is a very important element in providing the clearest and most stable image. During each pixel time, there is a period during which the signal slews from the old pixel amplitude and settles at its new value. Then there is a time when the input voltage is stable, before the signal must slew to a new value (see Figure 6). The ratio of the slewing time to the stable time is a function of the bandwidth of the graphics DAC and the bandwidth of the transmission system (cable and termination). It is also a function of the overall pixel rate. Clearly, if the dynamic characteristics of the system remain fixed, then the slewing and settling time is likewise fixed. This time must be subtracted from the total pixel period, leaving the stable period. At higher pixel frequencies, the total cycle time is shorter and the stable pixel time also becomes shorter.

Figure 6. Pixel Sampling Times

Any jitter in the clock reduces the precision with which the sampling time can be determined and must also be subtracted from the stable pixel time. Considerable care has been taken in the design of the AD9983A clock generation circuit to minimize jitter. The clock jitter of the AD9983A is low in all operating modes, making the reduction in the valid sampling time due to jitter negligible.

The PLL characteristics are determined by the loop filter design, the PLL charge pump current, and the VCO range setting. The loop filter design is shown in Figure 7. Recommended settings of the VCO range and charge pump current for VESA standard display modes are listed in Table 10.

Figure 7. PLL Loop Filter Detail

Four programmable registers are provided to optimize the performance of the PLL. These registers are the 12-Bit Divisor Register, the 2-Bit VCO Range Register, the 3-Bit Charge Pump Current Register, and the 5-Bit Phase Adjust Register.

### The 12-Bit Divisor Register

The input Hsync frequencies can accommodate any Hsync as long as the product of the Hsync and the PLL divisor falls within the operating range of the VCO. The PLL multiplies the frequency of the Hsync signal, producing pixel clock frequencies in the range of 10 MHz to 140 MHz. The divisor register controls the exact multiplication factor. This register may be set to any value between 2 and 4095 as long as the output frequency is within range.

# The 2-Bit VCO Range Register

To improve the noise performance of the AD9983A, the VCO operating frequency range is divided into four overlapping regions. The VCO range register sets this operating range. The frequency ranges for the four regions are shown in Table 8.

**Table 8. VCO Frequency Ranges**

|  | 1 ; 0 |     |             |              |  |  |  |

|--|-------|-----|-------------|--------------|--|--|--|

|  |       |     | Pixel Clock | KVCO         |  |  |  |

|  | PV1   | PV0 | Range (MHz) | Gain (MHz/V) |  |  |  |

|  | 0     | 0   | 10 to 21    | 150          |  |  |  |

|  | 0     | 1   | 21 to 42    | 150          |  |  |  |

|  | 1     | 0   | 42 to 84    | 150          |  |  |  |

|  | 1     | 1   | 84 to 140   | 150          |  |  |  |

### The 3-Bit Charge Pump Current Register

This register varies the current that drives the low pass loop filter. The possible current values are listed in Table 9.

Table 9. Charge Pump Current/Control Bits

| lp2 | lp1 | lp0 | Current (µA) |  |

|-----|-----|-----|--------------|--|

| 0   | 0   | 0   | 50           |  |

| 0   | 0   | 1   | 100          |  |