# High Speed, Low Power Monolithic Op Amp

**AD847**

#### **FEATURES**

**Superior Performance**

High Unity Gain BW: 50 MHz Low Supply Current: 5.3 mA High Slew Rate: 300 V/μs Excellent Video Specifications

0.04% Differential Gain (NTSC and PAL) 0.19° Differential Phase (NTSC and PAL)

**Drives Any Capacitive Load**

Fast Settling Time to 0.1% (10 V Step): 65 ns

**Excellent DC Performance**

High Open-Loop Gain 5.5 V/mV ( $R_{LOAD}$  = 1 k $\Omega$ )

Low Input Offset Voltage: 0.5 mV

Specified for ±5 V and ±15 V Operation

Available in a Wide Variety of Options

Plastic DIP and SOIC Packages

Cerdip Package Die Form

DIE FUITH

MIL-STD-883B Processing

Tape & Reel (EIA-481A Standard)

Dual Version Available: AD827 (8 Lead) Enhanced Replacement for LM6361

Replacement for HA2544, HA2520/2/5 and EL2020

#### **APPLICATIONS**

Video Instrumentation Imaging Equipment Copiers, Fax, Scanners, Cameras High Speed Cable Driver High Speed DAC and Flash ADC Buffers

#### PRODUCT DESCRIPTION

The AD847 represents a breakthrough in high speed amplifiers offering superior ac & dc performance and low power, all at low cost. The excellent dc performance is demonstrated by its  $\pm 5~\rm V$

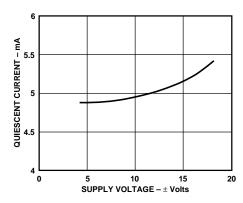

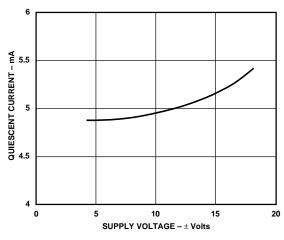

Quiescent Current vs. Supply Voltage

#### REV. F

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

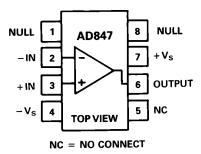

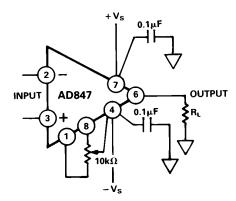

#### CONNECTION DIAGRAM

Plastic DIP (N), Small Outline (R) and Cerdip (Q) Packages

specifications which include an open-loop gain of 3500 V/V (500  $\Omega$  load) and low input offset voltage of 0.5 mV. Commonmode rejection is a minimum of 78 dB. Output voltage swing is  $\pm 3$  V into loads as low as 150  $\Omega$ . Analog Devices also offers over 30 other high speed amplifiers from the low noise AD829 (1.7 nV/ $\overline{\text{Hz}}$ ) to the ultimate video amplifier, the AD811, which features 0.01% differential gain and 0.01° differential phase.

#### APPLICATION HIGHLIGHTS

- 1. As a buffer the AD847 offers a full-power bandwidth of 12.7 MHz (5 V p-p with  $\pm 5$  V supplies) making it outstanding as an input buffer for flash A/D converters.

- 2. The low power and small outline package of the AD847 make it very well suited for high density applications such as multiple pole active filters.

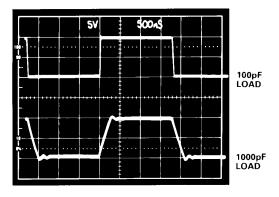

- 3. The AD847 is internally compensated for unity gain operation and remains stable when driving any capacitive load.

AD847 Driving Capacitive Loads

# **AD847\* Product Page Quick Links**

Last Content Update: 11/01/2016

# Comparable Parts

View a parametric search of comparable parts

# Evaluation Kits <a> □</a>

Universal Evaluation Board for Single High Speed Operational Amplifiers

### Documentation <a>□</a>

#### **Application Notes**

- AN-402: Replacing Output Clamping Op Amps with Input Clamping Amps

- AN-417: Fast Rail-to-Rail Operational Amplifiers Ease Design Constraints in Low Voltage High Speed Systems

- AN-581: Biasing and Decoupling Op Amps in Single Supply Applications

#### **Data Sheet**

- AD847: High Speed, Low Power Monolithic Op Amp Data Sheet

- AD847: Military Data Sheet

#### **User Guides**

UG-135: Evaluation Board for Single, High Speed Operational Amplifiers (8-Lead SOIC and Exposed Paddle)

# Tools and Simulations

- · Analog Filter Wizard

- · Analog Photodiode Wizard

- Power Dissipation vs Die Temp

- VRMS/dBm/dBu/dBV calculators

- AD847 SPICE Macro-Model

## Reference Materials

#### **Product Selection Guide**

High Speed Amplifiers Selection Table

#### **Tutorials**

- MT-032: Ideal Voltage Feedback (VFB) Op Amp

- MT-033: Voltage Feedback Op Amp Gain and Bandwidth

- MT-047: Op Amp Noise

- MT-048: Op Amp Noise Relationships: 1/f Noise, RMS Noise, and Equivalent Noise Bandwidth

- MT-049: Op Amp Total Output Noise Calculations for Single-Pole System

- MT-050: Op Amp Total Output Noise Calculations for Second-Order System

- MT-052: Op Amp Noise Figure: Don't Be Misled

- MT-053: Op Amp Distortion: HD, THD, THD + N, IMD, SFDR, MTPR

- MT-056: High Speed Voltage Feedback Op Amps

- MT-058: Effects of Feedback Capacitance on VFB and CFB Op Amps

- MT-059: Compensating for the Effects of Input Capacitance on VFB and CFB Op Amps Used in Current-to-Voltage Converters

- MT-060: Choosing Between Voltage Feedback and Current Feedback Op Amps

# Design Resources <a>□</a>

- AD847 Material Declaration

- PCN-PDN Information

- · Quality And Reliability

- · Symbols and Footprints

# Discussions 4

View all AD847 EngineerZone Discussions

# Sample and Buy -

Visit the product page to see pricing options

# Technical Support -

Submit a technical question or find your regional support number

<sup>\*</sup> This page was dynamically generated by Analog Devices, Inc. and inserted into this data sheet. Note: Dynamic changes to the content on this page does not constitute a change to the revision number of the product data sheet. This content may be frequently modified.

# $\begin{cases} AD847-SPECIFICATIONS (@ T_A = +25 ^{\circ}C, unless otherwise noted) \end{cases}$

| Model                                          | Conditions                                                                                                                                         | Vs                             | Min                          | AD847J<br>Typ     | Max               | A<br>Min               | D847AR<br>Typ     | Max               | Units                |

|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|------------------------------|-------------------|-------------------|------------------------|-------------------|-------------------|----------------------|

| INPUT OFFSET VOLTAGE <sup>1</sup>              | Conditions                                                                                                                                         | ±5 V                           | 141111                       | 0.5               | 1                 | IVALIA                 | 0.5               | 1                 | mV                   |

| Offset Drift                                   | T <sub>MIN</sub> to T <sub>MAX</sub>                                                                                                               |                                |                              | 15                | 3.5               |                        | 15                | 4                 | mV<br>μV/°C          |

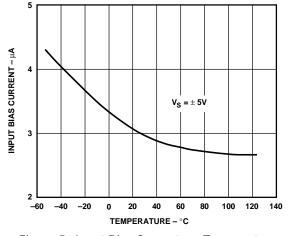

| INPUT BIAS CURRENT                             | T <sub>MIN</sub> to T <sub>MAX</sub>                                                                                                               | ±5 V, ±15 V                    |                              | 3.3               | <b>6.6</b> 7.2    |                        | 3.3               | <b>6.6</b> 10     | μA<br>μA             |

| INPUT OFFSET CURRENT                           | T <sub>MIN</sub> to T <sub>MAX</sub>                                                                                                               | ±5 V, ±15 V                    |                              | 50                | <b>300</b><br>400 |                        | 50                | <b>300</b><br>500 | nA<br>nA             |

| Offset Current Drift                           | V +0.5 V                                                                                                                                           |                                |                              | 0.3               |                   |                        | 0.3               |                   | nA/°C                |

| OPEN-LOOP GAIN                                 | $V_{OUT} = \pm 2.5 \text{ V}$ $R_{LOAD} = 500 \Omega$ $T_{MIN} \text{ to } T_{MAX}$ $R_{LOAD} = 150 \Omega$ $V_{OUT} = \pm 10 \text{ V}$           | ±5 V<br>±15 V                  | <b>2</b><br>1                | 3.5<br>1.6        |                   | <b>2</b><br>1          | 3.5<br>1.6        |                   | V/mV<br>V/mV<br>V/mV |

|                                                | $R_{LOAD} = 1 \text{ k}\Omega$ $T_{MIN} \text{ to } T_{MAX}$                                                                                       |                                | <b>3</b><br>1.5              | 5.5               |                   | 3<br>1.5               | 5.5               |                   | V/mV<br>V/mV         |

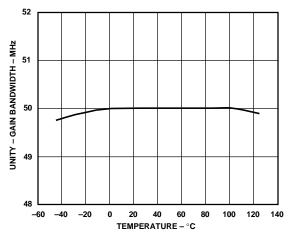

| DYNAMIC PERFORMANCE<br>Unity Gain Bandwidth    |                                                                                                                                                    | ±5 V<br>±15 V                  |                              | 35<br>50          |                   |                        | 35<br>50          |                   | MHz<br>MHz           |

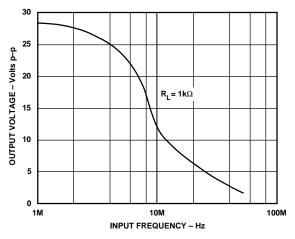

| Full Power Bandwidth <sup>2</sup>              | $\begin{aligned} V_{OUT} &= 5 \text{ V p-p} \\ R_{LOAD} &= 500 \Omega, \\ V_{OUT} &= 20 \text{ V p-p}, \end{aligned}$                              | ±5 V                           |                              | 12.7              |                   |                        | 12.7              |                   | MHz                  |

| Slew Rate <sup>3</sup>                         | $\begin{aligned} R_{LOAD} &= 1 \ k\Omega \\ R_{LOAD} &= 1 \ k\Omega \end{aligned}$                                                                 | ±15 V<br>±5 V<br>±15 V         | 225                          | 4.7<br>200<br>300 |                   | 225                    | 4.7<br>200<br>300 |                   | MHz<br>V/μs<br>V/μs  |

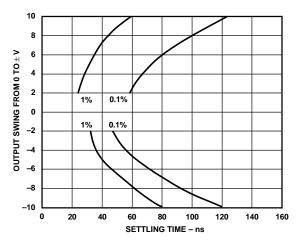

| Settling Time to 0.1%, $R_{LOAD} = 250 \Omega$ | -2.5 V to +2.5 V<br>10 V Step, A <sub>V</sub> = -1                                                                                                 | ±5 V<br>±15 V                  |                              | 65<br>65          |                   |                        | 65<br>65          |                   | ns<br>ns             |

| to 0.01%, $R_{LOAD} = 250 \Omega$              | -2.5 V to +2.5 V<br>10 V Step, A <sub>V</sub> = -1                                                                                                 | ±5 V<br>±15 V                  |                              | 140<br>120        |                   |                        | 140<br>120        |                   | ns<br>ns             |

| Phase Margin  Differential Gain                | $\begin{split} C_{LOAD} &= 10 \text{ pF} \\ R_{LOAD} &= 1 \text{ k}\Omega \\ f &\approx 4.4 \text{ MHz}, R_{LOAD} = 1 \text{ k}\Omega \end{split}$ | ±15 V<br>±15 V                 |                              | 50<br>0.04        |                   |                        | 50<br>0.04        |                   | Degree<br>%          |

| Differential Phase                             | $f \approx 4.4 \text{ MHz}, R_{LOAD} = 1 \text{ k}\Omega$                                                                                          | ±15 V                          |                              | 0.19              |                   |                        | 0.19              |                   | Degree               |

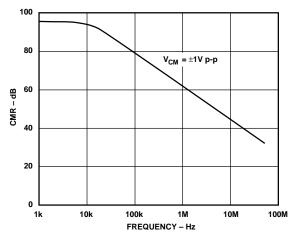

| COMMON-MODE REJECTION                          | $V_{CM} = \pm 2.5 \text{ V}$ $V_{CM} = \pm 12 \text{ V}$ $T_{MIN} \text{ to } T_{MAX}$                                                             | ±5 V<br>±15 V                  | <b>78</b><br><b>78</b><br>75 | 95<br>95          |                   | <b>78 78</b> 75        | 95<br>95          |                   | dB<br>dB<br>dB       |

| POWER SUPPLY REJECTION                         | $V_S = \pm 5 \text{ V to } \pm 15 \text{ V}$ $T_{MIN}$ to $T_{MAX}$                                                                                |                                | <b>75</b><br>72              | 86                |                   | <b>75</b><br>72        | 86                |                   | dB<br>dB             |

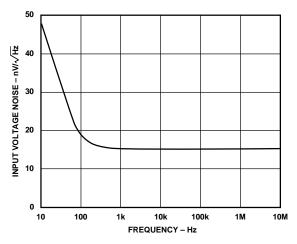

| INPUT VOLTAGE NOISE                            | f = 10 kHz                                                                                                                                         | ±15 V                          |                              | 15                |                   |                        | 15                |                   | nV/√Hz               |

| INPUT CURRENT NOISE                            | f = 10 kHz                                                                                                                                         | ±15 V                          |                              | 1.5               |                   |                        | 1.5               |                   | pA/√Hz               |

| INPUT COMMON-MODE<br>VOLTAGE RANGE             |                                                                                                                                                    | ±5 V                           |                              | +4.3<br>-3.4      |                   |                        | +4.3<br>-3.4      |                   | V<br>V               |

|                                                |                                                                                                                                                    | ±15 V                          |                              | +14.3<br>-13.4    |                   |                        | +14.3<br>-13.4    |                   | V<br>V               |

| OUTPUT VOLTAGE SWING                           | $\begin{aligned} R_{LOAD} &= 500~\Omega\\ R_{LOAD} &= 150~\Omega\\ R_{LOAD} &= 1~k\Omega\\ R_{LOAD} &= 500~\Omega \end{aligned}$                   | ±5 V<br>±5 V<br>±15 V<br>±15 V | 3.0<br>2.5<br>12<br>10       | 3.6<br>3          |                   | 3.0<br>2.5<br>12<br>10 | 3.6               |                   | ±V<br>±V<br>±V       |

| Short-Circuit Current                          |                                                                                                                                                    | ±15 V                          |                              | 32                |                   |                        | 32                |                   | mA                   |

| INPUT RESISTANCE                               |                                                                                                                                                    |                                |                              | 300               |                   |                        | 300               |                   | kΩ                   |

| INPUT CAPACITANCE                              |                                                                                                                                                    |                                |                              | 1.5               |                   |                        | 1.5               |                   | pF                   |

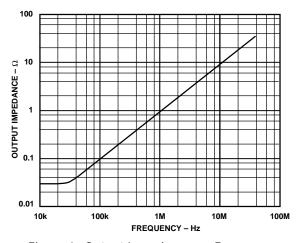

| OUTPUT RESISTANCE                              | Open Loop                                                                                                                                          |                                |                              | 15                |                   |                        | 15                |                   | Ω                    |

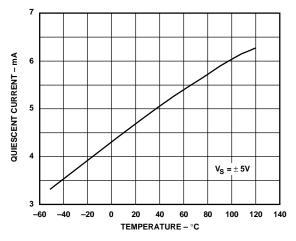

| POWER SUPPLY Operating Range Quiescent Current | B B                                                                                                                                                | ±5 V                           | ±4.5                         | 4.8               | ±18<br>6.0        | ±4.5                   | 4.8               | ±18<br>6.0        | V<br>mA              |

|                                                | T <sub>MIN</sub> to T <sub>MAX</sub>                                                                                                               | ±15 V                          |                              | 5.3               | 7.3<br><b>6.3</b> |                        | 5.3               | 7.3<br><b>6.3</b> | mA<br>mA             |

|                                                | T <sub>MIN</sub> to T <sub>MAX</sub>                                                                                                               |                                |                              |                   | 7.6               |                        |                   | 7.6               | mA                   |

REV. F -2-

NOTES  $^{l}$  Input Offset Voltage Specifications are guaranteed after 5 minutes at  $T_{A}$  = +25  $^{\circ}C.$

$<sup>^{2}</sup>$ Full Power Bandwidth = Slew Rate/2  $\pi$  V<sub>PEAK</sub>.

<sup>&</sup>lt;sup>3</sup>Slew Rate is measured on rising edge.

All min and max specifications are guaranteed. Specifications in **boldface** are 100% tested at final electrical test. Specifications subject to change without notice.

| Model                                          | Conditions                                                                                                             | V <sub>s</sub> | AD847AQ<br>Min Typ Max |                |            | AD847S<br>Min Typ |                | Max        | Units        |

|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|----------------|------------------------|----------------|------------|-------------------|----------------|------------|--------------|

| INPUT OFFSET VOLTAGE <sup>1</sup>              |                                                                                                                        | ±5 V           |                        | 0.5            | 1          |                   | 0.5            | 1          | mV           |

| Offset Drift                                   | $T_{MIN}$ to $T_{MAX}$                                                                                                 |                |                        | 15             | 4          |                   | 15             | 4          | mV<br>μV/°C  |

| INPUT BIAS CURRENT                             | $ m T_{MIN}$ to $ m T_{MAX}$                                                                                           | ±5 V, ±15 V    |                        | 3.3            | 5<br>7.5   |                   | 3.3            | 5<br>7.5   | μΑ<br>μΑ     |

| INPUT OFFSET CURRENT                           |                                                                                                                        | ±5 V, ±15 V    |                        | 50             | 300        |                   | 50             | 300        | nA           |

| Offset Current Drift                           | $T_{MIN}$ to $T_{MAX}$                                                                                                 |                |                        | 0.3            | 400        |                   | 0.3            | 400        | nA<br>nA/°C  |

| OPEN-LOOP GAIN                                 | $V_{OUT} = \pm 2.5 \text{ V}$                                                                                          | ±5 V           |                        | 0.5            |            |                   | 0.5            |            | 37/37        |

|                                                | $R_{LOAD} = 500 \Omega$ $T_{MIN} \text{ to } T_{MAX}$                                                                  |                | 2 1                    | 3.5            |            | 2 1               | 3.5            |            | V/mV<br>V/mV |

|                                                | $R_{LOAD} = 150 \Omega$                                                                                                | . 45 77        |                        | 1.6            |            |                   | 1.6            |            | V/mV         |

|                                                | $V_{OUT} = \pm 10 \text{ V}$ $R_{LOAD} = 1 \text{ k}\Omega$                                                            | ±15 V          | 3                      | 5.5            |            | 3                 | 5.5            |            | V/mV         |

|                                                | $T_{MIN}$ to $T_{MAX}$                                                                                                 |                | 1.5                    | 0.0            |            | 1.5               | 0.0            |            | V/mV         |

| DYNAMIC PERFORMANCE                            |                                                                                                                        |                |                        |                |            |                   |                |            |              |

| Unity Gain Bandwidth                           |                                                                                                                        | ±5 V<br>±15 V  |                        | 35<br>50       |            |                   | 35<br>50       |            | MHz          |

| Full Power Bandwidth <sup>2</sup>              | $V_{OUT} = 5 \text{ V p-p}$                                                                                            | ±15 V          |                        | 50             |            |                   | 30             |            | MHz          |

|                                                | $R_{LOAD} = 500 \Omega$                                                                                                | ±5 V           |                        | 12.7           |            |                   | 12.7           |            | MHz          |

|                                                | $V_{OUT} = 20 \text{ V p-p},$ $R_{LOAD} = 1 \text{ k}\Omega$                                                           | ±15 V          |                        | 4.7            |            |                   | 4.7            |            | MHz          |

| Slew Rate <sup>3</sup>                         | $R_{LOAD} = 1 \text{ k}\Omega$<br>$R_{LOAD} = 1 \text{ k}\Omega$                                                       | ±5 V           |                        | 200            |            |                   | 200            |            | V/µs         |

| C. vilt Tr                                     |                                                                                                                        | ±15 V          | 225                    | 300            |            | 225               | 300            |            | V/µs         |

| Settling Time to 0.1%, $R_{LOAD} = 250 \Omega$ | -2.5 V to +2.5 V                                                                                                       | ±5 V           |                        | 65             |            |                   | 65             |            | ns           |

| ·                                              | 10 V Step, $A_V = -1$                                                                                                  | ±15 V          |                        | 65             |            |                   | 65             |            | ns           |

| to 0.01%, $R_{LOAD} = 250 \Omega$              | -2.5 V to +2.5 V                                                                                                       | ±5 V<br>±15 V  |                        | 140<br>120     |            |                   | 140<br>120     |            | ns           |

| Phase Margin                                   | $10 \text{ V Step}, A_V = -1$<br>$C_{LOAD} = 10 \text{ pF}$                                                            | ±15 V<br>±15 V |                        | 120            |            |                   | 120            |            | ns           |

|                                                | $R_{LOAD} = 1 k\hat{\Omega}$                                                                                           |                |                        | 50             |            |                   | 50             |            | Degree       |

| Differential Gain<br>Differential Phase        | $f \approx 4.4 \text{ MHz}, R_{LOAD} = 1 \text{ k}\Omega$<br>$f \approx 4.4 \text{ MHz}, R_{LOAD} = 1 \text{ k}\Omega$ | ±15 V<br>±15 V |                        | $0.04 \\ 0.19$ |            |                   | $0.04 \\ 0.19$ |            | %<br>Degree  |

| COMMON-MODE REJECTION                          | $V_{CM} = \pm 2.5 \text{ V}$                                                                                           | ±5 V           | 80                     | 95             |            | 80                | 95             |            | dB           |

|                                                | $V_{\rm CM} = \pm 12 \text{ V}$                                                                                        | ±15 V          | 80                     | 95             |            | 80                | 95             |            | dB           |

|                                                | T <sub>MIN</sub> to T <sub>MAX</sub>                                                                                   |                | 75                     |                |            | 75                |                |            | dB           |

| POWER SUPPLY REJECTION                         | $V_S = \pm 5 \text{ V to } \pm 15 \text{ V}$<br>$T_{MIN} \text{ to } T_{MAX}$                                          |                | 75<br>72               | 86             |            | 75<br>72          | 86             |            | dB<br>dB     |

| INPUT VOLTAGE NOISE                            | f = 10  kHz                                                                                                            | ±15 V          |                        | 15             |            |                   | 15             |            | nV/√Hz       |

| INPUT CURRENT NOISE                            | f = 10  kHz                                                                                                            | ±15 V          |                        | 1.5            |            |                   | 1.5            |            | pA/√Hz       |

| INPUT COMMON-MODE                              |                                                                                                                        | . ~ **         |                        | 4.0            |            |                   | 4.0            |            | **           |

| VOLTAGE RANGE                                  |                                                                                                                        | ±5 V           |                        | +4.3<br>-3.4   |            |                   | +4.3<br>-3.4   |            | V            |

|                                                |                                                                                                                        | ±15 V          |                        | +14.3          |            |                   | +14.3          |            | V            |

|                                                |                                                                                                                        |                |                        | -13.4          |            |                   | -13.4          |            | V            |

| OUTPUT VOLTAGE SWING                           | $R_{LOAD} = 500 \Omega$<br>$R_{LOAD} = 150 \Omega$                                                                     | ±5 V<br>±5 V   | 3.0<br>2.5             | 3.6<br>3       |            | 3.0<br>2.5        | 3.6<br>3       |            | ±V<br>±V     |

|                                                | $R_{LOAD} = 130 \Omega$<br>$R_{LOAD} = 1 k\Omega$                                                                      | ±15 V          | 12                     | 3              |            | 12                | J              |            | ±V           |

|                                                | $R_{LOAD} = 500 \Omega$                                                                                                | ±15 V          | 10                     |                |            | 10                |                |            | ±V           |

| Short-Circuit Current                          |                                                                                                                        | ±15 V          |                        | 32             |            |                   | 32             |            | mA           |

| INPUT RESISTANCE                               |                                                                                                                        |                | -                      | 300            |            |                   | 300            |            | kΩ           |

| INPUT CAPACITANCE                              |                                                                                                                        |                |                        | 1.5            |            |                   | 1.5            |            | pF           |

| OUTPUT RESISTANCE                              | Open Loop                                                                                                              |                | 1                      | 15             |            |                   | 15             |            | Ω            |

| POWER SUPPLY<br>Operating Range                |                                                                                                                        |                | ±4.5                   |                | ±18        | ±4.5              |                | ±18        | V            |

| Quiescent Current                              |                                                                                                                        | ±5 V           | -4.5                   | 4.8            | 5.7        | -4.0              | 4.8            | 5.7        | mA           |

|                                                | $T_{\text{MIN}}$ to $T_{\text{MAX}}$                                                                                   | 11537          |                        | r 0            | 7.0        |                   | r 0            | 7.8        | mA           |

|                                                | $T_{\text{MIN}}$ to $T_{\text{MAX}}$                                                                                   | ±15 V          |                        | 5.3            | 6.3<br>7.6 |                   | 5.3            | 6.3<br>8.4 | mA<br>mA     |

REV. F -3-

# **AD847**

#### ABSOLUTE MAXIMUM RATINGS<sup>1</sup>

| Supply Voltage                                   |

|--------------------------------------------------|

| Internal Power Dissipation <sup>2</sup>          |

| Plastic (N)                                      |

| Small Outline (R) 0.8 Watts                      |

| Cerdip (Q)                                       |

| Input Voltage                                    |

| Differential Input Voltage±6 V                   |

| Storage Temperature Range (Q)65°C to +150°C      |

| (N, R)65°C to +125°C                             |

| Junction Temperature175°C                        |

| Lead Temperature Range (Soldering 60 sec) +300°C |

#### NOTES

<sup>1</sup>Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

$^2$ Mini-DIP Package:  $\theta_{JA}=100^{\circ} C/Watt; \ \theta_{JC}=33^{\circ} C/Watt$  Cerdip Package:  $\theta_{JA}=110^{\circ} C/Watt; \ \theta_{JC}=30^{\circ} C/Watt$  Small Outline Package:  $\theta_{JA}=155^{\circ} C/Watt; \ \theta_{JC}=33^{\circ} C/Watt$

#### ESD SUSCEPTIBILITY

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 volts, which readily accumulate on the human body and on test equipment, can discharge without detection. Although the AD847 features proprietary ESD protection circuitry, permanent damage may still occur on these devices if they are subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid any performance degradation or loss of functionality.

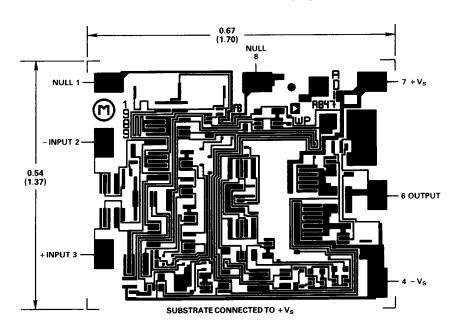

#### METALIZATION PHOTOGRAPH

Contact factory for latest dimensions. Dimensions shown in inches and (mm).

#### **ORDERING GUIDE**

| Models*        | Temperature<br>Range – °C | Package<br>Description | Package<br>Option |

|----------------|---------------------------|------------------------|-------------------|

| AD847JN        | 0 to +70                  | Plastic                | N-8               |

| AD847JR        | 0 to +70                  | SOIC                   | R-8               |

| AD847AQ        | -40 to +85                | Cerdip                 | Q-8               |

| AD847AR        | -40 to +85                | SOIC                   | R-8               |

| AD847SQ        | -55 to +125               | Cerdip                 | Q-8               |

| AD847SQ/883B   | -55 to +125               | Cerdip                 | Q-8               |

| 5962-8964701PA | -55 to +125               | Cerdip                 | Q-8               |

<sup>\*</sup>AD847 also available in J and S grade chips, and AD847JR and AD847AR are available in tape and reel.

–4– REV. F

# Typical Characteristics (@ +25°C and $V_S = \pm 15 V$ , unless otherwise noted)

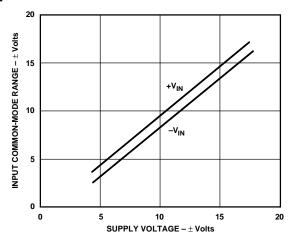

Figure 1. Input Common-Mode Range vs. Supply Voltage

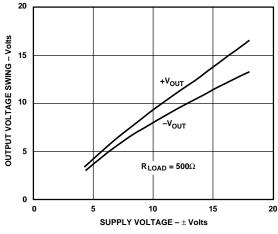

Figure 2. Output Voltage Swing vs. Supply Voltage

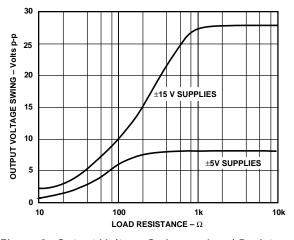

Figure 3. Output Voltage Swing vs. Load Resistance

Figure 4. Quiescent Current vs. Supply Voltage

Figure 5. Input Bias Current vs. Temperature

Figure 6. Output Impedance vs. Frequency

REV. F \_5\_

# AD847—Typical Characteristics (@ $\pm 25^{\circ}$ C and $V_s = \pm 15$ V, unless otherwise noted)

Figure 7. Quiescent Current vs. Temperature

Figure 9. Gain Bandwidth Product vs. Temperature

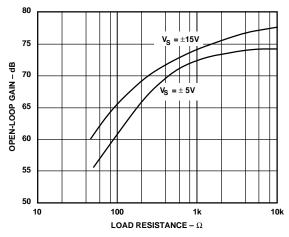

Figure 11. Open-Loop Gain vs. Load Resistance

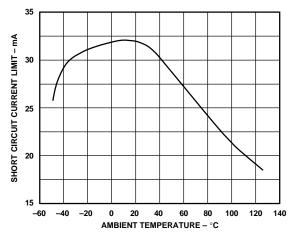

Figure 8. Short-Circuit Current Limit vs. Temperature

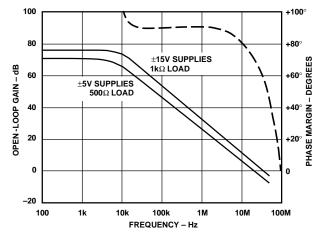

Figure 10. Open-Loop Gain and Phase Margin vs. Frequency

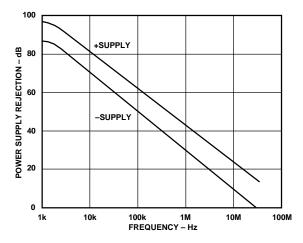

Figure 12. Power Supply Rejection vs. Frequency

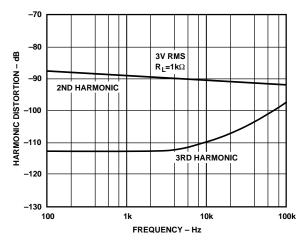

-6- REV. F

Figure 13. Common-Mode Rejection vs. Frequency

Figure 15. Output Swing and Error vs. Settling Time

Figure 17. Input Voltage Noise Spectral Density

Figure 14. Large Signal Frequency Response

Figure 16. Harmonic Distortion vs. Frequency

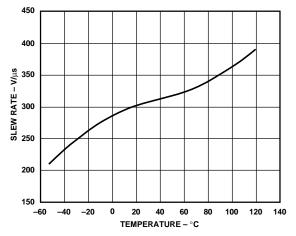

Figure 18. Slew Rate vs. Temperature

REV. F -7-

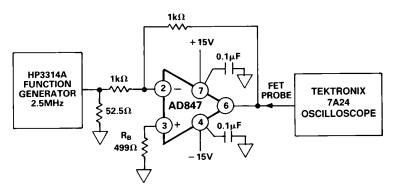

Figure 19. Inverting Amplifier Configuration

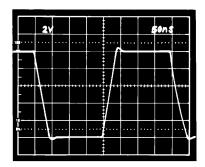

Figure 19a. Inverter Large Signal Pulse Response

Figure 19b. Inverter Small Signal Pulse Response

Figure 20. Noninverting Amplifier Configuration

Figure 20a. Noninverting Large Signal Pulse Response

Figure 20b. Noninverting Small Signal Pulse Response

-8- REV. F

#### **OFFSET NULLING**

The input offset voltage of the AD847 is very low for a high speed op amp, but if additional nulling is required, the circuit shown in Figure 21 can be used.

Figure 21. Offset Nulling

#### INPUT CONSIDERATIONS

An input resistor ( $R_{\rm IN}$  in Figure 20) is required in circuits where the input to the AD847 will be subjected to transient or continuous overload voltages exceeding the  $\pm 6$  V maximum differential limit. This resistor provides protection for the input transistors by limiting the maximum current that can be forced into their bases.

For high performance circuits it is recommended that a resistor ( $R_{\rm B}$  in Figures 19 and 20) be used to reduce bias current errors by matching the impedance at each input. The offset voltage error will be reduced by more than an order of magnitude.

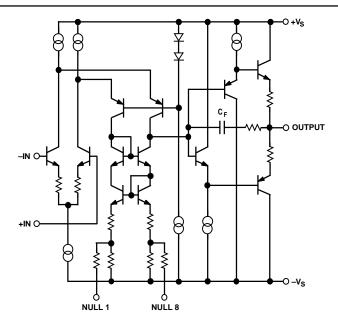

#### THEORY OF OPERATION

The AD847 is fabricated on Analog Devices' proprietary complementary bipolar (CB) process which enables the construction of pnp and npn transistors with similar  $f_{T}s$  in the 600 MHz to 800 MHz region. The AD847 circuit (Figure 22) includes an npn input stage followed by fast pnps in the folded cascode intermediate gain stage. The CB pnps are also used in the current amplifying output stage. The internal compensation capacitance that makes the AD847 unity gain stable is provided by the junction capacitances of transistors in the gain stage.

The capacitor,  $C_F$ , in the output stage mitigates the effect of capacitive loads. At low frequencies and with low capacitive loads, the gain from the compensation node to the output is very close to unity. In this case  $C_F$  is bootstrapped and does not contribute to the compensation capacitance of the part. As the capacitive load is increased, a pole is formed with the output impedance of the output stage. This reduces the gain, and therefore,  $C_F$  is incompletely bootstrapped. Some fraction of  $C_F$  contributes to the compensation capacitance, and the unity gain bandwidth falls. As the load capacitance is increased, the bandwidth continues to fall, and the amplifier remains stable.

Figure 22. AD847 Simplified Schematic

#### **GROUNDING AND BYPASSING**

In designing practical circuits with the AD847, the user must remember that whenever high frequencies are involved, some special precautions are in order. Circuits must be built with short interconnect leads. A large ground plane should be used whenever possible to provide a low resistance, low inductance circuit path, as well as minimizing the effects of high frequency coupling. Sockets should be avoided because the increased interlead capacitance can degrade bandwidth.

Feedback resistors should be of low enough value to assure that the time constant formed with the capacitance at the amplifier summing junction will not limit the amplifier performance. Resistor values of less than 5 k $\Omega$  are recommended. If a larger resistor must be used, a small (<10 pF) feedback capacitor in parallel with the feedback resistor,  $R_F$ , may be used to compensate for the input capacitances and optimize the dynamic performance of the amplifier.

Power supply leads should be bypassed to ground as close as possible to the amplifier pins. Ceramic disc capacitors of 0.1  $\mu F$  are recommended.

REV. F \_9=

## **AD847**

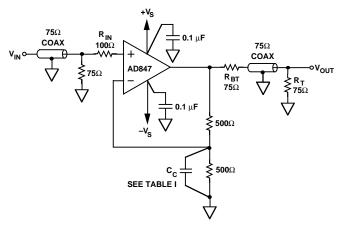

#### **VIDEO LINE DRIVER**

The AD847 functions very well as a low cost, high speed line driver for either terminated or unterminated cables. Figure 23 shows the AD847 driving a doubly terminated cable in a follower configuration.

The termination resistor,  $R_T$ , (when equal to the cable's characteristic impedance) minimizes reflections from the far end of the cable. While operating from  $\pm 5$  V supplies, the AD847 maintains a typical slew rate of 200 V/ $\mu$ s, which means it can drive a  $\pm 1$  V, 30 MHz signal into a terminated cable.

Figure 23. Video Line Driver

**Table I. Video Line Driver Performance Chart**

| V <sub>IN</sub> *    | V <sub>SUPPLY</sub> | C <sub>C</sub> | -3 dB B <sub>W</sub> | Over-<br>shoot |

|----------------------|---------------------|----------------|----------------------|----------------|

| 0 dB or ±500 mV Step | ±15                 | 20 pF          | 23 MHz               | 4%             |

| 0 dB or ±500 mV Step | ±15                 | 15 pF          | 21 MHz               | 0%             |

| 0 dB or ±500 mV Step | ±15                 | 0 pF           | 13 MHz               | 0%             |

| 0 dB or ±500 mV Step | ±5                  | 20 pF          | 18 MHz               | 2%             |

| 0 dB or ±500 mV Step | ±5                  | 15 pF          | 16 MHz               | 0%             |

| 0 dB or ±500 mV Step | ±5                  | 0 pF           | 11 MHz               | 0%             |

<sup>\*-3</sup> dB bandwidth numbers are for the 0 dBm signal input. Overshoot numbers are the percent overshoot of the 1 volt step input.

A back-termination resistor  $(R_{BT},$  also equal to the characteristic impedance of the cable) may be placed between the AD847 output and the cable input, in order to damp any reflected signals caused by a mismatch between  $R_T$  and the cable's characteristic impedance. This will result in a flatter frequency response, although this requires that the op amp supply  $\pm 2~V$  to the output in order to achieve a  $\pm 1~V$  swing at resistor  $R_T$ .

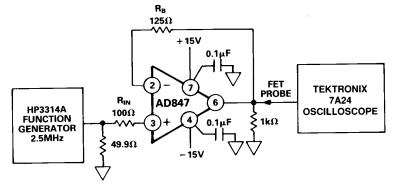

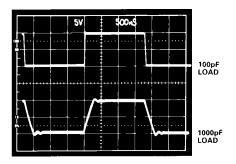

Figure 24 shows the AD847 driving 100 pF and 1000 pF loads.

Figure 24. AD847 Driving Capacitive Loads

#### FLASH ADC INPUT BUFFER

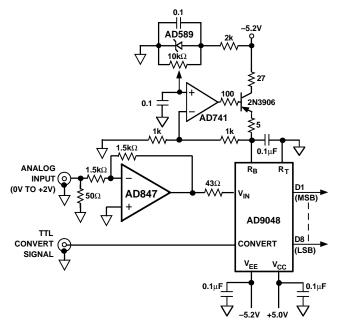

The 35 MHz unity gain bandwidth of the AD847 makes it an excellent choice for buffering the input of high speed flash A/D converters, such as the AD9048.

Figure 25 shows the AD847 as a unity inverter for the input to the AD9048.

Figure 25. Flash ADC Input Buffer

–10– REV. F

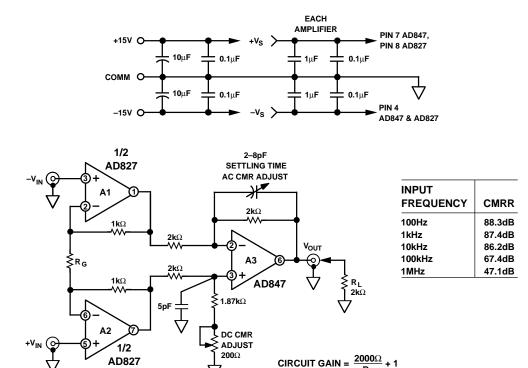

#### A High Speed, Three Op-Amp In-Amp

The circuit of Figure 26 lends itself well to CCD imaging and other video speed applications. It uses two high speed CB process op-amps: Amplifier A3, the output amplifier, is an AD847.

The input amplifier (A1 and A2) is an AD827, which is a dual version of the AD847. This circuit has the optional flexibility of both dc and ac trims for common-mode rejection, plus the ability to adjust for minimum settling time.

#### BANDWIDTH, SETTLING TIME AND TOTAL HARMONIC DISTORTION VS. GAIN

| GAIN | $R_{G}$      | C <sub>ADJ</sub> (pF) | SMALL<br>SIGNAL<br>BANDWIDTH | SETTLING<br>TIME<br>TO 0.1% | THD + NOISE<br>BELOW INPUT<br>LEVEL<br>@ 10kHz |

|------|--------------|-----------------------|------------------------------|-----------------------------|------------------------------------------------|

| 1    | OPEN         | 2–8                   | 16.1MHz                      | 200ns                       | 82dB                                           |

| 2    | <b>2k</b> Ω  | 2–8                   | 14.7MHz                      | 200ns                       | 82dB                                           |

| 10   | <b>226</b> Ω | 2–8                   | 4.5MHz                       | 370ns                       | 81dB                                           |

| 100  | <b>20</b> Ω  | 2–8                   | 660kHz                       | <b>2.5</b> μ <b>s</b>       | 71dB                                           |

Figure 26. A High Speed In-Amp Circuit for Data Acquisition

REV. F –11–

## **AD847**

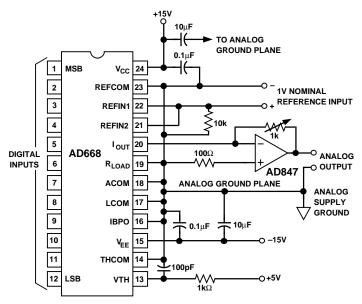

#### HIGH SPEED DAC BUFFER

The wide bandwidth and fast settling time of the AD847 makes it a very good output buffer for high speed current-output D/A converters like the AD668. As shown in Figure 27, the op amp establishes a summing node at ground for the DAC output. The output voltage is determined by the amplifier's feedback resistor

$(10.24~V~for~a~1~k\Omega~resistor)$ . Note that since the DAC generates a positive current to ground, the voltage at the amplifier output will be negative. A  $100~\Omega$  series resistor between the noninverting amplifier input and ground minimizes the offset effects of op amp input bias currents.

Figure 27. High Speed DAC Buffer

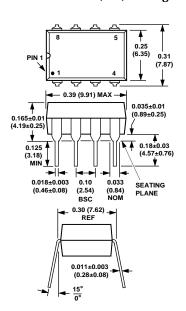

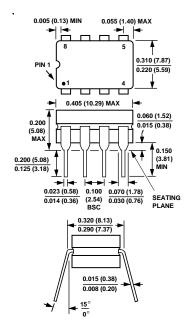

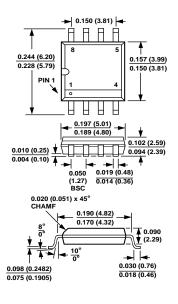

#### **OUTLINE DIMENSIONS**

Dimensions shown in inches and (mm).

#### Mini-DIP (N-8) Package

#### Cerdip (Q-8) Package

#### Small Outline (R-8) Package

All brand or product names mentioned are trademarks or registered trademarks of their respective holders.