# Analog Devices Welcomes Hittite Microwave Corporation

NO CONTENT ON THE ATTACHED DOCUMENT HAS CHANGED

# **HMC703\* Product Page Quick Links**

Last Content Update: 11/01/2016

### Comparable Parts

View a parametric search of comparable parts

#### Evaluation Kits <a> □</a>

• HMC703LP4E Evaluation Board

#### Documentation <a>□</a>

#### **Data Sheet**

• HMC703 Data Sheet

#### Tools and Simulations

ADIsimPLL<sup>TM</sup>

#### Reference Materials <a> □</a>

#### **Quality Documentation**

- Package/Assembly Qualification Test Report: LP4, LP4B, LP4C, LP4K (QTR: 2013-00487 REV: 04)

- Semiconductor Qualification Test Report: BiCMOS-A (QTR: 2013-00235)

# Design Resources -

- HMC703 Material Declaration

- · PCN-PDN Information

- · Quality And Reliability

- · Symbols and Footprints

#### Discussions <a>□</a>

View all HMC703 EngineerZone Discussions

# Sample and Buy -

Visit the product page to see pricing options

# Technical Support <a> □</a>

Submit a technical question or find your regional support number

<sup>\*</sup> This page was dynamically generated by Analog Devices, Inc. and inserted into this data sheet. Note: Dynamic changes to the content on this page does not constitute a change to the revision number of the product data sheet. This content may be frequently modified.

#### Typical Applications

The HMC703LP4E is ideal for:

- Microwave Point-to-Point Radios

- Base Stations for Mobile Radio (GSM, PCS, DCS, CDMA, WCDMA)

- Wireless LANs, WiMAX

- Communications Test Equipment

- CATV Equipment

- · Automotive Sensors

- AESA Phased Arrays

- FMCW Radar Systems

#### **Features**

Wide band: DC - 8 GHz RF Input

Best Phase Noise and Spurious in the Industry: -112 dBc/Hz @ 8 GHz Fractional, 50 kHz Offset

Figure of Merit

- -230 dBc/Hz Fractional Mode

- -233 dBc/Hz Integer Mode

High PFD rate: 100 MHz

< 50 fs RMS jitter

Frequency and Phase Modulation

Integrated Frequency Sweeper

Triggered Frequency Hopping

**External Triggering**

24 Lead 4x4 mm SMT Package: 16 mm<sup>2</sup>

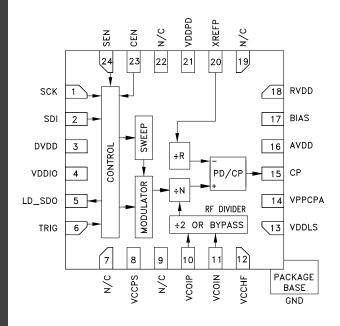

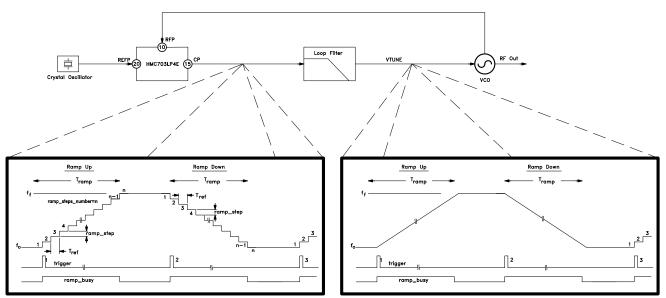

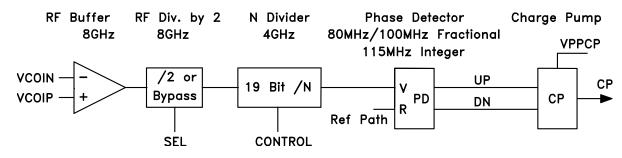

#### **Functional Diagram**

#### **General Description**

The HMC703LP4E fractional synthesizer is built upon the high performance PLL platform also contained in the HMC704LP4E and Hittite's latest generation of PLL+VCO products. This platform has the best phasenoise and spurious performance in the industry enabling higher order modulation schemes while minimizing blocker effects in high performance radios.

In addition, the HMC703LP4E offers frequency sweep and modulation features, external triggering, double-buffering, exact frequency control, phase modulation and more - while maintaining pin compatibility with the HMC700LP4E PLL.

Exact frequency mode with a 24-bit fractional modulator provides the ability to generate fractional frequencies with zero frequency error and very low channel spurious, an important feature for Digital Pre-Distortion systems.

The serial interface offers read back capability and is compatible with a wide variety of protocols.

#### **Table 1. Electrical Specifications**

Unless otherwise specified, data is collected at 3.3 V, and 5.0 V (on charge-pump), 100 MHz reference, 50 MHz  $f_{PD}$ . Min and Max are specified across temperature range from -40 °C to 85 °C ambient.

| Parameter                                    | Conditions                                                             | Min.    | Тур.           | Max.           | Units          |

|----------------------------------------------|------------------------------------------------------------------------|---------|----------------|----------------|----------------|

| RF INPUT CHARACTERISTICS                     | [6][7]                                                                 |         |                |                |                |

| RF Input Frequency Range                     | [1]                                                                    | DC 8000 |                | MHz            |                |

| Prescaler Input Freq Range                   | [1]                                                                    | DC      |                | 4000           | MHz            |

| Power Range                                  | [13]                                                                   | -15     | -10            | -3             | dBm            |

| Return Loss                                  | [15]                                                                   | -18     | -12            | -7             | dB             |

| REF INPUT CHARACTERISTICS                    |                                                                        |         |                |                |                |

| Frequency Range (3.3V)                       | [1][8]                                                                 | DC      | 50             | 350            | MHz            |

| Power from 50 Ω Source                       | [12] with 100 $\Omega$ termination off chip                            |         | 6              |                | dBm            |

| Return Loss                                  | [15]                                                                   | -16     |                | -8             | dB             |

| Ref Divider Range (14 bit)                   |                                                                        | 1       |                | 16,383         |                |

| PHASE DETECTOR RATE                          | [1]                                                                    |         |                |                |                |

| Integer Mode                                 |                                                                        | DC      | 50             | 115            | MHz            |

| Fractional Mode B                            |                                                                        | DC      | 50             | 100            | MHz            |

| Fractional Mode A                            |                                                                        | DC      | DC 50 80       |                | MHz            |

| CHARGE PUMP                                  |                                                                        |         |                |                |                |

| CP Output Current                            | 20 μA Steps, Charge Pump<br>Gain = CP Current/2π<br>Amps/rad           | 0.02    |                | 2.5            | mA             |

| CP HiK                                       | see "Charge Pump Gain" section                                         |         | 3.5            | 6              | mA             |

| POWER SUPPLIES                               |                                                                        |         |                |                |                |

| RVDD, AVDD, VCCPS, VCCHF, VCCPD, DVDD, VDDIO |                                                                        | 2.7     | 3.3            | 3.5            | V              |

| VDDLS, VPPCP Charge Pump                     | VDDLS, VPPCP must be equal                                             | 2.7     | 5.0            | 5.2            | V              |

| 3.3V - Current consumption                   | [9]<br>100 kHz PD<br>50 MHz PD<br>100 MHz PD                           |         | 34<br>54<br>74 | 45<br>70<br>95 | mA<br>mA<br>mA |

| 5V - Current consumption                     | All Modes<br>100 kHz PD<br>50 MHz PD w/ CP HiK<br>100 MHz PD w/ CP HiK |         | 3<br>7<br>13   | 5<br>12<br>16  | mA<br>mA<br>mA |

| Power Down Current                           | [10]                                                                   |         |                | 100            | uA             |

| BIAS Reference Voltage                       | Pin 12. Measured with 10 GΩ Meter                                      | 1.880   | 1.920          | 1.960          | V              |

#### Table 34. Electrical Specifications (Continued)

| Parameter                                                                                                    | Conditions                                                                                                                               | Min.                                          | Тур.                         | Max.                                 | Units    |

|--------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|------------------------------|--------------------------------------|----------|

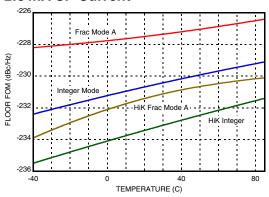

| PHASE NOISE [14]                                                                                             |                                                                                                                                          |                                               |                              |                                      |          |

| Flicker Figure of Merit (FOM)[2]                                                                             |                                                                                                                                          | -270                                          |                              | dBc/Hz                               |          |

| Floor Figure of Merit [11]                                                                                   | Integer HiK Mode -236 -233<br>Integer Normal Mode -232 -230<br>Fractional HiK Mode [3] -232 -230<br>Fractional Normal Mode [3] -228 -227 |                                               | -231<br>-228<br>-227<br>-225 | dBc/Hz<br>dBc/Hz<br>dBc/Hz<br>dBc/Hz |          |

| Flicker Noise at foffset                                                                                     | PN <sub>flick</sub> = Flicker FOM +20log(                                                                                                | f <sub>vco</sub> ) -10log(f <sub>offset</sub> | )                            |                                      | dBc/Hz   |

| Phase Noise Floor at f <sub>vco</sub> with f <sub>pd</sub>                                                   | PN <sub>floor</sub> = Floor FOM + 10log(f                                                                                                | pd) +20log(f <sub>vco</sub> /f <sub>p</sub>   | d)                           |                                      | dBc/Hz   |

| VCO referred Phase Noise Contribution of the PLL vs f <sub>Offset</sub> , f <sub>vco</sub> , f <sub>pd</sub> | PN = 10log(10(PNflick /10) + 1                                                                                                           | O(PNfloor /10)                                |                              |                                      | dBc/Hz   |

| Jitter                                                                                                       | SSB 100Hz to 100MHz with HMC508LP5E VCO                                                                                                  |                                               | 50                           |                                      | fs       |

| SPURIOUS                                                                                                     | [4][5]                                                                                                                                   |                                               |                              |                                      |          |

| Integer Boundary Spurs @~8GHz                                                                                | offsets less than loop bandwidth, f <sub>pd</sub> = 50MHz                                                                                |                                               | -52                          | dBc                                  |          |

| LOGIC INPUTS                                                                                                 |                                                                                                                                          |                                               |                              |                                      |          |

| Switching Theshold (Vsw)                                                                                     | VIH/VIL within 50 mV of Vsw                                                                                                              | 38                                            | 47                           | 54                                   | % VDDIO  |

| LOGIC OUTPUT                                                                                                 |                                                                                                                                          |                                               |                              |                                      |          |

| VOH Output High Voltage                                                                                      |                                                                                                                                          |                                               | VDDIO                        |                                      | V        |

| VOL Output Low Voltage                                                                                       |                                                                                                                                          |                                               | 0                            |                                      | V        |

| Output impedance : Pull Up                                                                                   | VDDIO=3.3 V                                                                                                                              | 115                                           | 150                          | 180                                  | Ohm      |

| Output impedance : Pull Dn                                                                                   | VDDIO=3.3 V                                                                                                                              | 130                                           | 135                          | 210                                  | Ohm      |

| DC load                                                                                                      |                                                                                                                                          |                                               |                              | 1.5                                  | mA       |

| Digital Output Driver Delay<br>SCK to Digital Output Delay                                                   | 1.7nsec with a 3 pF load                                                                                                                 | 0.5ns+0.2ns/pF<br>8.2ns+0.2ns/pF              |                              |                                      | ns<br>ns |

| RF Divider Range                                                                                             |                                                                                                                                          |                                               |                              |                                      |          |

| >4GHz Integer Mode                                                                                           | 16 bit , Even values only                                                                                                                | 32                                            |                              | 131,070                              |          |

| < 4GHz Integer Mode                                                                                          | 16 bit , All values                                                                                                                      | 16                                            |                              | 65,535                               |          |

| > 4GHz Fractional Mode                                                                                       | 16 bit                                                                                                                                   | 40.0                                          |                              | 131,065.0                            |          |

| < 4GHz Fractional Mode                                                                                       | 16 bit                                                                                                                                   | 20.0                                          |                              | 65,531.0                             |          |

- [1] Frequency is guaranteed across process, voltage and temperature from -40  $^{\circ}$ C to 85  $^{\circ}$ C.

- [2] With high charge-pump current, +12dBm 100MHz sine reference

- [3] Fractional FOM degrades about 3dB/octave for prescaler input frequencies below 2GHz

- [4] Using 50MHz reference with VCO tuned to within one loop bandwidth of an integer multiple of the PD frequency. Larger offsets produce better results. See the "Spurious Performance" section for more information.

- [5] Measured with the HMC703LP4E evaluation board. Board design and isolation will affect performance.

- [6] Internal divide-by-2 should be enabled for frequencies >4GHz

- [7] At low RF Frequency, Rise and fall times should be less than 1ns to maintain performance

- [8] Slew rate of greater or equal to 0.5 V/ns

- [9] Current consumption depends upon operating mode and frequency of the VCO. Typical values are for fractional mode.

- [10] Reference input disconnected

- $\hbox{[11] Min/Max versus temperature and supply, under typical reference \&\,RF\,frequencies\,and\,power\,levels}$

- [12] Slew > 0.5V/ns is recommended , see  $\underline{\text{Table 7}}$ ,  $\underline{\text{Figure 5}}$ ,  $\underline{\text{Figure 6}}$  for more information.

- [13] Operable with reduced spectral performance outside of this range.

- [14] This section specifies the Phase Noise contribution of the PLL, solution phase noise with a given VCO, loop filter and reference requires a closed loop calculation using Hittite PLL Design Tool.

- $\hbox{\small [15] As measured on HMC703LP4E Evaluation board, with 1000hm external termination.}$

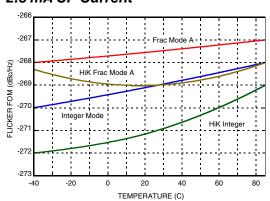

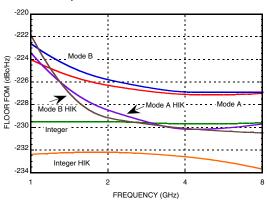

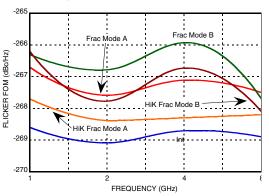

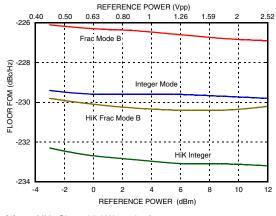

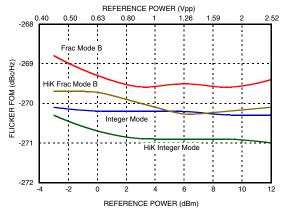

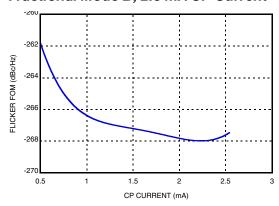

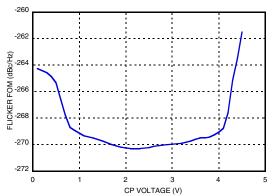

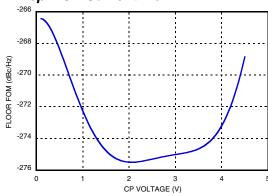

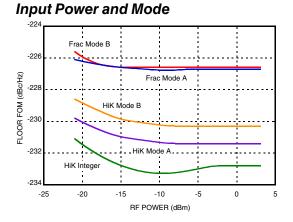

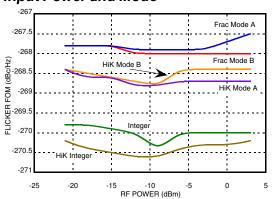

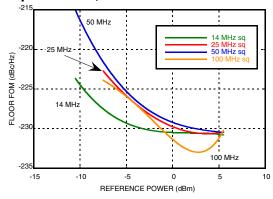

#### TYPICAL PERFORMANCE CHARACTERISTICS

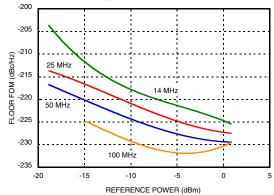

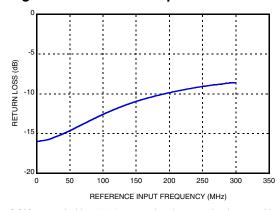

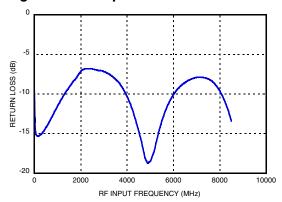

Unless otherwise specified, plots are measured with a 50 MHz PD rate, VCO near 8 GHz, RF power ≈ -10 dBm, and a Wenzel 100 MHz sinusoid reference. The operating modes in the following plots refer to Integer (int), Fractional Modes A and B, HiKcp (HiK).

Figure 1. Floor FOM vs. Mode and Temp, 2.5 mA CP Current

Figure 2. Flicker FOM vs. Mode and Temp, 2.5 mA CP Current

Figure 3. Floor FOM vs. Output Frequency and Mode, 2.5 mA CP Current

Figure 4. Flicker FOM vs. Output Frequency and Mode, 2.5 mA CP Current

Figure 5. Floor FOM vs. Reference Power and Mode, 2.5 mA CP Current [1]

Figure 6. Flicker FOM vs. Reference Power and Mode, 2.5 mA CP Current [1]

[1] 100 MHz Sinusoidal Wenzel reference.

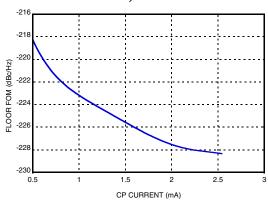

#### Figure 7. Flicker FOM vs. CP Current, Fractional Mode B, 2.5 mA CP Current

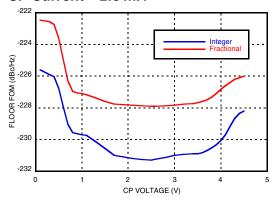

Figure 9. Flicker FOM vs. CP Voltage, CP Current = 2.5 mA [1]

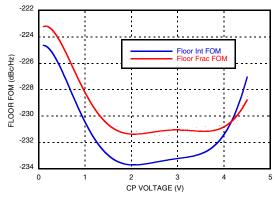

Figure 11. Flicker FOM vs. CP Voltage, HiKcp + CP Current = 6 mA [2]

#### **8 GHz FRACTIONAL SYNTHESIZER**

Figure 8. Floor FOM vs. CP Current, Fractional Mode B, 2.5 mA CP Current

Figure 10. Floor FOM vs. CP Voltage, CP Current = 2.5 mA [1]

Figure 12. Floor FOM vs. CP Voltage, HiKcp + CP Current = 6 mA [2]

[2] Active Loop Filter, with DC bias point on -ve leg of op-amp swept.

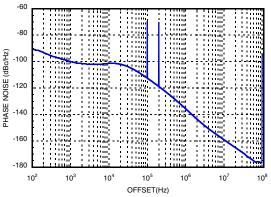

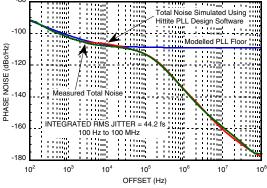

# Figure 13. Typical Phase Noise & Spur Performance at 8 GHz + 200 kHz<sup>[3]</sup>

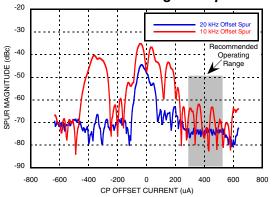

Figure 15. Integer Boundary Spur at 8 GHz + 20 kHz vs. Charge Pump Offset[5]

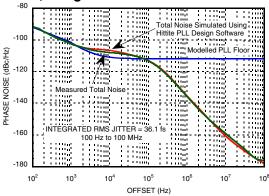

Figure 17. Modelled vs. Measured Phase Noise, Integer Mode HiK at 8 GHz [7]

#### **8 GHz FRACTIONAL SYNTHESIZER**

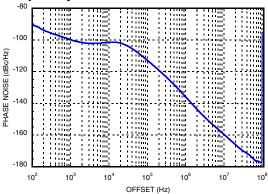

Figure 14. Fractional Performance, Exact Frequency Mode On at 8013.6 MHz [4]

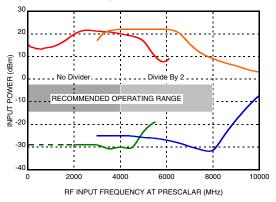

Figure 16. RF Input Limits [6]

Figure 18. Modelled vs. Measured Phase Noise, Fractional Mode B, HiK at ~ 8 GHz [8]

- [3] Output frequency = 8 GHz + 200 kHz using HMC508LP5E VCO, Reference Input = 100 MHz, PD frequency = 100 MHz, CP current = 2.5 mA, Fractional Mode B, 20 kHz bandwidth Loop Filter. Spur at 200kHz due to RF signal at 8GHz + 200kHz, spur at 100kHz due to prescaler input at 4GHz+100kHz. Reference feedthrough spur at 100 MHz offset.

- [4] Exact Frequency Mode channel spacing 100 kHz, Fractional N, Rfout = 8013.6 MHz using HMC508LP5E VCO, Reference Input = 100 MHz, PD frequency = 100 MHz, Prescaler divide-by-2 selected. 20 kHz Loop Filter bandwidth, reference feedthrough spur at 100 MHz offset.

- [5] Tuned to 8 GHz + 20 kHz, Prescaler at 4 GHz + 10 kHz, Loop bandwidth >> 20 kHz, Reference Frequency 50 MHz. Offset polarity should be positive for inverting configurations and negative otherwise.

- [6] Low frequency minimum power levels not characterized. Low frequency limitation is only a function of external AC coupling capacitance signal

- [7] HiK integer mode measured at 8 GHz, Prescalar at 4 GHz, 50 MHz reference frequency.

- [8] Active Fractional B Mode (Prescalar @ 4 GHz + 2.5 kHz), Reference Frequency 50 MHz.

# Figure 19. Floor FOM Near 8 GHz vs RF

Figure 20. Flicker FOM Near 8 GHz vs. RF Input Power and Mode

Figure 21. Reference Input Sensitivity, Square Wave, 50  $\Omega$  [9]

Figure 22. Reference Input Sensitivity Sinusoid Wave, 50  $\Omega$  [9]

Figure 23. Reference Input Return Loss [10]

Figure 24. RF Input Return Loss [11]

[9] Measured with a 100 Ω external resistor termination, resulting in 500hm effective input impedance.. See <u>"Reference Input Stage"</u> for more details. Full FOM performance up to maximum 3.3 Vpp input voltage.

[10] Measured with a 100  $\Omega$  external termination AC coupled on HMC703LP4E evaluation board, as in Figure 35.

[11] Measured with a 100 Ω external termination AC coupled on HMC703LP4E evaluation board, as in Figure 37.

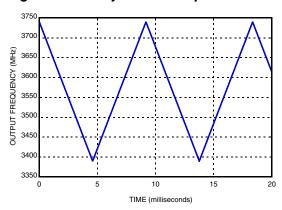

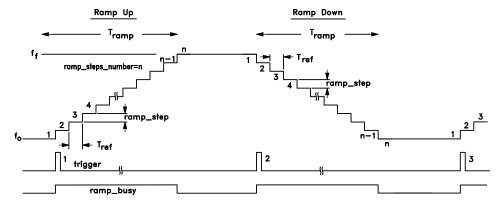

#### Figure 25. 2-Way Auto Sweep

#### **Table 2. Pin Descriptions**

| Pin Number | Function | Description                                                                                                                                                                                                                                     |

|------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | SCK      | CMOS Input: Serial port clock                                                                                                                                                                                                                   |

| 2          | SDI      | CMOS Input: Serial port data                                                                                                                                                                                                                    |

| 3          | DVDD     | Power Supply for digital - Nominal 3.3 V MAX 25 mA, f <sub>PD</sub> dependent                                                                                                                                                                   |

| 4          | VDDIO    | Power Supply for Digital IO - 3.3 V, 8 mA MAX (only when driving LD_SDO)                                                                                                                                                                        |

| 5          | LD_SDO   | CMOS Output: General Purpose Output - Lock Detect, Serial Data Out, others, Selectable                                                                                                                                                          |

| 6          | TRIG     | CMOS Input: External Trigger pin.                                                                                                                                                                                                               |

| 7          | N/C      | No Connect                                                                                                                                                                                                                                      |

| 8          | VDDPS    | Power Supply for RF Divider, Nominal 3.3 V 35 mA MAX                                                                                                                                                                                            |

| 9          | N/C      | No Connect                                                                                                                                                                                                                                      |

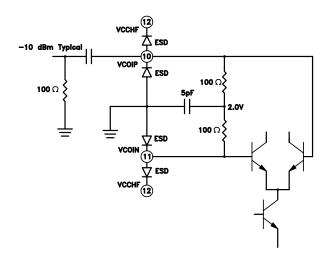

| 10         | VCOIP    | Differential RF Inputs. Normally AC Coupled, 2 V DC bias generated internally. For Single Ended                                                                                                                                                 |

| 11         | VCOIN    | operation, RFN must be AC coupled to the ground plane, typically 100 pF ceramic. DC Bias of 2.3 V is generated internally                                                                                                                       |

| 12         | VDDHF    | Power Supply for RF Buffer, Nominal 3.3 V, 6 mA MAX                                                                                                                                                                                             |

| 13         | VDDLS    | Power Supply for PFD to CP Level Shifters, Nominal 5 V, 5 mA MAX, f <sub>PD</sub> dependent.                                                                                                                                                    |

| 14         | VDDCPA   | Power Supply for charge pump, Nominal 5 V, 10 mA MAX                                                                                                                                                                                            |

| 15         | СР       | Charge pump output                                                                                                                                                                                                                              |

| 16         | AVDD     | Power supply for analog bias generation, Nominal 3.3 V, 2 mA MAX                                                                                                                                                                                |

| 17         | BIAS     | External bypass decoupling for precision bias circuits, 1.920 V +/-2 mV NOTE: BIAS ref voltage cannot drive an external load. Must be measured with 10 G $\Omega$ meter such as Agilent 34410A, normal 10 M $\Omega$ DVM will read erroneously. |

| 18         | RVDD     | Power Supply for Reference path, Nominal 3.3 V. 15 mA MAX reference dependent                                                                                                                                                                   |

| 19         | N/C      | No Connect                                                                                                                                                                                                                                      |

| 20         | XREFP    | Reference Input. DC bias is generated internally. Normally AC coupled externally.                                                                                                                                                               |

| 21         | VDDPD    | Power Supply for phase detector. Nominally 3.3 V. Decoupling for this supply is critical. 5 mA MAX, f <sub>PD</sub> dependent                                                                                                                   |

| 22         | N/C      | No Connect                                                                                                                                                                                                                                      |

| 23         | CEN      | CMOS Input: Hardware Chip Enable                                                                                                                                                                                                                |

| 24         | SEN      | CMOS Input: Serial port latch enable                                                                                                                                                                                                            |

**Table 3. Absolute Maximum Ratings**

| Parameter                                          | Rating               |  |  |

|----------------------------------------------------|----------------------|--|--|

| Max Vdc to paddle on supply pins 3,4,8,12,16,18,21 | -0.3 V to +3.6 V     |  |  |

| VDDLS, VPPCP                                       | -0.3 V to +5.5 V     |  |  |

| VCOIN, VCOIP Single Ended DC                       | VCCHF -0.2 V         |  |  |

| VCOIN, VCOIP Differential DC                       | 5.2 V                |  |  |

| VCOIN, VCOIP Single Ended AC 500hm                 | +7 dBm               |  |  |

| VCOIN, VCOIP Differential AC 500hm                 | +13 dBm              |  |  |

| Digital Load                                       | 1 kΩ min             |  |  |

| Digital Input 1.4 V to 1.7 V min rise time         | 20 nsec              |  |  |

| Digital Input Voltage Range                        | -0.25 to VDDIO+0,5 V |  |  |

| Thermal Resistance (Jxn to Gnd Paddle)             | 25 °C/W              |  |  |

| Operating Temperature Range                        | -40 °C to +85 °C     |  |  |

| Storage Temperature Range                          | -65 °C to + 125 °C   |  |  |

| Maximum Junction Temperature                       | +150 °C              |  |  |

| Reflow Soldering                                   |                      |  |  |

| Peak Temperature                                   | 260 °C               |  |  |

| Time at Peak Temperature                           | 40 sec               |  |  |

| ESD Sensitivity HBM                                | Class 1B             |  |  |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

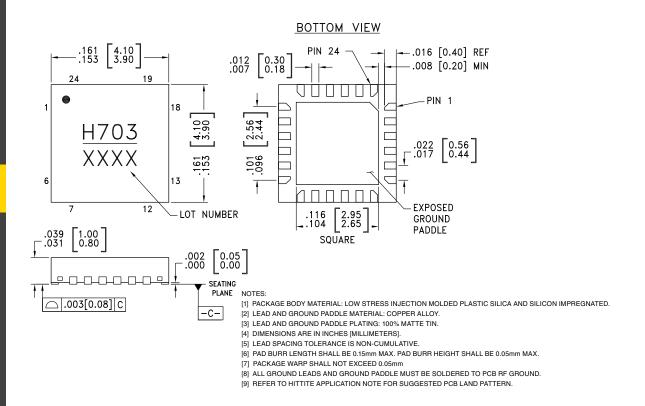

#### **Outline Drawing**

#### **Table 4. Package Information**

| Part Number | Package Body Material                              | Lead Finish   | MSL Rating          | Package Marking [1] |

|-------------|----------------------------------------------------|---------------|---------------------|---------------------|

| HMC703LP4E  | RoHS-compliant Low Stress Injection Molded Plastic | 100% matte Sn | MSL1 <sup>[2]</sup> | H703<br>XXXX        |

<sup>[1] 4-</sup>Digit lot number XXXX

<sup>[2]</sup> Max peak reflow temperature of 260°C

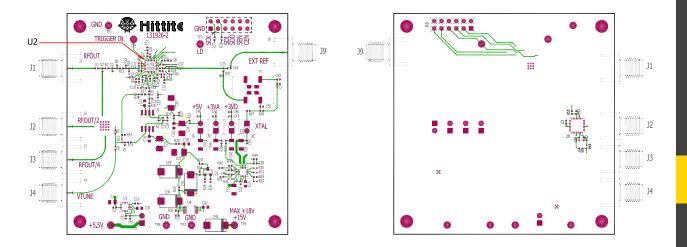

#### **Evaluation PCB**

The circuit board used in the application should use RF circuit design techniques. Signal lines should have 50 Ohms impedance while the package ground leads and exposed paddle should be connected directly to the ground plane similar to that shown. A sufficient number of via holes should be used to connect the top and bottom ground planes. The evaluation circuit board shown is available from Hittite upon request.

Table 5. Evaluation Order Information

| Item           | Contents                                                                                                                                                                                    | Part Number       |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| Evaluation Kit | HMC703LP4E Evaluation PCB USB Interface Board 6' USB A Male to USB B Female Cable CD ROM (Contains User Manual, Evaluation PCB Schematic, Evaluation Software, Hittite PLL Design Software) | EKIT01-HMC703LP4E |

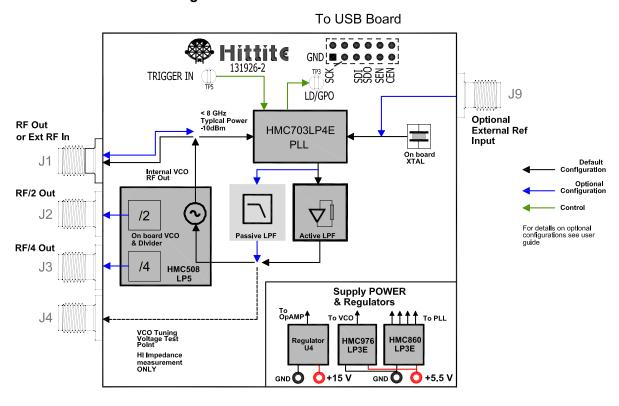

#### **Evaluation PCB Block Diagram**

#### **Evaluation PCB Schematic**

To view <u>Evaluation PCB Schematic</u> please visit <u>www.hittite.com</u> and choose HMC703LP4E from "Search by Part Number" pull down menu to view the product splash page.

#### **Theory Of Operation**

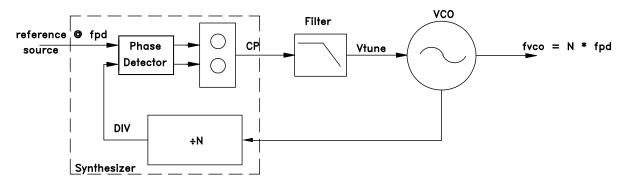

#### **PLL Basics**

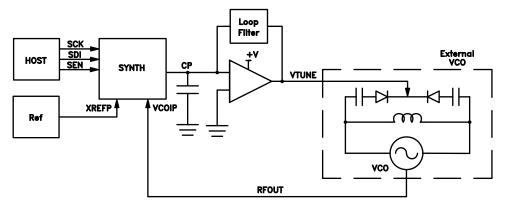

In its most trivial form, a synthesizer IC, such as the HMC703LP4E forms the heart of the control loop to multiply a low frequency reference source up to a higher frequency. The phase detector (PD) and charge-pump (CP) drive the tuning signal of a voltage-controlled oscillator in an attempt to bring the phases, at the phase-detector input, into alignment. If the loop can manage this, it means that the phase detector inputs (reference and DIV) must also be at the same frequency. Since the frequency of the DIV signal = f(x) = f(x), this means the control loop must have forced the frequency of the VCO output must be locked to N x fpd.

Figure 26. Typical PLL

In integer synthesizers, N can only take on discrete values (eg. 200, 201, etc.). In fractional synthesizers, such as the HMC703LP4E and others, N can also take on fractional levels, eg. N=20.4. In theory, the fractional divider normally permits higher phase-detector frequencies for a given output frequency, with associated improvements in signal quality (phase-noise). Unfortunately, fractional synthesizers suffer from imperfections which do not effect integer synthesizers. These problems can effect the phase noise, but more seriously they tend to manifest as spurious emissions - and these spurs are the most serious drawback of fractional synthesis.

Hittite's fractional synthesizer family (including the HMC703LP4E) offer drastic performance advantages over other fractional synthesizers in the industry.

The HMC703LP4E synthesizer consists of the following functional blocks:

- 1. Reference Path Input Buffer and 'R' Divider

- 2. VCO Path Input Buffer, RF Divide-by-2 and Multi-Modulus 'N' Divider

- **3.**  $\Delta \sqcap$  Fractional Modulator

- 4. Phase Detector

- 5. Charge Pump

- 6. Main Serial Port

- 7. Lock Detect and Register Control

- 8. Power On Reset Circuit

#### **High Performance Low Spurious Operation**

The HMC703LP4E has been designed for the best phase noise and low spurious content possible in an integrated synthesizer. Spurious signals in a synthesizer can occur in any mode of operation and can come from a number of sources.

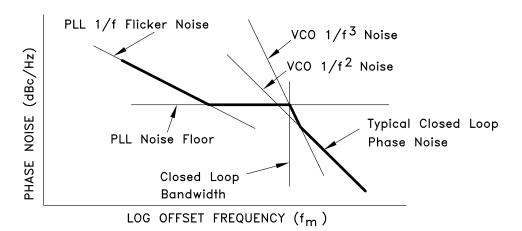

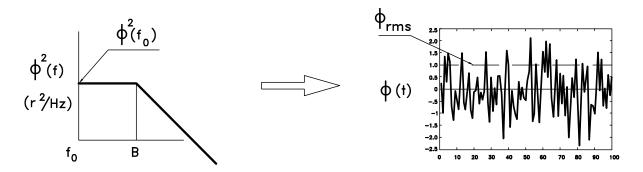

#### Figure of Merit, Noise Floor, and Flicker Noise Models

The phase noise of an ideal phase locked oscillator is dependent upon a number of factors:

- a. Frequency of the VCO, and the Phase detector

- b. VCO Sensitivity, kvco, VCO and Reference Oscillator phase noise profiles

- c. Charge Pump current, Loop Filter and Loop Bandwidth

- d. Mode of Operation: Integer, Fractional modulator style

The contributions of the PLL to the output phase noise can be characterized in terms of a Figure of Merit (FOM) for both the PLL noise floor and the PLL flicker (1/f) noise regions, as follows:

where:

$\begin{array}{lll} \Phi_{p^2} & \text{Phase Noise Contribution of the PLL (rads}^2/\text{Hz}) \\ f_o & \text{Frequency of the VCO (Hz)} \\ f_{pd} & \text{Frequency of the Phase Detector (Hz)} \\ f_m & \text{Frequency offset from the carrier (Hz)} \\ F_{po} & \text{Figure of Merit (FOM) for the phase noise floor} \\ F_{n1} & \text{Figure of Merit (FOM) for the flicker noise region} \end{array}$

Figure 27. Figure of Merit Noise Models for the PLL

If the free running phase noise of the VCO is known, it may also be represented by a figure of merit for both  $1/f^2$ ,  $F_{v2}$ , and the  $1/f^3$ ,  $F_{v3}$ , regions.

#### VCO Phase Noise Contribution

$$\Box_n^2 \bullet f_m \rightarrow \frac{F_{n_2} f_0^2}{f_m^2} + \frac{F_{n_3} f_0^2}{f_m^3}$$

(EQ 2)

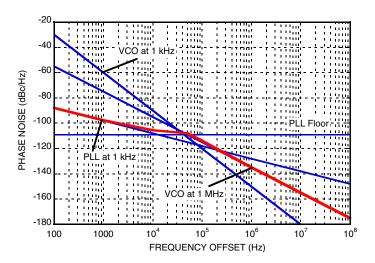

The Figures of Merit are essentially normalized noise parameters for both the PLL and VCO that can allow quick estimates of the performance levels of the PLL at the required VCO, offset and phase detector frequency. Normally, the PLL IC noise dominates inside the closed loop bandwidth of the synthesizer, and the VCO dominates outside the loop bandwidth at offsets far from the carrier. Hence a quick estimate of the closed loop performance of the PLL can be made by setting the loop bandwidth equal to the frequency where the PLL and free running phase noise are equal.

The Figure of Merit is also useful in estimating the noise parameters to be entered into a closed loop design tool such as Hittite PLL Design, which can give a much more accurate estimate of the closed loop phase noise and PLL loop filter component values.

Given an optimum loop design, the approximate closed loop performance is simply given by the minimum of the PLL and VCO noise contributions.

An example of the use of the FOM values to make a quick estimate of PLL performance: Estimate the phase noise of an 8 GHz closed loop PLL with a 100 MHz reference operating in Fractional Mode B with the VCO operating at 8 GHz and the VCO divide by 2 port driving the PLL at 4 GHz. Assume an HMC509 VCO has free running phase noise in the 1/f<sup>2</sup> region at 1 MHz offset of -135 dBc/Hz and phase noise in the 1/f<sup>3</sup> region at 1 kHz offset of -60 dBc/Hz.

| F <sub>v1_dB</sub> = | -135<br>+20*log10(1e6)<br>-20*log10(8e9)<br>= -213.1 dBc/Hz at 1Hz | Free Running VCO PN at 1MHz offset<br>PNoise normalized to 1Hz offset<br>Pnoise normalized to 1Hz carrier<br>VCO FOM         |

|----------------------|--------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| F <sub>v3_dB</sub> = | -60<br>+30*log10(1e3)<br>-20*log10(8e9)<br>= -168 dBc/Hz at 1Hz    | Free Running VCO PN at 1kHz offset<br>PNoise normalized to 1Hz offset<br>Pnoise normalized to 1Hz carrier<br>VCO Flicker FOM |

We can see from Figure 3 and Figure 4 respectively that the PLL FOM floor and FOM flicker parameters in fractional Mode A:

$Fpo_dB = -227 dBc/Hz$  at 1Hz $Fp1_dB = -266 dBc/Hz$  at 1Hz

Each of the Figure of Merit equations result in straight lines on a log-frequency plot. We can see in the example below the resulting

PLL floor at 8 GHz =  $F_{po\_dB}$  +20log10(fvco) -10log10(fpd) = -227+198 -80 = -109 dBc/Hz PLL Flicker at 1 kHz =  $F_{po\_dB}$ +20log10(fvco)-10log10(fm) = -266 +198-30 = -98 dBc/Hz VCO at 1 MHz =  $F_{vo_dB}$ +20log10(fvco)-20log10(fm)= -213 +198-120 = -135 dBc/Hz VCO flicker at 1 kHz =  $F_{vo_dB}$ +20log10(fvco)-30log10(fm)= -168 +198-90 = -60 dBc/Hz

These four values help to visualize the main contributors to phase noise in the closed loop PLL. Each falls on a linear line on the log-frequency phase noise plot shown in <u>Figure 27</u>.

Figure 28. Figure of Merit Example

It should be noted that actual phase noise near the corner frequency of the loop bandwidth is affected by loop parameters and one should use a more complete design tool such as Hittite PLL Design for better estimates of the phase noise performance. Noise models for each of the components in Hittite PLL Design can be derived from the FOM equations or can be provided by Hittite applications engineering.

#### **Spurious Performance**

#### Integer Operation

The VCO always operates at an integer multiple of the PD frequency in an integer synthesizer. In general, spurious signals originating from an integer synthesizer can only occur at multiples of the PD frequency. These unwanted outputs are often simply referred to as reference sidebands.

Spurs unrelated to the reference frequency must originate from outside sources. External spurious sources can modulate the VCO indirectly through power supplies, ground, or output ports, or bypass the loop filter due to poor isolation of the filter. It can also simply add to the output of the synthesizer.

The HMC703LP4E has been designed and tested for ultra-low spurious performance. Reference spurious levels are typically below -100 dBc with a well designed board layout. A regulator with low noise and high power supply rejection, such as the HMC860LP3E, is recommended to minimize external spurious sources.

Reference spurious levels of below -100 dBc require superb board isolation of power supplies, isolation of the VCO from the digital switching of the synthesizer and isolation of the VCO load from the synthesizer. Typical board layout, regulator design, demo boards and application information are available for very low spurious operation. Operation with lower levels of isolation in the application circuit board, from those recommended by Hittite, can result in higher spurious levels.

Of course, if the application environment contains other interfering frequencies unrelated to the PD frequency, and if the application isolation from the board layout and regulation are insufficient, then the unwanted interfering frequencies will mix with the desired synthesizer output and cause additional spurs. The level of these spurs is dependant upon isolation and supply regulation or rejection (PSRR).

#### Fractional Operation

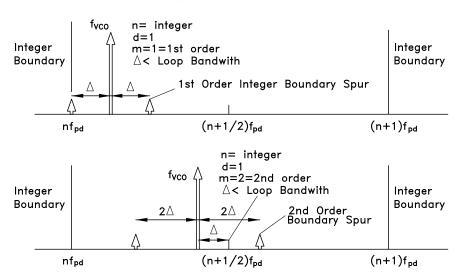

Unlike an integer synthesizer, spurious signals in a fractional synthesizer can occur due to the fact that the VCO operates at frequencies unrelated to the PD frequency. Hence intermodulation of the VCO and the PD harmonics can cause spurious sidebands. Spurious emissions are largest when the VCO operates very close to an integer multiple of the PD. When the VCO operates exactly at a harmonic of the PD then, no in-close mixing products are present.

Interference is always present at multiples of the PD frequency,  $f_{pd}$ , and the VCO frequency,  $f_{vco}$ . If the fractional mode of operation is used, the difference,  $\Delta$ , between the VCO frequency and the nearest harmonic of the reference, will create what are referred to as integer boundary spurs. Depending upon the mode of operation of the synthesizer, higher order, lower power spurs may also occur at multiples of integer fractions (sub-harmonics) of the PD frequency. That is, fractional VCO frequencies which are near  $nf_{pd} + f_{pd}d/m$ , where n, d and m are all integers and  $d \le m$  (mathematicians refer to d/m as a rational number). We will refer to  $f_{pd}d/m$  as an integer fraction. The denominator, m, is the order of the spurious product. Higher values of m produce smaller amplitude spurious at offsets of  $m\Delta$  and usually when m>4 spurs are very small or unmeasurable.

The worst case, in fractional mode, is when d=1, and the VCO frequency is offset from nf<sub>pd</sub> by less than the loop bandwidth. This is the "in-band fractional boundary" case.

Figure 29. Fractional Spurious Example

Characterization of the levels and orders of these products is not unlike a mixer spur chart. Exact levels of the products are dependent upon isolation of the various synthesizer parts. Hittite can offer guidance about expected levels of spurious with our PLL and VCO application boards. Regulators with high power supply rejection ratios (PSRR) are recommended, especially in noisy applications.

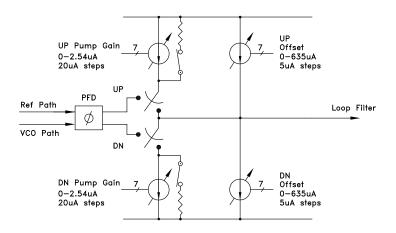

When operating in fractional mode, charge pump and phase detector linearity is of paramount importance. Any non-linearity degrades phase noise and spurious performance. Phase detector linearity degrades when the phase error is very small and is operating back and forth between reference lead and VCO lead. To mitigate these non-linearities in fractional mode it is critical to operate the phase detector with some finite phase offset such that either the reference or VCO always leads. To provide a finite phase error, extra current sources can be enabled which provide a constant DC current path to VDD (VCO leads always) or ground (reference leads always). These current sources are called charge pump offset and they are controlled via  $\frac{\text{Reg 09h}}{\text{Pps}}$ . The time offset at the phase detector should be ~2.5 ns + 4 T<sub>ps</sub>, where T<sub>ps</sub> is the RF period at the fractional prescaler input in nanoseconds (ie. after the optional fixed divide by 2). The specific level of charge pump offset current is determined by this time offset, the comparison frequency and the charge pump current and can be calculated from:

Required CP Offset =  $(2.5 \cdot 10^{-9} + 4T_{PS}) \cdot (F_{comparison}) \cdot I_{CP}$  where: **(EQ 4)**

T<sub>PS</sub>: is the RF period at the fractional prescaler input

ICP: is the full scale current setting of the switching charge pump

Note that this calculation can be performed for the center frequency of the VCO, and does not need refinement for small differences (<25%) in center frequencies. Also, operation with unreasonably large charge pump offset may cause Lock Detect to incorrectly indicate an unlocked condition. To correct, reduce the offset to recommended levels.

Another factor in Fractional spectral performance is the choice of the Delta-Sigma Modulator mode. Mode B is normally recommended, as it allows higher PD frequencies and makes it easier to filter the fractional quantization noise. For low prescaler frequencies (<1.5GHz), however, mode A can offer better in-band spectral performance. See Reg 06h[0] for DSM mode selection. Finally, all fractional synthesizers create fractional spurs at some level. Hittite offers the lowest level fractional spurious in the industry in an integrated solution.

#### **Operational Modes**

The HMC703LP4E can operate in a eight of different modes (Reg 06h[7:5]), and supports "Triggering" from 3 different sources. The modes of operation include:

"Integer Mode"

"Fractional Mode"

"Exact Frequency Mode"

Frequency Modulation "FM Mode"

Phase Modulation "PM Mode"

"Frequency Sweep Mode" (3 types)

All modes require Fractional mode to be enabled except for Integer mode. Fractional mode allows fine frequency steps. Exact Frequency mode allows precise fractional frequency steps with zero frequency error. FM and PM modes can be used for simple communications links, with data rate limitations set by the loop filter bandwidth. The PM mode also allows for precise incremental phase adjustments, which can be important in phased arrays and other systems. Frequency sweep supports built-in one-way, two-way, or user defined frequency sweeps, useful in FMCW radar applications.

Depending on the mode, the auxiliary registers Reg 0Ah, Reg 0Ch and Reg 0Dh are used for different functions, as shown in Table 6.

#### **Table 6. Operational Modes**

|                        |                         | PLL Operating Mode (SD_MODE = Reg 06h[7:5])            |              |                                                        |                                           |                                     |                                      |  |

|------------------------|-------------------------|--------------------------------------------------------|--------------|--------------------------------------------------------|-------------------------------------------|-------------------------------------|--------------------------------------|--|

| Register<br>Number     |                         | 0                                                      | 1            | 2                                                      | 3                                         | 4                                   | 5 to 7                               |  |

|                        | Register Name           | Fractional<br>Mode                                     | Integer Mode | Exact<br>Frequency<br>Mode                             | FM (Frequency<br>Modulation)<br>Mode      | PM (Phase<br>Modulation)<br>Mode    | Ramp Mode                            |  |

| Function of<br>Reg 03h | N Integer Part          | Nint                                                   | N            | Nint                                                   | Freq 1: Nint                              | Nint                                | Start Nint                           |  |

| Function of Reg 04h    | N Fractional<br>Part    | Nfrac                                                  |              | Nfrac                                                  | Freq 1: Nfrac                             | Nfrac                               | Start Nfrac                          |  |

| Function of Reg 0Ah    | Aux Register            |                                                        |              |                                                        |                                           | Phase Step                          | Frequency step<br>/ reference clock  |  |

| Function of<br>Reg 0Ch | Alternate<br>Integer    |                                                        |              |                                                        | Freq 2: Nint                              |                                     | STOP Nint                            |  |

| Function of<br>Reg 0Dh | Alternate<br>Fractional |                                                        |              | Channels / PD frequency                                | Freq 2: Nfrac                             |                                     | STOP Nfrac                           |  |

| Additional Func        | tionality               |                                                        |              |                                                        |                                           |                                     |                                      |  |

| Double                 | e Buffer                | YES                                                    | NO           | YES                                                    | YES                                       | YES                                 | YES                                  |  |

| On Ti                  | rigger                  | Updates<br>frequency,<br>optionally<br>initiates phase |              | Updates<br>frequency,<br>optionally<br>initiates phase | Toggles<br>frequency (level<br>sensitive) | Increments /<br>decrements<br>phase | Proceeds to<br>next stage of<br>ramp |  |

Those registers which are unused in a particular mode can take on any value, and are ignored.

#### **Triggering**

Depending on the operating mode, a trigger event is used to change frequency, FM modulate the frequency, modulate the phase, or advance the frequency ramp profile to its next state. In general the HMC703LP4E can be triggered via one of three methods. Not all modes support all trigger methods.

- 1. An external hardware trigger pin-6 (TRIG)

- 2. SPI write to TRIG BIT in Reg 0Eh[0]

- 3. SPI write to fractional register Reg 04h (frequency hopping triggers only).

Depending on the mode, the part is sensitive to either the rising edge, or the level of the trigger. The SPI's TRIG bit emulates the external TRIG pin, and so it must typically be written to 1 for a trigger, and then back to 0 in preparation for another trigger cycle. To use the external TRIG pin, it must be enabled via EXTTRIG\_EN (Reg 06h[9]).

#### Fractional Mode or Exact Frequency Mode Frequency Updates

In non-modulated fractional modes (Reg 06h[7:5] = 0 or 2), if the external trigger is enabled, writes to  $N_{INT}$  and  $N_{frac}$  (Reg 03h and Reg 04h) are internally buffered and wait for an explicit trigger via either the TRIG pin or the SPI's TRIG bit before taking effect. If EXTTRIG\_EN = 0, the write to  $N_{INT}$  is double-buffered, and waits for a fractional write to Reg 04h so that both  $N_{INT}$  and  $N_{frac}$  are internally recognized together. See the "Fractional Mode" section for more information on calculating the fractional multiplier for your application.

#### **Initial Phase Control**

On the HMC703LP4E, the user has control of the initial phase of the VCO via the 24-bit SEED  $\underline{\text{Reg 05h}}$ . This seed phase is loaded on the 1st clock cycle following a trigger event, provided that autoseed ( $\underline{\text{Reg 06h}}$  [8] = 1) is enabled. The value in  $\underline{\text{Reg 05h}}$  represents the phase of the VCO. For example, if two synthesizers are triggered in parallel, but one has a SEED of 0.2 (0.2x2<sup>24</sup>) and the other has a SEED of 0.7 (0.7x2<sup>24</sup>), the steady state outputs of the two VCOs

(not accounting for any mismatch) will be  $180^{\circ}$  out of phase = ((0.7-0.2) x  $360^{\circ}$ ). The user can take advantage of this for phase control of the outputs of multiple synthesizers.

If phase control is not needed, the best spurious operation is achieved with the SEED set to a busy binary number, for example 50F1CDh, or B29D08h.

Note that in Exact Frequency mode with an exact step of  $f_{step}$ , if autoseed is off, there can be a delay of up to  $1/f_{step}$  after a trigger before a new fractional frequency is recognized.

#### Frequency Tuning

#### Integer Mode

In integer mode the VCO step size is fixed to that of the PD frequency,  $f_{pd}$ . Integer mode typically has lower phase noise than fractional mode for a given PD operating frequency. The advantage is usually of the order of 2 to 3 dB. Integer mode, however, often requires a lower PD frequency to meet channel step size requirements. The fractional mode advantage is that higher PD frequencies can be used, hence lower phase noise can often be realized. "Charge Pump Offset" should be disabled in integer mode. In integer mode the  $\Delta\Sigma$  modulator is shut off and the N divider (Reg 03h) may be programmed to any integer value in the range 16 to  $2^{16}$ -1. To use the HMC703LP4E in integer mode program Reg 06h[7:5] = 1, then program the integer portion of the frequency (as per (EQ 5)), ignoring the fractional part.

There is no double buffering in integer mode, i.e. write data then trigger the frequency change later. A write to the  $N_{INT}$  register ( $\frac{\text{Reg 03h}}{\text{Reg 03h}}$ ) immediately starts the RF frequency hop. There is no external trigger available in this mode. If double buffering is required, use fractional mode ( $\frac{\text{Reg 06h}}{\text{Reg 06h}}$ ) = 0, with  $N_{frac}$  ( $\frac{\text{Reg 04h}}{\text{Reg 04h}}$ ) = 0, and SEED ( $\frac{\text{Reg 05h}}{\text{Reg 05h}}$ ) = 0.

#### Fractional Mode

The HMC703LP4E is placed into fractional mode by setting SD\_MODE (Reg 06h[7:5]) = 0

The frequency of a locked VCO controlled by the HMC703LP4E,  $f_{vco}$ , is given by

$$f_{ps} = \frac{f_{xtal}}{R} (N_{int} + N_{frac}) = f_{int} + f_{frac}$$

(EQ 5)

$$f_{vco} = k f_{ps}$$

(EQ 6)

Where:

$f_{ps}$  is the frequency at the prescalar input after any potential RF divide by 2

$f_{vco}$  is the frequency at the HMC703LP4E's RF port

k is 1 if the RF Divide by 2 is bypassed, 2 if on (Reg 08h[17])

$N_{int}$  is the integer division ratio, Reg 03h, an integer between 20 and  $2^{16}$ - 1

$N_{frac}$  is the fractional part, from 0.0 to 0.99999..., $N_{frac} = \frac{\text{Reg 04h}}{2^{24}}$

R is the reference path division ratio, Reg 02h

$f_{xtal}$  is the frequency of the reference oscillator input

$f_{pd}$  is the PD operating frequency,  $f_{xtal}/R$

As an example, suppose we want to tune a VCO to 7910 MHz. Since the input frequency is > 4 GHz, the RF divide-by-2 must be engaged, so k=2:

$f_{vco}$ 7,910 MHz k 3,955 MHz  $f_{xtal}$ = 50 MHz R = 1 = 50 MHz $f_{pd}$  $N_{int}$ = 79= 0.1 $N_{frac}$ Reg 04h  $= round(0.1 \times 2^{24}) = round(1677721.6) = 1677722$  $f_{ps} = \frac{50e6}{1} (79 + \frac{1677722}{2^{24}}) = 3955 MHz + 1.2 Hz error$ (EQ 7)

$$f_{vco} = 2 (3955 + 1.2 \text{ Hz}) = 7910 \text{ MHz} + 2.4 \text{ Hz error}$$

(EQ 8)

In this example the output frequency of 7910 MHz is achieved by programming the 16-bit binary value of 79d = 4Fh = 0000 0000 0100 1111 into *intg\_reg* in Reg 03h, and the 24-bit binary value of 1677722d = 19999Ah = 0001 1001 1001 1001 1001 1010 into *frac\_reg* in Reg 04h. The 2.4 Hz quantization error can be eliminated using the exact frequency mode if required.

#### **Exact Frequency Mode**

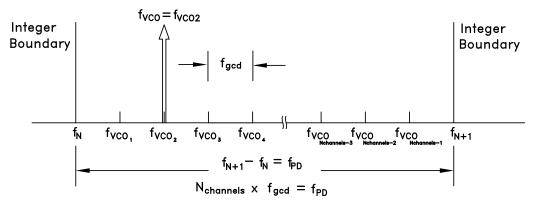

The absolute frequency precision of a fractional PLL is normally limited by the number of bits in the fractional modulator. For example a 24 bit fractional modulator has frequency resolution set by the phase detector (PD) comparison rate divided by 2<sup>24</sup>. In the case of a 50 MHz PD rate, this would be approximately 2.98 Hz, or 0.0596 ppm.

In some applications it is necessary to have exact frequency steps, and even an error of 3 Hz cannot be tolerated. In some fractional synthesizers it is necessary to shorten the length of the accumulator (the denominator or the modulus) to accommodate the exact period of the step size. The shortened accumulator often leads to very high spurious levels at multiples of the channel spacing,  $f_{\text{step}} = f_{\text{PD}}/\text{Modulus}$ . For example 200 kHz channel steps with a 10 MHz PD rate requires a modulus of just 50. The Hittite method achieves the exact frequency step size while using the full 24 bit modulus, thus achieving exact frequency steps with very low spurious and a high comparison rate, which maintains excellent phase noise.

Fractional PLLs are able to generate exact frequencies (with zero frequency error) if N can be exactly represented in binary (eg. N = 50.0,50.5,50.25,50.75 etc.). Unfortunately, some common frequencies cannot be exactly represented. For example,  $N_{frac} = 0.1 = 1/10$  must be approximated as round((0.1 x  $2^{24}$ )/  $2^{24}$ )  $\approx 0.100000024$ . At  $f_{PD} = 50$  MHz this translates to 1.2 Hz error. HMC703LP4E exact frequency mode addresses this issue, and can eliminate quantization error by programming the  $N_{channels}$  (Reg 0Dh) to 10 (in this example). More generally, this feature can be used whenever the prescaler frequency,  $f_{ps}$ , can be exactly represented on a step plan where there are an integer number ( $N_{channels}$ ) of frequency steps across integer-N boundaries. Assuming the RF divide by 2 is disabled so that  $f_{ps} = f_{vco}$ , this holds when the VCO frequency,  $f_{vco}$  satisfies (EQ 9), shown graphically in Figure 30.

$$f_{VCO} \mod_{f}^{f} = 0$$

, where  $f_{gcd} = \gcd(f_{VCO}, f_{PD})$

$$N_{channels} = f_{PD} / f_{gcd}, \text{ and } N_{channels} < 2^{24}$$

(EQ 9)

Where:

$f_{PD}$  = frequency of the Phase Detector  $f_{VCO}$  is the desired output frequency  $f_N$ ,  $f_{N}$ +1 are integer multiples of the Phase Detector  $f_{\rm gcd}$  stands for Greatest Common Divisor eg.  $f_{\rm gcd}$  (4000.200MHz, 50MHz) = 200kHz therefore  $N_{\rm channels}$  = 50~MHz/200~kHz = 250~c

$f_{VCOn}$  are other VCO frequencies we can exactly tune to, given this  $f_{qcd}$  spacing

Figure 30. Exact Frequency Tuning

In the previous paragraph, it was assumed that a single frequency was to be achieved with zero error. Exact frequency mode also applies to cases where many exact frequencies are required, all of which fit on a particular channel spacing.

Example: To achieve exactly 50 kHz channel steps with a 61.44 MHz reference, calculate  $f_{\rm gcd}$  and  $N_{\rm channels}$ :

```

\begin{split} f_{PD} &= 61.44 \text{ MHz} \\ f_{step} &= 50 \text{ kHz} \\ f_{gcd} &= 61.44 \text{ MHz}, 50 \text{ kHz}) \\ &\qquad \qquad \text{Using the Euclidean algorithm to find the greatest common denominator:} \\ &\qquad \qquad 61.440 \text{ MHz} = 50 \text{ kHz x } 1228 + 50 \text{ kHz} \\ &\qquad \qquad 50 \text{ kHz} = 40 \text{ kHz x } 1 + 10 \text{ kHz} \\ &\qquad \qquad 40 \text{ kHz} = 10 \text{ kHz x } 4 + 0 \text{ (0 remainder, algorithm complete)} \\ f_{gcd} &= 61.44 \text{ MHz}, 50 \text{ kHz}) = 10 \text{ kHz} \\ N_{channels} &= 61.44 \text{ MHz} / 10 \text{ kHz} = 6144 \end{split}

```

For improved spectral performance (to keep spurs low and further out of band), it is best to keep  $f_{gcd}$  as high as possible ( $N_{channels}$  as low possible) for a given application.

#### **Using Hittite Exact Frequency Mode**

To use Exact Frequency Mode, we recommend the following procedure:

- 1. Calculate the required  $f_{gcd}$  as either  $gcd(f_{VCO}, f_{PD})$  or  $gcd(f_{PD}, f_{step})$  depending on your application

- 2. Calculate the number of channels per integer boundary,  $N_{channels} = f_{PD} / f_{gcd}$  and program into Reg 0Dh

- 3. Set the modulator mode to Exact Frequency (SD\_MODE in Reg 06h[7:5] = 2)

Then, for each frequency of interest,  $f_{VCO}$ :

- 4 Calculate the approximate value of N that is required:  $N = f_{VCO}/f_{PD} = N_{INT} + N_{frac}$

- 5. Program *N<sub>INT</sub>* into integer register Reg 03h

Note: There is no need to re-program  $N_{INT}$  if it has not changed from the previous set-point.

6. Program the fractional register,  $\frac{\text{Reg 04h}}{\text{Reg 04h}} = \text{Ceiling}(N_{frac}^*2^{24})$  where the ceiling function means "round up to the nearest integer."

Example: To configure HMC703LP4E for exact frequency mode with channel spacing of 50 kHz, VCO frequency = 2000.200 MHz and  $f_{PD}$  = 61.44 MHz:

- 1.  $f_{qcd}(61.44 \text{ MHz}, 50 \text{ kHz}) = 10 \text{ kHz (as above)}$

- 2. Čalculate  $N_{channels} = f_{PD} / f_{gcd} = 6144$ . Program into Reg 0Dh (6144 dec = 1800 hex)

- 3. Set the modulator mode to Exact Frequency (SD\_MODE in Reg 06h[7:5] = 2)

- 4. Calculate N = 2000.2 MHz / 61.44 MHz = 32.55533854 = 32 + 0.55533854

- 5. Program integer divisor  $N_{INT}$  (Reg 03h) = 32d = 20h

- 6. Program fractional divisor  $\frac{\text{Reg 04h}}{\text{Reg 04h}} = \text{CEILING}(0.55533854 \times 2^{24}) = 9,317,035 = 8E2AABh$

In the above example, without exact frequency mode, there would have been a -1.2 Hz error due to quantization.

#### FM Mode

The HMC703LP4E PM mode supports simple FSK modulation via a level sensitive trigger. FM mode can be used for simple communications links, with data rate limitations set by the loop filter bandwidth.

The HMC703LP4E is configured to operate in FM mode by writing Reg 06h[7:5] = 3.

The FM mode allows the user to toggle between two frequencies  $F_0 = N_1^* f_{PD}$  and  $F_1 = N_2^* f_{PD}$  based on the level of the TRIG.

The following procedure is recommended to configure HMC703LP4E to FM mode:

- 1. Lock in fractional mode (Reg 06h[7:5]= 0) to  $F_0 = f_{PD} \times (Reg 03h.Reg 04h)$ .

- 2. Program (Reg 0Ch.Reg 0Dh) for F<sub>1</sub>.

- 3. Change mode to FM ( $\frac{\text{Reg 06h}}{\text{[7:5]}} = 3$ ).

- 4. Select the trigger source Reg 06h[9] = 1, TRIG (pin-6), or Reg 06h[9] = 0 trigger from SPI bit Reg 0Eh[0]

- 5. Switch between  $F_0$  and  $F_1$  on a trigger state  $0/1 = F_0/F_1$ .

It is possible to change the next frequency state between trigger events, without affecting the output - ie. write the  $F_0$  value while on  $F_1$ , or  $F_1$  while on  $F_0$ .

#### PM Mode

The HMC703LP4E PM mode supports simple bi-phase modulation via a level sensitive trigger. PM mode also supports programmable phase steps via an edge sensitive trigger. PM modes can be used for simple communications links, with data rate limitations set by the loop filter bandwidth.

The HMC703LP4E is configured to operate in all PM mode by writing  $\frac{\text{Reg 06h}}{\text{[7:5]}} = 4$ . In general the modulation phase step,  $\Delta\theta$ , in either PM mode is given by

$$\Box\Box = \frac{x \Box 360}{2^{24}} \quad \text{(deg)}$$

where x = Reg OAh.

#### **Bi-Phase Modulation**

Phase step is programmed in  $\frac{\text{Reg 0Ah}}{\text{Amount}}$  as a fraction of  $2\pi$ , where  $2^{24} = 2\pi$ . For example, for bi-phase modulation a phase step of  $180^{\circ}$ , program  $\frac{\text{Reg 0Ah}}{\text{Amount}}$  round(  $(180/360) \times 2^{24} = 8388608d = 800000h$ ).

Phase modulation data is input via a "trigger" source, where the trigger is level dependent (Reg 06h[8] = 0), high trigger advances the phase and low trigger returns the phase.

#### **Phase Step Control**

Phase may also be advanced on the rising edge of the trigger only. Phase step is programmed in Reg 0Ah as a fraction of 360°, where  $2^{24} = 2\pi$ . For example, for a 1° phase step, program Reg 0Ah = round( (1/360) x  $2^{24} = 46603d = 860Bh$ )

In summary the following procedure is recommended to configure HMC703LP4E for PM mode:

- 1. Lock in fractional mode (Reg 06h[7:5] = 0) to  $F = f_{PD} \times (Reg 03h.Reg 04h)$ .

- Program (Reg 0Ah) to the intended phase step.

- 3. Change mode to PM ( $\frac{\text{Reg 06h}}{\text{[7:5]}} = 4$ ).

- 4. Change trigger option to edge or level (Reg 06h[8])

- 5. Select the trigger source Reg 06h[9] = 1, TRIG (pin-6), or Reg 06h[9] = 0 trigger from SPI write to Reg 0Eh).

#### Frequency Sweep Mode

The HMC703LP4E features a built-in sweeper mode, that supports external or automatic triggered sweeps. The maximum sweep range is only limited by the VCO dynamics and range.

Sweeper Mode includes:

a. Automatic 2-Way Sweep Mode

INITIAL trigger, ramp, ramp back, ramp, ramp back, ... Selected by writing Reg 06h[7:5] = 7

b. Triggered 2-Way Sweep Mode

INITIAL trigger, ramp, wait for trigger, ramp back, wait for trigger, ramp, ... Selected by writing Reg 06h[7:5] = 6

c. Triggered 1-Way Sweep Mode -

INITIAL trigger, ramp, wait for trigger, hop back to initial frequency, wait for trigger, ramp, ... Selected by writing Reg 06h[7:5] = 5

Applications include test instrumentation, FMCW sensors, automotive radars and others.

The parameters of the sweep function are illustrated in <u>Figure 31</u>. The HMC703LP4E generates a sweep by implementing miniature frequency steps in time. A smooth and continuous sweep is then generated, at the output of the VCO, after the stepped signal is filtered by the loop filter, as shown in <u>Figure 31</u>. The stepped sweep approach enables the HMC703LP4E to be in lock for entire duration of the sweep. This gives the HMC703LP4E a number of advantages over conventional methods including:

- · The ability to generate a linear sweep.

- The ability to have phase coherence between different ramps, so that the phase profile of each sweep is identical.

- The ability to generate sweeps with identical phase and phase noise performance.

- The ability to generate user defined sweeps in single-step ramp mode.

The HMC703LP4E sweep function cycles through a series of discrete frequency values which may be

- a. Stepped by an automatic sequencer or,

- b. Single stepped by individual triggers in Single Step Mode.

Triggering of each sweep, or step, may be configured to operate:

- a. Via a serial port write of 1 to Reg 0Eh[0] (it should then be returned to 0)

- b. Automatically generated internally

- c. Triggered via TRIG pin-6

Figure 31. HMC703LP4E Sweep Function

#### 2-Way Sweeps

The HMC703LP4E can be configured to operate in 2-Way Sweep mode by programming Reg 06h [7:5] = 6 or 7. A 2-way sweep is shown in Figure 32. The start of the sweep can be triggered by external TRIG pin-6 if EXTTRIG\_EN = 1, or the SPI\_TRIG (Reg 0Eh). In automatic 2-Way sweep (Reg 06h [7:5] = 7), the ramp restarts immediately, without waiting for an external trigger.

Figure 32. 2-Way Triggered Sweep

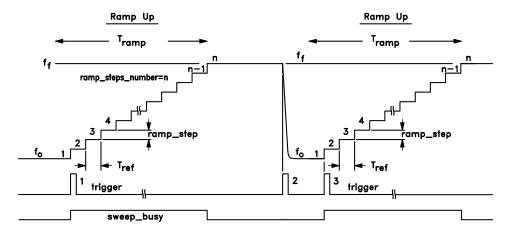

#### 1-Way Sweeps

The HMC703LP4E can be configured to operate in Triggered 1-Way Sweep mode by programming Reg 06h [7:5] = 6. Triggered 1-way sweeps are shown in Figure 33. Unlike 2-Way sweeps, Triggered 1-Way sweeps force the VCO to hop back to the start frequency upon the next trigger. Triggered 1-Way sweeps also require a 3<sup>rd</sup> trigger to start the new sweep. The 3<sup>rd</sup> trigger should be timed appropriately to allow the VCO to settle after the large frequency hop back to the start frequency. Subsequent odd numbered triggers will start the 1-Way sweep and repeat the process. 1-way sweep can be triggered by external TRIG pin-6 if EXTTRIG\_EN = 1, or the SPI\_TRIG (Reg 0Eh).

Figure 33. 1-Way Sweep Control

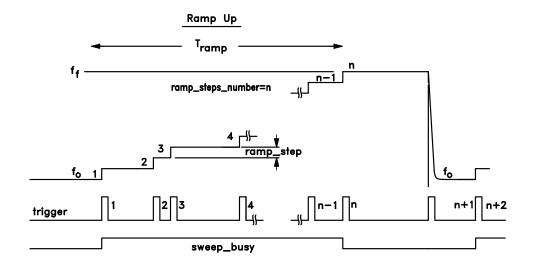

#### Single Step Ramp Mode

With any of the sweeper profiles, the HMC703LP4E can be configured to operate in single step mode. This causes it to wait for an explicit trigger before every change in the frequency setpoint. A Single Step 1-Way Ramp is shown in Figure 34. In this mode, a trigger is required for each step of the ramp. Similar to autosweep, the ramp\_busy flag will go high on the first trigger, and will stay high until the nth trigger. The n+1 trigger will cause the ramp to jump to the start frequency in 1-way ramp mode. The n+2 trigger will restart the 1-way ramp. Single step ramp mode can be triggered by external TRIG pin-6 if EXTTRIG\_EN = 1, or the SPI\_TRIG (Reg 0Eh).

In single-step mode (Reg 06h[23] = 1), the HMC703LP4E has the capability to generate arbitrarily shaped profiles defined by the timing density of the trigger pulses. On each trigger event the frequency is stepped by the step value programmed in Reg 0Ah. In addition, the HMC703LP4E allows the flexibility to change the step size (Reg 0Ah) during the ramp, between steps, adding another degree of freedom to ramp profile generation. Note that the maximum trigger rate where operation can be guaranteed is  $f_{PD}$ /5. In addition, the step register (Reg 0Ah) should not be updated via the SPI during the first two reference clock cycles after the trigger. The discrete nature of the frequency updates is smoothed by the loop filter, and should not pose a problem provided that update rate is > 10 x the loop bandwidth.

Figure 34. Single Step Ramp Mode

The user should be aware that the synthesized ramp is subject to normal phase locked loop dynamics. If the loop bandwidth in use is much wider than the rate of the steps then the locking will be fast and the ramp will have a staircase shape. If the update rate is higher than the loop bandwidth, as is normally the case, then the loop will not fully settle before a new frequency step is received. Hence the swept output will have a small lag and will sweep in a near continuous fashion.

#### **Detailed Sweeper Configuration**

The Following procedure is recommended to configure the frequency sweep in HMC703LP4E:

- 1. Lock in fractional mode (Reg 06h[7:5] = 0) to the start frequency ( $f_0$ ).

- 2. Program frequency step Reg 0Ah and stop N (Reg 0Ch, Reg 0Dh). Note that stop N must be exactly equal to start N plus an integer number of steps (Reg 0Ah). If it is not, the sweeper function will not terminate properly. This normally means rounding the stop N up or down slightly to ensure it falls on a step boundary.

- 3. Change Mode to Reg 06h[7:5] = 5,6, or 7 depending on the desired profile.

Note that the ramp step Reg 0Ah is signed two's complement. If negative, the first ramp has a negative slope, and vice-versa.

Setting autoseed ( $\frac{\text{Reg 06h}}{\text{Reg 05h}}$ ) into the phase accumulator at the beginning of each ramp

Setting Reg 06h[22] = 1 ensures identical phase AND quantization noise performance on each sweep by resetting the entire delta-sigma modulator at the beginning of each ramp.

Note that, while the HMC703LP4E can enforce phase coherence between different frequency sweeps, there will be a phase discontinuity if the start phase that is programmed in SEED (Reg 05h) is different from the phase state that the PLL finds itself in at the end of the ramp. This discontinuity can be prevented by tailoring the sweep profile such that the phase of the PLL at the start of the ramp is equal to phase at the end of the ramp.

Example: Configure a sweep from  $f_0 = 3000$  MHz to  $f_f = 3105$  MHz in Tramp  $\approx 2$  ms, with  $f_{PD} = 50$  MHz:

- 1. Start in fractional mode (Program Reg 06h[7:5] = 0)

- 1. Calculate Start N and Stop N, Program Start N (Reg 03h, Reg 04h)

Start N = 3000.0 MHz / 50.0 MHz = 60.0

Stop N = 3105.0 MHz / 50.0 MHz = 62.1

Program Reg 03h = 60, Reg 04h = 0

2. Calculate how many reference cycles will occur in 2 ms. Given that Tref =  $1/f_{PD}$  = 20ns,

Nbr of Steps = Tramp/Tref = 2ms/20ns = 100,000

3. Calculate the desired N step size, given Start N, Stop N and Nbr of Steps

$N_Step_Size_desired = (62.1 - 60.0) / 100,000 = 21u [fractions of N]$

4. Quantize the fractional N step into the 24 bit step size

Program Reg 0Ah =  $21u \times 2^{24}$  = round(352.32) = 352

5. Readjust the stop frequency slightly to ensure it falls exactly on a step boundary

Due to step quantization, there will be some finite error in either the sweep time or sweep span.

We have 3 choices:

a) Target an accurate sweep time, sacrifice resolution on stop frequency

Sweep time = 100k cycles = 2 ms

Stop  $N = Start N + 100,000 \times 352/2^{24}$  (Keep 100k cycles)

Stop  $N = 60.000 + 35,200,000 / 2^{24} \approx 62.09808$

*Program* Reg 0Ch = 62, Reg 0Dh = 35,200,000 MOD  $2^{24}$  = 1,645,568 ≈ 0.09808

$f_f \approx 3104.904$  (96 kHz lower stop frequency then desired)

b) Target an accurate stop frequency, at the expense of sweep time accuracy

Given step size of 352/224, how many cycles to get from 60.0 to 62.1

Nbr of Steps = (62.1 - 60.0) / (352/2<sup>24</sup>) = 100,091.345

Must round to 100,091 steps.

Sweep time = Tref \* 100,091 = 2.00182ms (1.82 us longer than desired)

Stop  $N = 60.0 + 100,091 \times 352/2^{24} \approx 62.0999927$

Program Reg 0Ch= 62, Reg 0Dh = 35,232,032 MOD  $2^{24}$  = 1,677,600 ≈ 0.0999927

$f_f = 3104.99964 \text{ MHz}$  (362 Hz lower stop frequency then desired)

- c) A combination of situation a and b

- 6. Program SD\_Mode based on desired trigger and ramp/hop profile (Reg 06h[7:5] = 5,6, or 7)

- 7. Trigger via either the external pin or SPI TRIG bit.

Continue to issue triggers to advance the ramp profile to the next stage...

#### Sweeper Configuration for Ultra Fine Step Sizes

In cases where finer step size resolution is desired, it is possible to reduce the  $f_{PD}$ , along with performance implications it has, or use a single-step mode (Reg 06h[23] = 1) and provide a lower frequency clock on the external trigger pin to reduce the update rate. The HMC703LP4E can generate a lower frequency clock by programming the R divider appropriately, and not using it for the PD (Reg 06h[21] = 1), but rather routing it out of the HMC703LP4E via the GPO. The R divider output can then be looped back to the TRIG pin of the HMC703LP4E to use as a low rate trigger. See "Ref Path 'R' Divider" for more details.

#### Reference Input Stage

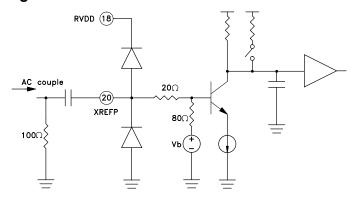

Figure 35. Reference Path Input Stage

The reference buffer provides the path from an external reference source (generally crystal based) to the R divider, and eventually to the phase detector. The buffer has two modes of operation. High Gain (recommended below 200 MHz), and High frequency, for 200 to 350 MHz operation. The buffer is internally DC biased, with 100  $\Omega$  internal termination. For 50  $\Omega$  match, an external 100  $\Omega$  resistance to AC ground should be added, followed by an AC coupling capacitance (impedance < 1 Ohm), then to the XREFP pin of the part.

At low frequencies, a relatively square reference is recommended to keep the input slew rate high. At higher frequencies, a square or sinusoid can be used. The following table shows the recommended operating regions for different reference frequencies. If operating outside these regions the part will normally still operate, but with degraded performance.

Minimum pulse width at the reference buffer input is 2.5 ns. For best spur performance when R = 1, the pulse width should be > (2.5 ns + 8 Tps), where Tps is the period of the VCO at the prescaler input. When R > 1 minimum pulse width is 2.5 ns.

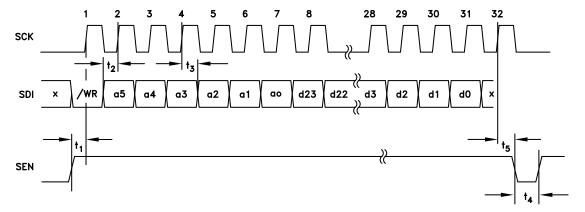

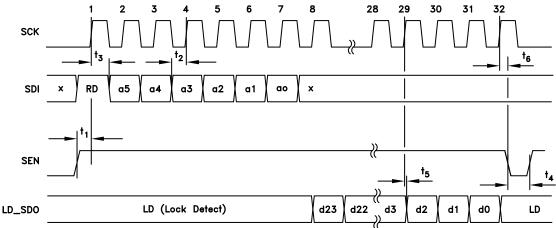

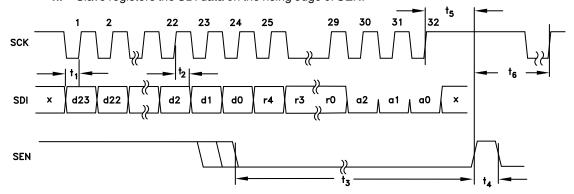

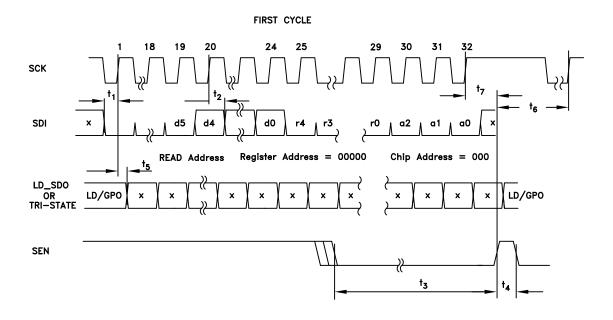

Table 7. Reference Sensitivity Table