SNVS489I-NOVEMBER 2006-REVISED SEPTEMBER 2013

# LP3913 Power Management IC for Flash Memory-Based Portable Media Players

Check for Samples: LP3913

## **FEATURES**

- 2 Low-Dropout Regulators -- LDO1 is Used for General Purpose Applications, LDO2 is Used for Low-Noise Analog Applications. Both LDOs Have Programmable Output Voltages.

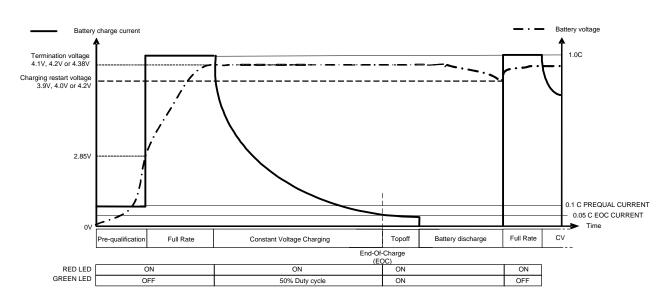

- Green and Red LED Charger Status Drivers

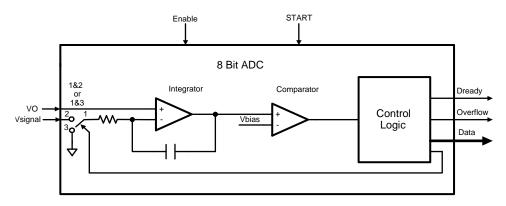

- 4-Channel 8-Bit Dual Slope A/D Converter

- **3 High-Efficiency DVS Buck Converters** •

- 400 kHz I<sup>2</sup>C Compatible Interface

- Linear Constant-Current/Constant-Voltage Charger for Single Cell Lithium-Ion Batteries

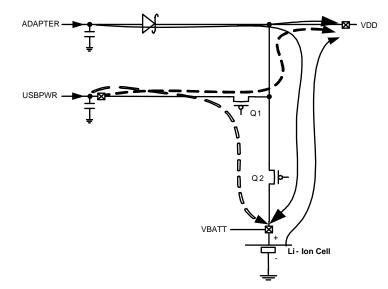

- USB and Adapter Charging

- System Power Supply Management

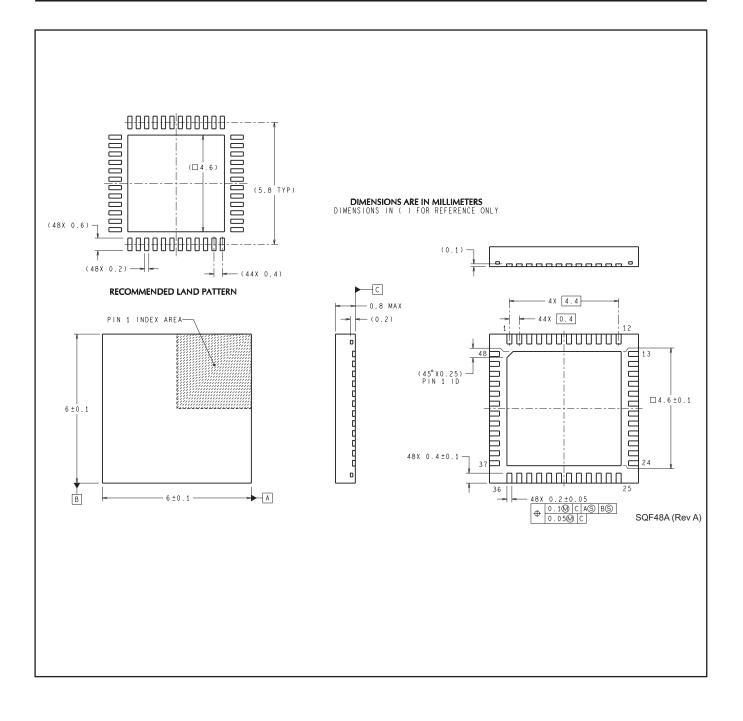

- 6x6 x 0.8 mm 48 WQFN Package

- Voltage and Thermal Supervisory Circuits

- **Continuous Battery Voltage Monitoring**

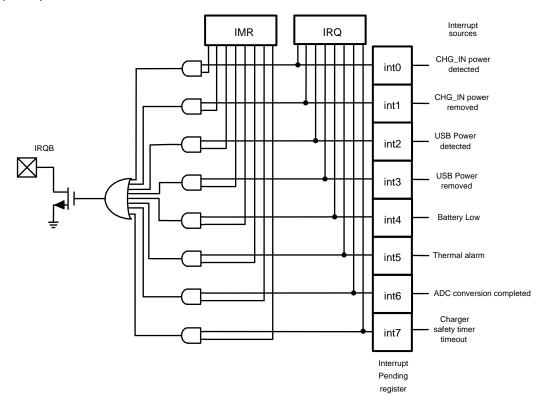

- **Interrupt Request Output with 8 Sources**

- LP3913 is Pin-for-Pin and Software-Compatible with the LP3910 Hard Drive Based PMIC

## **KEY SPECIFICATIONS**

- LDO1: 150 mA, 1.2V-3.3V

- LDO2: 150 mA, 1.3V-3.3V

- Buck1: 600 mA, 0.8V-2.0V

- Buck2: 600 mA, 1.8V-3.3V .

- Buck3: 500 mA, 1.8V-3.3V

- 50 mΩ Battery Path Resistance

- 100 mA to 1000 mA Full-Rate Charge Current Using Wall Adapter

- Selectable 0.05C and 0.1C EOC Current

- USB Current Limit of 100 mA, 500 mA, and 800 . mΑ

- **USB Pre-Qual Current of 50 mA**

- Selectable 4.1V, 4.2V or 4.38V battery • termination voltages

- 0.35% Battery Termination Accuracy

- ±1 LSB INL/DNL on 8-bit A/D Converter

## **APPLICATIONS**

- **Flash-Based Portable Media Players** •

- **Portable Gaming Devices**

- **Portable Navigation Systems** •

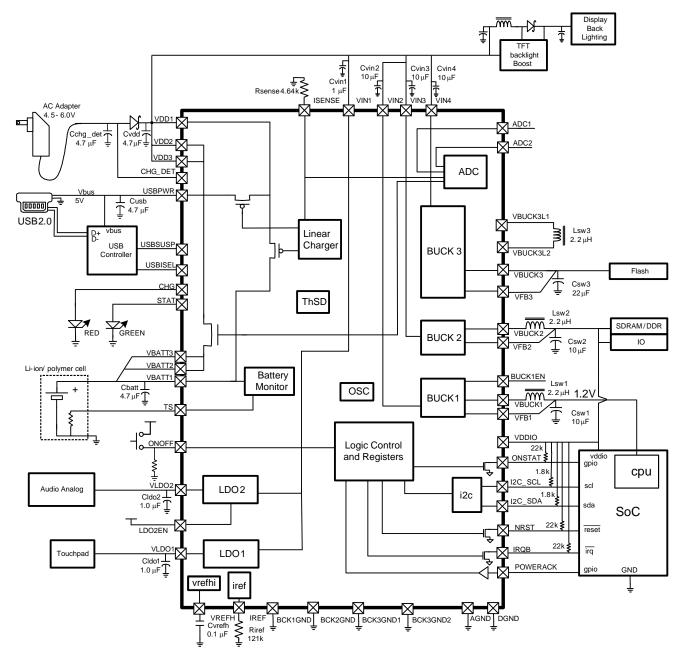

## DESCRIPTION

The LP3913 is a programmable system power management unit that is optimized for Flash Memory based Portable Media Players.

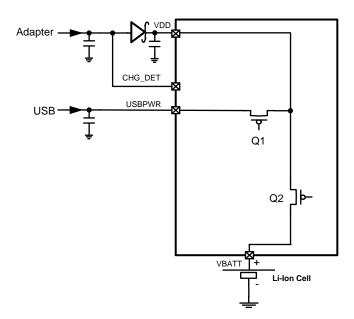

The LP3913 incorporates 2 low-dropout LDO voltage regulators, 3 integrated Buck DC/DC converters with Dynamic Voltage Scaling (DVS), a 4-channel 8-bit A/D converter, and a dual source Li-lon/polymer battery charger. The charger has the capability to charge and maintain a single cell battery from a regulated wall adapter or USB power. When both USB and adapter sources are present, then the adapter source takes precedence and switching between USB and adapter power sources is seamless. In addition, the battery charger supports power routing. which allows system usage immediately after an external power source has been detected. The LP3913 also incorporates some advanced battery management functions such as battery temperature measurement, reverse current blocking for USB, LED charger status indication, thermally regulated internal power FETs, battery voltage monitoring, over-current protection and a 10-hour safety timer.

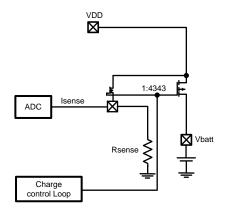

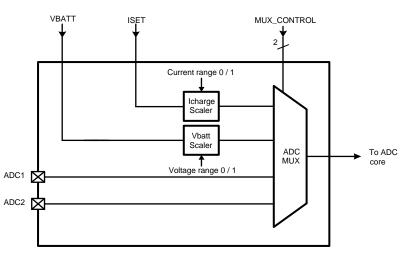

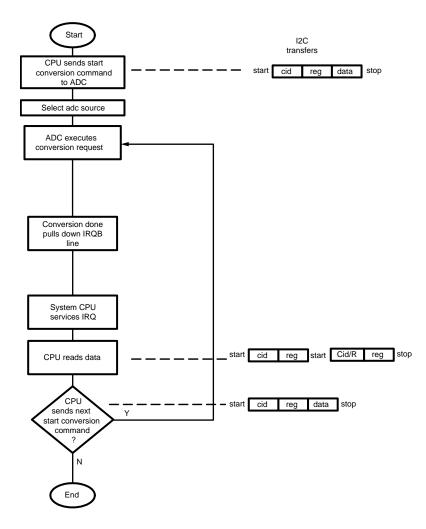

The 4-channel A/D converter measures the battery voltage and charge current, which can be used for fuel gauging. Two undedicated channels can be used to measure other analog parameters such as discharge current, battery temperature, keyboard resistor scanning and more.

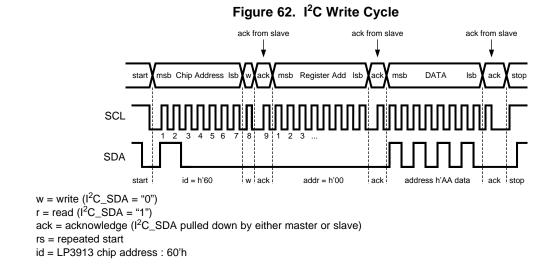

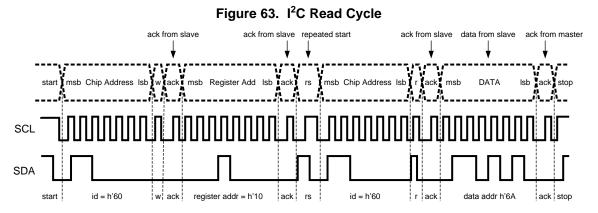

The various IC parameters are programmable through a 400 kHz I<sup>2</sup>C compatible interface.

The LP3913 is available in a thermally-enhanced 6x6x0.8 mm 48 WQFN package and operates over an ambient temperature range of -40°C to +85°C.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. All trademarks are the property of their respective owners.

www.ti.com

www.ti.com

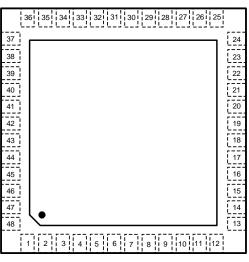

### **Connection Diagram**

## **Device Connection Diagram**

Figure 1. 48 WQFN Package (Top View) Package Number NJV0048A

### **Table 1. Additional Application Information**

| Part Number                | LDO1 (V) | LDO2 (V) | Buck1 (V) | Buck2 (V) | Buck 3 (V) | ICHRG (mA) |

|----------------------------|----------|----------|-----------|-----------|------------|------------|

| LP3913SQ-AA/LP3913SQX-AA   | 2.00     | 3.30     | 1.20      | 3.30      | 3.30       | 100        |

| LP3913SQ-AC/LP3913SQX-AC   | 1.30     | 3.30     | 1.30      | 1.80      | 3.30       | 100        |

| LP3913SQ-AD/LP3913SQX-AD   | 2.00     | 3.30     | 1.20      | 1.80      | 3.30       | 100        |

| LP3913SQ-ADJ/LP3913SQX-ADJ | 1.80     | 3.30     | ADJ       | ADJ       | 3.30       | 100        |

| LP3913SQ-AE/LP3913SQX-AE   | 1.30     | 3.30     | 1.30      | 3.30      | 3.30       | 100        |

| LP3913SQ-AR/LP3913SQX-AR   | 1.80     | 3.30     | 1.20      | 1.80      | 3.30       | 1000       |

## **Pin Descriptions**

| Pin # | Name     | I/O | Туре          | Functional Description                                                                                                                                                                            |

|-------|----------|-----|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

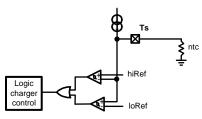

| 1     | TS       | Ι   | A             | Battery temperature sense pin. This pin is normally connected to the thermistor pin of the battery cell.                                                                                          |

| 2     | VBATT1   | 0   | А             | Positive battery terminal. This pin must be externally shorted to VBATT2 and VBATT3                                                                                                               |

| 3     | AGND     | G   | G             | Analog Ground                                                                                                                                                                                     |

| 4     | VREFH    | 0   | А             | Connection to bypass capacitor for internal high reference                                                                                                                                        |

| 5     | LDO2EN   | Ι   | D             | Digital input to enable/disable LDO2                                                                                                                                                              |

| 6     | VLDO2    | 0   | А             | LDO2 Output                                                                                                                                                                                       |

| 7     | VIN1     | Ι   | PWR           | Power input to LDO1 and LDO2. VIN1 pin must be externally shorted to the VDD pins.                                                                                                                |

| 8     | VLDO1    | 0   | А             | LDO1 Output                                                                                                                                                                                       |

| 9     | POWERACK | Ι   | D             | Digital power acknowledgment input (see Power On/Off Sequencing)                                                                                                                                  |

| 10    | ISENSE   | I   | A             | A 4.64-k $\Omega$ resistor must be connected between this pin and GND. A fraction of the charge current flows through this resistor to enable the A to D converter to measure the charge current. |

| 11    | ADC2     | Ι   | А             | Channel 2 input to AD converter                                                                                                                                                                   |

| 12    | ADC1     | I   | А             | Channel 1 input to AD converter                                                                                                                                                                   |

| 13    | IRQB     | 0   | Open<br>Drain | Open drain active low interrupt request                                                                                                                                                           |

| Pin # | Name                 | I/O | Туре          | Functional Description                                                                                                                                      |

|-------|----------------------|-----|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14    | NRST                 | 0   | Open<br>Drain | Open drain active low reset during Standby                                                                                                                  |

| 15    | CHG                  | 0   | D             | This output indicates that a valid charger supply source (USB adapter) has been detected, and the IC is charging. (Red LED)                                 |

| 16    | STAT                 | 0   | D             | Battery Status output indicator - Off during CC, 50% duty cycle during CV, 100% duty cycle with a fully charged Li-ion battery (Green LED)                  |

| 17    | BUCK1EN              | I   | D             | Digital input to enable/disable BUCK1                                                                                                                       |

| 18    | VFB1                 | I   | А             | Buck1 Feedback input terminal                                                                                                                               |

| 19    | BCKGND1              | G   | G             | Buck1 Ground                                                                                                                                                |

| 20    | VBUCK1               | 0   | А             | Buck1 Output                                                                                                                                                |

| 21    | VIN2                 | Ι   | PWR           | Power input to BUCK1. VIN2 pin must be externally shorted to the VDD pins.                                                                                  |

| 22    | VIN3                 | Ι   | PWR           | Power input to BUCK2. VIN3 pin must be externally shorted to the VDD pins.                                                                                  |

| 23    | VBUCK2               | 0   | А             | Buck2 Output                                                                                                                                                |

| 24    | BCKGND2              | G   | G             | Buck2 Ground                                                                                                                                                |

| 25    | VFB2                 | Ι   | А             | Buck2 Feedback input terminal                                                                                                                               |

| 26    | ONOFF                | I   | D             | Power ON/OFF pin configured either as level (High or Low) triggered or edge (High or Low) triggered.                                                        |

| 27    | I <sup>2</sup> C_SCL | Ι   | D             | I <sup>2</sup> C-compatible interface clock terminal                                                                                                        |

| 28    | VDDIO                | I   | D             | Supply to input / output stages of digital I/O                                                                                                              |

| 29    | I <sup>2</sup> C_SDA | I/O | D             | I <sup>2</sup> C-compatible interface data terminal                                                                                                         |

| 30    | ONSTAT               | 0   | Open<br>Drain | Open Drain output that reflects the debounced state of ONOFF pin.                                                                                           |

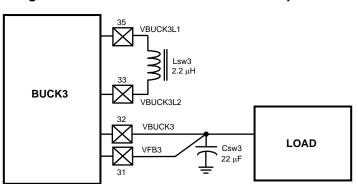

| 31    | VFB3                 | Ι   | А             | Buck3 Feedback input terminal                                                                                                                               |

| 32    | VBUCK3               | 0   | А             | Buck3Output voltage                                                                                                                                         |

| 33    | VBUCK3L2             | I   | А             | Buck3 inductor                                                                                                                                              |

| 34    | BCK3GND1             | G   | G             | Buck3t high current ground                                                                                                                                  |

| 35    | VBUCK3L1             | I   | А             | Buck3 inductor                                                                                                                                              |

| 36    | VIN4                 | Ι   | PWR           | Power input to Buck3. VIN4 pin must be externally shorted to the VDD pins.                                                                                  |

| 37    | USBSUSP              | Ι   | D             | This pin needs to be pulled high during USB suspend mode.                                                                                                   |

| 38    | USBISEL              | I   | D             | Pulling this pin low limits the USB charge current to 100 mA. Pulling this pin high limits the USB charge current to 500 mA.                                |

| 39    | BUCK3GND2            | G   | G             | Buck3 Core Ground                                                                                                                                           |

| 40    | DGND                 | G   | G             | Digital ground                                                                                                                                              |

| 41    | VDD3                 | I   | PWR           | Power input to supply application. This pin must be externally shorted to VDD1 and VDD2.                                                                    |

| 42    | VDD2                 | Ι   | PWR           | Power input to supply application This pin must be externally shorted to VDD1 and VDD3.                                                                     |

| 43    | VBATT3               | 0   | А             | Positive battery terminal. This pin must be externally shorted to V\BATT1 and VBATT2.                                                                       |

| 44    | VBATT2               | 0   | А             | Positive battery terminal. This pin must be externally shorted to VBATT1 and VBATT3.                                                                        |

| 45    | USBPWR               | I   | PWR           | USB power input pin                                                                                                                                         |

| 46    | VDD1                 | I   | PWR           | Power input to supply application This pin is shorted to VDD2 and VDD3.                                                                                     |

| 47    | CHG_DET              | I   | А             | Wall adapter power input pin                                                                                                                                |

| 48    | IREF                 | Ι   | A             | A 121 k $\Omega$ resistor must be connected between this pin and AGND. The resistor value determines the reference current for the internal bias generator. |

A: Analog Pin D: Digital Pin G: Ground Pin

Submit Documentation Feedback

4

Pin PWR: Power Pin

ower Pin I: Inp

I: Input Pin

I/O: Input/Output Pin

O: Output Pin

www.ti.com

P3913

www.ti.com

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

## ABSOLUTE MAXIMUM RATINGS (1) (2)(3)(4)

| Supply voltage range CHG_DET                                     | -0.3V to +6.5V     |

|------------------------------------------------------------------|--------------------|

| Voltage range USBPWR,<br>VIN1,VIN2,VIN3,VIN4, VDD1,VDD2,VDD3     | -0.3V to +6.2V     |

| Battery voltage range VBATT1, 2, 3                               | -0.3V to +5V       |

| All other pins                                                   | -0.3V to VDD +0.3V |

| Storage Temperature Range                                        | −45°C to +150°C    |

| Power Dissipation ( $T_A = 70^{\circ}C^{(5)}$ ):                 | 2.6W               |

| ESD Rating <sup>(6)</sup><br>Human Body Model:<br>Machine Model: | 2.0 kV<br>200V     |

(1) Absolute Maximum Ratings indicate limits beyond which damage to the component may occur. Operating Ratings are conditions under which operation of the device is specified. Operating Ratings do not imply performance limits. For performance limits and associated test conditions, see the Electrical Characteristics tables.

(2) All voltages are with respect to the potential at the GND pin.

(3) In applications where high power dissipation and/or poor package thermal resistance is present, the maximum ambient temperature may have to be derated. Maximum ambient temperature (T<sub>A-MAX</sub>) is dependent on the maximum operating junction temperature (T<sub>J-MAX-OP</sub> = 125°C), the maximum power dissipation of the device in the application (P<sub>D-MAX</sub>), and the junction-to-ambient thermal resistance of the part/package in the application (θ<sub>JA</sub>), as given by the following equation: T<sub>A-MAX</sub> = T<sub>J-MAX-OP</sub> - (θ<sub>JA</sub> × P<sub>D-MAX</sub>).

(4) If Military/Aerospace specified devices are required, please contact the TI Sales Office/Distributors for availability and specifications.

(4) If Military/Aerospace specified devices are required, please contact the TI Sales Office/Distributors for availability and specifications.

(5) Internal thermal shutdown circuitry protects the device from permanent damage. Thermal shutdown engages at T<sub>J</sub> = 160°C (typ.) and disengages at T<sub>J</sub> = 140°C (typ.).

(6) The Human body model is a 100 pF capacitor discharged through a 1.5 kΩ resistor into each pin. The machine model is a 200 pF capacitor discharged directly into each pin. MIL-STD-883 3015.7.

### **RECOMMENDED OPERATING CONDITIONS**<sup>(1)</sup> <sup>(2)</sup> <sup>(3)</sup>

| CHG_DET                                          | 4.5V to 6.0V    |

|--------------------------------------------------|-----------------|

| USBPWR                                           | 4.35V to 6.0V   |

| VBATT1, 2, 3                                     | 0V to 4.5V      |

| VIN1, VIN2, VIN3, VIN4, VDD1, VDD2, VDD3         | 2.5V to 6.0V    |

| VDDIO                                            | 2.5V to VDD     |

| Junction Temperature (T <sub>J</sub> ) Range     | -40°C to +125°C |

| Ambient Temperature (T <sub>A</sub> ) Range      | −40°C to +85°C  |

| Power Dissipation for $T_{JjMAX}$ and $T_{AMAX}$ | 1.6W            |

Junction-to-ambient thermal resistance is highly application and board-layout dependent. In applications where high maximum power dissipation exists, special care must be paid to thermal dissipation issues in board design.

(2) Min and Max limits are specified by design, test, or statistical analysis. Typical numbers represent the most likely norm.

(3) Typical values and limits appearing in normal type for  $T_J = 25^{\circ}$ C. Limits appearing in **boldface type** apply over the entire junction temperature range for operation, -40°C to +125°C.

## THERMAL INFORMATION<sup>(1)</sup>

| Junction-to-Ambient Thermal Resistance (θ <sub>JA</sub> ), | 25°C/W |

|------------------------------------------------------------|--------|

| 48-pin WQFN NJV0048A Package <sup>(2)</sup>                |        |

(1) In applications where high power dissipation and/or poor package thermal resistance is present, the maximum ambient temperature may have to be derated. Maximum ambient temperature  $(T_{A-MAX})$  is dependent on the maximum operating junction temperature  $(T_{J-MAX-OP} = 125^{\circ}C)$ , the maximum power dissipation of the device in the application  $(P_{D-MAX})$ , and the junction-to-ambient thermal resistance of the part/package in the application  $(\theta_{JA})$ , as given by the following equation:  $T_{A-MAX} = T_{J-MAX-OP} - (\theta_{JA} \times P_{D-MAX})$ .

(2) Min and Max limits are specified by design, test, or statistical analysis. Typical numbers represent the most likely norm.

www.ti.com

## **GENERAL ELECTRICAL CHARACTERISTICS**

Unless otherwise noted, VDD = 5V, VBATT = 3.6V. Typical values and limits appearing in normal type apply for  $T_J = 25^{\circ}C$ . Limits appearing in **boldface type** apply over the entire junction temperature range for operation,  $T_J = 0^{\circ}C$  to +125°C. (1)(2)(3)(4)

| Symbol                | Parameter                          | Conditions                                                                                       | Min | Тур | Max             | Units |

|-----------------------|------------------------------------|--------------------------------------------------------------------------------------------------|-----|-----|-----------------|-------|

| I <sub>Q_BATT</sub>   | Battery Standby Supply<br>Current  | All circuits off except for<br>POR and battery monitor.<br>No adapter or USB power<br>connected. |     | 6   | 20              | μA    |

| V <sub>POR</sub>      | Power-On Reset Threshold           | VDD Falling Edge                                                                                 |     | 1.9 |                 | V     |

| T <sub>SD</sub>       | Thermal Shutdown<br>Threshold      |                                                                                                  |     | 160 |                 | °C    |

| T <sub>SDH</sub>      | Themal Shutdown<br>Hysteresis      |                                                                                                  |     | 20  |                 | °C    |

| T <sub>TH-ALERT</sub> | Thermal Interrupt<br>Threshold     |                                                                                                  |     | 115 |                 | °C    |

| VDDIO                 | IO Supply                          |                                                                                                  | 2.5 |     | V <sub>DD</sub> | V     |

| F <sub>CLK</sub>      | Internal System Clock<br>Frequency |                                                                                                  |     | 2   |                 | MHz   |

(1) All voltages are with respect to the potential at the GND pin.

(2) Min and Max limits are specified by design, test, or statistical analysis. Typical numbers represent the most likely norm.

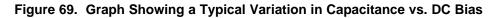

(3) Low ESR Surface-Mount Ceramic Capacitors (MLCCs) are used in setting electrical characteristics.

(4) Specified by design. Not production tested

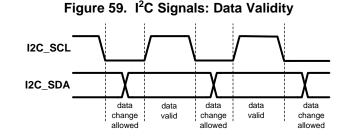

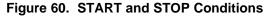

## I<sup>2</sup>C INTERFACE ELECTRICAL CHARACTERISTICS

Unless otherwise noted, VDDIO = 3.6V. Typical values and limits appearing in normal type apply for  $T_J = 25^{\circ}$ C. Limits appearing in **boldface type** apply over the entire junction temperature range for operation,  $T_J = 0^{\circ}$ C to +125°C.<sup>(1)(2)(3)(4)</sup>

| Symbol                 | Parameter                                                                                                        | Conditions                                  | Min          | Тур | Max          | Units |

|------------------------|------------------------------------------------------------------------------------------------------------------|---------------------------------------------|--------------|-----|--------------|-------|

| V <sub>IL</sub>        | Low Level Input Voltage                                                                                          | I <sup>2</sup> C_SDA & I <sup>2</sup> C_SCL |              |     | 0.3VDDI<br>O | V     |

| V <sub>IH</sub>        | High Level Input Voltage                                                                                         | I <sup>2</sup> C_SDA & I <sup>2</sup> C_SCL | 0.7VDDI<br>O |     |              | V     |

| V <sub>OL</sub>        | Low Level Output Voltage                                                                                         | I <sup>2</sup> C_SDA & I <sup>2</sup> C_SCL | 0            |     | 0.2VDDI<br>O | V     |

| V <sub>HYS</sub>       | Schmitt Trigger Input Hysterisis                                                                                 | I <sup>2</sup> C_SDA & I <sup>2</sup> C_SCL | 0.1VDDI<br>O |     |              | V     |

| F <sub>CLK</sub>       | Clock Frequency                                                                                                  |                                             |              |     | 400          | kHz   |

| t <sub>BF</sub>        | Bus-Free Time between START and STOP                                                                             | (4)                                         | 1.3          |     |              | μs    |

| t <sub>HOLD</sub>      | Hold Time Repeated START<br>Condition                                                                            | (4)                                         | 0.6          |     |              | μs    |

| t <sub>CLK-LP</sub>    | CLK Low Period                                                                                                   | (4)                                         | 1.3          |     |              | μs    |

| t <sub>CLK-HP</sub>    | CLK High Period                                                                                                  | (4)                                         | 0.6          |     |              | μs    |

| t <sub>SU</sub>        | Set-up Time Repeated START<br>Condition                                                                          | (4)                                         | 0.6          |     |              | μs    |

| t <sub>DATA-HOLD</sub> | Data Hold Time                                                                                                   | (4)                                         | 0            |     |              | μs    |

| t <sub>DATA-SU</sub>   | Data Set-up Time                                                                                                 | (4)                                         | 100          |     |              | ns    |

| t <sub>SU</sub>        | Set-Up Time for STOP Condition                                                                                   | (4)                                         | 0.6          |     |              | μs    |

| t <sub>TRANS</sub>     | Maximum Pulse Width of Spikes<br>That Must Be Suppressed by the<br>Input Filter of Both Data and<br>CLK Signals. | (4)                                         | 50           |     |              | μs    |

(1) All voltages are with respect to the potential at the GND pin.

(2) Min and Max limits are specified by design, test, or statistical analysis. Typical numbers represent the most likely norm.

(3) Low ESR Surface-Mount Ceramic Capacitors (MLCCs) are used in setting electrical characteristics.

(4) Specified by design. Not production tested.

P3913

www.ti.com

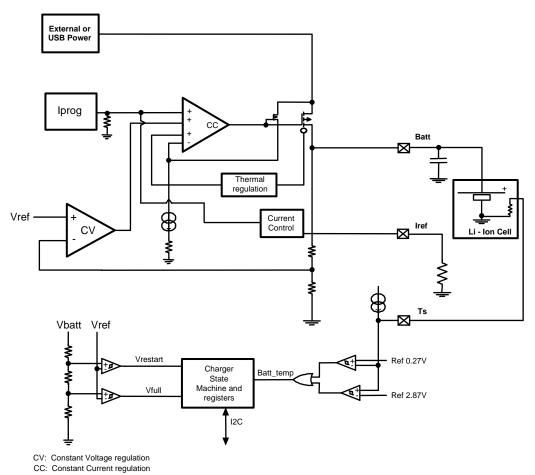

## LI-ION BATTERY CHARGER ELECTRICAL CHARACTERISTICS

Unless otherwise noted, VDD = 5.0V,VBATT = 3.6V,  $C_{BATT}$  = 4.7  $\mu$ F,  $C_{CHG_DET}$  = 10  $\mu$ F,  $R_{IREF}$  = 121 k $\Omega$ . Typical values and limits appearing in normal type apply for  $T_J$  = 25°C. Limits appearing in **boldface type** apply over the entire junction temperature range for operation,  $T_J$  = 0°C to +125°C. <sup>(1)(2)(3)(4)(5)</sup>

| Symbol                 | Parameter                                                                                 | Conditions                                                                                                                         | Min                   | Тур                   | Мах                   | Units |

|------------------------|-------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------|-----------------------|-------|

| V <sub>USB</sub>       | Minimum External USB<br>Supply Soltage                                                    | USB Current Limit = 500 mA                                                                                                         | 4.15                  | 4.25                  | 4.35                  | V     |

| V <sub>USB_HYST</sub>  | USBPWR Detect<br>Hysteresis                                                               |                                                                                                                                    |                       | 50                    |                       | mV    |

| CHG_DET                | Minimum External<br>Adapter Supply Voltage<br>Range                                       | Adapter Current Limit = 1A<br>V <sub>FWD</sub> Schottky = 350 mV                                                                   | 4.4                   | 4.5                   | 4.6                   | V     |

| V <sub>CHG_HYST</sub>  | CHG_DET Input<br>Hysteresis                                                               |                                                                                                                                    |                       | 150                   |                       | mV    |

| USB_SUSP               | Quiescent Current in USB<br>Suspend Mode                                                  | USB Suspend Mode,<br>$V_{USB} = 5.0V$<br>USBSUSP = USBPWR<br>USBISEL = 0V                                                          |                       | 30                    | 60                    | μA    |

| VTERM_TOL              | Battery Charge<br>Termination Voltage<br>Tolerance                                        | $T_{A} = 25^{\circ}C,$<br>$I_{PROG} = 500 \text{ mA}$<br>$I_{CHG} = 50 \text{ mA}$                                                 | -0.35<br>-0.5<br>-0.5 | 4.2V<br>4.1V<br>4.38V | +0.35<br>+0.5<br>+0.5 | %     |

|                        |                                                                                           | $T_{A} = 0^{\circ}C \text{ to } 125^{\circ}C,$<br>$I_{PROG} = 500 \text{ mA},$<br>$I_{CHG} = 50 \text{ mA}$                        | −1<br>−1.5<br>−1.5    | 4.2V<br>4.1V<br>4.38V | +1<br>+1.5<br>+1.5    | 70    |

| CHG_WA                 | Full-rate Charging Current<br>from Wall Adapter Input<br>(See Full-Rate Charging<br>Mode) | $\begin{array}{l} CHG\_DET=5.25V\\ V_{BATT}=3.6V\\ I_{PROG}=500 \text{ mA} \end{array}$                                            | 450                   | 500                   | 550                   | mA    |

| CHG_USB                | Full-rate Charging Current<br>from USBPWR Input (See<br>Full-Rate Charging Mode)          |                                                                                                                                    | 450                   | 500                   | 550                   | mA    |

|                        |                                                                                           | $\label{eq:VB} \begin{array}{l} USB = 5V \\ V_{BATT} = 3.6V \\ I_{PROG} = 500 \text{ mA} \\ USB_ISEL = 500 \text{ mA} \end{array}$ | 405                   | 450                   | 495                   | mA    |

| USB I <sub>LIMIT</sub> |                                                                                           | USB_ISEL = 100 mA<br>USB_ISEL= 500 mA<br>USB_ISEL = 800 mA                                                                         | 90<br>450<br>720      | 95<br>475<br>760      | 100<br>500<br>800     | mA    |

| PREQUAL                | Pre-qualification Current                                                                 | V <sub>BATT</sub> = 2.5V, Wall Adapter<br>Charge Current.<br>Percentage of Programmed<br>Full Rate Current.                        | 8                     | 10                    | 12                    | %     |

|                        |                                                                                           | VBATT = 2.5V, USB Charge<br>Current                                                                                                | 40                    | 50                    | 60                    | mA    |

| /FULL_RATE             | Full-rate Qualification<br>Threshold                                                      | V <sub>BATT</sub> Rising, Transition from<br>Pre-Qualification to Full-rate<br>Charging                                            | 2.75                  | 2.85                  | 2.95                  | V     |

| V <sub>TH_H</sub>      | Upper T <sub>S</sub> Comparator<br>Limit                                                  |                                                                                                                                    | 2.82                  | 2.87                  | 2.93                  | V     |

| / <sub>TH_L</sub>      | Lower T <sub>S</sub> Comparator                                                           | 45°C CHSPV Reg D3 = 0                                                                                                              | 0.315                 | 0.33                  | 0.345                 | v     |

|                        |                                                                                           | 50°C CHSPV Reg D3 = 1                                                                                                              | 0.255                 | 0.27                  | 0.285                 | · ·   |

| TSENSE                 | Battery Temperature<br>Sense Current                                                      |                                                                                                                                    | 7.75                  | 8.00                  | 8.25                  | μA    |

(1) All voltages are with respect to the potential at the GND pin.

(2) Junction-to-ambient thermal resistance is highly application and board-layout dependent. In applications where high maximum power dissipation exists, special care must be paid to thermal dissipation issues in board design.

(3) Min and Max limits are specified by design, test, or statistical analysis. Typical numbers represent the most likely norm.

(4) Low ESR Surface-Mount Ceramic Capacitors (MLCCs) are used in setting electrical characteristics.

(5) Typical values and limits appearing in normal type for  $T_J = 25^{\circ}$ C. Limits appearing in **boldfacetype** apply over the entire junction temperature range for operation,  $-40^{\circ}$ C to  $+125^{\circ}$ C.

# LI-ION BATTERY CHARGER ELECTRICAL CHARACTERISTICS (continued)

Unless otherwise noted, VDD = 5.0V,VBATT = 3.6V,  $C_{BATT}$  = 4.7  $\mu$ F,  $C_{CHG_{DET}}$  = 10  $\mu$ F,  $R_{IREF}$  = 121 k $\Omega$ . Typical values and limits appearing in normal type apply for  $T_J$  = 25°C. Limits appearing in **boldface type** apply over the entire junction temperature range for operation,  $T_J$  = 0°C to +125°C. (1)(2)(3)(4)(5)

| Symbol           | Parameter                                 | Conditions | Min | Тур | Max | Units |

|------------------|-------------------------------------------|------------|-----|-----|-----|-------|

| T <sub>REG</sub> | Regulated Charger<br>Junction Temperature |            | 105 | 115 | 125 | °C    |

## **DETECTION AND TIMING**

| Symbol                | Parameter                                                                        | Conditions                                                                        | Min                  | Тур                   | Max                  | Units |

|-----------------------|----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|----------------------|-----------------------|----------------------|-------|

| IEOC                  | End-of-Charge Current                                                            | I <sub>PROG</sub> = 500 mA,<br>10% EOC Setting                                    | 40                   | 50                    | 60                   | mA    |

|                       |                                                                                  | I <sub>PROG</sub> = 500 mA<br>5% EOC Setting                                      | 20                   | 25                    | 30                   | mA    |

| V <sub>RESTARTI</sub> | Battery Restart Charging<br>Voltage                                              | V <sub>TERM</sub> = 4.1V<br>V <sub>TERM</sub> = 4.2V<br>V <sub>TERM</sub> = 4.38V | 3.82<br>3.94<br>4.14 | 3.9V<br>4.0V<br>4.2 V | 3.94<br>4.06<br>4.26 | v     |

| T <sub>CHG_IN</sub>   | Deglitch Adapter Insertion                                                       |                                                                                   | 28                   | 32                    | 36                   | ms    |

| T <sub>USB</sub>      | Deglitch USB Power<br>Insertion                                                  |                                                                                   | 28                   | 32                    | 36                   | ms    |

| T <sub>PQ_FULL</sub>  | Deglitch Time for Pre-<br>qualification to Full-rate<br>Charge Transition        |                                                                                   | 8                    | 10                    | 12                   | ms    |

| T <sub>FULL_PQ</sub>  | Deglitch Time for Full-rate<br>to Pre-qualification<br>Transition                |                                                                                   | 8                    | 10                    | 12                   | ms    |

| TBATTLOWF             | Deglitch Time for $V_{\text{BATT}}$ Falling below $V_{\text{BATTLOW}}$ Threshold |                                                                                   | 4                    | 5                     | 6                    | ms    |

| T <sub>BATTLOWR</sub> | Deglitch Time for $V_{\text{BATT}}$ Rising above $V_{\text{BATTLOW}}$ Threshold  |                                                                                   | 4                    | 5                     | 6                    | ms    |

| T <sub>BATTEMP</sub>  | Deglitch Time for Recovery<br>from Battery Temperature<br>Fault                  |                                                                                   | 8                    | 10                    | 12                   | ms    |

| T <sub>ONOFF_F</sub>  | Deglitching on Falling<br>Edge of ONOFF Pin                                      |                                                                                   | 28                   | 32                    | 36                   | ms    |

| T <sub>ONOFF_R</sub>  | Deglitching on Rising Edge of ONOFF Pin                                          |                                                                                   | 28                   | 32                    | 36                   | ms    |

| T <sub>RESTART</sub>  | Deglitching on Falling $V_{BATT}$ Crossing $V_{RESTART}$                         |                                                                                   | 8                    | 10                    | 12                   | ms    |

| T <sub>CCCV</sub>     | Deglitching of CC->CV<br>Charging Transition                                     |                                                                                   | 8                    | 10                    | 12                   | ms    |

| T <sub>CVEOC</sub>    | Deglitching of CV->EOC (End of Charge)                                           |                                                                                   | 8                    | 10                    | 12                   | ms    |

| T <sub>POWERACK</sub> | Deglitching of POWERACK<br>Pin                                                   |                                                                                   | 4                    | 5                     | 6                    | ms    |

| T <sub>TSHD</sub>     | Deglitching of Thermal Shutdown                                                  |                                                                                   |                      | 2                     |                      | ms    |

| T <sub>TOPOFF</sub>   | Topoff Timer                                                                     |                                                                                   | 17                   | 21                    | 25                   | min   |

| T <sub>10HR</sub>     | 10 Hour Safety Timer                                                             |                                                                                   | 9                    | 10                    | 11                   | hours |

| T <sub>1HR</sub>      | 1 Hour Prequal Safety<br>Timer                                                   |                                                                                   | 0.9                  | 1                     | 1.1                  | hour  |

**ISTRUMENTS**

ÈXAS

## **OUTPUTS ELECTRICAL CHARACTERISTICS: CHG, STAT**

Unless otherwise noted,  $V_{DD} = 5V$ ,  $V_{BATT} = 3.6V$ .  $C_{BATT} = 4.7 \ \mu\text{F}$ ,  $C_{CHG_DET} = 10 \ \mu\text{F}$ . Typical values and limits appearing in normal type apply for  $T_J = 25^{\circ}\text{C}$ . Limits appearing in **boldface type** apply over the entire junction temperature range for operation,  $T_J = 0^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$ . (1)(2)(3)(4)(5)

| Symbol              | Parameter          | Conditions                                                   | Min | Тур | Max | Units |

|---------------------|--------------------|--------------------------------------------------------------|-----|-----|-----|-------|

| I <sub>LED</sub>    | Output High Level  | V <sub>LED</sub> = 2.0V<br>CHSPV Register (02)h bit 5<br>= 1 | 4   | 5   | 6   | mA    |

| I <sub>LED</sub>    | Output High Level  | $V_{LED} = 2.0V$<br>CHSPV Register (02)h bit 5<br>= 0        | 8   | 10  | 12  | mA    |

| ILEAKAGE            | Leakage Current    | $V_{LED} = 1.5V$ , LED off                                   |     | 0.1 | 5   | μA    |

| LED <sub>FREQ</sub> | Blinking Frequency |                                                              | 0.8 | 1   | 1.2 | Hz    |

(1) All voltages are with respect to the potential at the GND pin.

(2) Junction-to-ambient thermal resistance is highly application and board-layout dependent. In applications where high maximum power dissipation exists, special care must be paid to thermal dissipation issues in board design.

(3) Min and Max limits are specified by design, test, or statistical analysis. Typical numbers represent the most likely norm.

(4) Low ESR Surface-Mount Ceramic Capacitors (MLCCs) are used in setting electrical characteristics.

(5) Typical values and limits appearing in normal type for  $T_J = 25^{\circ}$ C. Limits appearing in **boldfacetype** apply over the entire junction temperature range for operation,  $-40^{\circ}$ C to  $+125^{\circ}$ C.

## OUTPUTS ELECTRICAL CHARACTERISTICS: NRST, IRQB, ONSTAT

Unless otherwise noted, VDD = 5V, VBATT = 3.6V.  $C_{BATT}$  = 4.7  $\mu$ F,  $C_{CHG_DET}$  = 10  $\mu$ F. Typical values and limits appearing in normal type apply for  $T_J$  = 25°C. Limits appearing in **boldface type** apply over the entire junction temperature range for operation,  $T_J$  = 0°C to +125°C. <sup>(1)(2)(3)(4)(5)</sup>

| Symbol Parameter     |                  | Conditions                                   | Min | Тур | Max | Units |

|----------------------|------------------|----------------------------------------------|-----|-----|-----|-------|

| V <sub>OL</sub>      | Output Low Level | $I_{OL} = 4 \text{ mA}$                      |     |     | 0.4 | V     |

| I <sub>LEAKAGE</sub> | Leakage Current  | V <sub>DD</sub> = 2.5V, Output Logic<br>High | -1  |     | 1   | μA    |

(1) All voltages are with respect to the potential at the GND pin.

(2) Junction-to-ambient thermal resistance is highly application and board-layout dependent. In applications where high maximum power dissipation exists, special care must be paid to thermal dissipation issues in board design.

(3) Min and Max limits are specified by design, test, or statistical analysis. Typical numbers represent the most likely norm.

(4) Low ESR Surface-Mount Ceramic Capacitors (MLCCs) are used in setting electrical characteristics.

(5) Typical values and limits appearing in normal type for  $T_J = 25^{\circ}$ C. Limits appearing in **boldfacetype** apply over the entire junction temperature range for operation, -40°C to +125°C.

## INPUTS ELECTRICAL CHARACTERISTICS: USBSUSP, USBISEL

Unless otherwise noted,  $V_{USB} = 5V$ ,  $V_{BATT} = 3.6V$ .  $C_{BATT} = 4.7 \ \mu\text{F}$ ,  $C_{CHG_DET} = 10 \ \mu\text{F}$ . Typical values and limits appearing in normal type apply for  $T_J = 25^{\circ}\text{C}$ . Limits appearing in **boldface type** apply over the entire junction temperature range for operation,  $T_J = 0^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$ .  $^{(1)(2)(3)(4)(5)(6)}$

| Symbol               | Parameter        | Conditions | Min                  | Тур | Max                  | Units |

|----------------------|------------------|------------|----------------------|-----|----------------------|-------|

| V <sub>IL</sub>      | Input Low Level  |            |                      |     | 0.3*V <sub>USB</sub> | V     |

| V <sub>IH</sub>      | Input High Level |            | 0.7*V <sub>USB</sub> |     |                      | V     |

| I <sub>LEAKAGE</sub> | Input Leakage    |            | -1                   |     | 1                    | μA    |

(1) All voltages are with respect to the potential at the GND pin.

(2) Junction-to-ambient thermal resistance is highly application and board-layout dependent. In applications where high maximum power dissipation exists, special care must be paid to thermal dissipation issues in board design.

(3) Min and Max limits are specified by design, test, or statistical analysis. Typical numbers represent the most likely norm.

(4) Low ESR Surface-Mount Ceramic Capacitors (MLCCs) are used in setting electrical characteristics.

(5) Typical values and limits appearing in normal type for  $T_J = 25^{\circ}$ C. Limits appearing in **boldfacetype** apply over the entire junction temperature range for operation, -40°C to +125°C.

(6) LDO2EN, BUCKTEN, and USBSUSP have weak internal pull downs while pins POWERACK, ONOFF do not have this.

www.ti.com

## INPUTS ELECTRICAL CHARACTERISTICS: POWERACK, ONOFF, LDO2EN, BUCK1EN

Unless otherwise noted,  $V_{DD} = 5V$ ,  $V_{BATT} = 3.6V$ .  $C_{BATT} = 4.7 \ \mu\text{F}$ ,  $C_{CHG\_IN} = 10 \ \mu\text{F}$ . Typical values and limits appearing in normal type apply for  $T_J = 25^{\circ}\text{C}$ . Limits appearing in **boldface type** apply over the entire junction temperature range for operation,  $T_J = 0^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$ .  $^{(1)(2)(3)(4)(5)(6)}$

| Symbol               | Parameter        | Conditions | Min | Тур | Max | Units |

|----------------------|------------------|------------|-----|-----|-----|-------|

| V <sub>IL</sub>      | Input Low Level  |            |     |     | 0.4 | V     |

| V <sub>IH</sub>      | Input High Level |            | 1.4 |     |     | V     |

| I <sub>LEAKAGE</sub> | Input Leakage    |            | -1  |     | 1   | μA    |

(1) All voltages are with respect to the potential at the GND pin.

(2) Junction-to-ambient thermal resistance is highly application and board-layout dependent. In applications where high maximum power dissipation exists, special care must be paid to thermal dissipation issues in board design.

(3) Min and Max limits are specified by design, test, or statistical analysis. Typical numbers represent the most likely norm.

(4) Low ESR Surface-Mount Ceramic Capacitors (MLCCs) are used in setting electrical characteristics.

(5) Typical values and limits appearing in normal type for  $T_J = 25^{\circ}$ C. Limits appearing in **boldfacetype** apply over the entire junction temperature range for operation, -40°C to +125°C.

(6) LDO2EN, BUCK1EN, and USBSUSP have weak internal pull downs while pins POWERACK, ONOFF do not have this.

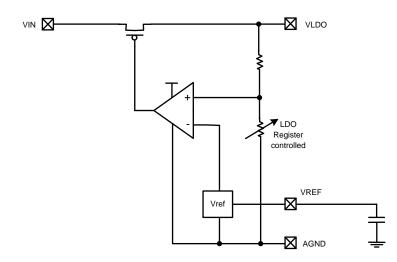

## LDO1: LOW DROPOUT LINEAR REGULATORS

Unless otherwise noted, VIN1 = 3.6V,  $I_{MAX}$  = 150 mA,  $V_{OUT}$  = Default Value,  $C_{VDD}$  = 10 µF,  $C_{LDO1}$  = 1.0 µF, ESR = 5 mΩ–500 mΩ,  $C_{VREFH}$  = 100 nF. Typical values and limits appearing in normal type apply for  $T_J$  = 25°C. Limits appearing in **boldface type** apply over the entire junction temperature range for operation, 0°C to +125°C.

| Symbol                    | Parameter                           | Conditions                                                                                                                                                                         | Min | Тур | Max | Units |

|---------------------------|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| VIN1                      | Operational Voltage Range           |                                                                                                                                                                                    | 2.5 |     | 6.0 | V     |

| V <sub>OUT</sub> Range    | Output Voltage<br>Programming Range | T <sub>A</sub> = 25°C<br>1.2V–3.3V in 100 mV Steps                                                                                                                                 | 1.2 |     | 3.3 | V     |

| V <sub>OUT</sub> Accuracy | Output Voltage Accuracy             | $  \begin{array}{l} 1 \text{ mA} \leq I_{OUT} \leq I_{MAX}, \text{ Over} \\ \hline \\ Full Line and Load \\ Regulation. \\ \hline \\ V_{OUT} = \text{Default Value.} \end{array} $ |     |     | 3   | %     |

| ΔV <sub>OUT</sub>         | Line Regulation                     | $V_{IN} = (V_{OUT} + 500 \text{ mV}) \text{ to}$<br>5.5V, Load Current = $I_{MAX}$                                                                                                 |     | 3   |     | mV    |

|                           | Load Regulation                     | $V_{IN} = 3.6V$ ,<br>Load Current = 1 mA to I <sub>MAX</sub>                                                                                                                       |     | 10  |     | mV    |

| I <sub>SC</sub>           | Short Circuit Current Limit         | $V_{OUT} = 0V$                                                                                                                                                                     | 600 | 750 |     | mA    |

| $V_{IN} - V_{OUT}$        | Dropout Voltage                     | Load Current = I <sub>MAX</sub>                                                                                                                                                    |     | 60  | 150 | mV    |

| PSRR                      | Power Supply Ripple<br>Rejection    | F = 10 kHz, Load Current = I <sub>MAX</sub>                                                                                                                                        |     | 30  |     | dB    |

| R <sub>SHUNT</sub>        | LDO Output Impedance                | LDO Disabled, V <sub>OUT</sub> =<br>Default Value                                                                                                                                  |     |     | 200 | Ω     |

## LDO2: LOW DROPOUT LINEAR REGULATOR

Unless otherwise noted VIN1 = 3.6V,  $I_{MAX}$  = 150 mA,  $V_{OUT}$  = Default Value,  $C_{VDD}$  = 10.0  $\mu$ F,  $C_{LDO2}$  = 1.0  $\mu$ F, ESR = 5 m $\Omega$ -500 m $\Omega$ ,  $C_{VREFH}$  = 100 nF. Typical values and limits appearing in normal type apply for  $T_J$  = 25°C. Limits appearing in **boldface type** apply over the entire junction temperature range for operation, 0°C to +125°C.

| Symbol                    | Parameter                                                                                                                                                                                                                                            | Conditions                                                                                   | Min | Тур | Max | Units |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| VIN2                      | Operational Voltage Range                                                                                                                                                                                                                            |                                                                                              | 2.5 |     | 6.0 | V     |

| V <sub>OUT</sub> Range    | Output Voltage<br>Programming RangeT_A = 25°C<br>1.3V–3.3V in 100 mV Steps                                                                                                                                                                           |                                                                                              | 1.3 |     | 3.3 | V     |

| V <sub>OUT</sub> Accuracy | $ \begin{array}{c} \text{Output Voltage Accuracy} \\ (\text{Default V}_{\text{OUT}}) \end{array} \begin{array}{c} 1 \text{ mA} \leq I_{\text{OUT}} \leq I_{\text{MAX}}, \text{Over} \\ \text{Full Line and Load} \\ \text{Regulation.} \end{array} $ |                                                                                              | -3  |     | 3   | %     |

| ΔV <sub>OUT</sub>         | Line Regulation                                                                                                                                                                                                                                      | $V_{IN} = (V_{OUT} + 500 \text{ mV}) \text{ to}$<br>5.5V,<br>Load Current = I <sub>MAX</sub> |     | 3   |     | mV    |

|                           | Load Regulation                                                                                                                                                                                                                                      | $V_{IN} = 3.6V,$<br>Load Current = 1 mA to I <sub>MAX</sub>                                  |     | 10  |     | mV    |

| I <sub>SC</sub>           | Short Circuit Current Limit                                                                                                                                                                                                                          | V <sub>OUT</sub> = 0V                                                                        | 600 | 750 |     | mA    |

P3913

www.ti.com

## LDO2: LOW DROPOUT LINEAR REGULATOR (continued)

Unless otherwise noted VIN1 = 3.6V,  $I_{MAX}$  = 150 mA,  $V_{OUT}$  = Default Value,  $C_{VDD}$  = 10.0 µF,  $C_{LDO2}$  = 1.0 µF, ESR = 5 mΩ–500 mΩ,  $C_{VREFH}$  = 100 nF. Typical values and limits appearing in normal type apply for  $T_J$  = 25°C. Limits appearing in **boldface type** apply over the entire junction temperature range for operation, 0°C to +125°C.

| Symbol             | Parameter                             | Conditions                                        | Min | Тур | Max | Units |  |

|--------------------|---------------------------------------|---------------------------------------------------|-----|-----|-----|-------|--|

| $V_{IN} - V_{OUT}$ | Dropout Voltage                       | Load Current = I <sub>MAX</sub>                   |     | 60  | 150 | mV    |  |

| PSRR               | Power Supply Ripple<br>Rejection      | $F = 1 \text{ kHz}$ , Load Current = $I_{MAX}$    |     | 50  |     | dB    |  |

|                    |                                       | F = 10 kHz, Load Current = I <sub>MAX</sub>       |     | 35  |     | uв    |  |

| e <sub>N</sub>     | Analog Supply Output<br>Noise Voltage | 10 Hz < F < 100 kHz                               |     | 50  |     | µVrms |  |

| R <sub>SHUNT</sub> | LDO Output Impedance                  | LDO Disabled, V <sub>OUT</sub> =<br>Default Value |     |     | 200 | Ω     |  |

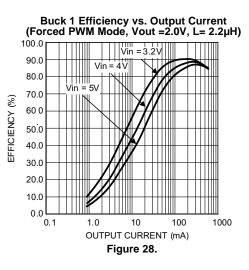

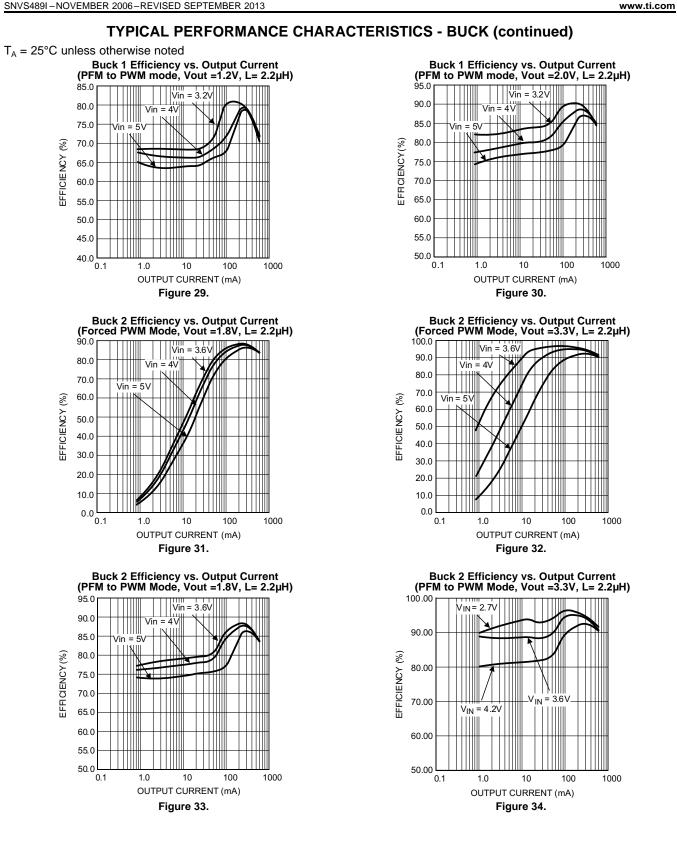

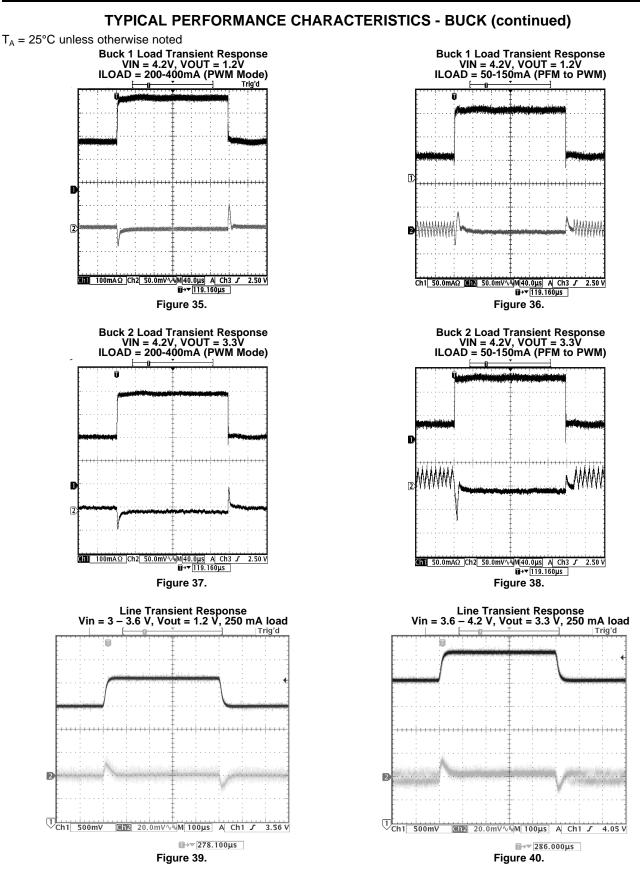

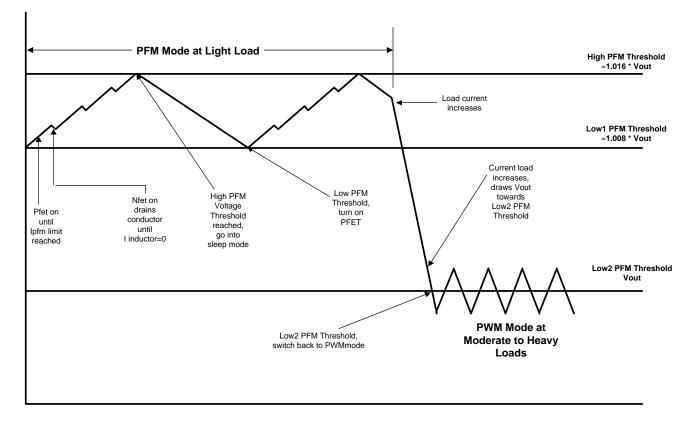

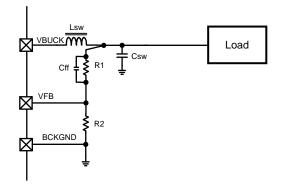

## **BUCK1 CONVERTER ELECTRICAL CHARACTERISTICS**

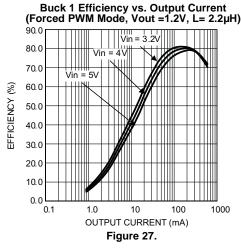

Unless otherwise noted, VIN2 = 3.6 V,  $V_{OUT}$  = default value,  $C_{VIN2}$  = 10 µF,  $C_{SW1}$  = 10 µF,  $L_{SW1}$  = 2.2 µH Typical values and limits appearing in normal type apply for  $T_J$  = 25°C. Limits appearing in **boldface type** apply over the entire junction temperature range for operation, 0°C to +125°C. Modulation mode is PWM mode with automatic switch to PFM at light loads.

| Symbol                 | Parameter                           | Conditions                                                       | Min | Тур   | Max  | Units |

|------------------------|-------------------------------------|------------------------------------------------------------------|-----|-------|------|-------|

| VIN2                   | Input Voltage                       |                                                                  | 2.7 |       | 6.0  | V     |

| V <sub>OUT</sub> Range | Output Voltage<br>Programming Range |                                                                  |     |       | 2.0  | V     |

| ΔV <sub>OUT</sub>      | Static Output Voltage<br>Tolerance  | I <sub>OUT</sub> = 200 mA, Including<br>Line and Load Regulation | -3  |       | 3    | %     |

|                        | Line Regulation                     | $I_{OUT} = 10 \text{ mA}$<br>$V_{IN2} = 2.5 \text{V} - V_{DD}$   |     | 0.2   |      | %/V   |

|                        | Load Regulation                     | 100 mA < I <sub>OUT</sub> < 300 mA                               |     | 0.002 |      | %/mA  |

| I <sub>OUT</sub>       | Continuous Output<br>Current        |                                                                  | 600 |       |      | mA    |

|                        | Peak Output Current<br>Limit        |                                                                  | 850 | 1000  | 1150 | mA    |

| I <sub>PFM</sub>       | Max I <sub>LOAD</sub> , PFM<br>Mode |                                                                  |     | 75    |      | mA    |

| l <sub>Q</sub>         | Quiescent Current                   | I <sub>OUT</sub> = 0 mA                                          |     | 30    | 90   |       |

|                        |                                     | Buck1 Disabled                                                   |     |       | 1    | μA    |

| F <sub>OSC</sub>       | Internal Oscillator<br>Frequency    | PWM Mode                                                         |     | 2     |      | MHz   |

| η                      | Peak Efficiency                     |                                                                  |     | 90    |      | %     |

| T <sub>ON</sub>        | Turn-on Time                        | To 95% Level (1)                                                 |     |       | 1    | ms    |

(1) Specified by design. Not production tested.

## **BUCK2 CONVERTER ELECTRICAL CHARACTERISTICS**

Unless otherwise noted, VIN3 = 3.6V,  $V_{OUT}$  = default value,  $C_{VIN3}$  = 10 µF,  $C_{SW1}$  = 10 µF,  $L_{SW2}$  = 2.2 µH Typical values and limits appearing in normal type apply for  $T_J$  = 25°C. Limits appearing in **boldface type** apply over the entire junction temperature range for operation, 0°C to +125°C. Modulation mode is PWM mode with automatic switch to PFM at light loads.

| Symbol                 | Parameter                           | Conditions                                                            | Min | Тур   | Max | Units |

|------------------------|-------------------------------------|-----------------------------------------------------------------------|-----|-------|-----|-------|

| VIN3                   | Input Voltage                       |                                                                       | 2.7 |       | 6.0 | V     |

| V <sub>OUT</sub> Range | Output Voltage<br>Programming Range | 1.80V–3.30V in 100 mV<br>Steps                                        | 1.8 |       | 3.3 | V     |

| ΔV <sub>OUT</sub>      | Static Output Voltage<br>Tolerance  | I <sub>OUT</sub> = 200 mA, Including<br>Line and Load Regulation      | -3  |       | 3   | %     |

|                        | Line Regulation                     | I <sub>OUT</sub> = 10 mA<br>V <sub>IN3</sub> = 2.5V - V <sub>DD</sub> |     | 0.2   |     | %/V   |

|                        | Load Regulation                     | 100 mA < I <sub>OUT</sub> < 300 mA                                    |     | 0.002 |     | %/mA  |

Copyright © 2006–2013, Texas Instruments Incorporated

www.ti.com

STRUMENTS

XAS

## BUCK2 CONVERTER ELECTRICAL CHARACTERISTICS (continued)

Unless otherwise noted, VIN3 = 3.6V,  $V_{OUT}$  = default value,  $C_{VIN3}$  = 10 µF,  $C_{SW1}$  = 10 µF,  $L_{SW2}$  = 2.2 µH Typical values and limits appearing in normal type apply for  $T_J$  = 25°C. Limits appearing in **boldface type** apply over the entire junction temperature range for operation, 0°C to +125°C. Modulation mode is PWM mode with automatic switch to PFM at light loads.

| Symbol           | Parameter                           | Conditions              | Min | Тур  | Max  | Units |

|------------------|-------------------------------------|-------------------------|-----|------|------|-------|

| I <sub>OUT</sub> | Continuous Output<br>Current        |                         | 600 |      |      | mA    |

|                  | Peak Output Current<br>Limit        |                         | 850 | 1000 | 1150 | mA    |

| I <sub>PFM</sub> | Max I <sub>LOAD</sub> , PFM<br>Mode |                         |     | 75   |      | mA    |

| l <sub>Q</sub>   | Quiescent Current                   | I <sub>OUT</sub> = 0 mA |     | 30   | 90   | ۵     |

|                  |                                     | Buck2 Disabled          |     |      | 1    | μA    |

| F <sub>OSC</sub> | Internal Oscillator<br>Frequency    | PWM Mode                |     | 2    |      | MHz   |

| η                | Peak Efficiency                     |                         |     | 90   |      | %     |

| T <sub>ON</sub>  | Turn-on Time                        | To 95% Level (1)        |     |      | 1    | ms    |

(1) Specified by design. Not production tested.

## **BUCK3 ELECTRICAL CHARACTERISTICS**

Unless otherwise noted, VIN4 = 3.6V,  $C_{VIN4} = 10 \ \mu\text{F}$ ,  $C_{BB} = 22 \ \mu\text{F}$ ,  $L_{BB} = 2.2 \ \mu\text{H}$  Typical values and limits appearing in normal type apply for  $T_J = 25^{\circ}\text{C}$ . Limits appearing in **boldface type** apply over the entire junction temperature range for operation, 0°C to +125°C. Modulation mode is PWM mode with automatic switch to PFM at light loads.

| Symbol                 | Parameter                           | Conditions                                                               | Min | Тур    | Max  | Units |

|------------------------|-------------------------------------|--------------------------------------------------------------------------|-----|--------|------|-------|

| VIN4                   | Input Voltage                       | I <sub>OUTMAX</sub> = 500 mA                                             | 2.7 |        | 5.7  | V     |

| V <sub>OUT</sub> Range | Output Voltage<br>Programming Range |                                                                          |     |        | 3.3  | V     |

| ΔV <sub>OUT</sub>      | Static Output Voltage<br>Tolerance  | I <sub>OUT</sub> = 0 mA–500 mA,<br>Including Line and Load<br>Regulation | -4  |        | 4    | %     |

|                        | Line Regulation                     | I <sub>OUT</sub> = 10 mA                                                 |     | 0.2    |      | %/V   |

|                        | Load Regulation                     | 100 mA < I <sub>OUT</sub> < 500 mA                                       |     | 0.0016 |      | %/mA  |

| I <sub>OUT</sub>       | Continuous Output<br>Current        |                                                                          | 500 |        |      | mA    |

|                        | Peak Inductor Current<br>Limit      | V <sub>OUT</sub> = 3.3V<br>1A Load at V <sub>IN</sub> = 2.7V             | 900 |        | 1200 | mA    |

| I <sub>PFM</sub>       | Max I <sub>LOAD</sub> , PFM<br>Mode |                                                                          |     | 75     |      | mA    |

| Ι <sub>Q</sub>         | Quiescent Current                   | I <sub>OUT</sub> = 0 mA PFM No<br>Switching                              |     | 80     |      | μA    |

|                        |                                     | Buck3 Disabled                                                           |     |        | 1    |       |

| F <sub>OSC</sub>       | Internal Oscillator<br>Frequency    | PWM Mode                                                                 |     | 2      |      | MHz   |

| η                      | Peak Efficiency                     |                                                                          |     | 93     |      | %     |

| T <sub>ON</sub>        | Turn-on Time                        | To 95% Level <sup>(1)</sup>                                              |     |        | 1    | ms    |

(1) Specified by design. Not production tested.

## ADC ELECTRICAL CHARACTERISTICS

External components:

| Symbol                     | Parameter                                                          | Conditions                                                                                 | Min              | Тур   | Max                | Units |

|----------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------|------------------|-------|--------------------|-------|

| V <sub>REF</sub>           | Reference Voltage                                                  | T = 25°C                                                                                   | 1.220            | 1.225 | 1.230              | V     |

|                            |                                                                    | T = 0°C to +125°C                                                                          | 1.200            | 1.225 | 1.230              | V     |

| INL                        | Core ADC Integral Non-<br>linearity                                | $V_{REF} = 1.225^{(1)}$                                                                    | -1               |       | 1                  | LSB   |

| DNL                        | Core ADC Differential Non-<br>linearity                            | $V_{REF} = 1.225$ <sup>(1)</sup>                                                           | -0.5             |       | 0.5                | LSB   |

| V <sub>GP_IN</sub>         | General Purpose ADC<br>Input Voltage Range                         |                                                                                            | V <sub>REF</sub> |       | 2·V <sub>REF</sub> | V     |

| VBATT,                     | Battery Max Voltage Scalar<br>Output                               | VBATT = 3.5V                                                                               | 2.435            | 2.45  | 2.465              | V     |

| RANGE 0                    | Battery Min Voltage Scalar<br>Output                               | VBATT = 2.6V                                                                               | 1.217            | 1.225 | 1.232              | V     |

| V <sub>BATT,</sub>         | Battery Max Voltage Scalar<br>Output                               | VBATT = 4.4V                                                                               | 2.435            | 2.45  | 2.465              | V     |

| RANGE 1                    | Battery Min Voltage Scalar<br>Output                               | V <sub>REF</sub> = 2.6V                                                                    | 1.217            | 1.225 | 1.232              | V     |

| V <sub>ISENSE</sub>        | ISENSE Max Voltage<br>Scalar Output                                | $V_{ISENSE} = 0.6463V$<br>( $I_{CHG} = 0.605A$ ,<br>$R_{SENSE} = 4.64 \text{ k}\Omega$ )   | 2.373            | 2.45  | 2.519              | V     |

| RANGE 0                    | ISENSE Min Voltage<br>Scalar Output                                | $V_{ISENSE} = 0V$<br>( $I_{CHG} = 0A$ ,<br>$R_{SENSE} = 4.64 \text{ k}\Omega$ )            | 1.186            | 1.225 | 1.260              | V     |

| V <sub>ISENSE</sub>        | ISENSE Max Voltage<br>Scalar Output                                | V <sub>ISENSE</sub> = 1.175V<br>(I <sub>CHG</sub> = 1.1A,<br>R <sub>SENSE</sub> = 4.64 kΩ) | 2.373            | 2.45  | 2.519              | V     |

| RANGE 1                    | ISENSE Min Voltage<br>Scalar Output                                |                                                                                            | 1.186            | 1.225 | 1.260              | V     |

| ADC1 & ADC2 <sub>MIN</sub> | ADC1 & ADC2 Min Voltage<br>Scalar Output                           | V <sub>REFH</sub> = 1.225                                                                  | 1.218            | 1.225 | 1.230              | V     |

| ADC1 & ADC2 <sub>MAX</sub> | DC1 & ADC2 <sub>MAX</sub> ADC1 & ADC2 Max<br>Voltage Scalar Output |                                                                                            | 2.436            | 2.45  | 2.46               | V     |

| t <sub>CONV</sub>          | Conversion Time                                                    | (1)                                                                                        |                  |       | 5                  | ms    |

| t <sub>WARM</sub>          | Warm-up Time                                                       |                                                                                            |                  | 2     |                    | ms    |

(1) Specified by design. Not production tested.

www.ti.com

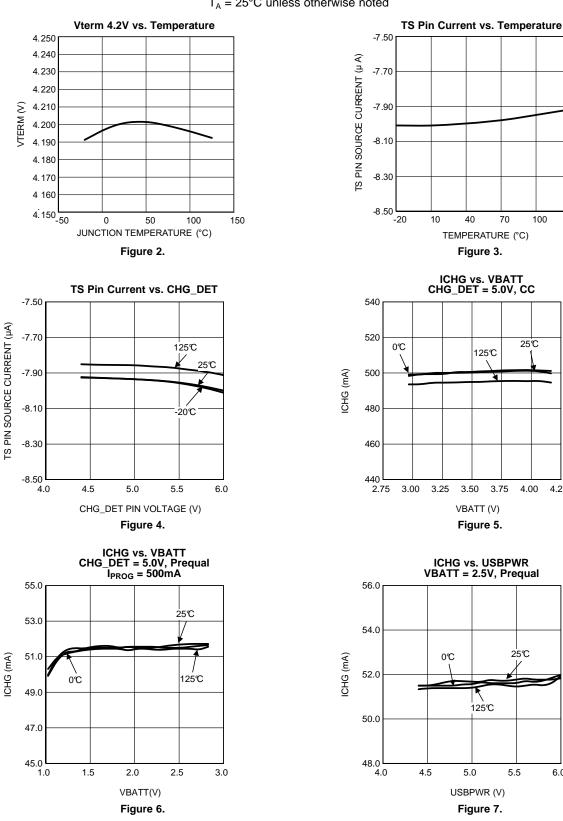

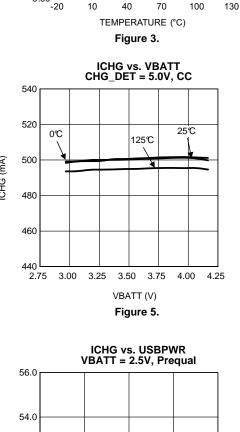

## **TYPICAL CHARACTERISTICS — BATTERY CHARGER**

$T_A = 25^{\circ}C$  unless otherwise noted

SNVS489I-NOVEMBER 2006-REVISED SEPTEMBER 2013

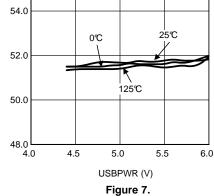

#### $T_A = 25^{\circ}C$ unless otherwise noted ICHG vs. CHG\_DET VBATT = 3.5V, CC ICHG vs. Temperature CHG\_DET = 5V, VBATT = 3.75V, CC 540 540 520 520 0℃ ICHG (mA) 500 500 ICHG (mA) 25℃ 480 480 125°C 460 460 440 440 0 25 50 75 100 125 150 4.0 4.5 5.0 5.5 6.0 JUNCTION TEMPERATURE (°C) CHG\_DET (V) Figure 8. Figure 9. ICHG vs. Temperature CHG\_DET = 5V, VBATT = 2.5V, Prequal **Thermal Regulation of Charge Current** 55.0 600 500 53.0 CHARGE CURRENT (mA) 400 ICHG (mA) 51.0 300 Active Thermal Regulation 49.0 200 47.0 100 VDD = 5VVBATT = 3.5V 0 45.0 125 90 0 25 50 75 100 150 80 100 110 120 130 JUNCTION TEMPERATURE (°C) JUNCTION TEMPERATURE (℃) Figure 10. Figure 11. **USB ILIMIT vs. Temperature** 520 500 USB ILIMIT (mA) 480 460 440 420 50 75 100 125 150 0 25 JUNCTION TEMPERATURE (℃) Figure 12. Submit Documentation Feedback Copyright © 2006–2013, Texas Instruments Incorporated

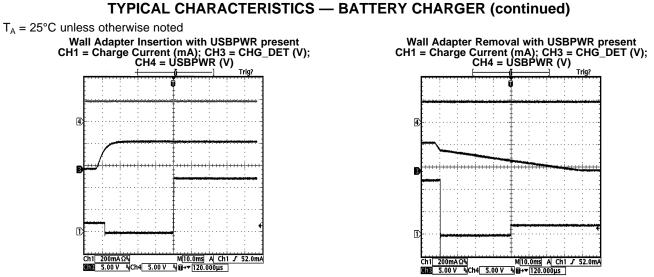

**TYPICAL CHARACTERISTICS — BATTERY CHARGER (continued)**

Product Folder Links: LP3913

SNVS489I-NOVEMBER 2006-REVISED SEPTEMBER 2013

Figure 13.

Figure 14.

Trig'd

Triq'd

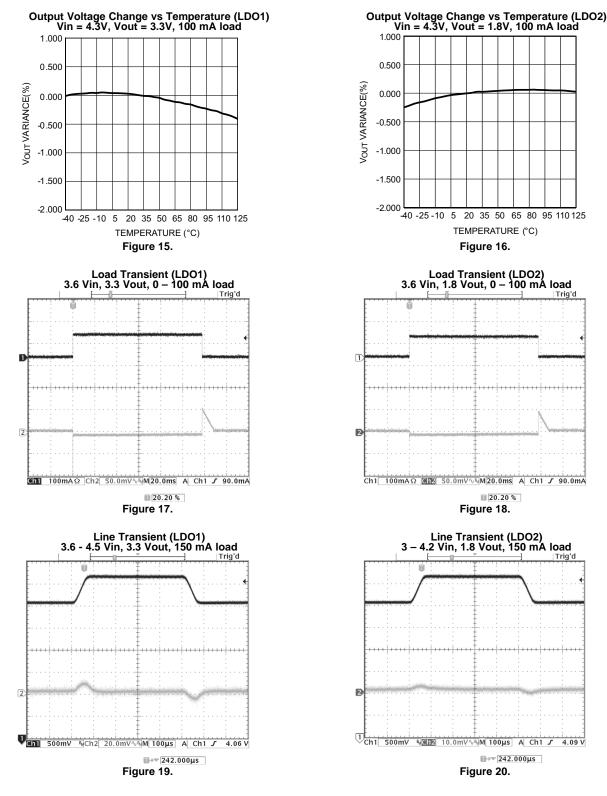

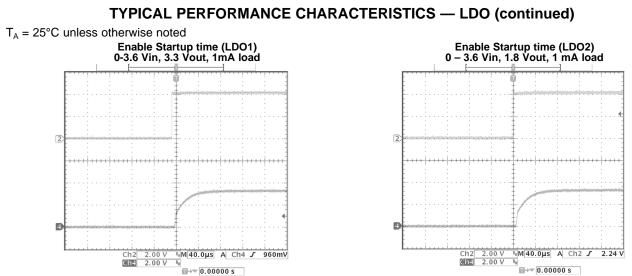

## **TYPICAL PERFORMANCE CHARACTERISTICS — LDO**

$T_A = 25^{\circ}C$  unless otherwise noted

SNVS489I-NOVEMBER 2006-REVISED SEPTEMBER 2013

Figure 22.

#### SNVS489I-NOVEMBER 2006-REVISED SEPTEMBER 2013

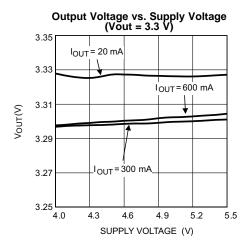

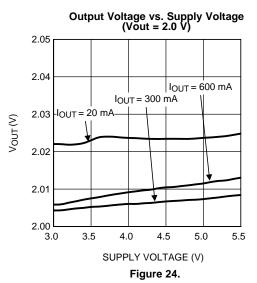

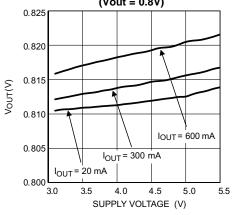

### **TYPICAL PERFORMANCE CHARACTERISTICS - BUCK**

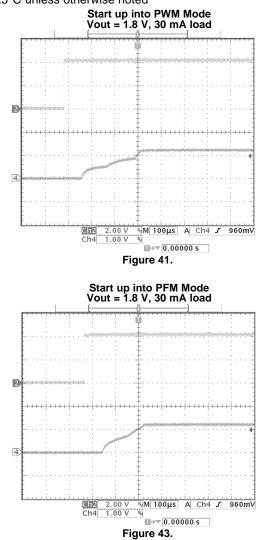

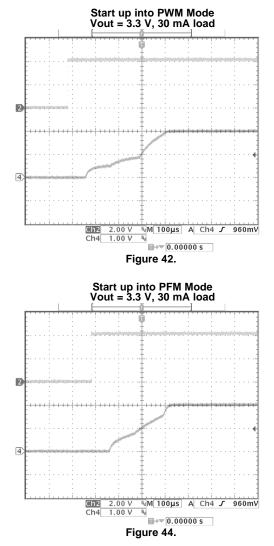

$T_A = 25^{\circ}C$  unless otherwise noted

#### Figure 23.

Output Voltage vs. Supply Voltage (Vout = 0.8V)

#### Figure 26.

www.ti.com

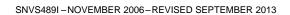

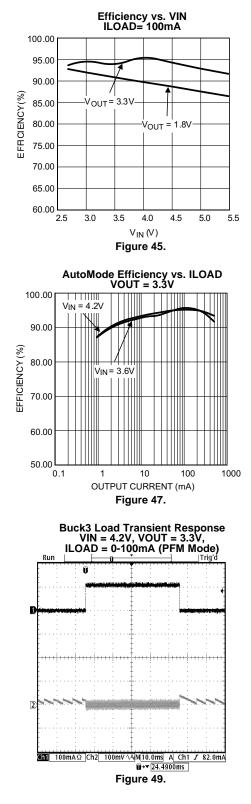

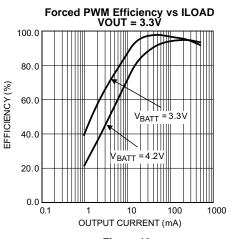

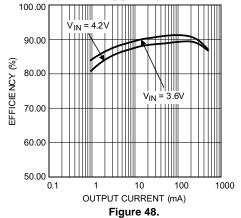

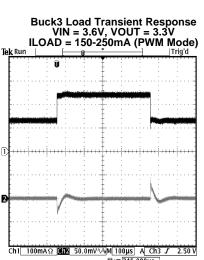

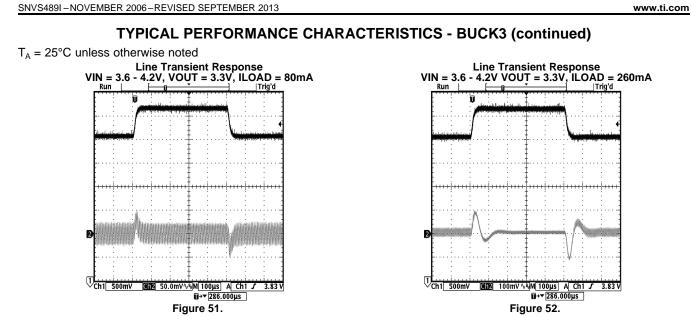

## **TYPICAL PERFORMANCE CHARACTERISTICS - BUCK3**

$T_A = 25^{\circ}C$  unless otherwise noted

#### Figure 46.

AutoMode Efficiency vs. ILOAD VOUT = 1.8V

www.ti.com

## FUNCTIONAL DESCRIPTION

## **Operating Modes**

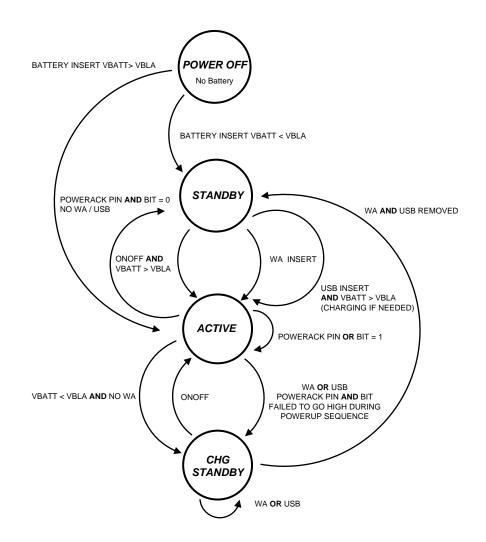

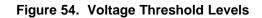

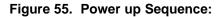

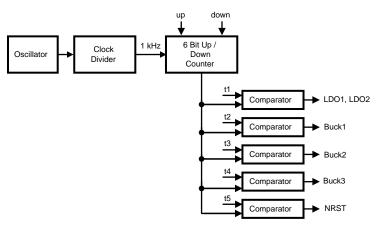

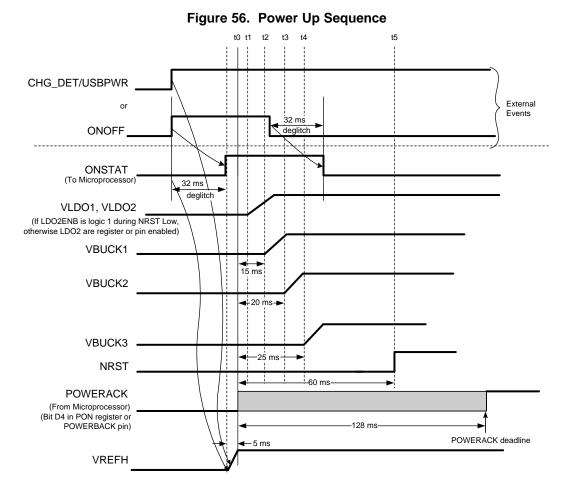

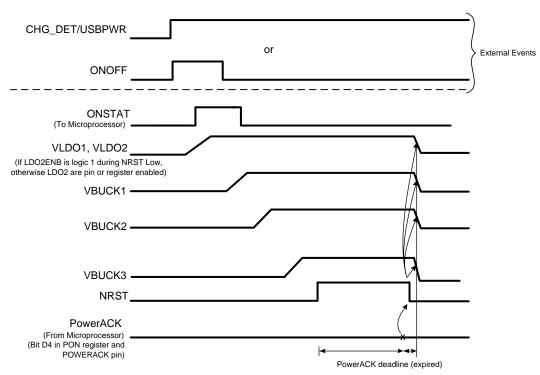

The LP3913 can be in 3 different operating modes as illustrated in Figure 53:

### **State Machine Definitions**

V<sub>BLA</sub> Battery low alarm threshold

V<sub>BATT</sub> Battery voltage

WA Wall Adapter

**USB** Universal Serial Bus Adapter

**ONOFF** On off pin event

**POWERACK** Acknowledgment from the Host Processor

Table 2. Power State Table

|                            | Power Off | Standby     | Active                            | Charger Standby                   |

|----------------------------|-----------|-------------|-----------------------------------|-----------------------------------|

| LDO1,2                     | Off       | Off         | On                                | Off                               |

| BUCK1,2                    | Off       | Off         | On                                | Off                               |

| BUCK3                      | Off       | Off         | On                                | Off                               |

| CHARGER                    | Off       | Off         | On if Charger / USB<br>Present    | On if Charger / USB<br>Present    |

| A/D Converter              | Off       | Off         | On                                | Off                               |

| NRST                       | Low       | Low         | High                              | Low                               |

| I <sup>2</sup> C interface | Off       | Off         | On                                | On                                |

| Internal System Oscillator | Off       | Off         | On                                | On                                |

| Battery Monitor            | Off       | On          | On                                | On                                |

| Current consumption        | <1 µA     | 10 μA (typ) | See Electrical<br>Characteristics | See Electrical<br>Characteristics |

## Power-On-Reset

The LP3913 is equipped with an internal Power-On-Reset ("POR") circuit that will reset the logic when  $V_{DD} < V_{POR}$ . This ensures that the logic is properly initialized when  $V_{DD}$  rises above the minimum operating voltage of the Logic and the internal oscillator that clocks the Sequential Logic in the Control section.

### Thermal Shutdown and Thermal Alarm

An internal temperature sensor monitors the junction temperature of the LP3913 and forcibly invokes standby mode in the unusual case when the junction temperature of the silicon exceeds the normal operating level due to excessive loads on all power regulators and the Li-ion charger and/or due to an abnormally high ambient temperature. The thermal Shutdown threshold is 160°C.

The thermal shutdown is preceded by a Thermal alarm that generates an interrupt request if unmasked (see Interrupt Request generation). The temperature threshold for triggering the alarm is 115°C.

### NRST Pin

The NRST pin is an open-drain output and is active low during Standby, Power Off and Charger Standby modes. The NRST timing is determined by a factory programmable counter.

### **Control Registers**